4月17日,飞凌嵌入式「2026嵌入式及边缘AI技术生态大会」在深圳圆满收官!这场大会以“AI向实 生态共融”为核心,汇聚了300余位来自芯片、操作系统、存储、工控等全产业链的专家、生态伙伴与技术从业者,共话技术趋势、拆解落地实践、共筑开放生态,为嵌入式AI技术赋能千行百业,写下了浓墨重彩的一笔。

盛会启幕:锚定产业务实新航向

飞凌嵌入式研发总监宋明洋致开幕辞,分享企业20年来的技术深耕与生态布局,明确大会“AI向实”的核心:让技术走出概念、落地产业,为千行百业智能化升级注入真实动力。

主题演讲:11场分享覆盖全赛道

现场11位行业大咖聚焦工业升级、边缘AI、开源鸿蒙、工控生态等核心赛道,全程输出实战干货,直击产业痛点与未来方向:(以下按嘉宾演讲顺序排序):

飞凌嵌入式技术副总经理梁飞带来《嵌入式新趋势・新技术・新产品》的内容分享,解读行业风向与飞凌嵌入式的最新的产品与技术布局。

飞凌嵌入式项目总监王二猛,《聚焦热点行业,解析嵌入式应用》的主题演讲,分享嵌入式技术如何在各行业落地生根。

瑞芯微产品总监杨凯,带来《瑞芯微AIoT 2.0平台助力工业升级》畅享芯片级平台如何为工业智能化注入新动能。

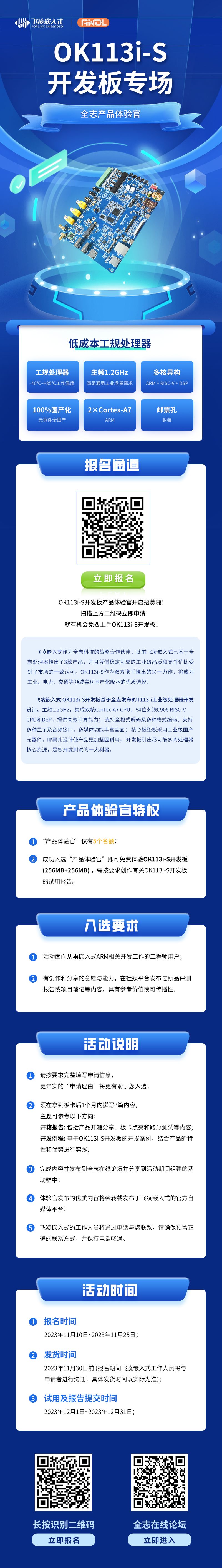

全志工业车载事业部副总经理皮杰勇,带来《深耕工业控制,共创智能未来——全志芯平台助力工业智能化升级》,探索国产芯片在工控领域的创新实践。

安谋科技高级市场经理陈翊翔,带来《安谋科技JishuShell一键部署OpenClaw助力Agentic AI端侧落地》详细讲解小龙虾部署背后的秘密。

飞凌嵌入式边缘AI专家柴宇,用《嵌入式AI边缘计算:技术能力构建与规模化商业落地》的主题演讲,拆解边缘AI的技术路径与商业实践。

飞凌嵌入式测试专家张硕,依据《从单项测试到系统验证:嵌入式板卡可靠性实战之道》的分享,揭秘板卡从研发到量产的质量保障体系。

江波龙高级商业拓展总监钟山,带来《集成存储,探索端侧AI》的主题分享,让我们看到了存储与AI融合的新可能。

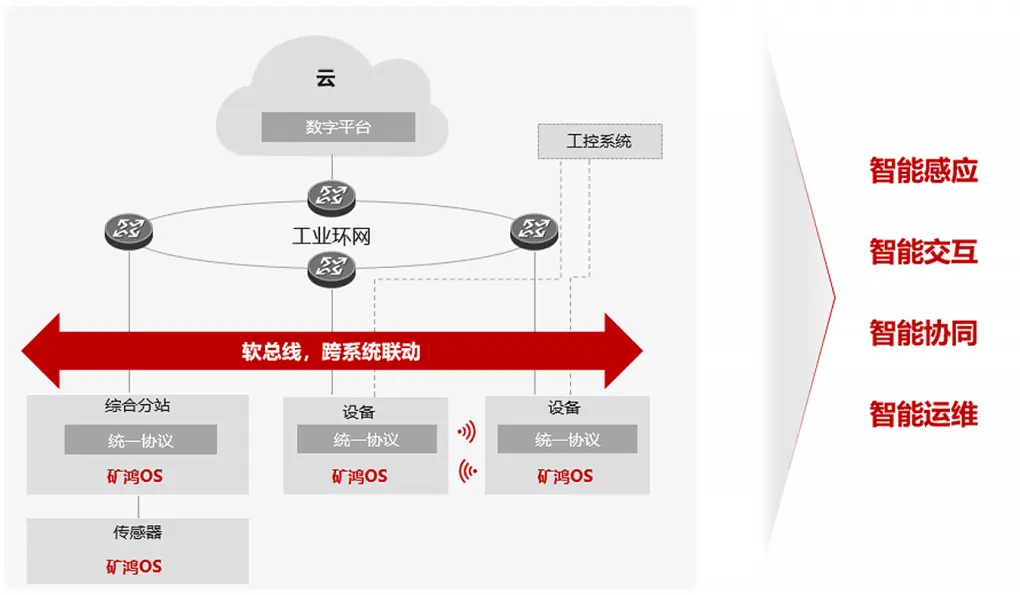

软通动力助理副总裁/鸿湖万联开源鸿蒙与矿鸿事业部总经理段威,用《开源鸿蒙与嵌入式硬件的协同创新与应用:鸿湖万联携手飞凌共创开源新生态》的分享,探索开源鸿蒙在嵌入式领域的实践与未来。

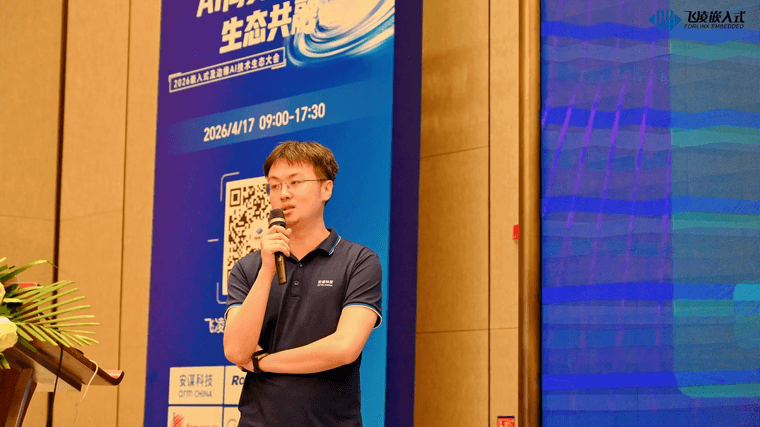

菲尼克斯电气PLCnext软件生态产品经理徐佩文,带来《硬件筑基,软件赋智:vPLCnext&飞凌赋能工控新生态》的主题分享,带我们领略软硬件的结合如何重构工控生态。

最后,由飞凌嵌入式生态发展总监薛凯带来《融生态・聚合力:飞凌嵌入式开放生态与伙伴共赢》的分享,解读飞凌嵌入式的生态布局与合作愿景。

展区沉浸体验:共览全栈生态成果

大会设置了全产品矩阵、新品推荐、软件生态、教育市场产品、生态厂商等五大主题展区,集中呈现飞凌嵌入式全栈产品矩阵与生态伙伴前沿成果。

安谋科技、瑞芯微电子、全志科技、江波龙、鸿湖万联、菲尼克斯电气、统信软件、中移物联、麒麟软件共9家合作伙伴,联合带来多领域前沿成果。从底层芯片架构、高性能硬件平台,到国产化系统适配、工业级通讯方案与端边协同应用,全方位展现产业链协同创新实力。

现场还展示了智能安防、工业视觉、人脸识别、储能运维、多模态分析等热门场景,嘉宾可零距离体验、与技术专家面对面交流,一站式掌握产业最新落地成果,让技术交流不止于讲台,真正实现技术大会的深度沟通价值。

福利高光:多重好礼点燃现场氛围

除了干货满满的技术分享,本次大会也为到场嘉宾准备了多重惊喜福利,四轮抽奖共送出飞凌嵌入式开发板、华为 GT6手表、夸克AI眼镜、Mac mini等价值近2万元的重磅好礼,将现场氛围一次次推向高潮。

圆满收官:以技术赋能千行百业

本次大会的成功举办,是飞凌嵌入式与生态伙伴打造的嵌入式 AI 领域技术盛宴,更是产业生态协同的重要里程碑。

未来,飞凌嵌入式将持续推动技术创新与生态协同,让嵌入式及边缘 AI 技术真正落地应用,携手全产业链伙伴共筑产业新生态,为中国产业智能化升级注入更强动力!

Forlinx 发布的帖子

-

不止技术盛宴!2026嵌入式及边缘AI大会,这些现场亮点燃爆了发布在 飞凌嵌入式专区

-

噢!来自78元T153开发板的降维打击发布在 飞凌嵌入式专区

¥78能买到什么? 也许是1顿工作餐,也许是2杯拿铁咖啡,也许是3条数据线......

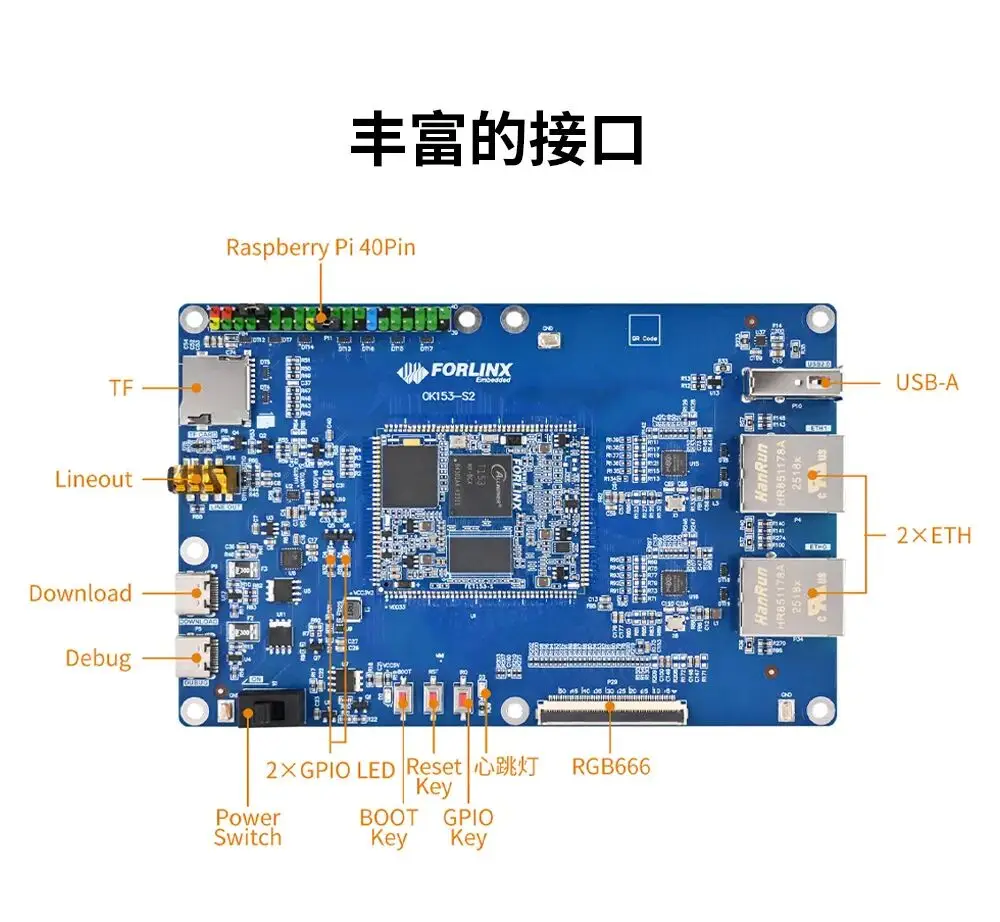

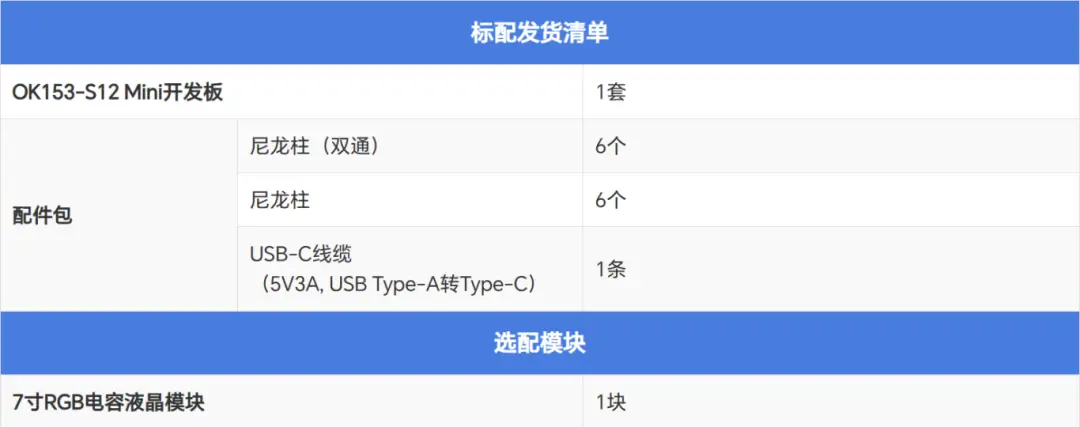

而飞凌嵌入式的答案是:1块集成了4核Cortex-A7高性能CPU、1颗RISC-V MCU、多种高速总线、还兼容树莓派的“全能小钢炮”——OK153-S12 Mini开发板。

当一款搭载了全志T153处理器的嵌入式开发板来到了这个价格,就不是仅是性价比了,而是“降维打击”!

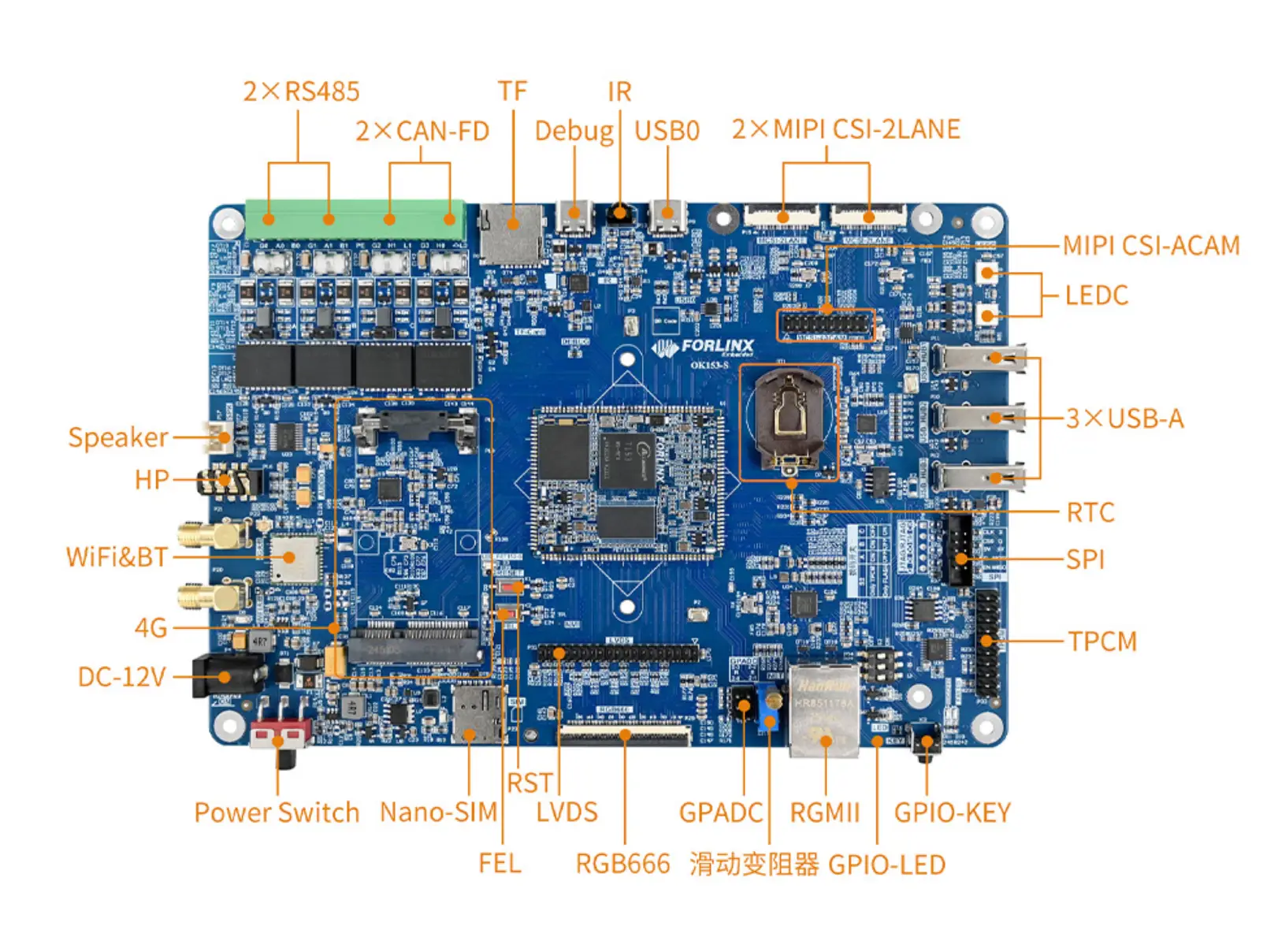

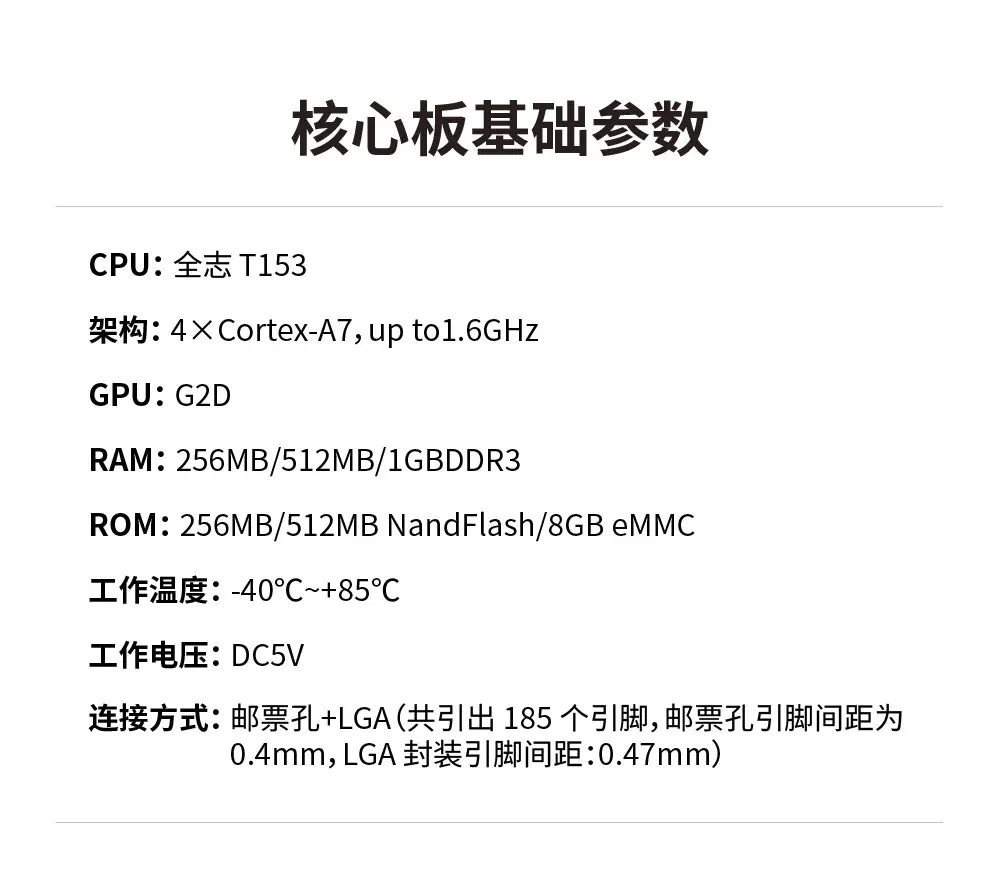

OK153-S12 Mini开发板

OK153-S12 Mini开发板基于全志T153处理器开发设计,该处理器是全志面向工业的处理器,芯片具备丰富的接口,如RGMII、UART、CAN、Display等,可以满足不同的应用场景开发。10~15年生命周期,为您的产品提供持续供应保障。

树莓派40PinGPIO接口

OK153-S12 Mini开发板板载树莓派40Pin GPIO接口,方便连接各种外部硬件。

全志新一代高性能芯片

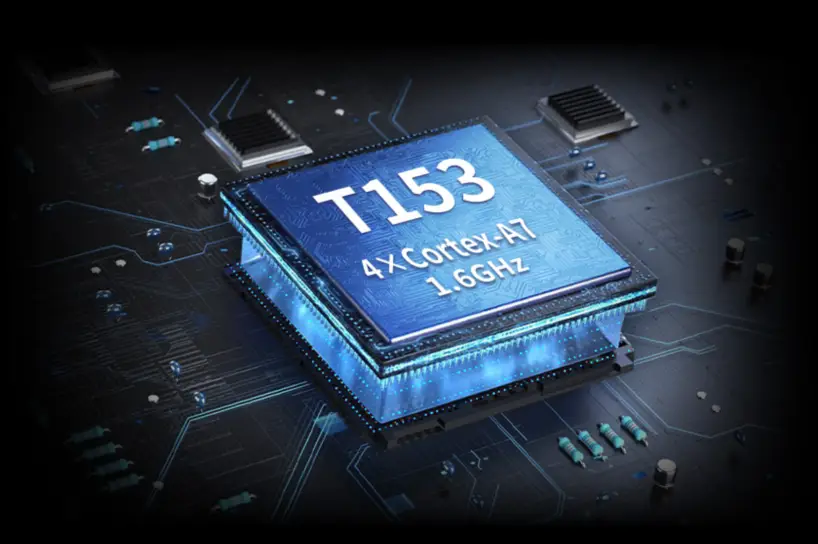

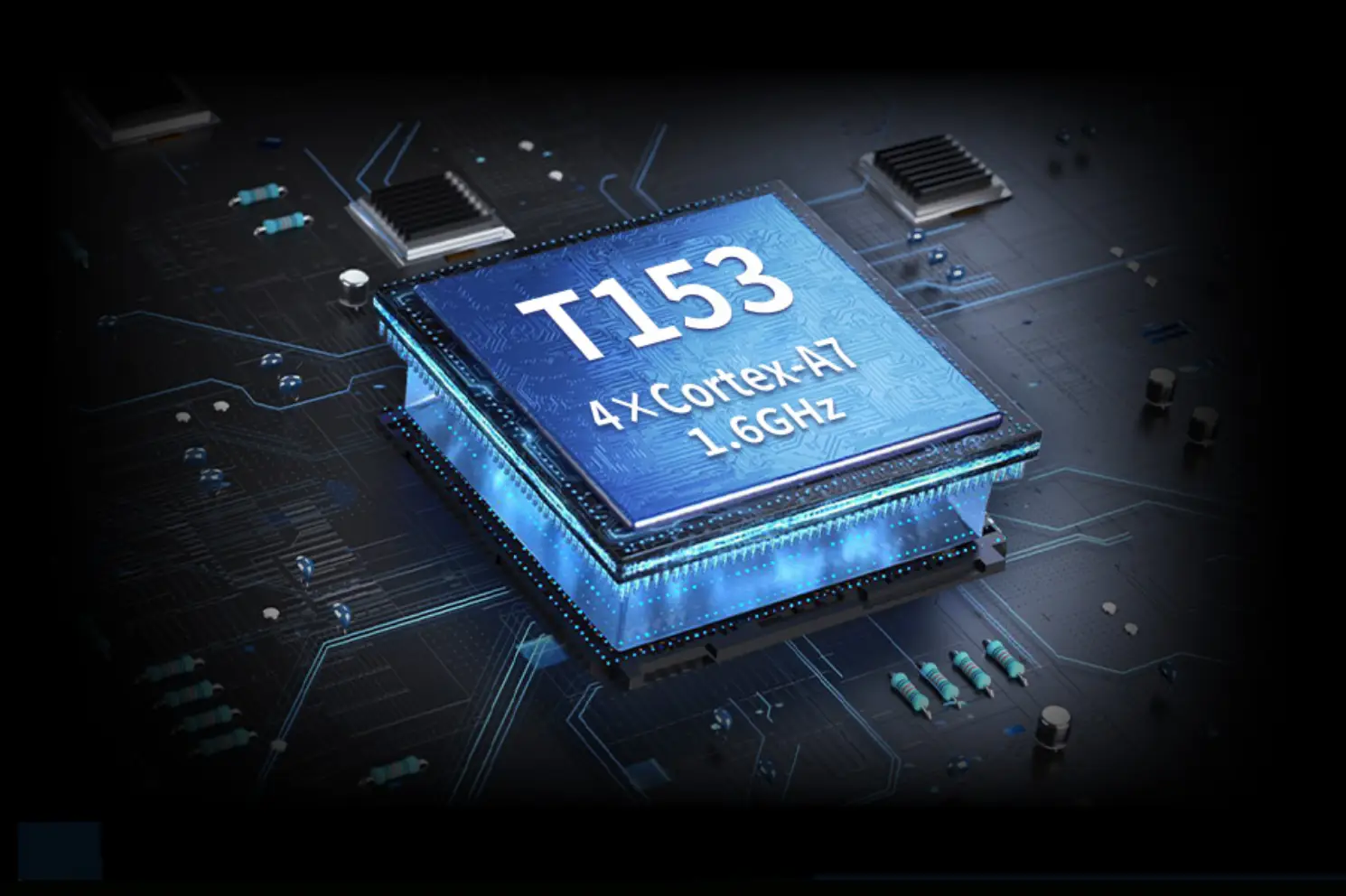

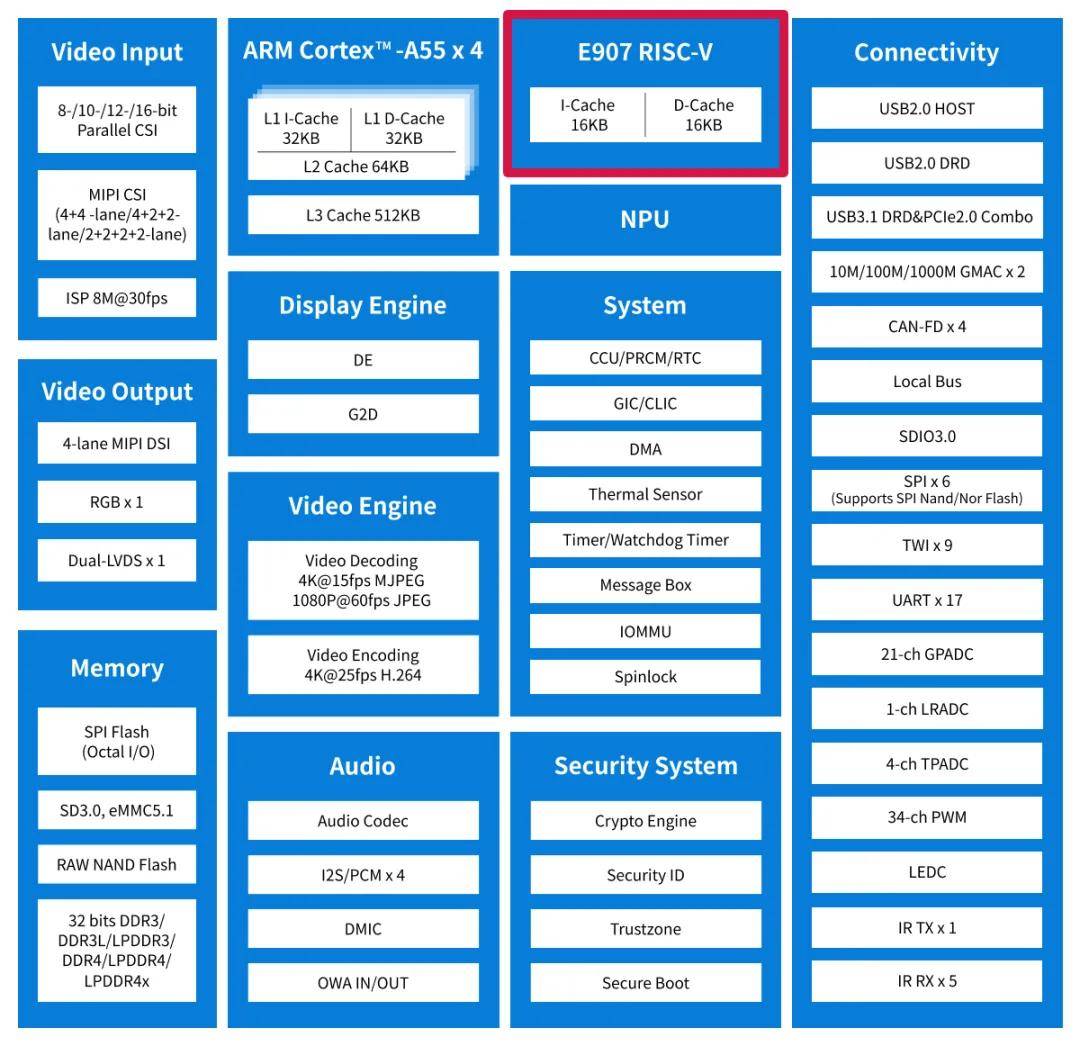

T153汇集了高性能4xCortex-A7、CPU主频1.6GHz、独立的RISC-VMCU、支持安全启动、国密算法IP、LocalBus等,赋能工业、电力等行业应用。

资源丰富

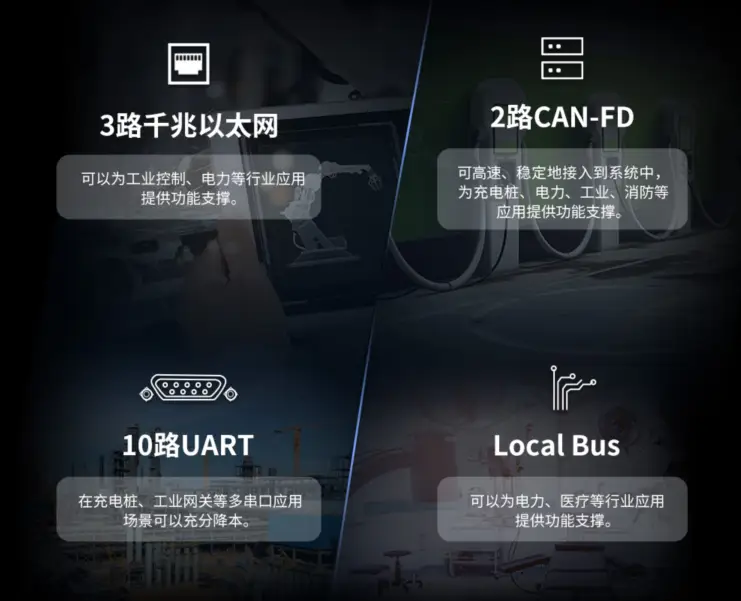

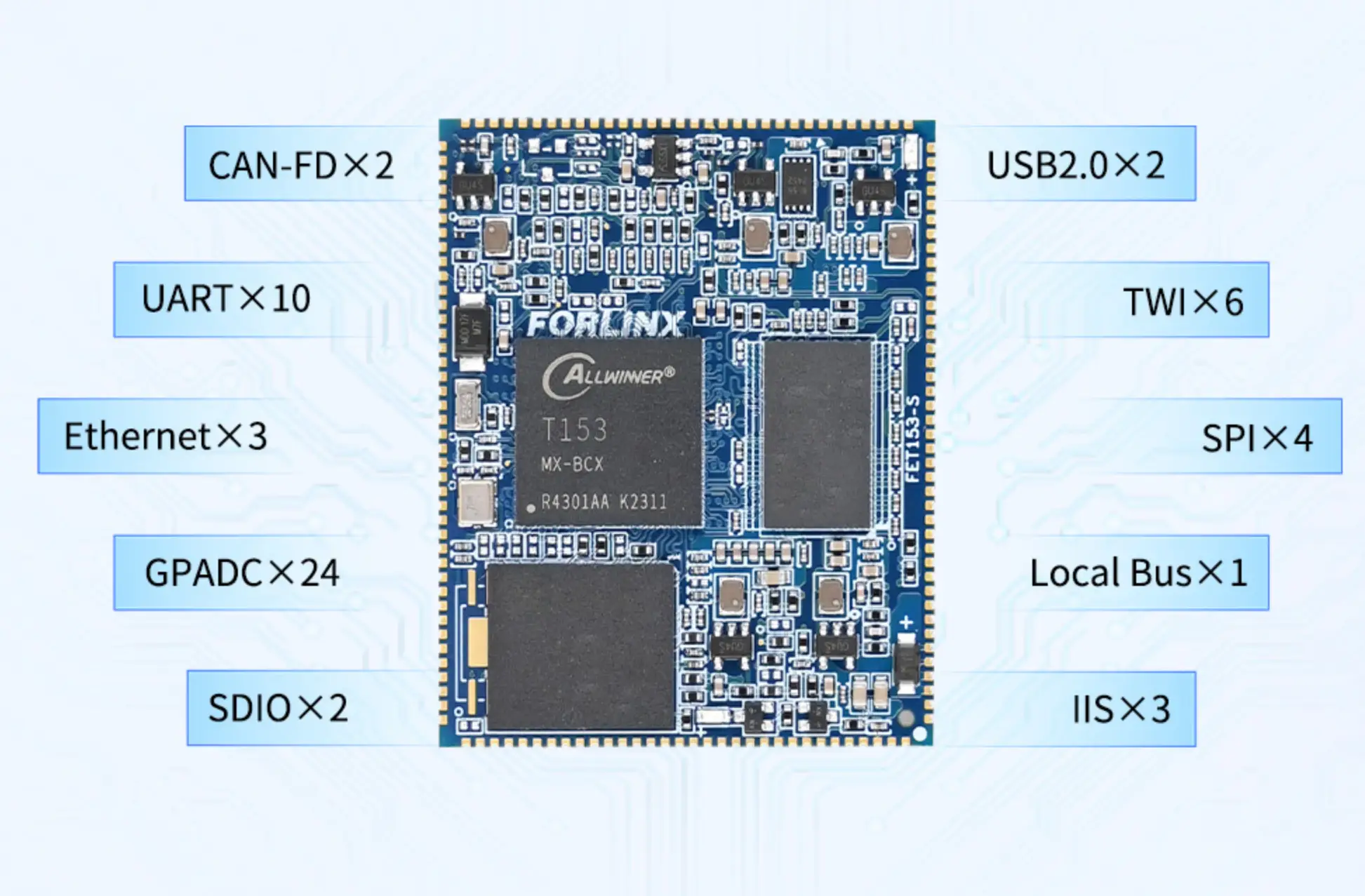

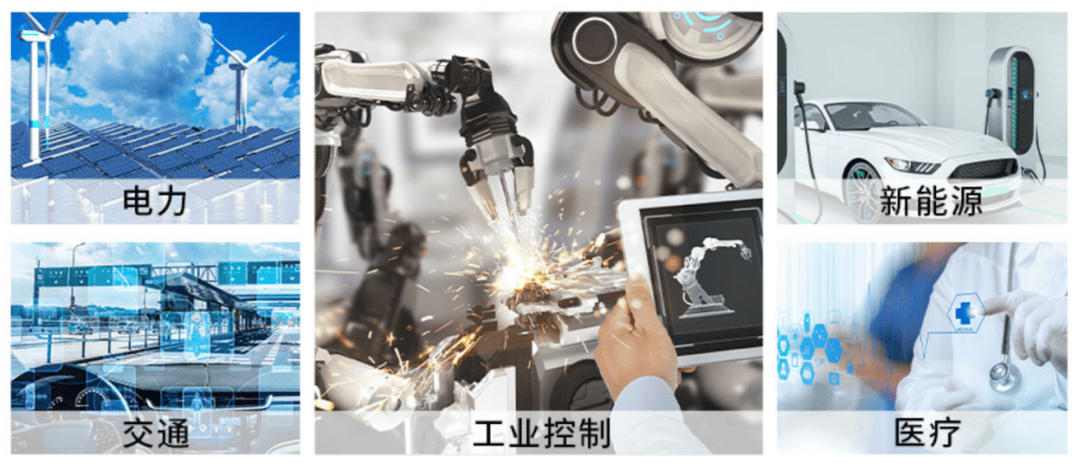

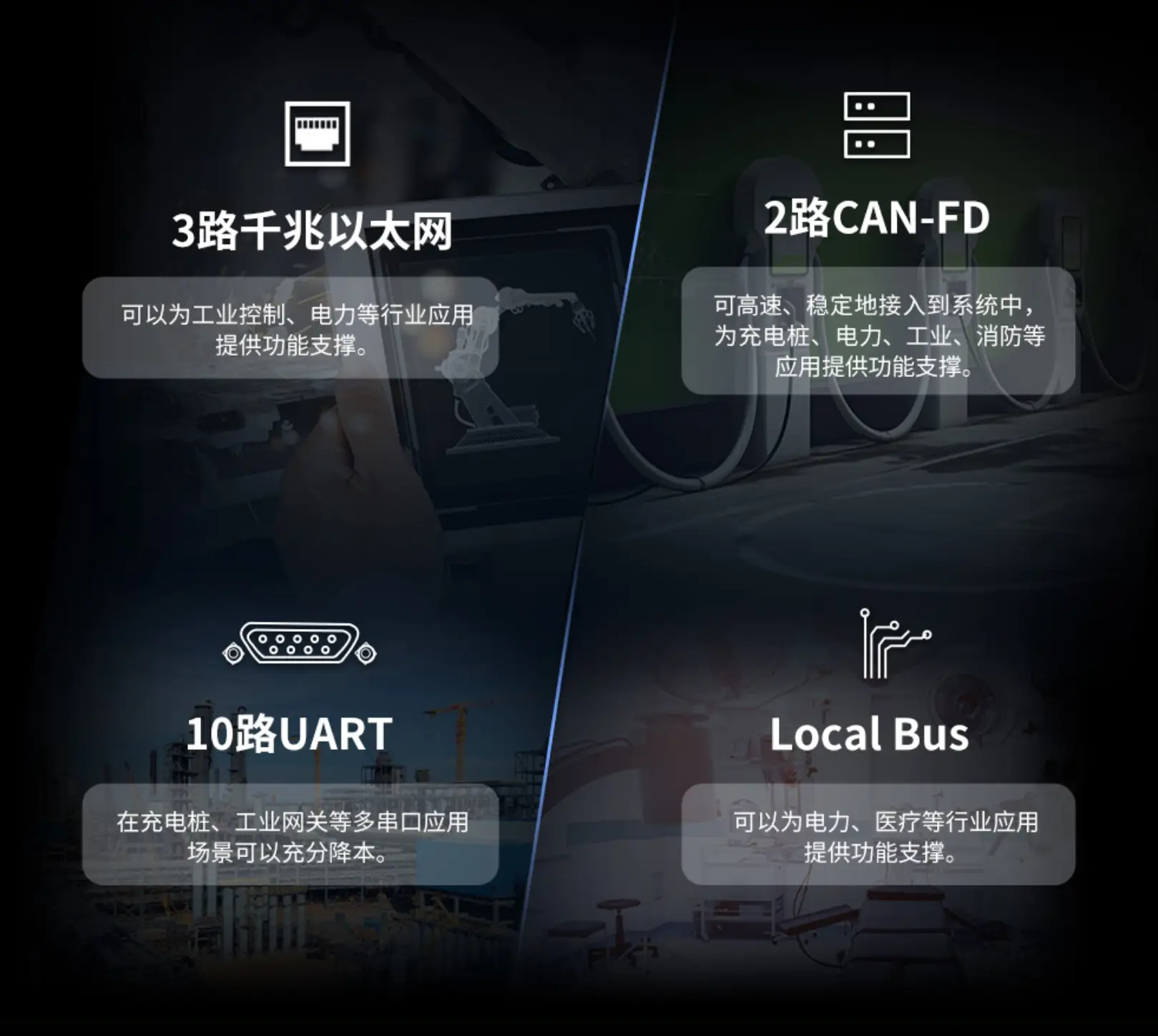

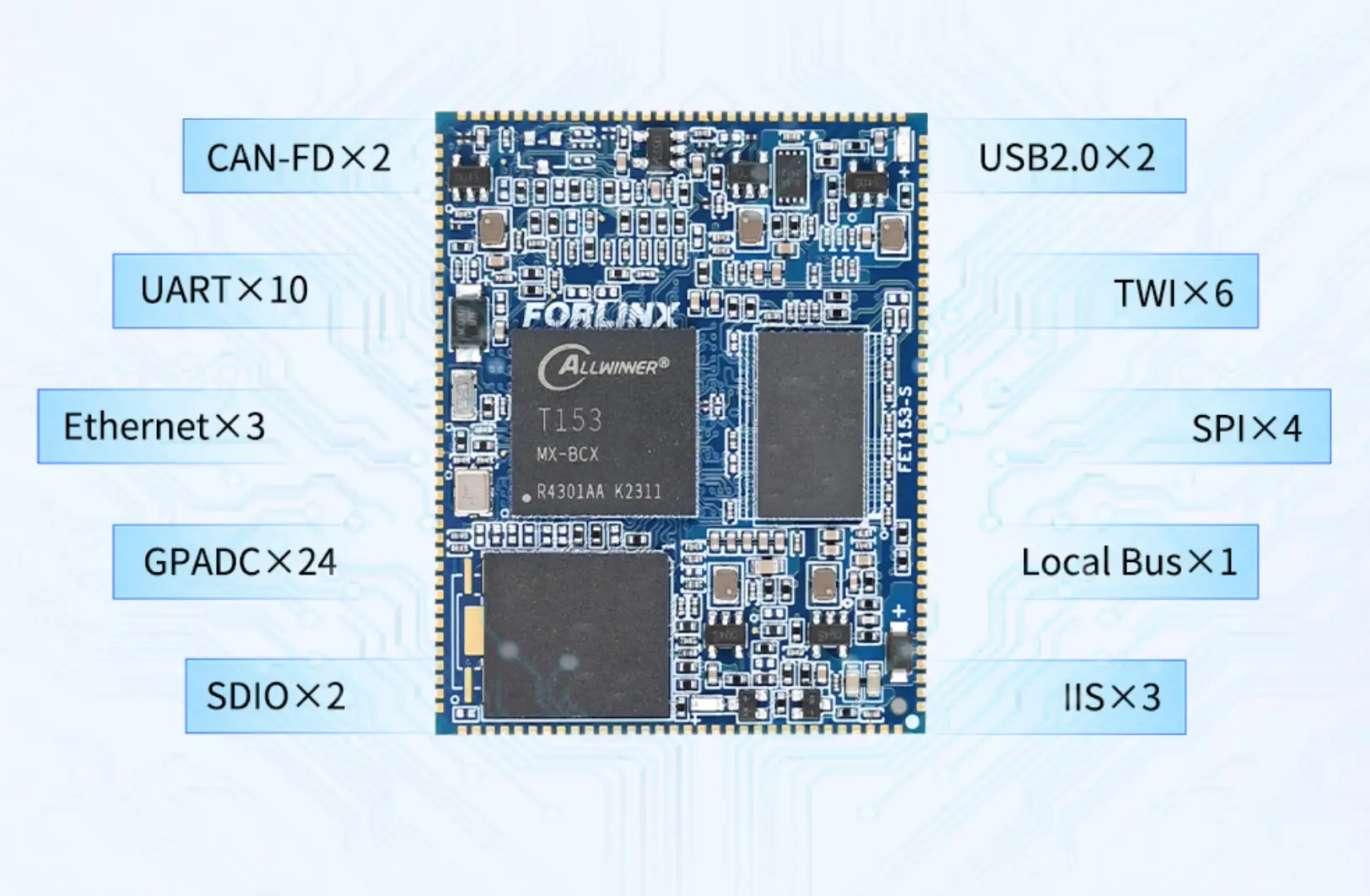

FET153-S核心板具备丰富的接口资料,可以满足工业控制、电力、新能源、交通、医疗等多个行业产品需求。

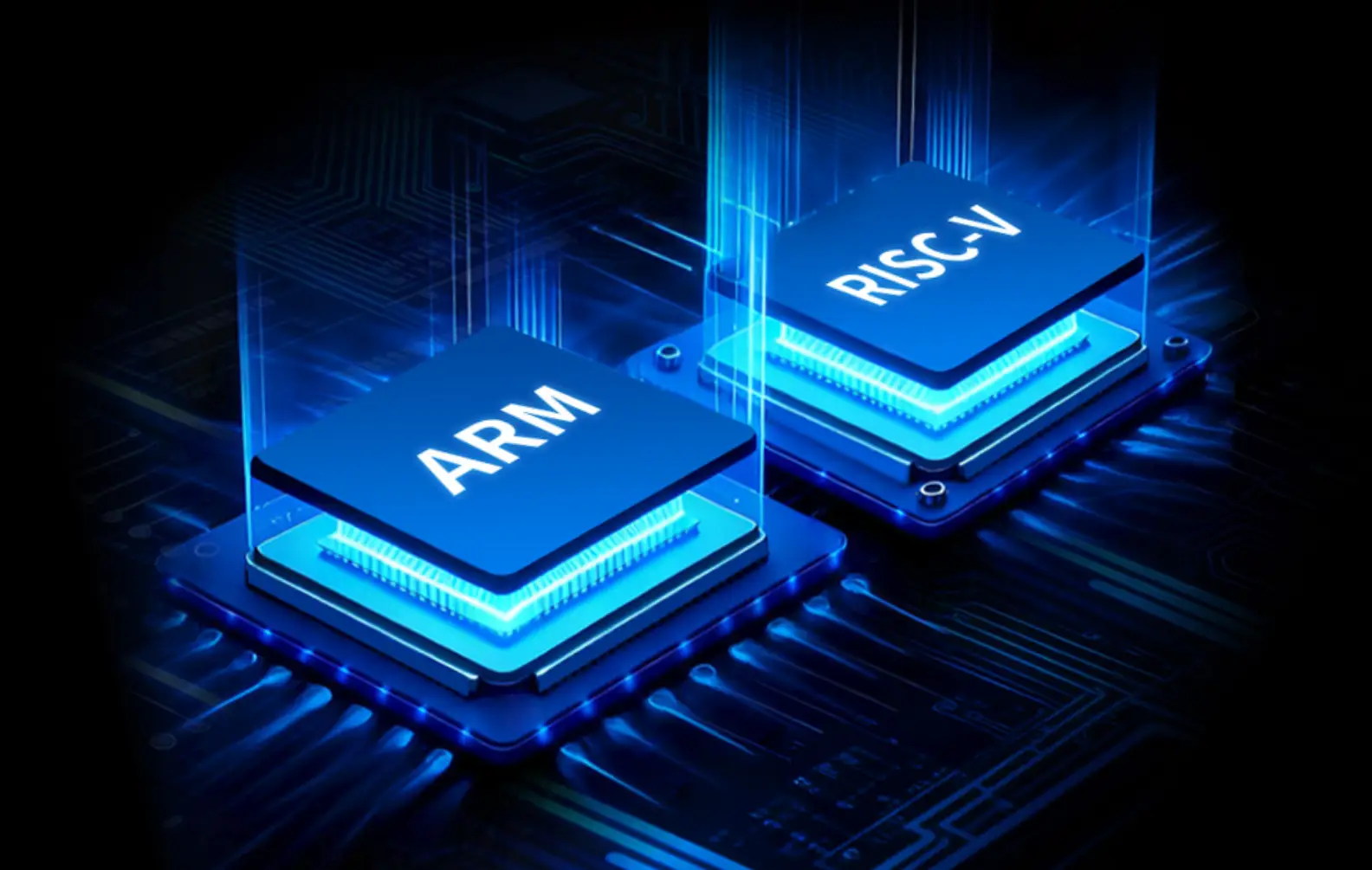

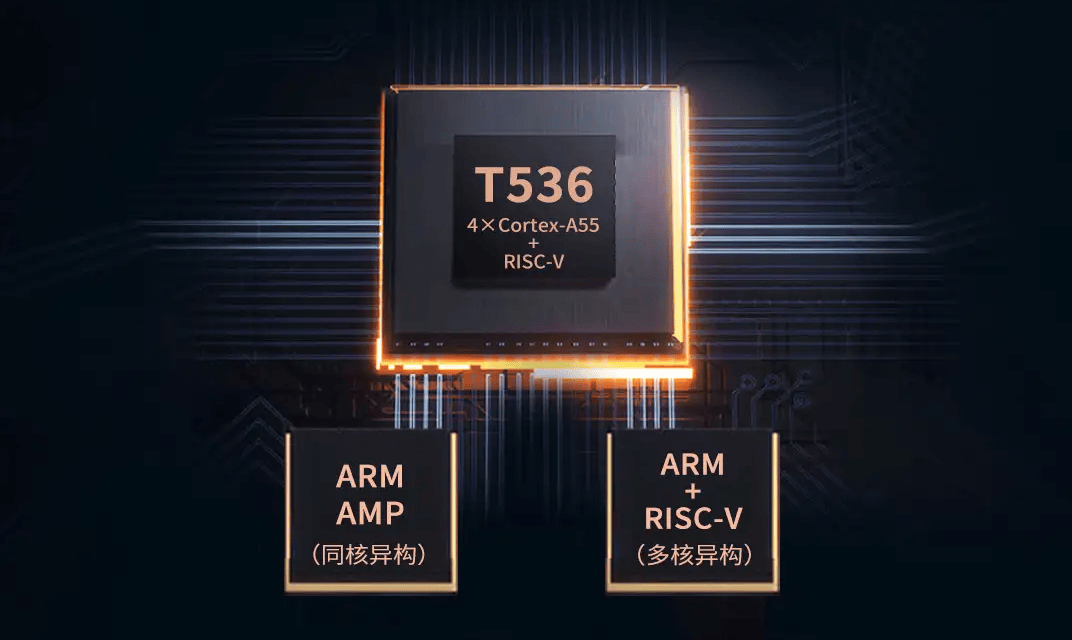

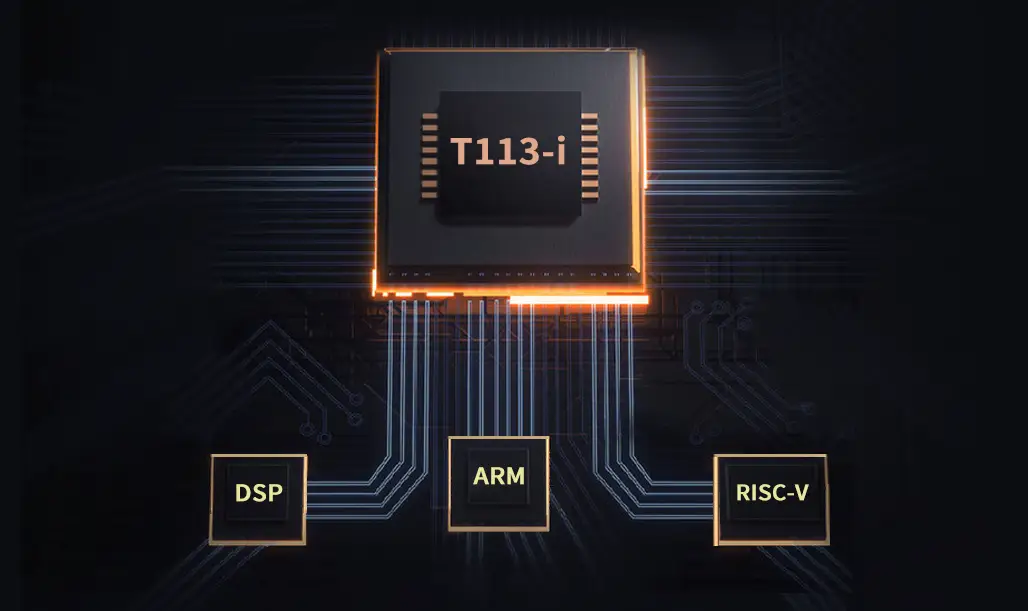

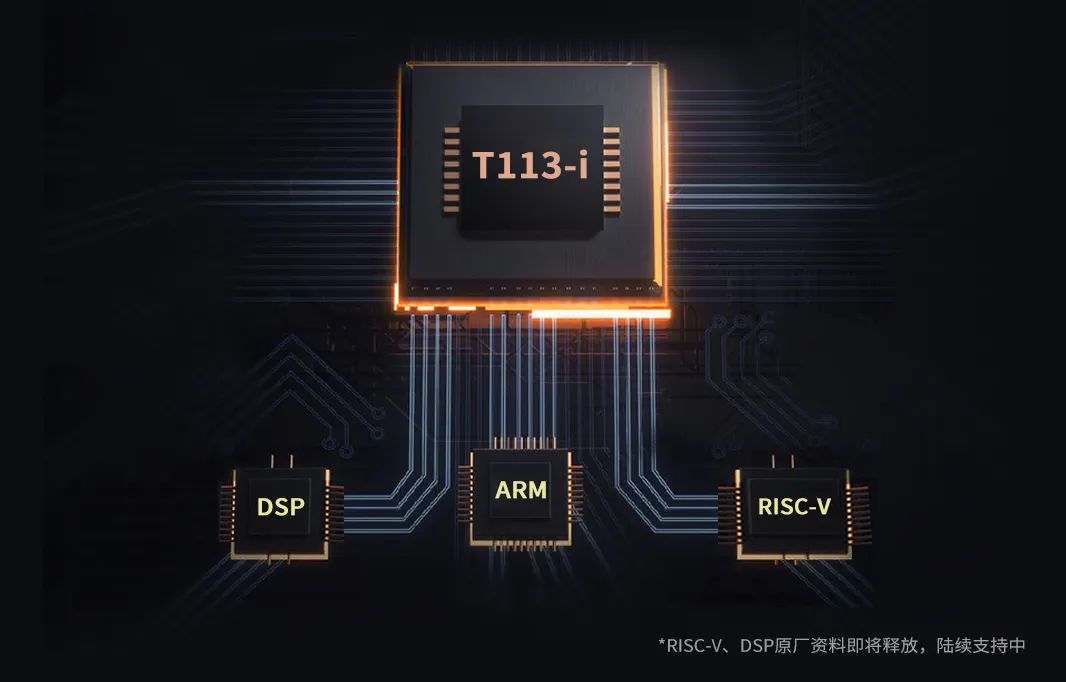

ARM+RISC-V,多核异构

T153集成四核Cortex-A7、64位玄铁E907 RISC-VMCU,以同时满足高效能与实时性控制的需求,四核Cortex-A7有强大的数据处理能力,而RISC-V核又可以匹配对实时性要求较高的应用场景。

核心板全功能引出

核心板将处理器全部功能引出,最大化释放T153潜能,为不同行业、不同产品的功能拓展提供充足硬件支持。

支持并行总线LocalBus

FET153-S核心板支持并行总线Local Bus 16bit/32bit,数据读写速率高,方便ARM和FPGA通讯。

安全特性

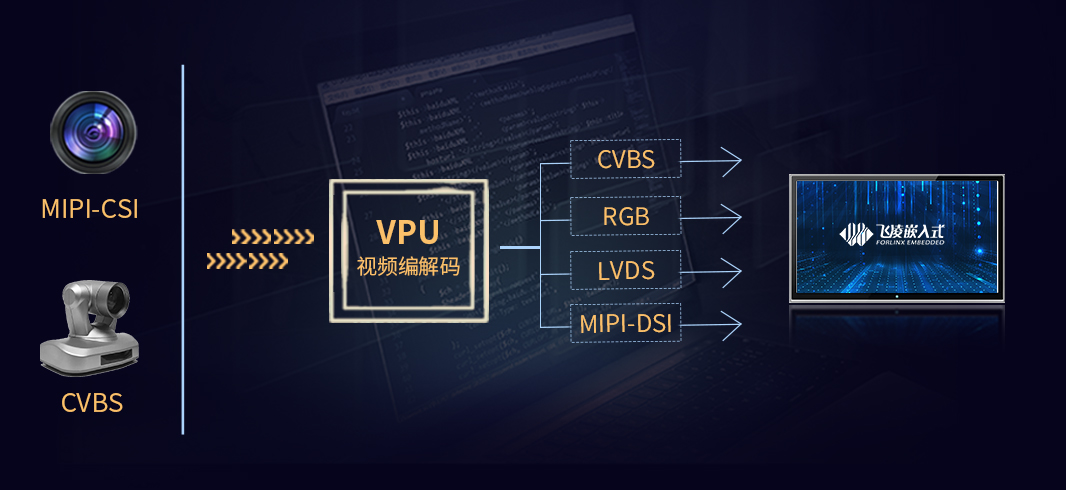

丰富的显示能力

FET153-S核心板多样的显示方式,支持RGB、LVDS、MIPI DSI显示。RGB分辨率可达1920X1080@60fps,LVDS分辨率可达1920X1080@60fps,MIPI DSI分辨率可达1920X1200@60fps。

ISP提升图像质量

T153支持4-lane/2-lane MIPI CSl,集成的ISP最大支持2路sensor,处理能力可达1M@30fps online、2M@30fps offline。

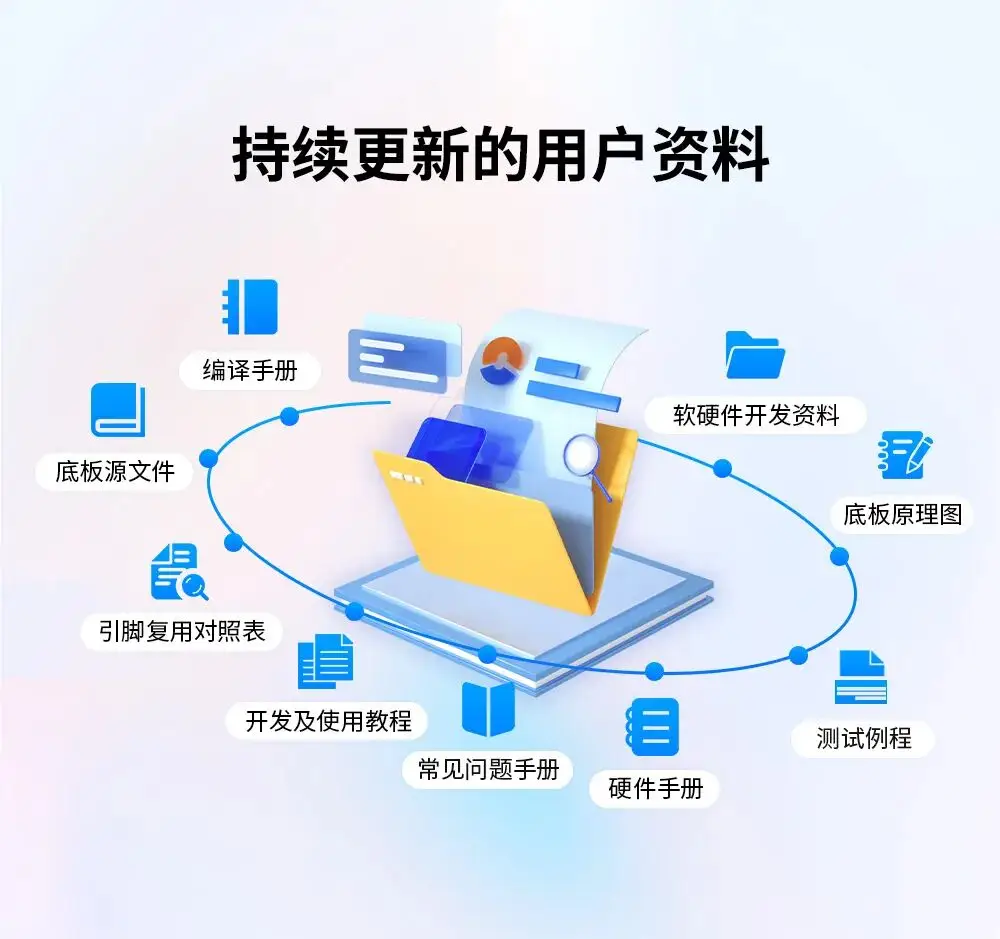

持续更新的用户资料

广泛的行业应用

FET153-S核心板物料100%国产化,核心板功能全面,在工业控制、电力、新能源、交通、医疗等多个行业,FET153-S核心板以其高性能、多接口、工业级等综合优势,加之飞凌嵌入式具备竞争力的价格优势及完备的售后技术支持,助力您的产品快速上市,走在行业前沿。

-

全志T153处理器ARM+RISC-V的双核CP有多强?发布在 飞凌嵌入式专区

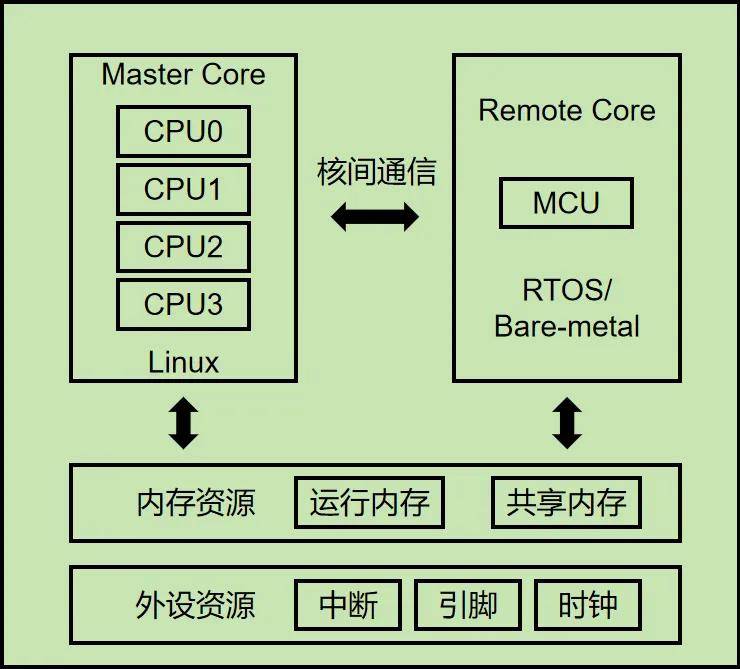

在嵌入式设备拼性能、拼响应、拼功耗的内卷时代,双核协作才是破局的关键。传统的对称多处理(SMP)架构已难以兼顾全场景需求,非对称多处理(AMP)异构架构正在成为行业主流,在这样的背景下,全志T153平台直接搬出ARM+RISC-V的“双核CP”:主打高性能计算的Cortex-A7核心运行Linux,聚焦高实时性任务的RISC-V E907核心运行RTOS,组成 “互补型搭档”。

本文会通过飞凌嵌入式OK153-S开发板,为大家实测这对双核CP的协作实力——依托异构核间通讯机制(IPC)与Suspend/Resume电源管理机制,全面验证A核与R核的协同工作能力,并验证异构多核环境下的数据交互效率与智能化唤醒逻辑。

1、休眠唤醒功能验证

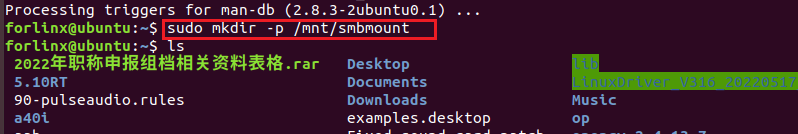

pm_test 节点可以用于测试Linux部分的休眠唤醒功能。设备冻结后,等待5s,即返回,执行唤醒动作。echodevices > /sys/power/pm_test设备进入休眠:

echomem > /sys/power/state执行以上命令后,设备5s后会被唤醒。

2、R核唤醒休眠的A核

“功耗管理”是产品续航与成本控制的核心竞争力。T153处理器的异构多核架构为此提供了的解决方案:A核休眠:ARM核在空闲时进入WFI深度睡眠,功耗降至最低;

R核值守:RISC-V核心持续运行,监听外部事件;

按需唤醒:当传感器触发、定时任务到达时,R核一键唤醒A核处理复杂任务。A核进入WFI模式,R核运行在DRAM上,R核唤醒A核。

首先设置主核休眠时,DRAM不进入自刷新,从核保持运行在DRAM上。可以通过linux控制台输入以下命令切换:

echo0>/sys/class/pm_msgbox/set_dram_refresh然后A核进入休眠状态:

echomem > /sys/power/state使用R核唤醒A核。我们的R核提供了cpux_resume接口来唤醒主核,在R核中执行以下命令进行A核唤醒:

cpux_resume在低功耗场景下,高性能的A核休眠待机,低功耗的R核持续值守。当外部事件触发时,R核可瞬间唤醒A核响应任务。这种 "小核值班、大核待命" 的架构,让设备在续航与实时响应之间达到平衡。

3、双核通讯验证

T153处理器采用ARM Cortex-A7+RISC-V 的多核异构架构,让系统兼具"大脑"与"小脑",而异构核间通讯机制(IPC)正是连接两个"脑"的高速通道,通过共享内存机制,双核之间可实现数据传输。以下是操作方法:测试之前首先使能R核:

echo amp_rv0.bin > /sys/class/remoteproc/remoteproc0/firmware echo start > /sys/class/remoteproc/remoteproc0/state(1)RISC-V端例程

rtos/lichee/rtos-components/aw/rpbuf/rpbuf_demo/rpbuf_test.c命令使用方法:

static void print_help_msg(void) { printf("\n"); printf("USAGE:\n"); printf(" rpbuf_test [OPTIONS]\n"); printf("OPTIONS:\n"); printf(" -h : print help message\n"); printf(" -c : create buffer\n"); printf(" -C : Send Cnt(default: 1)\n"); printf(" -d : destory buffer\n"); printf(" -s : send test messagese\n"); printf(" -l : list created buffers\n"); printf(" -a : sync transmit\n"); printf(" -I ID : specify controller ID (default: 0)\n"); printf(" -N NAME : specify buffer name (default: "%s")\n", RPBUF_BUFFER_NAME_DEFAULT); printf(" -L LENGTH : specify buffer length (default: %d bytes)\n", RPBUF_BUFFER_LENGTH_DEFAULT); printf(" -p : print performance data\n"); printf("\n"); printf("e.g.\n"); printf(" First, create a buffer (its name and length should match " "that of remote rpbuf buffer):\n"); printf(" rpbuf_buffer -N "xxx" -L LENGTH -c\n"); printf(" Then if remote sends data to it, the buffer callback will be called.\n"); printf("\n"); printf(" We can send test data to remote:\n"); printf(" rpbuf_test -d 100 -s -L 32\n"); printf("\n"); printf(" If this buffer is no longer in use, destroy it:\n"); printf(" rpbuf_test -N "xxx" -d\n"); printf("\n"); }参数解释:

-c 创建缓冲区

-C发送次数

-d销毁

-i 哪个节点

-a数据同步

-N名字

-L缓冲区大小(2)A核例程

命令使用方法:static void print_help_msg(void) { printf("\n"); printf("USAGE:\n"); printf(" rpbuf_test [OPTIONS]\n"); printf("\n"); printf("OPTIONS:\n"); printf(" -d time : set data sending interval (default: 100 ms)\n"); printf(" -s : send test messages\n"); printf(" -c : send count (default: 10)\n"); printf(" -r : receive messages\n"); printf(" -t time : specifies the time of receive messagess, unit:ms\n"); printf(" -a : sync transmit\n"); printf(" -I ID : specify rpbuf ctrl ID (default: 0)\n"); printf(" -N NAME : specify buffer name (default: "%s")\n", RPBUF_BUFFER_NAME_DEFAULT); printf(" -L LENGTH : specify buffer length (default: %d bytes)\n", RPBUF_BUFFER_LENGTH_DEFAULT); printf(" -p : print performance data\n"); printf("\n"); printf("e.g.\n"); printf(" rpbuf_test -L 0x1000 -c 10 -s : send 10 test data, size=0x1000\n"); printf(" rpbuf_test -L 0x1000 -r : receive test data forever, size=0x1000\n"); printf(" rpbuf_test -L 0x1000 -r -t 1000 : receive test data 1 second, size=0x1000\n"); printf("\n"); }参数解释:

-s发送

-c发送次数

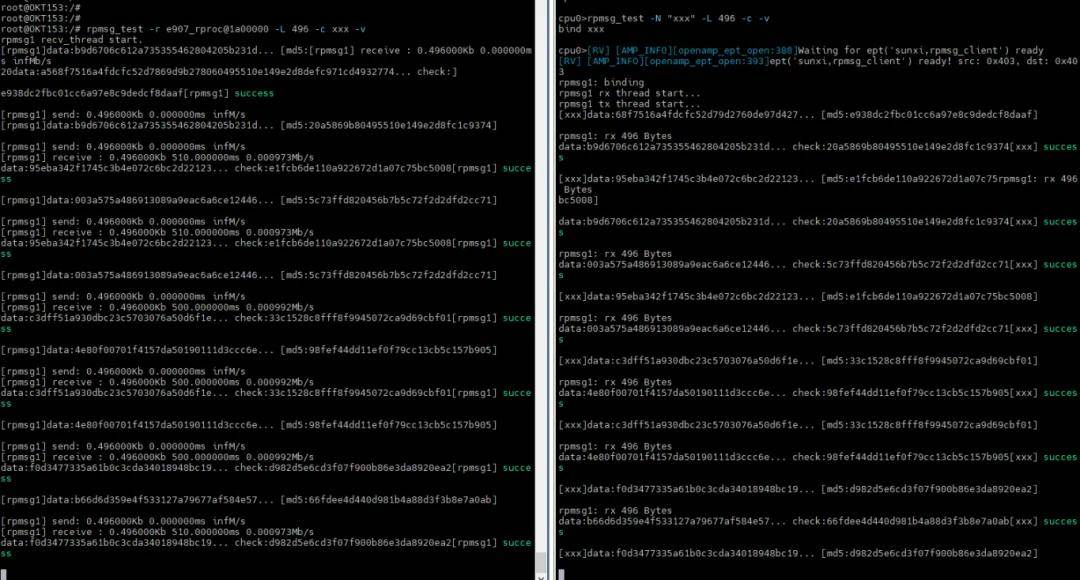

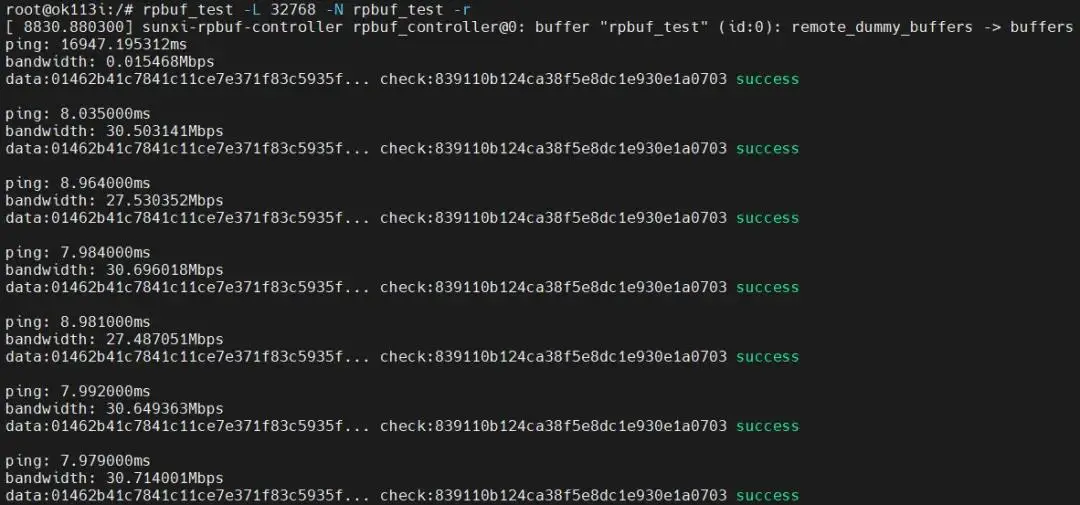

-r阻塞接收(3)实验现象

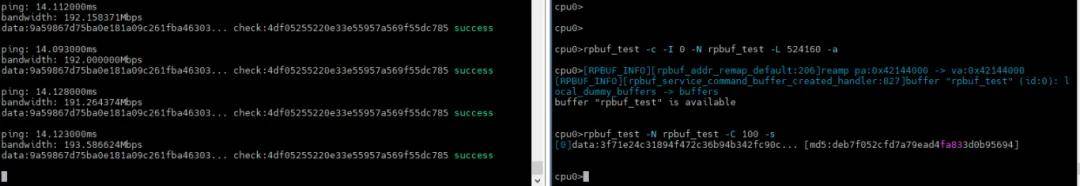

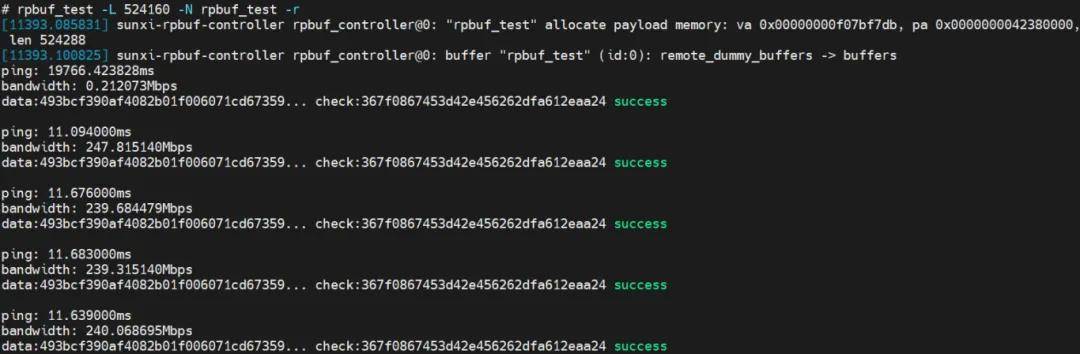

以RISC-V向A核发送数据为例,缓冲区大小为511.875K,发送100次;

开辟一个511.875K的缓冲区,A核向RISC-V发送一百次数据。

以下命令按次序执行:RISC-V命令:rpbuf_test -c -I 0 -N rpbuf_test -L 524160 -a

A端命令:rpbuf_test -L 524160 -N rpbuf_test -r

RISC-V命令:rpbuf_test -N rpbuf_test -C 100 -sRISC-V 串口:

cpu0>rpbuf_test -c -I 0 -N rpbuf_test -L 524160 -a cpu0>[RPBUF_INFO][rpbuf_addr_remap_default:206]reamp pa:0x42144000 -> va:0x42144000 [RPBUF_INFO][rpbuf_service_command_buffer_created_handler:827]buffer "rpbuf_test" (id:0): local_dummy_buffers -> buffers buffer "rpbuf_test" is available cpu0>rpbuf_test -N rpbuf_test -C 100 -s [0]data:21a94801873e262b487f31000da27543... [md5:fd0f42ddde63121837ebcdec775250b9]A核串口:

root@OKT153:/# rpbuf_test -L 524160 -N rpbuf_test -r ping: 8099.576172ms bandwidth: 0.517149Mbps data:21a94801873e262b487f31000da27543... check:fd0f42ddde63121837ebcdec775250b9 success ping: 14.155000ms bandwidth: 186.086807Mbps data:21a94801873e262b487f31000da27543... check:fd0f42ddde63121837ebcdec775250b9 success ping: 14.721000ms bandwidth: 181.881592Mbps data:21a94801873e262b487f31000da27543... check:fd0f42ddde63121837ebcdec775250b9 success ping: 14.694000ms bandwidth: 181.992096Mbps data:21a94801873e262b487f31000da27543... check:fd0f42ddde63121837ebcdec775250b9 success ping: 14.680000ms bandwidth: 182.055313Mbps data:21a94801873e262b487f31000da27543... check:fd0f42ddde63121837ebcdec775250b9 success ping: 14.712000ms bandwidth: 181.779083Mbps data:21a94801873e262b487f31000da27543... check:fd0f42ddde63121837ebcdec775250b9 success ping: 14.690000ms bandwidth: 182.276901Mbps data:21a94801873e262b487f31000da27543... check:fd0f42ddde63121837ebcdec775250b9 success测试数据显示,ARM与RISC-V双核间数据传输带宽平均可达184Mbps,验证了共享内存机制的高效与稳定。

4、结论

全志T153处理器通过异构多核架构、高效异构核间通讯机制(IPC)以及与之配套的智能休眠唤醒方案,可以实现ARM核与RISC-V核的高效协作——Linux负责复杂运算,RTOS保障实时响应,同时将“高性能计算”、“硬实时控制” 与 “超低功耗待机” 这三大关键能力融为一体,满足工业控制等场景需求。这远不止是技术功能的实现,更是为下一代智能硬件提供了一个量产化、功能完整、性能可靠的芯片级解决方案平台。 -

飞凌嵌入式启动LPDDR5升级战略,破局供应难题发布在 飞凌嵌入式专区

当前全球存储市场结构性调整持续深化,LPDDR4系列内存供需失衡问题愈发严峻,价格暴涨与供应缺口形成双重压力,给产业链上下游的稳定运营带来系统性挑战。在此背景下,内存等核心部件的供应稳定性已成为决定企业竞争力的关键变量,如何为客户筑牢供应防线、保障量产计划稳步推进,成为飞凌嵌入式当下最为关注的核心问题。

飞凌嵌入式深刻洞察内存供需的行业挑战,以前瞻性布局积极应对。现已完成对RK3588及RK3576系列核心板产品向LPDDR5内存升级的全面适配与验证,并且后续将把此项升级逐步拓展至更多平台。这一举措,彰显了飞凌嵌入式以供应链优势赋能客户发展的核心能力。

1、主动应对,化解供应风险

面对LPDDR4市场的结构性供需矛盾,被动应对无法从根本上保障客户项目的长期安全。飞凌嵌入式选择以主动升级作为战略支点,将产品平台提前迁移至技术更先进、产能规划更富前瞻性的LPDDR5轨道。这一决策源于飞凌嵌入式对产业趋势的深度研判,旨在帮助客户跳出当前供应链困境,获取更长远、更可靠的核心元器件支持,化被动为主动。

2、双重价值:技术领先与供应保障并举

此次升级为客户带来性能与供应链安全的双重收益:(1)技术层面,实现跃迁式提升

LPDDR5内存带来了更高的带宽与更优的能效比,充分释放了RK3588/RK3576等高端平台的澎湃性能,能够更好地满足人工智能、高性能计算及复杂多媒体处理等前沿应用对内存性能的苛刻要求,让客户的终端产品更具竞争力。(2)供应层面,构建体系化保障优势

飞凌嵌入式所倡导的供应稳定,根植于系统性的保障能力:①前瞻布局:飞凌嵌入式主动为现有产品适配LPDDR5,有效规避了LPDDR4系列内存可能面临的长期产能约束与价格不确定性。

②战略协同:飞凌嵌入式与多家存储原厂及渠道建立的深度战略合作,通过早期参与、联合规划等方式,为核心资源争取优先保障。

③体系管理:凭借从精准预测、库存优化到多源预备的成熟供应链管理体系,飞凌嵌入式确保交付的可预期性与可规划性,为客户项目的顺利推进提供坚实后盾。

3、成为客户更值得信赖的伙伴

在充满不确定性的市场环境中,飞凌嵌入式选择以确定性的技术升级与供应链布局,回应客户的需求。我们深信,真正的伙伴关系,在于风雨同舟时的切实担当,在于前瞻未来时的携手共进。选择飞凌嵌入式,就是选择了一个将“供应稳定”置于战略高度的合作伙伴。未来,我们将持续强化供应保障体系,以更创新的产品、更可靠的交付、更紧密的协同,助力每一位客户精准把握市场机遇,行稳致远,共赢未来。

-

【玩转多核异构】T153核心板RISC-V核的实时性应用解析发布在 飞凌嵌入式专区

在智能硬件功能持续升级的当下,传统单片机以及传统的MPU都面临着“力不从心”的困境——多网络协同、多串口并发、多通道无线通信等复杂需求,以及文件管理、数据加密、人机交互、数据压缩等增强功能,单核方案已难以全面承载。

在这样的背景下,“管理核+实时核”的双核异构架构的方案逐渐脱颖而出,成为破局关键。因此,选择一款集成度高、通信效率优、成本可控的多核异构主控平台,就成为破解当前困局的更优答案。

1、FET153-S核心板

飞凌嵌入式FET153-S核心板基于全志T153处理器设计,面向工业与电力应用。该处理器集成四核Cortex-A7与一颗独立64位玄铁E907 RISC-V MCU,具备丰富的接口资源与工业级可靠性,完美契合现代FTU对处理性能与实时性的双重需求。此外,T153处理器还提供10路UART、24路GPADC、6路TWI接口、30路PWM等接口,这些接口为多样化应用提供灵活性。

01、实时方案: AP+MCU系统架构

飞凌嵌入式FET153-S核心板支持AP+MCU模式的实时方案。AP+MCU系统架构为Linux+MCU RTOS/Bare-metal。运行LinuxAP处理器核心作为主核(Master Core);运行RTOS/Bare-metal的MCU处理器核心作为从核(Remote Core)。主核负责整个多核异构系统中共享资源的划分和管理,并运行主站服务程序。

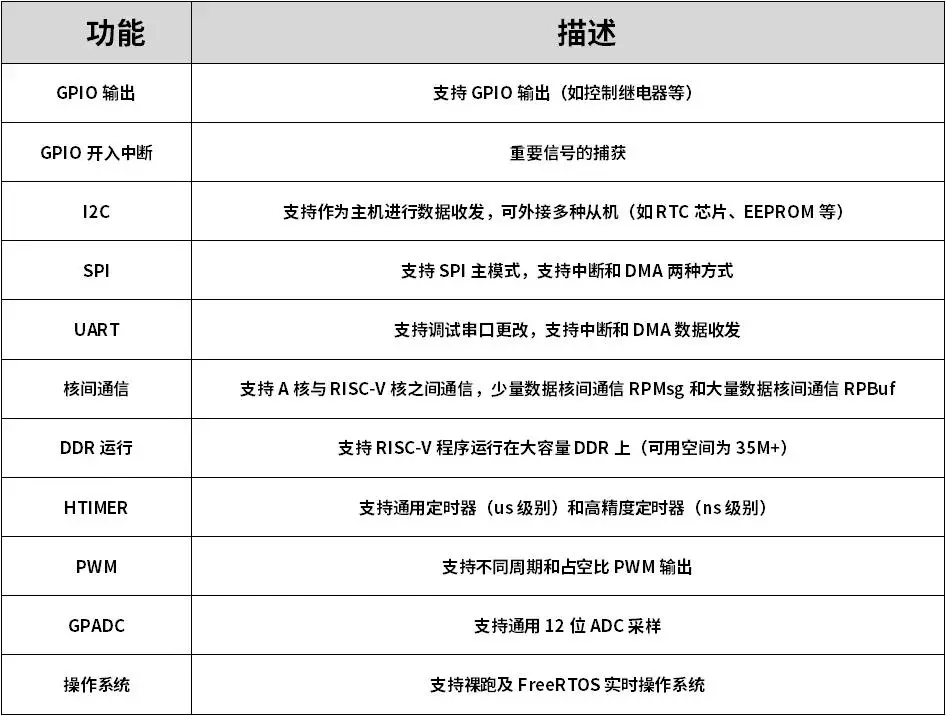

02、RISC-V核的接口资源

注:上表中功能均已测试通过。

2、应用实例

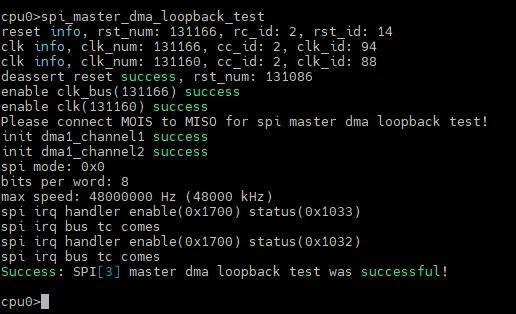

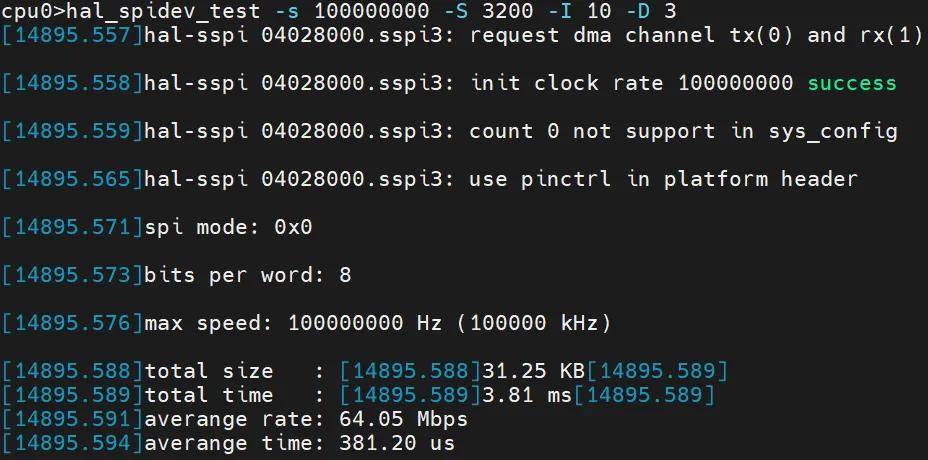

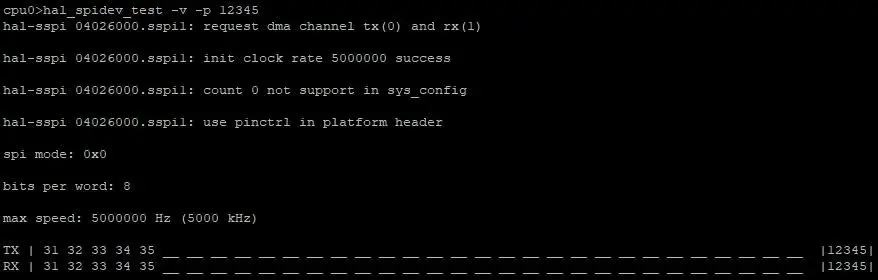

01、SPI数据收发

① 功能介绍

本案例为SPI外回环测试,即将SPI的MOSI和MISO两个引脚短接进行数据收发。

② 效果展现

传输效果:

AD采样芯片采用两线制串行总线接口进行数据传输,其标称典型通信速率可达20MHz级别。该两线制串行总线在电气特性和时序规范上与标准SPI接口高度契合,支持主从模式下的全双工同步通信板载SPI控制器支持最高通信速率达50MHz,SPI硬件控制器能够精确生成满足AD芯片建立时间和保持时间要求的时钟信号,确保数据传输的可靠性。

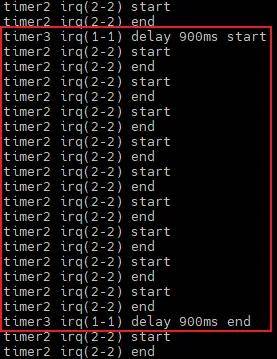

02、中断嵌套

本案例采用两个定时器进行测试。① 功能介绍

② 效果展现

测试方法:配置两个不同优先级的定时器,低优先级定时器(timer3)定时1s,回调中延迟900ms,以此达到延迟退出中断的时间。高优先级定时器(timer2)定时100ms,中断回调中不加延时。注意:在RISC-V核中,中断优先级为数字越大,优先级越高。

现象如下:在低优先级中断中,被高优先级的中断打断,并且执行完高优先级中断后程序回到低优先级中断中继续执行。

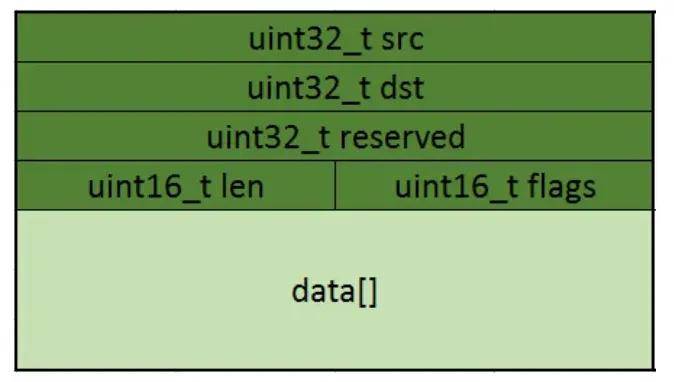

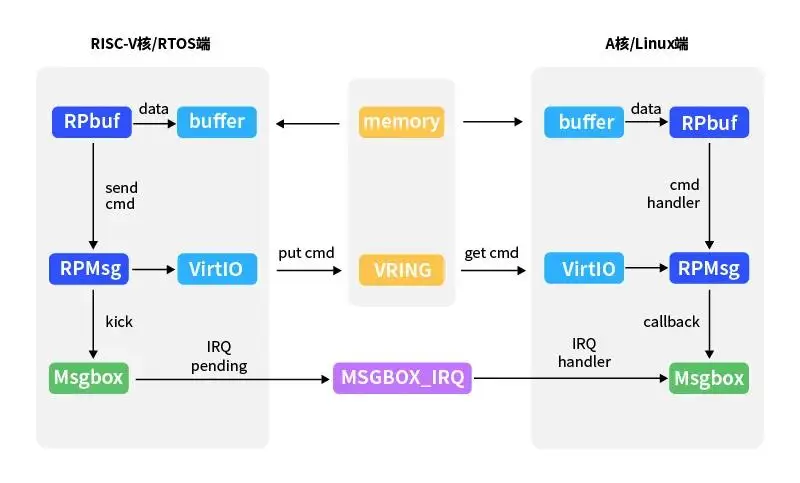

03、核间通信RPMgs

① 标准框架RPMsg是一种基于Virtio的消息总线,构建于Virtio框架之上,用于实现处理器间的消息传递。每个RPMsg通道包含本地源地址和远程目标地址,消息可在两者之间传输。

Virtio提供了共享内存管理与虚拟设备支持,其核心是成对的vring(环形缓冲区),分别用于发送和接收消息。这两个vring共同构成一个环形队列,vring缓冲区即为处理器间的共享内存区域。当共享内存中有新消息到达时,mailbox框架会通知相应处理器进行接收处理。

② 通信流程

在RPMsg中,只有在主处理器发送第一条消息以后,双核之间才可以进行核间通信,才可以互发数据。因此,当创建debugfs节点后,主处理器在 rpmsg_test_probe() 函数中调用 rpmsg_send() 函数主动向远端处理器发送第一条信息:

在DSP端调用rpmsg_test_init() 接口,并创建rpmsg端点;

在主处理器的debugfs节点的write函数中先从用户层得到要传输的数据,并调用rpmsg_send()函数发送至DSP;

DSP在接收到数据之后,调用callback函数,将接收到数据显示出来;

DS中调用rpmsg_test_send()接口(内部真实调用rpmsg_send() 函数),发送数据至主处理器;

在主处理器接收到数据之后,callback回调会调用 rpmsg_test_cb()函数,将接收到的数据显示出来,完成 CPUX→DSP、DSP→CPUX通信的完整回路。

RPMsg每次发送的最大数据长度为512Bytes,由于RPMsg还带有16Bytes的数据头,因此一次性传输的最大数据量为496Bytes。

③ 通信流程

普通传输:乒乓示例

大数据传输:

在实际应用中,原始RPMsg框架在通信传输方面存在一定的局限性,主要表现为单次数据负载上限较低,默认仅为496字节。以传输1MB数据为例,需拆分为约2114次发送操作方可完成。每次数据传输需触发两次中断,累计中断次数高达4228次,频繁的中断处理引入了显著的性能开销。同时,实测单次传输496字节耗时约1.05毫秒,综合上述因素,完成1MB数据的传输总耗时约为2.2秒,该传输效率在当前应用场景下难以满足用户对实时性与吞吐量的要求。全志科技在RPMsg基础上增加了RPBuf大数据传输的框架,如下图所示。

以上就是小编为大家带来的飞凌嵌入式FET153-S核心板RISC-V的使用方法。它的异构多核架构展现出了卓越的通信性能,能够为诸多应用提供高效可靠的核心支撑,特别适用于对实时性和稳定性要求极高的智能应用场景。

-

全志T153核心板:PLC的全国产主控新选择发布在 飞凌嵌入式专区

在工业4.0与智能制造浪潮下,可编程逻辑控制器(PLC)作为工业自动化的核心设备,正面临性能提升与高可靠性需求的多重挑战。飞凌嵌入式推出的FET153-S核心板,凭借全志T153工业级处理器的底层优势,通过多核异构计算、全场景接口覆盖、工业级可靠性设计等多重优势,为PLC设备提供了一套全新的国产化解决方案。

1、多核异构架构,破解PLC“实时控制与高效计算”的矛盾

传统PLC主控多采用单核架构,在处理复杂逻辑控制(如电机调速、传感器实时采集)与高吞吐量数据(如多网口通信、设备状态监测)时易出现算力瓶颈。飞凌嵌入式FET153-S核心板搭载的全志T153处理器采用4核Cortex-A7+独立RISC-V E907的多核异构架构,精准匹配PLC的双重需求:

4*Cortex-A7核心负责PLC的通信管理、数据存储与复杂算法运算,例如,在汽车制造的焊接生产线上,可处理来自多个焊接机器人的状态数据和上位机的指令,实现数据的实时解析与响应。

RISC-V E907核心专注实时控制任务,如PLC的毫秒/微秒级逻辑运算、高速I/O点位扫描与中断处理。在自动化装配线等场景中,能确保多个传感器与执行器之间的严格同步,避免因扫描周期延迟导致的生产节拍下降或产品加工错误。

2、全场景接口覆盖,适配PLC复杂工业互联需求

PLC作为工业现场的“神经中枢”,需连接传感器、执行器、人机界面(HMI)等多类设备。飞凌嵌入式FET153-S核心板通过邮票孔+LGA连接器引出CPU全部引脚,可以提供高带宽通信和灵活扩展接口的能力:工业网络组网:集成3路千兆以太网(支持RMII/RGMII)与2路CAN-FD(兼容CAN2.0A/B),无需外接扩展芯片即可实现“工业交换机级”组网。例如,在电力监控终端中,可同时连接智能电表、断路器与上位机。

传感器与执行器连接:提供24路12位GPADC、30路PWM与10路UART,可精准采集温度、压力等模拟信号,并驱动伺服电机、变频器等设备。在光伏逆变器场景中,GPADC可实时监测直流侧电压,PWM输出频率达0~24MHz或0~100MHz,确保MPPT算法的高效执行。

显示与交互支持:集成MIPI-DSI、LVDS及RGB接口,最高支持1920×1200@60fps分辨率显示,可适配工业触摸屏与HMI设备。同时,4-lane MIPI-CSI接口支持双路摄像头接入,为机器视觉检测提供硬件基础。

3、工业级可靠性,严苛、复杂环境稳定运行

工业现场环境恶劣,PLC需承受高低温、振动、电磁干扰等多重考验。FET153-S核心板通过以下设计确保长期稳定运行:严苛环境测试:通过飞凌嵌入式自建的标准实验室测试,涵盖:物理环境试验、电磁兼容试验、稳定性试验等。

长期供应保障:响应全志“工业芯片10年+生命周期”承诺,提供10~15年稳定供货,避免因芯片停产导致的设备迭代成本。

4、安全合规与高效开发,加速PLC项目落地

FET153-S核心板不仅提供硬件性能,更通过安全防护、软件生态与全维服务降低PLC开发门槛:安全合规:内置TrustZone与Secure Boot,防止固件篡改;集成国密算法IP(SM2/SM3/SM4),支持电力数据加密与金融工业终端敏感信息保护。

软件及资料:支持Linux 5.10,提供底板原理图、引脚复用表、测试例程等全套技术资料,开发者可快速完成驱动移植与应用程序开发。

5、总结:国产化PLC主控的标杆之选

FET153-S核心板以“多核算力+全接口+工业级可靠”的组合优势,为PLC设备提供了一套高性价比的国产化解决方案。其不仅满足工业现场对性能、连接与稳定性的严苛要求,更通过安全合规与开发支持,助力客户快速完成项目落地。在智能制造与自主可控的大趋势下,FET153-S核心板正成为工业PLC主控领域的标杆之选。 -

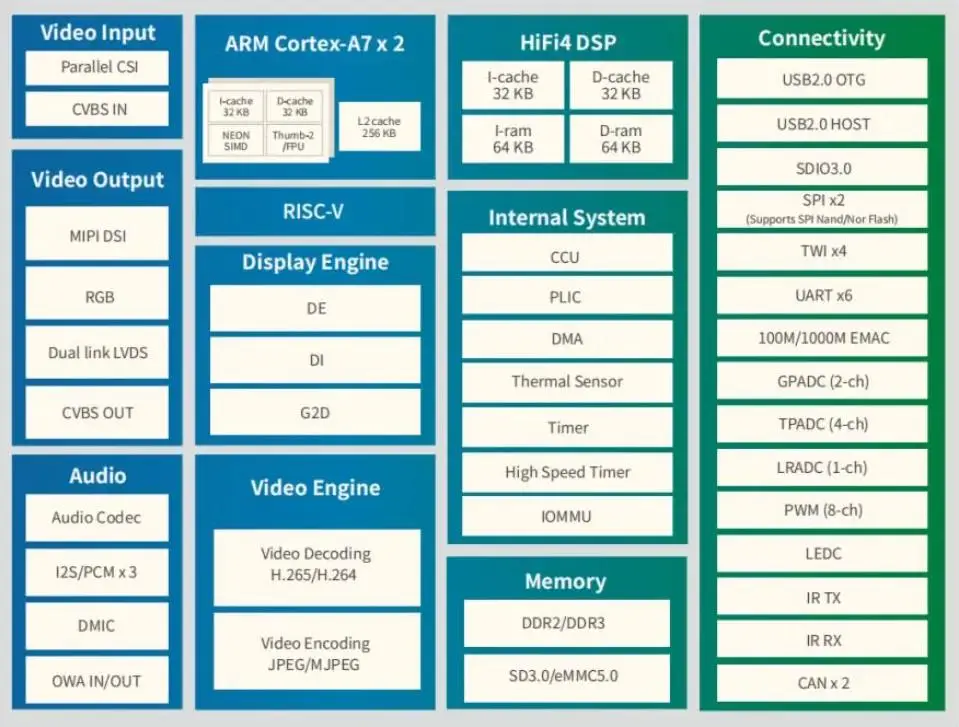

全志T153处理器详解:物超所值的工业芯发布在 飞凌嵌入式专区

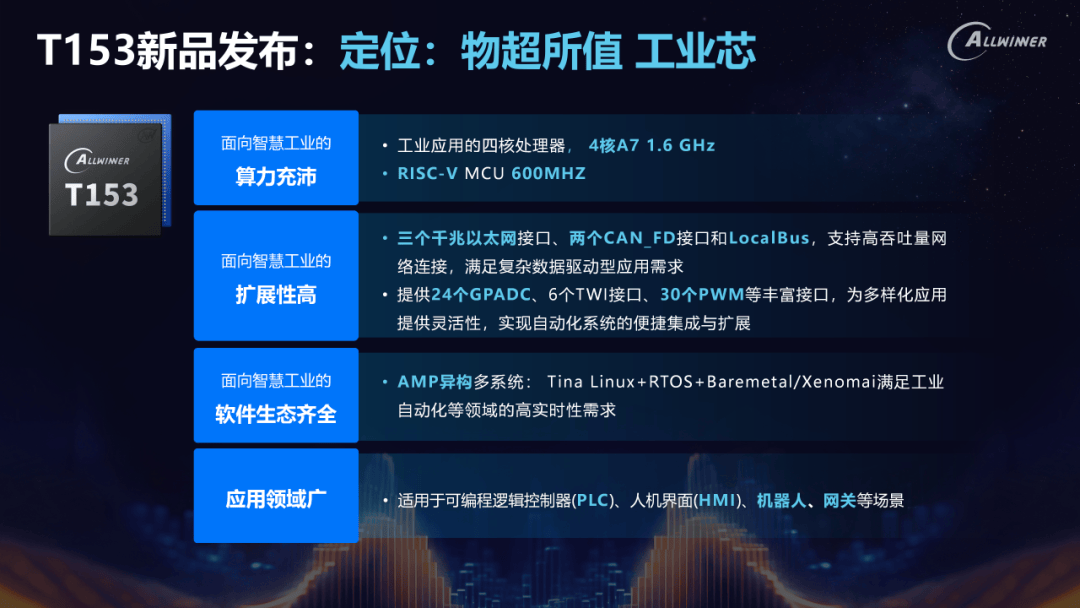

2025年9月24日,全志科技在上海成功举办“全志工业生态研讨会暨T153芯片发布会”,正式推出T153处理器。全志给T153的定位是“物超所值 工业芯”,旨在为智慧工业带来一款算力充沛、扩展性高、软件生态齐全、应用领域广泛的“智慧大脑”。

那么,T153是如何塑造这些优势的呢?本篇内容,就让我们走近这颗芯片,展开讲讲。

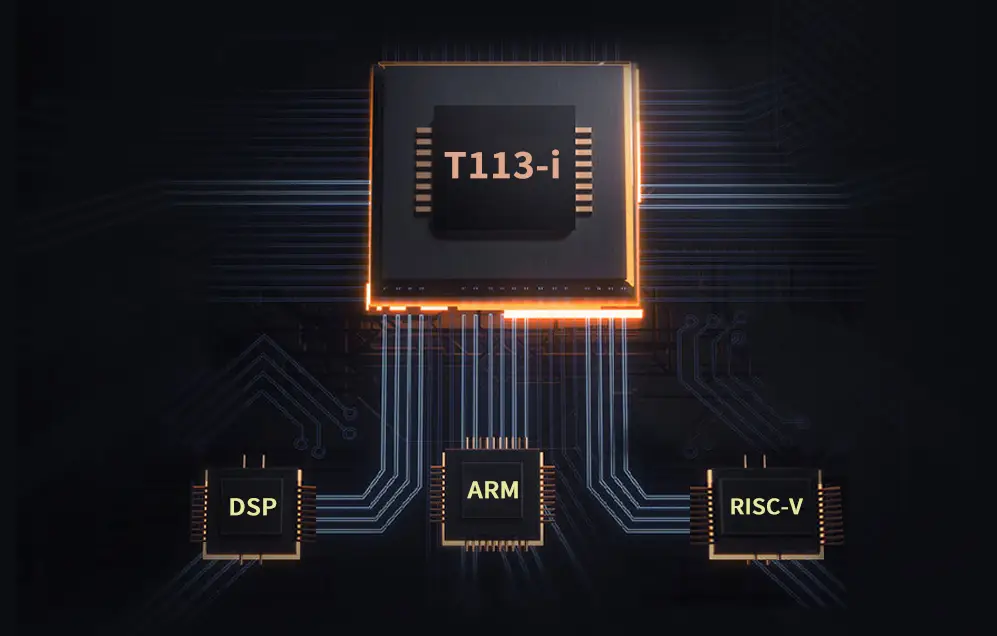

1.多核异构:高性能与实时性的平衡

全志T153处理器采用独特的多核异构设计,集成四核Arm Cortex-A7高性能CPU,主频高达1.6GHz,同时配备单核RISC-V 玄铁E907实时协处理器,主频达600MHz。这种架构巧妙地平衡了计算性能与实时控制需求,实现了鱼和熊掌的兼得:Cortex-A7核心:负责处理复杂的上层应用、数据通信和人机交互任务,提供强大的通用计算能力;

RISC-V E907核心:则专注于实时性要求高的控制任务,如电机控制、传感器数据采集和实时响应,显著降低主核负载。

与传统工业MCU/MPU相比,T153不仅提供了更强的计算能力,还通过异构架构实现了真正的高性能与实时性兼备,为现代工业自动化设备提供了更为理想的硬件平台。

2.丰富接口:满足多元化工业场景需求

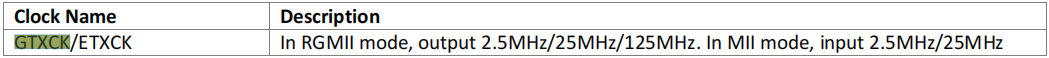

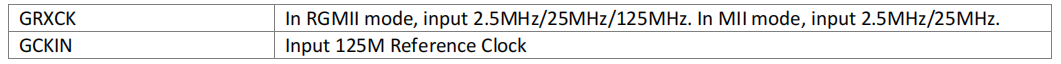

T153处理器在接口配置上充分考虑了工业应用的实际需求,提供了极为丰富的接口:(1)网络与工业总线接口

3路千兆以太网接口:支持多节点网络部署,满足工业设备对高吞吐量网络连接的需求;

2路CAN-FD接口:支持最高64字节数据传递,兼容CAN 2.0A/2.0B标准,适用于车载、电力等领域的高可靠性数据交互需求;

1路LocalBus并行总线:支持8/16/32位宽,最高接口速度:150MHz@16bits、100MHz@32bits,方便与FPGA等外设进行高速数据交换。

(2)通用外设接口10路UART串口:满足多串口设备连接需求;

30路PWM接口:支持多种电机控制和电源管理场景;

24路GPADC:12位采样分辨率,最大采样率1MHz,支持模拟信号采集;

6路TWI接口:兼容I2C标准,支持多种传感器连接;

4路SPI接口:最高100MHz时钟频率;

141路GPIO:提供充分的扩展能力。

这些接口为多样化应用提供灵活性,实现自动化系统的便捷集成与扩展。(3)显示与图像处理能力

T153集成了强大的图像处理与显示引擎,为工业人机界面(HMI)应用提供了良好的视觉体验:

显示接口:支持RGB、LVDS和MIPI-DSI三种显示接口(复用),最高分辨率可达1920×1200@60fps;

图像处理:集成ISP图像信号处理器,支持2路sensor输入,处理能力达1M@30fps online或2M@30fps offline;

图形加速:内置G2D图形加速单元,支持界面流畅渲染。3.工业级可靠设计,带来全面保障

T153处理器在参数设计上紧扣工业场景痛点,通过宽温、高集成度与安全机制,确保在恶劣环境下的稳定运行。宽温工作:支持-40℃~+85℃的工作温度范围,适应各种恶劣工业环境;

长生命周期:提供10-15年的持续供应保障,满足工业设备长服役周期需求,为工业客户的长期项目提供稳定保障;

安全特性:支持安全启动与国密算法IP,可满足IEC-60730 Class-B及PSA L1等工业安全认证要求。

4.软件生态与开发支持

在软件层面,T153支持AMP多核异构系统,可同时运行Tina Linux、RTOS和Baremetal等多种操作系统。这种灵活的软件架构使开发者能够根据实际需求分配任务,满足工业自动化等领域的高实时性需求,形成面向智慧工业的完整软件生态。全志科技还提供了完善的软件开发套件,助力客户快速产品化。此外,CODESYS、OneOS等软件生态合作伙伴还为其提供了工业操作系统和软件平台,形成了从芯片到系统的完整开发生态体系。

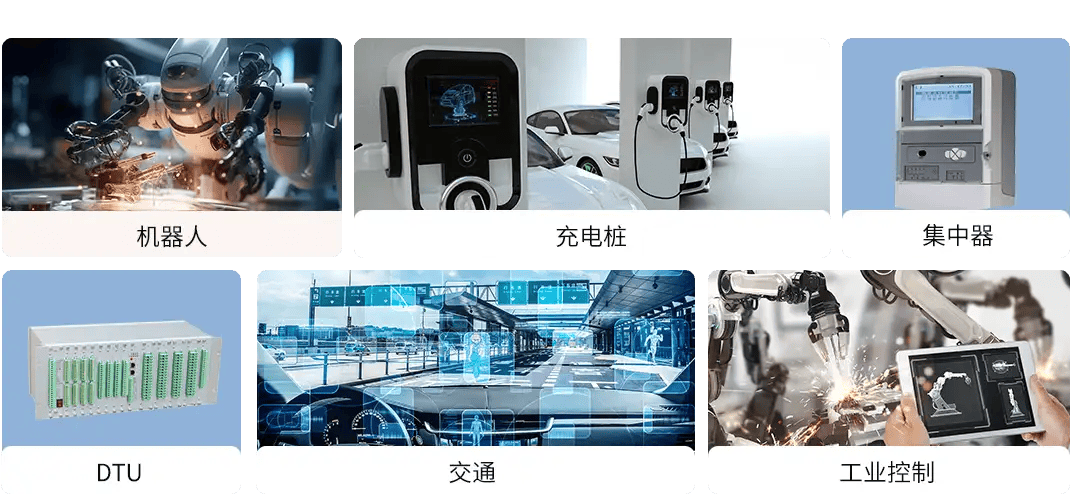

5.应用场景丰富,全面赋能智慧工业

T153处理器的多核异构架构与丰富接口,使其成为工业自动化、电力能源、机器人等领域的理想选择。这里简单列举几项应用。工业控制:

PLC(可编程逻辑控制器):Cortex-A7核心处理逻辑运算与数据通信,RISC-V核心实现实时I/O控制,提升设备响应速度;

电力行业:

电力监测终端:宽温设计与国密安全特性,适配变电站、分布式能源等户外场景,保障数据采集与传输的稳定性;

新能源:

光伏逆变器:通过CAN-FD接口监控光伏组件状态,PWM接口控制功率器件,实现最大功率点跟踪(MPPT);

充电桩:支持4G模块与支付系统对接,LocalBus接口连接计量模块,提升充电服务效率。

6.总结

全新T153芯片平台,集成高性能计算、实时控制、丰富接口与开放软件生态,从硬件底层夯实基础,为工业智能制造提供坚实支撑。随着工业4.0和智能制造的持续推进,T153有望在工业控制、电力能源、智能交通等领域发挥重要作用,为行业客户提供高性能、高可靠性且供应稳定的芯片解决方案,助力中国工业智能化升级!值得注意的是,飞凌嵌入式已正式发布基于T153的SoM方案——FET153-S核心板,为行业客户提供了快速实现产品化的便捷途径,显著缩短开发周期,加速产品上市。

-

【开发指南】全志系列核心板开发过程中的常见问题及排查策略发布在 飞凌嵌入式专区

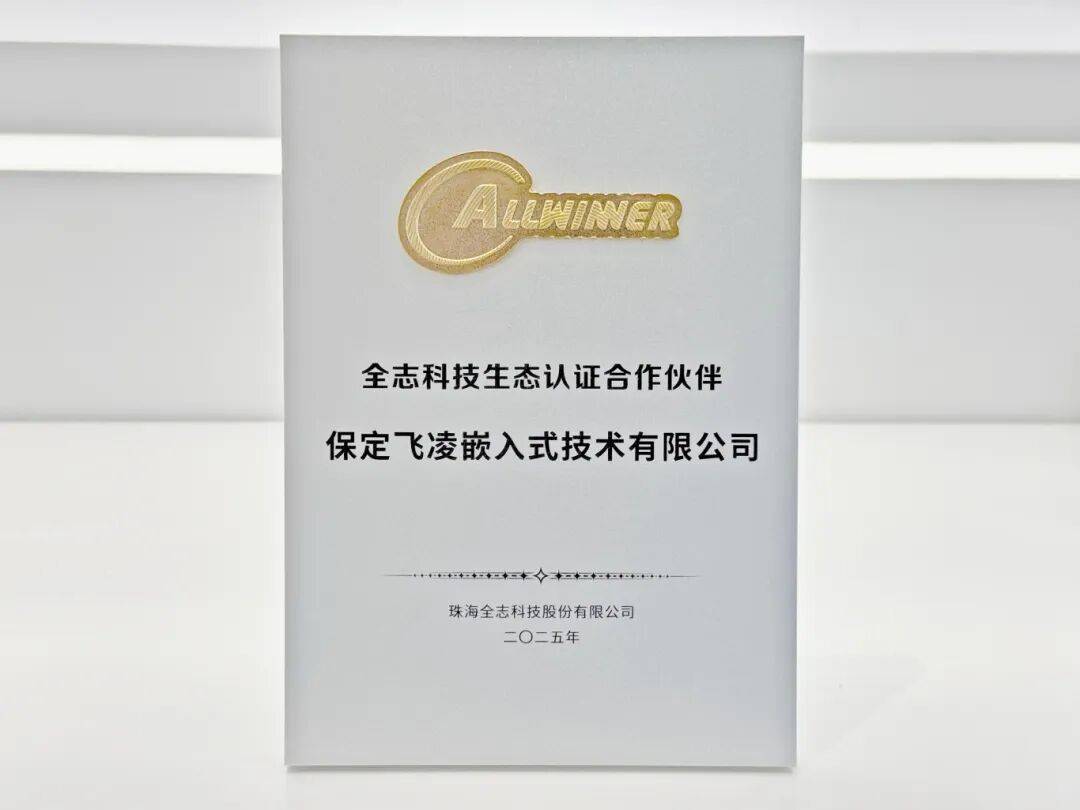

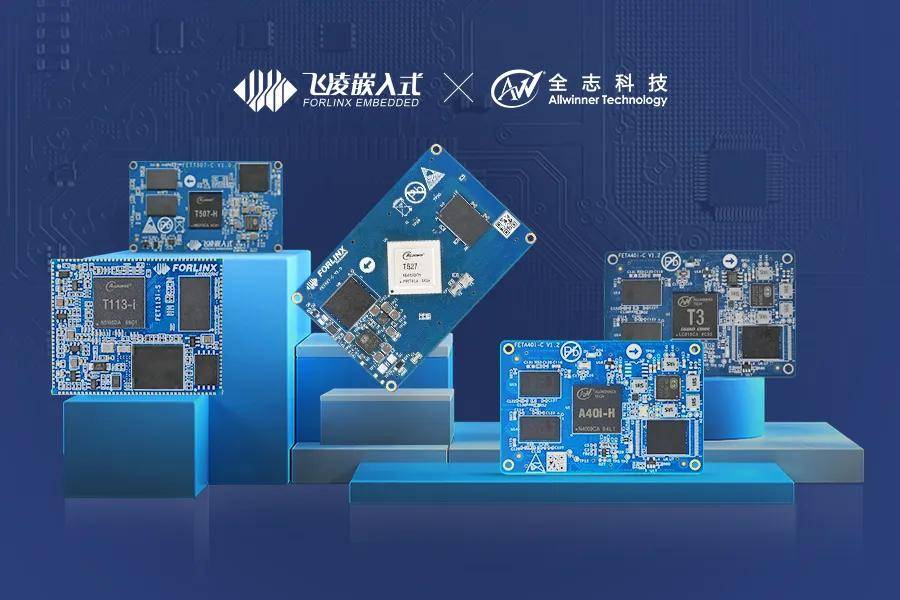

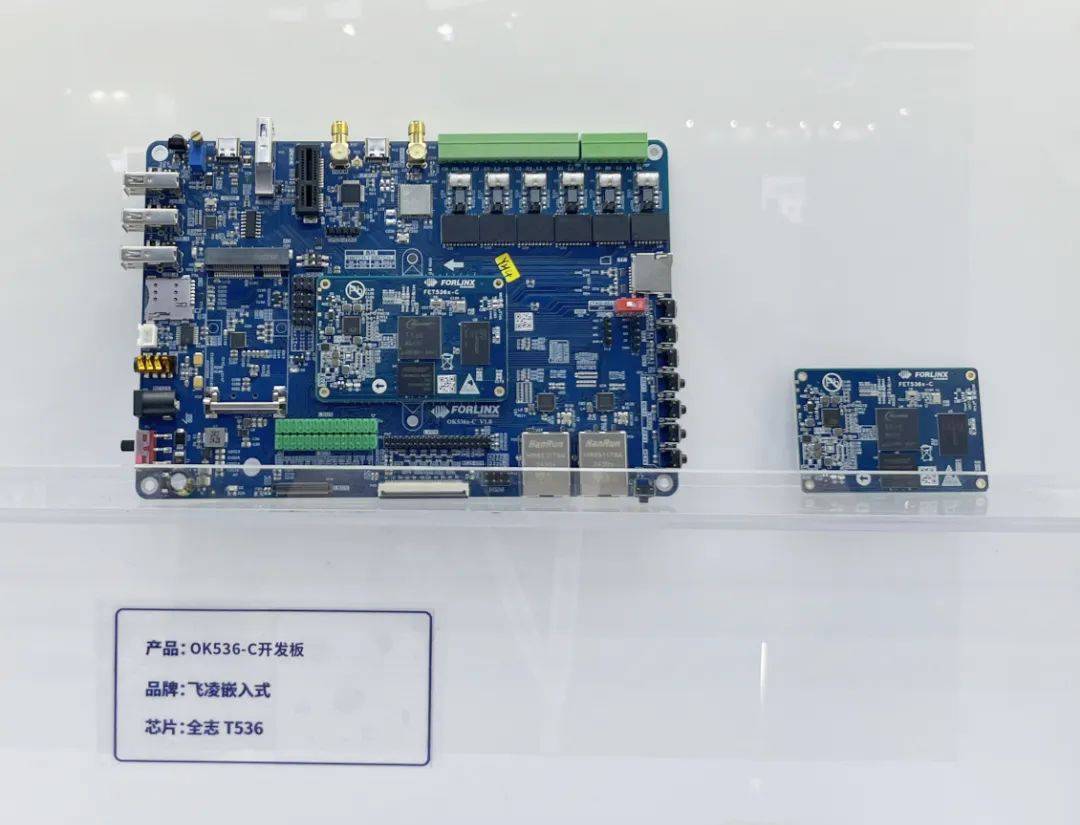

飞凌嵌入式自2019年起便与全志科技展开合作,目前飞凌嵌入式已基于全志处理器推出了7款核心板,分别是FETT507-C、FETA40i-C、FETT3-C、FET113i-S、FET527N-C、FET536-C和FET153-S。这些嵌入式主控产品具备稳定可靠的工业级品质,且性价比高,赢得了市场的广泛认可。得益于多年来紧密且深度的合作,飞凌嵌入式近期还成为首批“全志科技生态认证合作伙伴”。

在长期提供技术支持服务的过程中,飞凌嵌入式总结了用户开发全志系列产品时常见的问题及排查方法。本文中,小编将为大家梳理这些经验,助力开发者快速定位问题,提升开发效率。

一.通用排查思路

在全志系列主控的开发过程中,大家若遇到功能异常,可遵循以下通用排查步骤:如果参考飞凌嵌入式设计的底板功能,首先要保证所用芯片和原理的一致性,如果功能芯片不一致可能需要移植芯片驱动;

原理芯片一致,功能验证失败,需要依次排查功能芯片的电源、复位、时钟是否正常;

交叉测试,判断问题点在核心板上还是在底板上;

引脚电平是否匹配,数据信号是否有输出;

排查焊接问题,阻容器件是否存在虚焊、连焊、漏焊、错焊等问题;

测量信号的空闲状态是否正常;

确认引脚复用是否正确。二、具体模块的常见问题与解决思路

1、不启动问题(1)除电源和复位外,需要检查FEL信号是否正常,可摘并联电容看是否影响启动;

(2)使用示波器测量,核心板的供电波形,是否有跌坑导致启动异常。

2、I2C总线问题

(1)I2C为OD输出,首先需要确认是否有上拉电阻;

(2)确认同组I2C总线下挂载的设备地址是否有冲突;

(3)测量信号波形,空闲状态是否为高电平,数据传输时波形是否正常;

(4)如果波形上升缓慢可以减小上拉电阻阻值,如果低电平过高可以增大上拉电阻阻值;

(5)可通过I2C tool工具查看总线上是否挂载设备:

i2cdetect -l //检测系统上有几组I2Ci2cdetect -r -y 2 //检测I2C第二组总线上的挂载的设备

3、SPI通讯问题

(1)SPI接口MISO和MOSI不要交叉连接;

(2)确认片选信号是否连接;

(3)确认两个通讯设备的模式是否一致;

(4)测量时钟、数据输出是否正常。

4、USB接口问题

USB的正负信号是不可以交叉连接的,因此需要确认USB信号连接是否正确。

5、SDIO接口问题

(1)SDIO信号不可以通过电平转换芯片转换引脚电平;

(2)如果速度不满足要求,除引脚电平外,还需要确认SDIO总线是否做了等长处理;

(3)SDIO总线需要优先排查时钟输出是否正常。

6、LVDS显示问题

(1)LVDS显示屏的输出模式与屏幕是否一致(VESA和JEIDA);

(2)确认LVDS屏幕各差分信号的100Ω电阻是否焊接;

(3)测量时钟、数据输出是否正常。

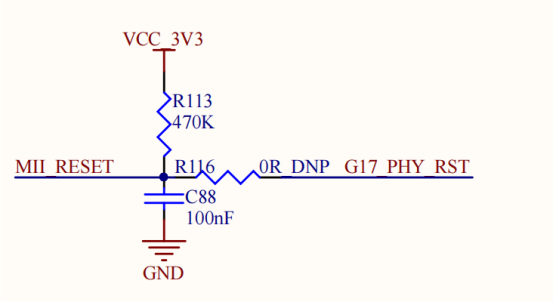

7、Ethernet网络问题

(1)确认PHY芯片与MAC端的通讯接口是否一致,是否做了等长处理;

(2)需检查MDIO总线是否上拉,波形是否正常;

(3)确认精密电阻是否满足要求;

(4)复位时间是否满足芯片要求;

(5)测量晶振是否起振;

(6)如果速度不满足需求,可以检测各路电源以及参考地是否完整;

(7)检测网络变压器的中心抽头是否正确;

(8)检查同一个总线上的不同PHY芯片地址是否有冲突,与软件是否一致;

(9)MDI数据线是否等长处理,阻抗是否满足要求;

(10)时钟线与其他线的间距是否满足3倍线宽;

(11)示波器测量芯片输出的DCDC是否有锯齿波。

8、UART问题

(1)串口收发信号需要交叉连接;

(2)确认串口工具配置是否正确,如:波特率;

(3)测量数据输出是否正常。

9、RS485问题

(1)RS485总线有多个设备时,需要确认两端的设备是否有120Ω的匹配电阻;

(2)如果RS485设备无法通讯,可以尝试RS485设备的参考地连接,减小工模干扰;

(3)由于RS485为半双工传输,有些RS485芯片需要收发控制信号,需要确认芯片驱动是否已经添加。

10、Audio音频问题

(1)源生的音频HPOUTL 、HPOUTR 如果做直接耦合的方式输出,需要把 HPCOMFB、HPCOM 这两个引脚拉一个对地电容;

(2)如果系统检测不到音频芯片,需要查看I2C总线通讯是否正常;

(3)如果可以正常挂载芯片但是没有声音输出,需要先排查I2S数据波形是否正常输出,再排查音频输出是否正常。

11、CAN总线问题

(1)CAN总线有多个设备时,需要确认两端的设备是否有120Ω的匹配电阻;

(2)如果CAN设备无法通讯,可以尝试将CAN设备的参考地连接,减小共模干扰。

三、总结

有了系统化的排查思路与模块化解决方案,就可以高效应对接口通信、信号完整性及配置逻辑等常见开发难题。希望本文总结的实战经验能够为各位开发者朋友提供清晰的问题定位路径,助力项目快速落地。 -

【新品】10路UART、3路千兆网、2路CAN-FD,全志T153核心板为工业应用而生发布在 飞凌嵌入式专区

在9月下旬举办的「2025工博会」上,全志科技专为工业领域推出的全新T153处理器惊艳亮相,飞凌嵌入式作为全志的生态认证伙伴也同步推出业内首个T153处理器的SoM方案——FET153-S核心板。

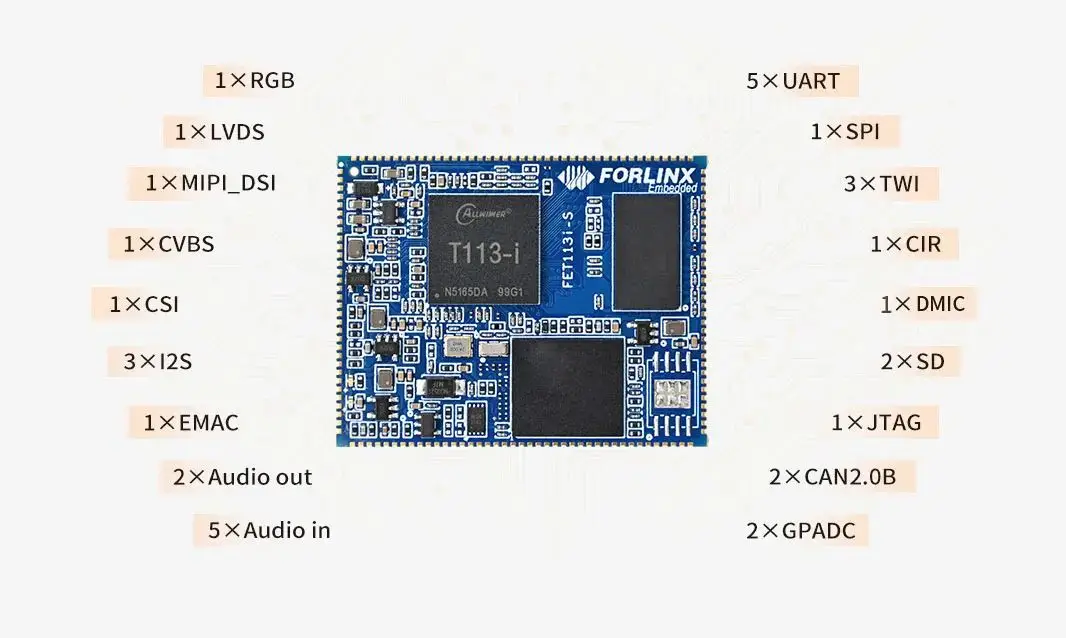

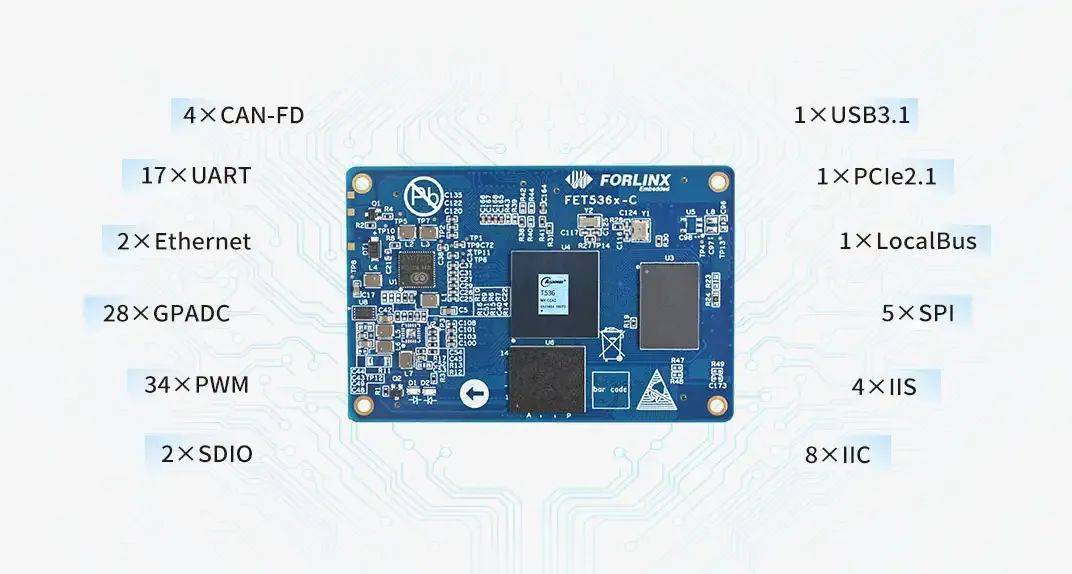

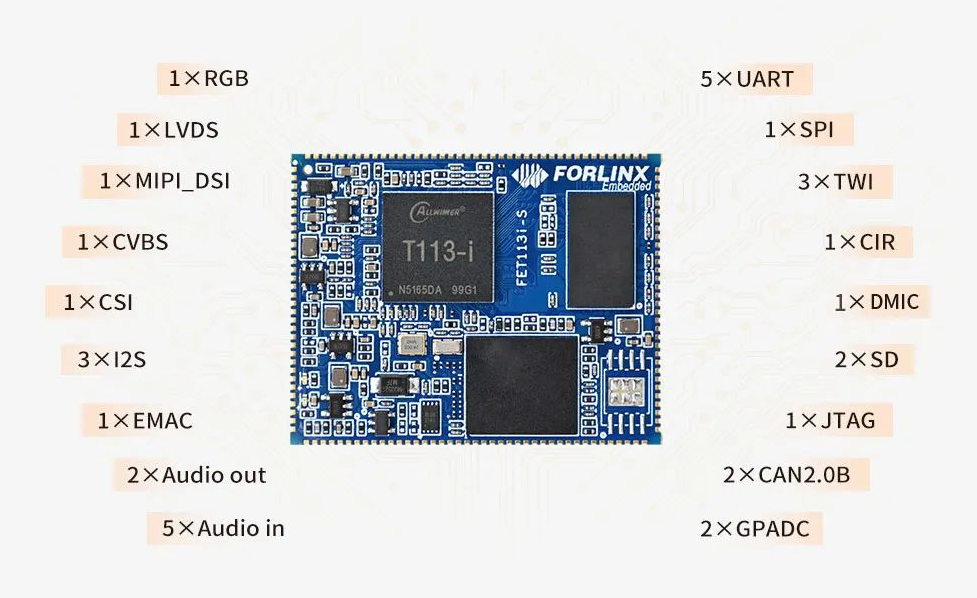

飞凌嵌入式FET153-S核心板配备3路千兆以太网接口、2路CAN-FD接口和Local Bus,支持高吞吐量网络连接,满足复杂数据驱动型应用需求。此外,T153处理器还提供10路UART、24路GPADC、6路TWI接口、30路PWM等接口,这些接口为多样化应用提供灵活性。

FET153-S核心板整板均采用工业级国产元器件,核心板与底板采用邮票孔连接,为您提供更牢固的连接方式。并且,产品通过飞凌嵌入式实验室严苛的工业环境测试,为您的产品稳定性保驾护航;10~15年生命周期,为您的产品提供持续供应保障。

1、全志新一代高性能芯片

T153汇集了高性能4xCortex-A7、CPU主频1.6GHZ、独立的RISC-V MCU、支持安全启动、国密算法IP、LocalBus等:赋能工业、电力等行业应用。

2、资源丰富

3、ARM+RISC-V,多核异构

T153集成四核Cortex-A7、64位玄铁E907 RISC-V MCU,以同时满足高效能与实时性控制的需求。四核Cortex-A7有强大的数据处理能力,而RISC-V核又可以匹配对实时性要求较高的应用场景。

4、引脚全部引出,满足各领域不同产品的不同功能需求

5、支持并行总线Local Bus

支持并行总线Local Bus 16bit/32bit,数据读写速率高,方便ARM和FPGA通讯。

6、安全特性

7、丰富的显示能力

多样的显示方式,支持RGB、LVDS、和MIPI-DSI显示,RGB分辨率可达1920x1080@60fps:LVDS支持1920x1080@60fpsMIPI-DSI分辨率可达1920x1200@60fps。

8、ISP提升图像质量

T153支持4-lane/2-lane MlPl-CSl,集成的ISP最大支持2路sensor,处理能力可达1M@30fps online、2M@30fps offline。

9、丰富的接口

10、广泛的行业应用

FET153-S核心板物料100%国产化,核心板功能全面在工业控制、电力、新能源、交通、医疗等多个行业FET153-S核心板以其高性能、多接口、工业级等综合优势加之飞凌嵌入式具备竞争力的价格优势及完备的售后技术支持助力您的产品快速上市,走在行业前沿。

11、规格参数

-

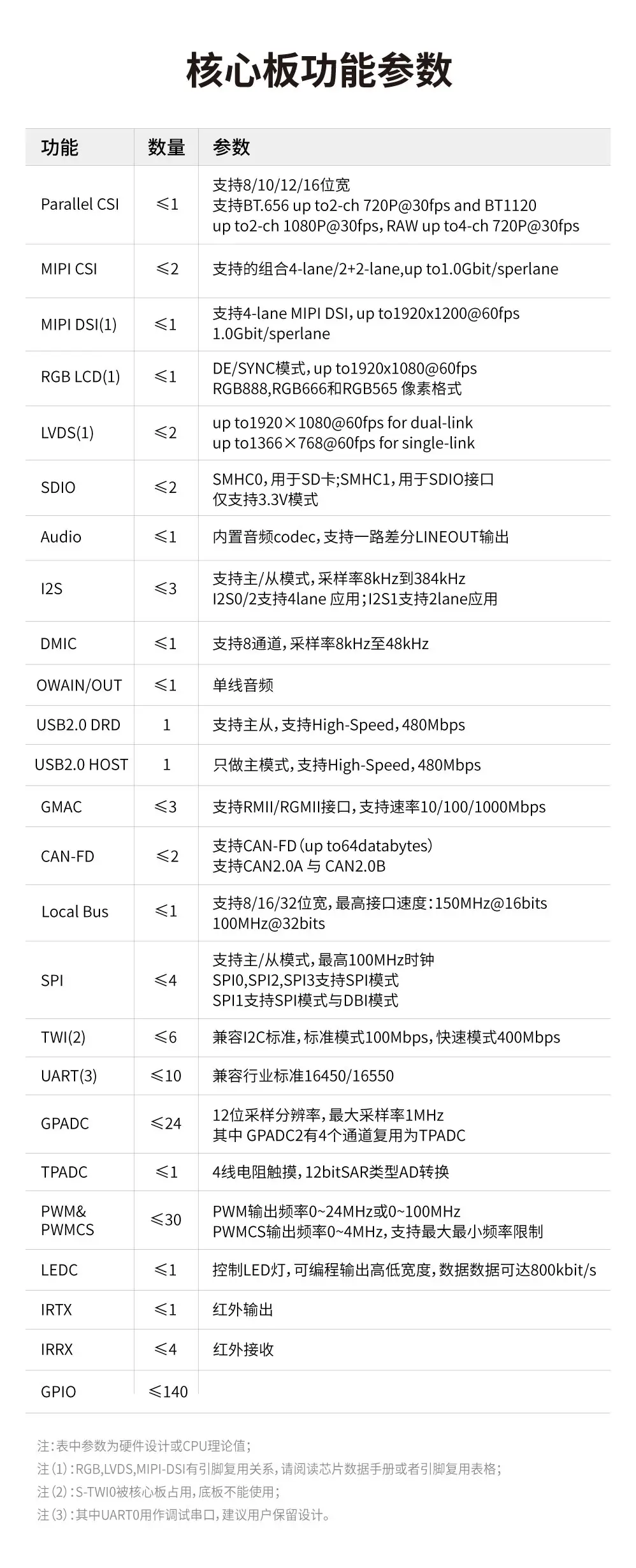

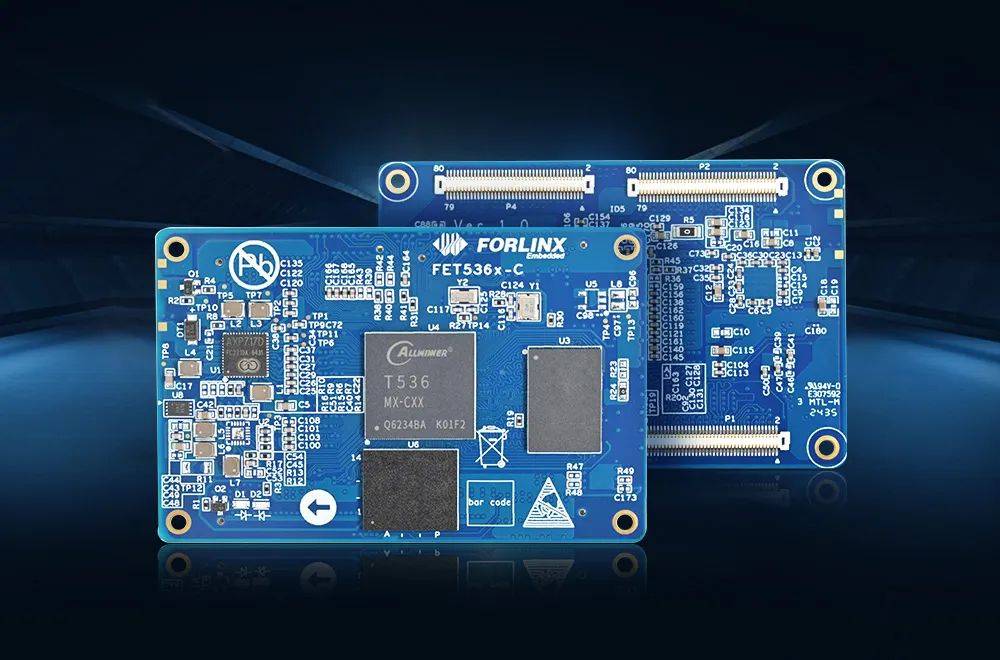

3.6Mbps稳定带宽:飞凌T536核心板8路CAN-FD技术方案解析发布在 飞凌嵌入式专区

在新能源汽车电池管理系统、工业自动化控制及智能电网等高新技术领域,电池模组数据的实时采集需求正随着电池组规模化发展呈现指数级增长。以新能源汽车为例,现代大型动力电池组普遍集成数百至数千个电芯单元,每个电芯均需实现电压、温度、荷电状态(SOC)等核心参数的持续监测,由此产生的数据吞吐量呈指数级攀升。

尽管控制器局域网(CAN)总线凭借其卓越的实时性、抗干扰能力和传输可靠性等优势,长期以来都是电池数据传输的主流协议,但在应对超大规模电池组监测场景时,传统处理器有限的CAN接口数量逐渐成为制约系统性能的瓶颈。

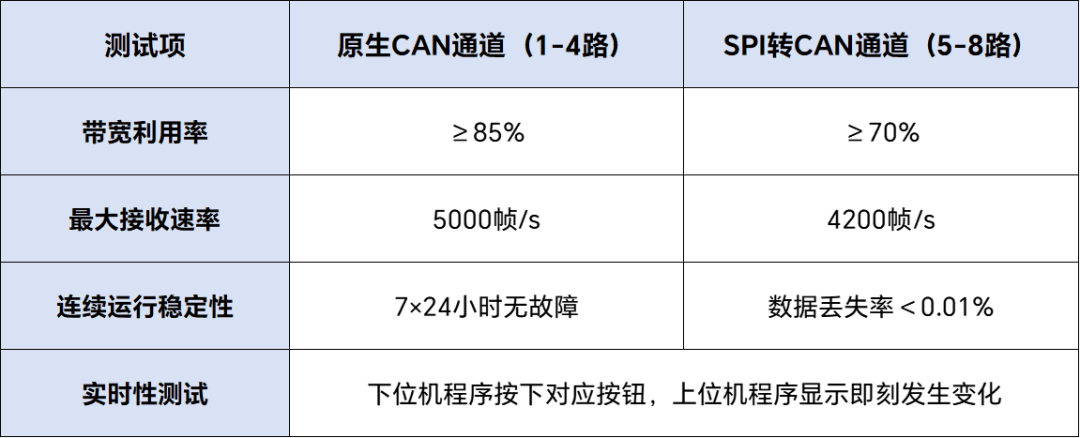

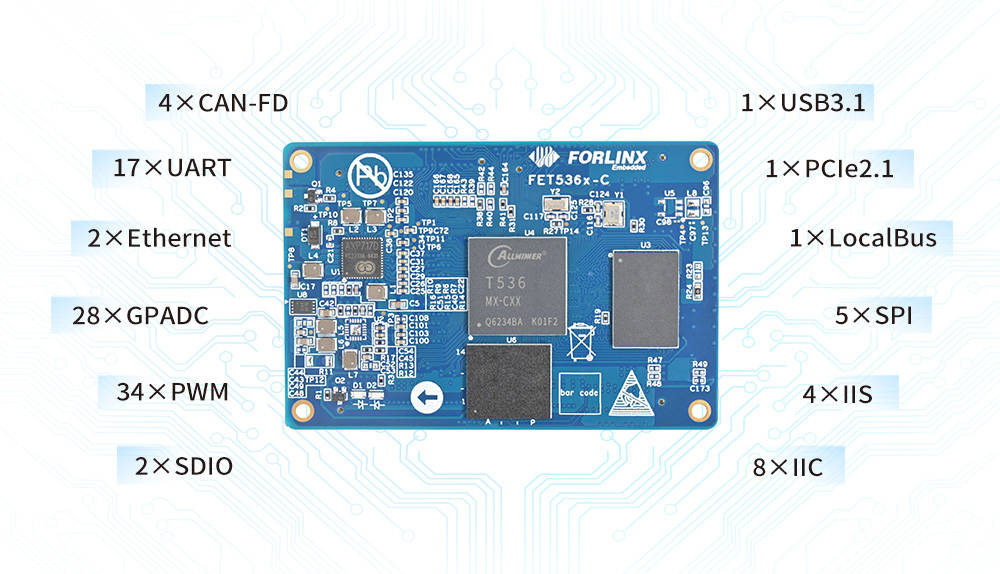

1、T536核心板,8路CAN-FD支持

在这样的背景下,飞凌嵌入式基于全志T536处理器设计开发的FET536-C核心板便是一款十分理想的主控选择 —— FET536-C核心板原生支持4路CAN-FD接口,并可通过4路SPI转CAN-FD接口进行扩展,直接满足8路CAN-FD并行采集的需求!搭载主频1.6GHz的4核A55架构CPU,使其具备线程级负载均衡能力。当面对8路CAN-FD并行接收产生的大量数据时,高性能CPU可将数据处理、中断响应等任务合理分配至不同核心,避免单一核心负载过重。

2、多线程架构,构建高效数据链路

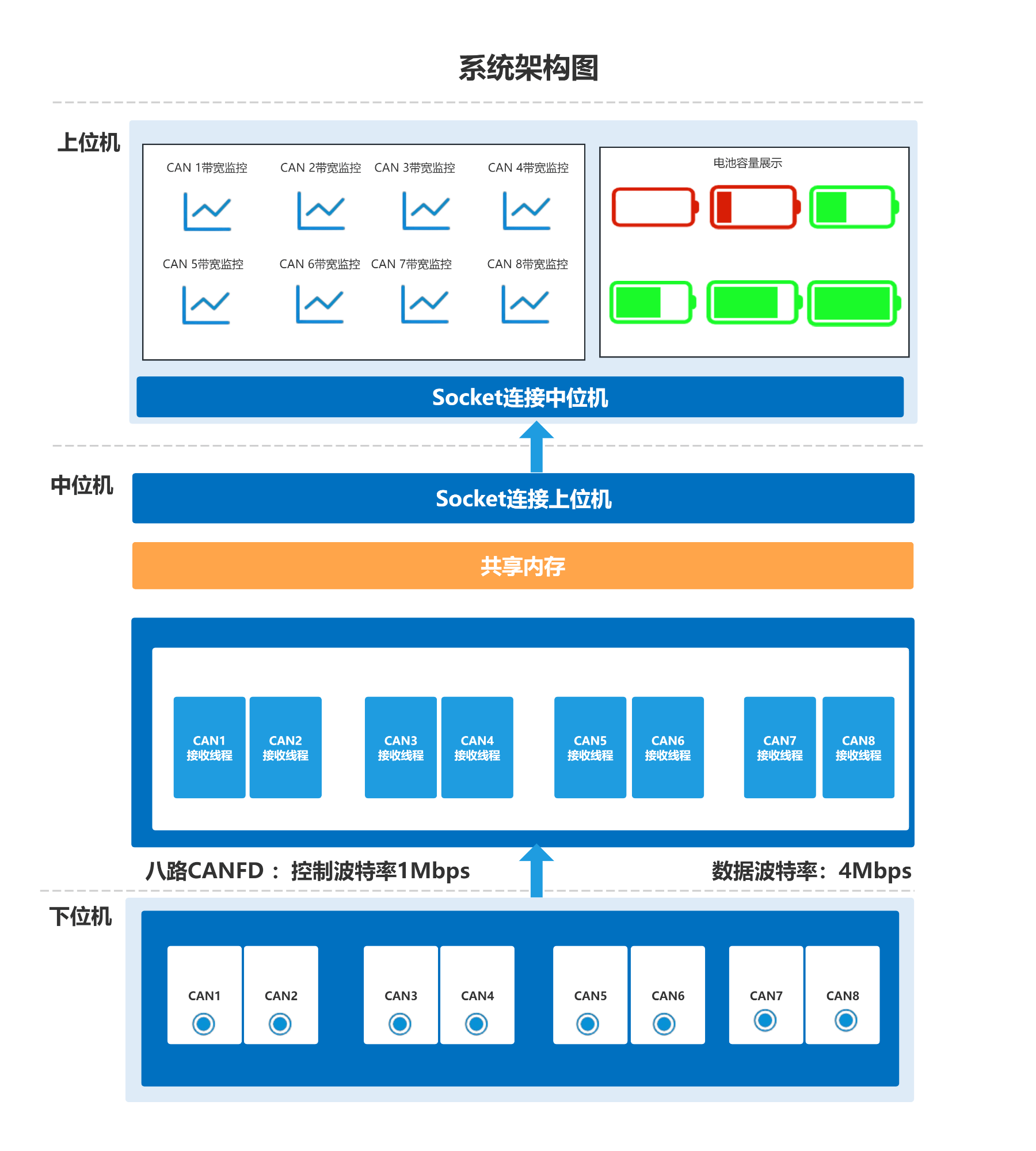

飞凌嵌入式基于FET536-C核心板设计了一套【8路CAN-FD技术展示方案】,它的架构分为下位机、中位机、上位机三级,通过协同工作实现实现8路CAN-FD并行处理。以下是系统框架图以及各层功能详解:

01 下位机

下位机是系统中直接与电池接触的部分,通常被称为执行器或传感器。下位机负责采集电池的实时数据,如电池电量、内阻等数据,并将这些数据上传给中位机。本展示方案中,下位机的主要功能包括:

数据采集:采集8路CAN-FD数据;

模拟按键操控:按键模拟电池容量,每按一下循环增加电池容量,将电池容量信息发送至中位机。

02 中位机中位机在系统中扮演着承上启下的角色,作为数据与通信中枢,一方面中位机通过下位机获取底层的电池系统数据,另一方面负责向上位机汇报数据。中位机的主要功能包括:

数据接收:通过下位机获取8路CAN-FD通道底层的电池容量数据和单位时间发送帧数,根据帧数分别计算出每个通道的带宽数据并更新共享内存;

数据上传:将计算出的带宽数据和电池容量数据,通过Socket发送至上位机进行分析和界面显示。

03 上位机上位机,是处于整个测试系统最上层的控制设备。上位机的主要功能包括:

数据接收:Socket连接中位机,接收来自中位机的带宽和电池容量数据;

可视化界面显示:界面展示带宽变化曲线图和实时电池容量,供用户分析。3、四大优化策略,提升性能上限

01 通道性能调优缓冲区扩容:扩大接收缓冲区,降低高负载丢包率;

CPU亲和性绑定:避免资源争抢,实现负载均衡。

02 并行处理优化非阻塞I/O与批量读取:避免线程阻塞,循环读取所有待处理帧;

原子操作替代锁:获取各通道帧计数,消除锁竞争带来的性能瓶颈。

03 通信协议增强CAN-FD协议适配:启用FD模式(数据段4Mbps),扩展帧、单帧承载数据量提升至64字节;

TCP可靠传输:避免客户端断开引发进程崩溃,支持断线重连机制。4、效果展示,表现优异

01 核心指标验证

02 实时监控效果

8路CAN-FD通道实时带宽监控曲线,原生通道稳定在3.2-3.6Mbps,扩展通道稳定在2.9Mbps;下位机按键模拟电池容量逐渐增加或置0后再次增加,中位机快速响应接收并上传至上位机,上位机界面可以即刻展示出相应变化。03 应用价值

新能源场景:支持百电芯级电池组实时监控,数据延迟<10ms;

工业自动化:8路并行采集满足多设备协同控制需求,系统响应效率大幅度提升;

技术前瞻性:为下一代车载ECU、智能电网边缘计算提供高带宽通信范式。5、总结

【基于飞凌嵌入式T536核心板的8路CAN-FD技术展示方案】通过多核架构优化、协议栈深度调优与并行处理技术,成功破解八路CAN-FD高带宽接收难题。在新能源与工业领域数字化转型浪潮中,该技术为海量数据实时采集提供了可复用的工程化解决方案,推动嵌入式系统向高并发、低延迟方向迈进。 -

从入门级到旗舰款,全志T系列核心板怎么选?发布在 飞凌嵌入式专区

在工业控制、物联网及边缘计算等领域中,全志科技T系列处理器以其出色的性能和稳定的工业级品质成为了越来越多客户的选择。作为全志科技的战略合作伙伴,飞凌嵌入式基于T系列处理器打造了多款核心板产品,覆盖从轻量级应用到高性能计算的全场景需求。

面对FET113i-S核心板、FET527N-C核心板和FET536-C核心板三款主流明星产品,工程师该如何选择?本文将从核心配置、功能特性到行业适配性进行全方位解析,助您找到匹配项目需求的全志T系列核心板解决方案。

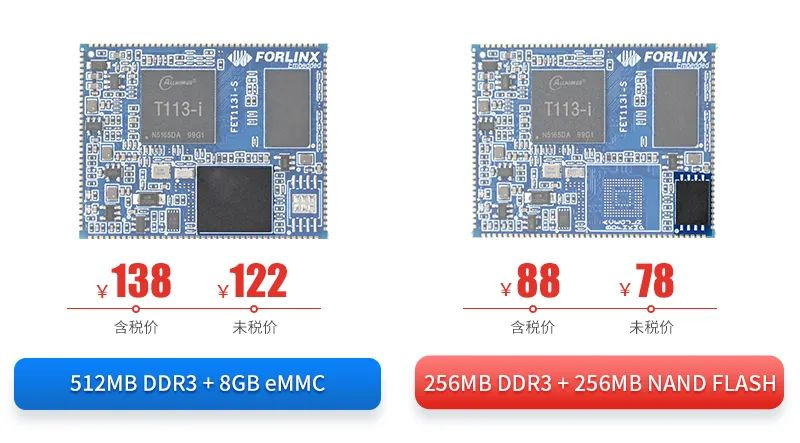

FET113i-S核心板,国产化降本之选

对于成本敏感型的工业项目,飞凌嵌入式FET113i-S核心板是一款极具优势的选择。这款基于全志T113-i工业级处理器打造的全国产工业级核心板,含税价格最低仅需88元。

- 多核异构,灵活配置

飞凌嵌入式FET113i-S核心板虽定位为入门级,却拥有三种处理器架构:双核ARM Cortex-A7 CPU(主频1.2GHz)、64位玄铁C906 RISC-V CPU和专用DSP核。通过软件可灵活控制各核心的开启与关闭,实现A7核+RISC-V核+DSP核同时运行的强大组合。

这种架构让单一芯片即可应对复杂场景:Cortex-A7负责主控运算,DSP核处理多媒体和数字信号,RISC-V核则满足实时控制需求,实现“一芯多用”。

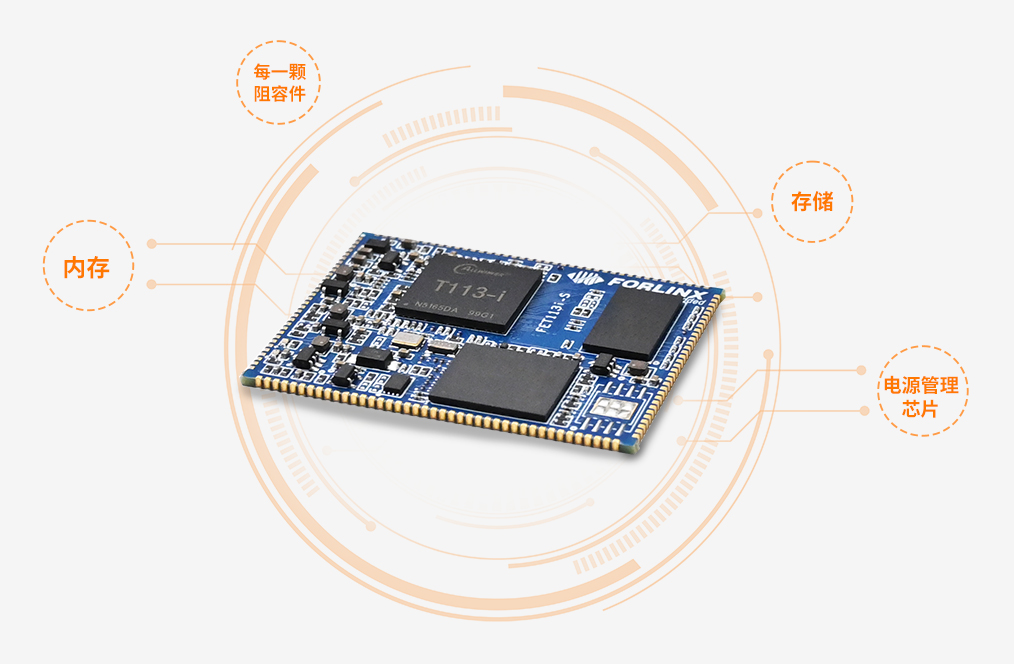

- 工业级可靠性与丰富接口

FET113i-S核心板整板采用100%国产工业级元器件,从内存、存储到每一颗阻容件均可经受-40℃~+85℃严苛工作温度的考验,适应工业现场复杂环境。

接口资源同样丰富:支持8位并行CSI、CVBS视频输入;CVBS、RGB、双通道LVDS、四通道MIPI DSI视频输出;同时还配备USB、SDIO、UART、SPI、CAN、Ethernet等工业常用接口。

- 适用领域

凭借超高性价比和工业级可靠性,FET113i-S特别适合应用于轨道交通、电力能源、工业控制、安防监控、会议系统等领域中对成本控制要求较高的项目。

FET536-C核心板,高性能多接口专家

在去年的9月的工博会上,全志科技发布了T系列处理的最新成员——T536,同一时间,飞凌嵌入式也行业首发了搭载T536系列处理器的FET536-C核心板。对于需要实时控制和丰富接口的高端工业应用而言,飞凌嵌入式FET536-C核心板是一款十分值得推荐的解决方案。

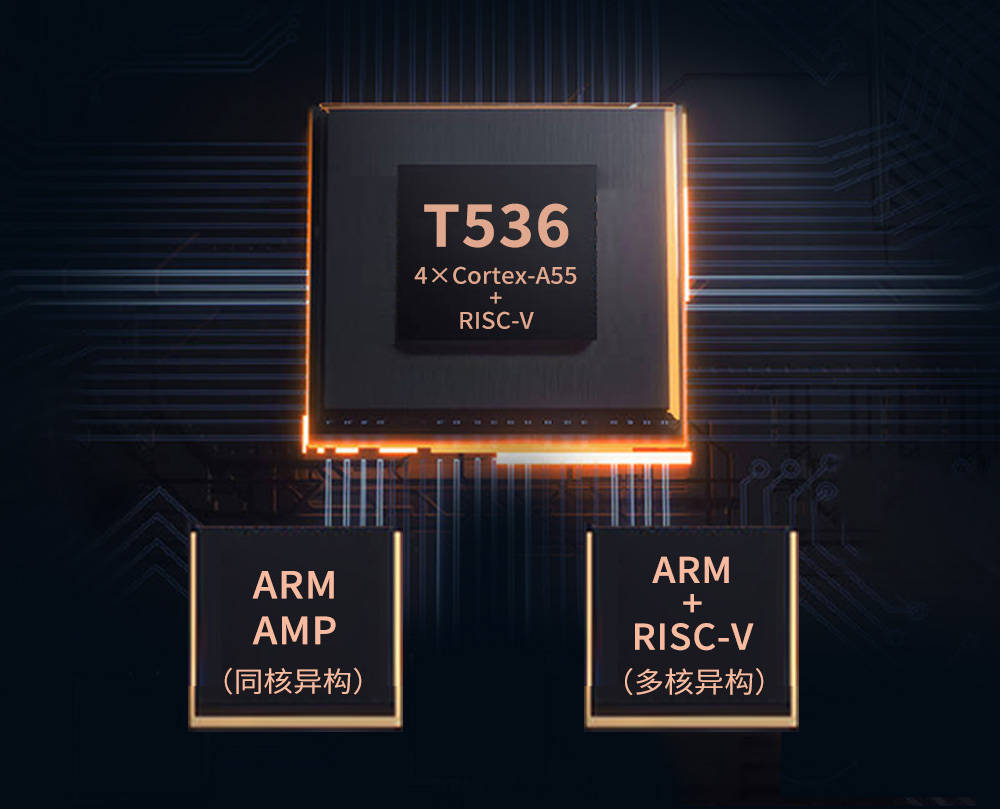

- 四核A55 + RISC-V实时双架构

飞凌嵌入式FET536-C核心板采用AMP多核异构设计:四核Cortex-A55(主频1.6GHz)处理复杂应用,600MHz玄铁E907 RISC-V MCU专攻实时任务。这种架构支持Linux RT+FreeRTOS+裸机代码混合运行,平衡高性能计算与实时控制需求。集成2TOPS NPU,为边缘AI应用提供强劲支持。

- 工业级接口矩阵

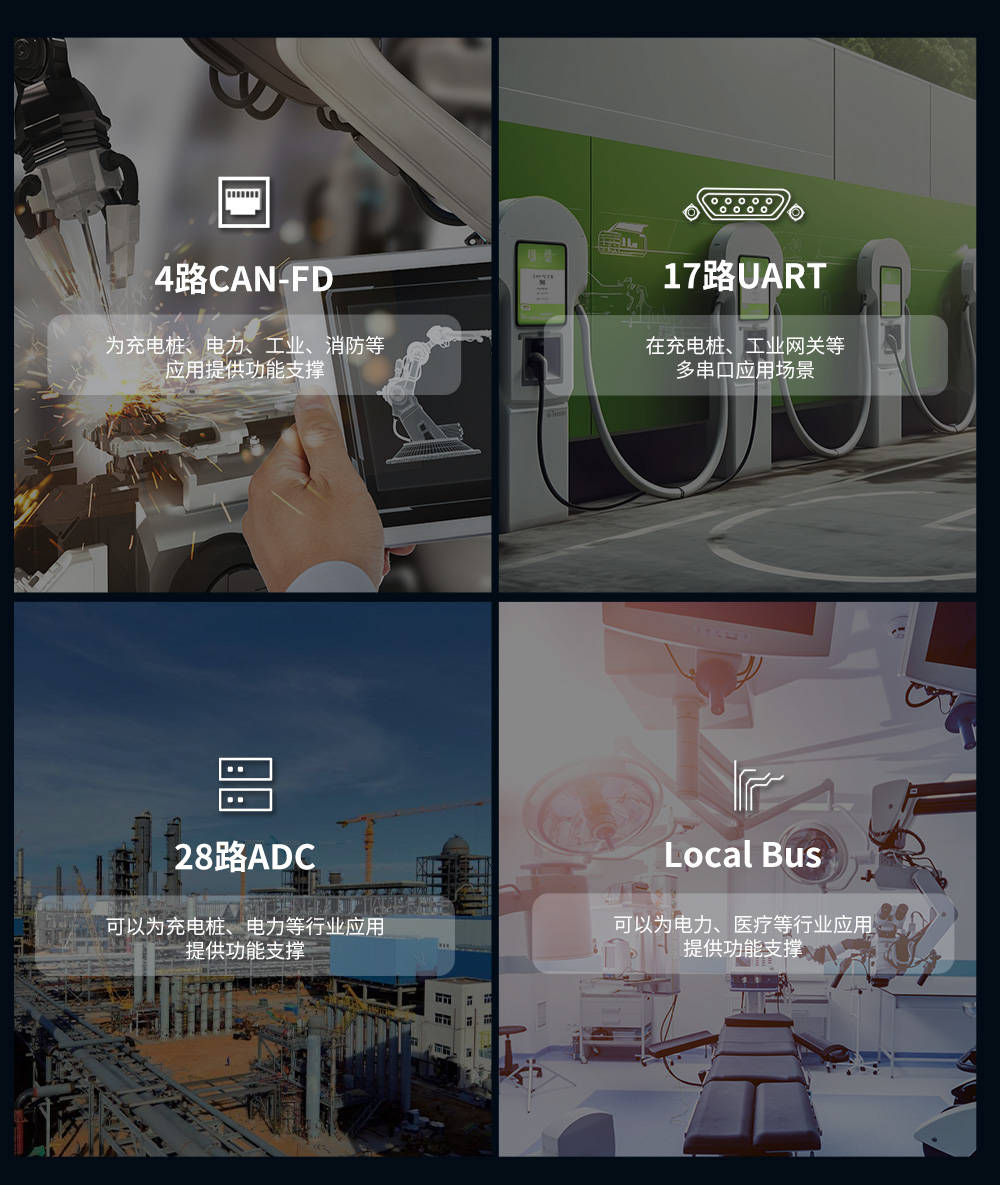

FET536-C核心板核心板的最大亮点在于其配备了丰富的接口资源:通信接口:4路CAN-FD、17路UART、2路千兆以太网;高速扩展:USB3.1、PCIe 2.1(5Gbps);控制信号:34路PWM、28路ADC、196路GPIO,此外,还支持并行总线LocalBus,读写速率高达16bit@100M/32bit@50M,可实现与FPGA的百纳秒级低延时数据交互,特别适合工业控制中的实时数据采集场景。

- 适用领域

凭借丰富接口和实时性能,FET536-C可以成为集中器、DTU、充电桩、工业控制等领域的理想选择。

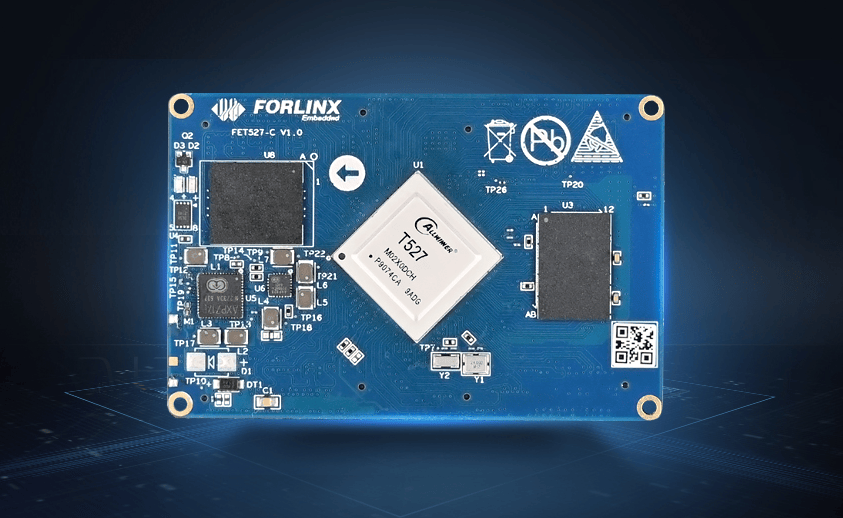

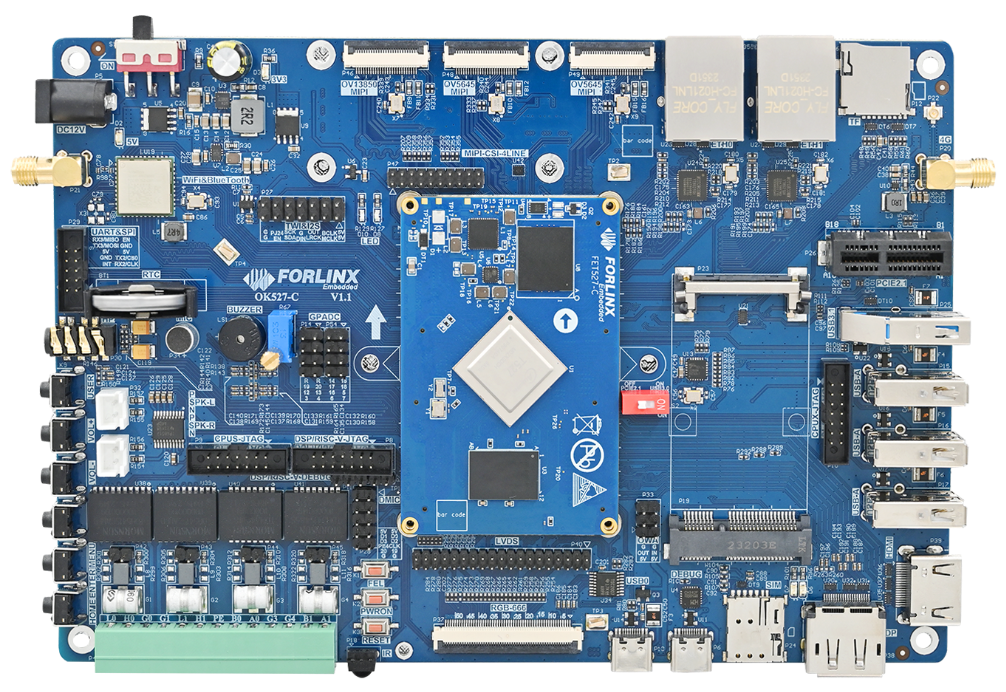

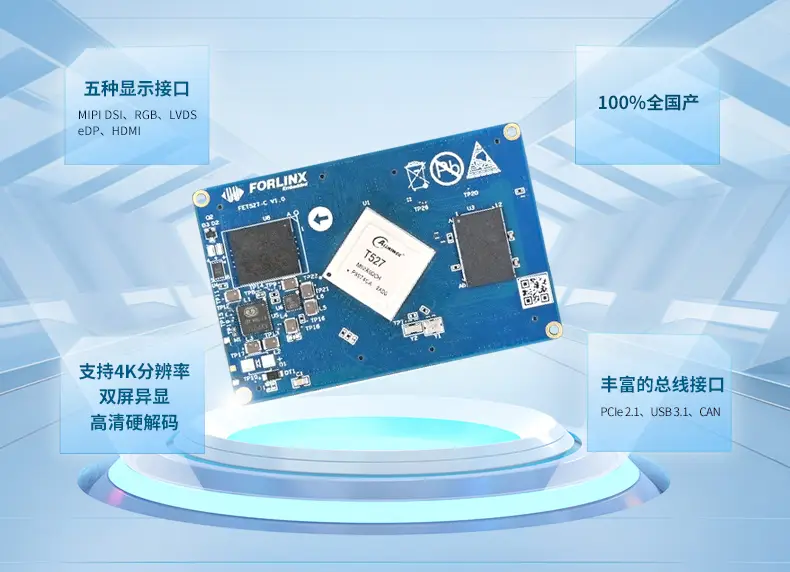

FET527N-C核心板,多场景性能旗舰

当项目需要处理复杂计算任务或AI推理时,飞凌嵌入式FET527N-C核心板展现出强大的多场景适应能力。该产品基于全志T527系列高性能处理器,采用板对板连接器设计,便于安装维护,并具有10-15年生命周期,保障长期供应。

- 八核超高性能工业级国产芯片

FET527N-C的核心亮点在于其8核Cortex-A55架构(4核@1.8GHz + 4核@1.4GHz),数据处理能力高达36.7K DMIPS。同时集成RISC-V协处理器和HiFi4 DSP核,形成完善的多核异构计算体系。

更重要的是其搭载的2TOPS NPU,支持INT8/INT16量化运算,提供40+种AI算子,为边缘AI应用提供强劲算力支持。

- 超强多媒体与显示能力

FET527N-C核心板在多媒体处理上表现卓越:支持H.264编解码、H.265解码(4K@60fps),并实现4K+1080P双屏异显输出。显示接口全面覆盖RGB、双通道LVDS、四通道MIPI DSI和eDP,满足多屏互动场景需求。

- 全栈国产化生态

作为战略合作伙伴,飞凌嵌入式与全志科技深度合作,确保硬件功能表现的深度优化。此外,核心板已适配OpenHarmony 4.1系统,实现从芯片到操作系统的全链路国产化。

- 适用领域

凭借卓越的综合性能,FET527N-C核心板广泛适用于商显/收银、云电脑、机器人、工业智能、边缘计算网关、后装中控、商用车、工控机等领域。

总结

通过深度解析三款核心板的特性,我们可清晰梳理出选型决策——FET113i-S核心板,适用于成本敏感型的轻量级工业应用场景;FET527N-C核心板,适合高性能多媒体及AI应用;FET536-C核心板,则是面向更为复杂的高端工业控制场景。希望本文能够帮助您找到更加匹配项目需求的全志T系列核心板解决方案,助力您的项目快速落地。 -

全志科技携飞凌嵌入式T527核心板亮相OpenHarmony开发者大会发布在 飞凌嵌入式专区

近日,OpenHarmony开发者大会2025(OHDC.2025,以下简称“大会”)在深圳举办,全志科技作为OpenHarmony生态的重要合作伙伴受邀参会,并进行了《全志科技行业智能芯片OpenHarmony方案适配与认证经验分享》的主题演讲。

值得注意的是,全志科技不仅介绍了在「工业智能SoC」的场景应用和产品路线图,还重点介绍了与飞凌嵌入式合作开发的FET527-C核心板,并分享了该产品在OpenHarmony生态中的适配经验与行业应用前景。

不久前,飞凌嵌入式基于全志T527处理器设计开发的FET527-C核心板获得了「OpenHarmony生态产品兼容性证书」,目前该方案已适配了标准版OpenHarmony4.1/OpenHarmony5.0系统,成为了工业智能化领域的重要OpenHarmony硬件方案。

现在,飞凌嵌入式FET527-C核心板的OpenHarmony适配代码已开源,开发者可通过社区获取相关资源,加速产品开发;未来,飞凌嵌入式也将继续与全志科技深化合作,推动更多工业级OpenHarmony嵌入式主控方案的落地,共同促进开源鸿蒙生态的建设与发展。

-

飞凌嵌入式T527核心板获得【OpenHarmony生态产品兼容性证书】发布在 飞凌嵌入式专区

近日,飞凌嵌入式FET527-C核心板通过OpenHarmony 4.1 Release版本兼容测评,获得【OpenHarmony生态产品兼容性证书】。

飞凌嵌入式FET527-C核心板搭载全志T527系列全国产高性能处理器,集成8个ARM Cortex-A55核心,并内置RISC-V核和DSP核,提供出色的处理能力和能效比,并且经过严格的工业环境测试,具备高稳定性和可靠性,可为产品的稳定运行保驾护航。

OpenHarmony 4.1则以开放生态为根基,通过分布式架构、高效开发工具与安全增强,构建了覆盖多场景的智能化底座。它不仅填补了传统操作系统在万物互联时代的短板,更通过全球化合作与行业深耕,成为推动工业4.0与数字化转型的关键力量。

这些特性与飞凌嵌入式FET527-C核心板的硬件能力相结合,能够为工业设备提供从底层硬件到上层应用的完整国产化解决方案。

-

飞凌嵌入式T527核心板+OpenHarmony 4.1,打造工业智能化升级的新范式发布在 飞凌嵌入式专区

飞凌嵌入式FET527N-C核心板正式发布OpenHarmony4.1系统,实现了从芯片架构到操作系统的全链路国产化。该产品具备灵活可编程、高效能运算、低成本控制等多重优势,通过多核异构设计同步支持边缘智能计算与精准实时控制,能够满足智能制造、能源管理、智能安防、智慧交通等领域对系统稳定性与安全性的高标准需求,为工业物联网应用提供自主可控的国产化解决方案。

1、全国产核心板+全国产操作系统

飞凌嵌入式FET527N-C核心板搭载全志T527系列全国产高性能处理器,集成8个ARM Cortex-A55核心,并内置RISC-V核和DSP核,提供出色的处理能力和能效比,并且经过严格的工业环境测试,具备高稳定性和可靠性,可为产品的稳定运行保驾护航。OpenHarmony 4.1系统在系统安全方面进行了全面增强,实现了对系统关键行为的监控与防护,以及针对潜在威胁的预测性安全分析,大大提高了整体系统的安全性。

2、独具优势的OpenHarmony 4.1

OpenHarmony 4.1以开放生态为根基,通过分布式架构、高效开发工具与安全增强,构建了覆盖多场景的智能化底座。它不仅填补了传统操作系统在万物互联时代的短板,更通过全球化合作与行业深耕,成为推动工业4.0与数字化转型的关键力量。OpenHarmony 4.1的优势可概括为三点——

- 开放性与兼容性:

通过标准化API接口,支持跨设备协同开发,降低多端适配成本;

- 高效开发模式:

提供统一的开发框架,简化应用部署流程,提升开发效率;

- 安全增强:

强化权限管理和数据加密机制,满足工业场景对安全性的严苛要求。

值得注意的是,飞凌嵌入式T527核心板的产品资料也即将上传至OpenHarmony的官方代码仓库,助力开发者高效开发,贡献代码。

3、国产高性能工业“芯”力量

聊完OpenHarmony 4.1的“软”实力,我们再来看看飞凌嵌入式FET527N-C核心板的“硬”实力。八核高性能工业“芯”

核心板搭载的全志T527系列处理器集成了8个ARM Cortex-A55高性能核,同时内置1个RISC-V核和1个DSP核,这意味着它能够提供卓越的处理能力和超高能效比。此外,还可选择2TOPS算力NPU,出色的处理器性能可以满足各种复杂的应用需求,让您的项目更加智能、稳定和高效。

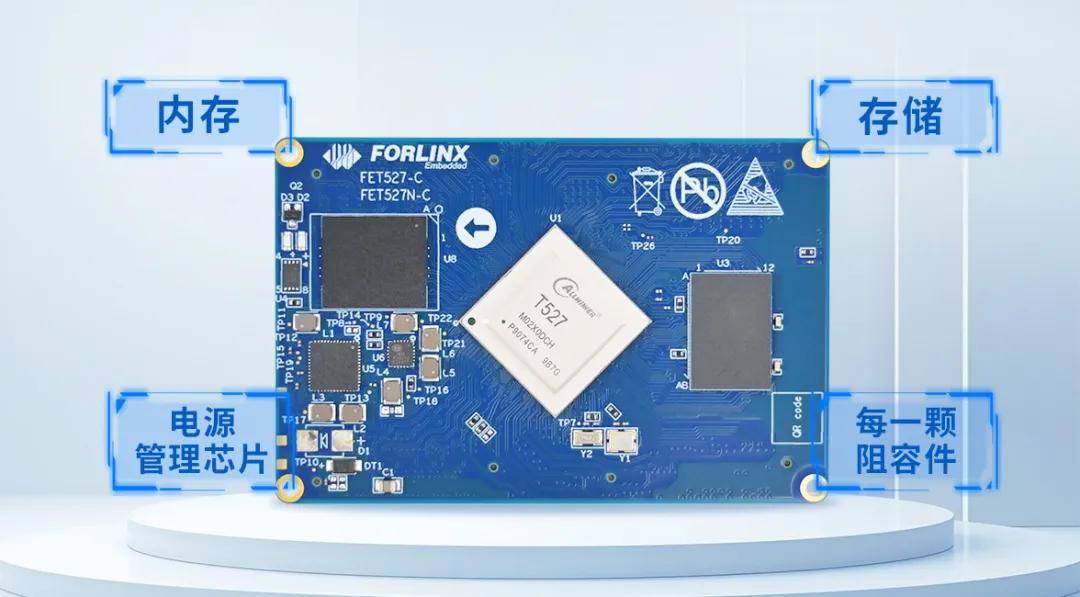

100%元器件国产化率

在核心板的选料上飞凌嵌入式FET527-C核心板实现了从内存到电源管理芯片再到每一颗阻容件的全部国产化。100%的国产化率意味着产品安全性和竞争力的提升,对产业链的优化和发展将起到重要的促进作用。FET527-C核心板能够为更多行业的国产化与智能化升级提供强大稳定的性能支持和长期稳定的供应保障。

α阶段参与开发,更稳定可靠

作为全志战略合作伙伴,飞凌嵌入式在T527系列处理器的α阶段便参与开发,这意味着FET527-C核心板拥有更高维度、更深层次的技术保障。此外,FET527-C核心板还经过了飞凌嵌入式实验室严格的工业环境测试,具备高稳定性和可靠性,可为您的产品稳定性保驾护航。

4、总结

OpenHarmony 4.1与飞凌嵌入式FET527N-C核心板的结合,不仅实现了从芯片到系统的全栈技术自主可控,更通过硬件加速、分布式架构优化和行业场景化适配,为工业4.0、智慧城市等关键领域提供了兼具性能、安全与成本优势的国产化解决方案。 -

智能配电新纪元:基于飞凌嵌入式T536核心板的DTU解决方案发布在 飞凌嵌入式专区

配电自动化终端DTU(数据终端单元)在智能电网的建设中扮演着至关重要的角色,它通过信息采集与控制,实现配电线路的遥测、故障检测及远程操作,极大提升了供电可靠性和效率。

在国网新规的推动下,采用多核异构处理器设计的DTU方案日益成为主流,其中实时核与控制核的协同工作,为配电系统的实时监控与高效管理提供了有力保障。在此背景下,飞凌嵌入式基于FET536-C核心板的RISC-V核DTU解决方案应运而生,凭借卓越的性能和灵活的多核架构,引领配电自动化进入全新时代。

1. T536核心板的优势

飞凌嵌入式FET536-C核心板基于全志T536工业级处理器开发设计,主频1.6GHz,集成4核Cortex-A55和64位玄铁E907 RISC-V MCU,能够提供高效的计算能力。其中RISC-V核最高主频可达600MHz,支持16KB指令缓存和16KB数据缓存, 可运行于超大容量DDR。T536处理器的玄铁E907 RISC-V核的接口资源也十分丰富,能够充分满足配电自动化终端DTU所需功能的实现。

2. 基于T536核心板的DTU方案亮点

实时业务高效处理:

如采样、FFT计算、故障动作等实时性强的业务,都可以在T536核心板的RISC-V核上运行,依靠600MHz主频和浮点运算单元,RISC-V核能轻松完成多路间隔的实时功能。对于多路AD7616采样,既可以凭借SPI高达100MHz的速率轻松实现,也可通过5MHz波特率和单帧64字节的CAN-FD与每个间隔的单片机高效实现。故障录波与双核协同:

T536核心板的RISC-V核可以动态调整DDR空间,满足故障录波数据存储需求,凭借RPMsg和RPbuf强大的双核通信带宽,可将故障录波数据高效传给A核,生成故障录波文件。管理核的通信中枢:

A核凭借四核1.6GHz主频和丰富的资源接口,可通过多种通信接口实现数据的采集和加密/解密功能,满足各种传感器接入和向调度中心加密后IEC101/IEC104的转出功能。

3. 应用实例

3.1 SPI数据收发

本案例为SPI回环测试,即将SPI的MOSI和MISO两个引脚短接进行数据收发。3.1.1 功能介绍

3.1.2 效果实现

SPI发送和接收的FIFO均为128个,在底层hal库程序中,当数据长度小于128字节时,采用中断方式,当FIFO大于等于128字节时,采用DMA模式。

中断方式传输效果:

DMA方式传输效果:

使用DMA传输3200字节,SPI速率默认为100Mbit/s,案例中平均传输速率为64Mbit/s,单次传输的字节越多,系统调度时间占比越可以忽略,接近理论值。

3.2 核间通信RPbuf

RPbuf是全志基于RPMsg所实现一套高带宽数据传输的框架。RPMsg是基于共享内存和msgbox中断实现的一套核间通信机制,RPMsg除去头部的16字节数据外,单次最多可发送496字节有效数据。目前RPbuf最高可支持511.875KB数据(512KB减去128Bytes头部)我们以单次511.875KB数据传输为例进行展示。

3.2.1 功能介绍

• VirtIO:一套虚拟化数据传输框架,用于管理共享内存VRING;

• VRING:由VirtIO管理的一个环形共享内存;

• Msgbox:全志提供的一套消息中断机制,已与Linux内核中原生的mailbox框架适配;

• MSGBOX_IRQ:Msgbox中断;

• RPMsg:基于VirtIO管理的共享内存所实现一套少量数据传输的框架;

• RPbuf:全志基于RPMsg所实现一套大量数据传输的框架。

由上图可知(以RISC-V核向A核发送数据为例),RPbuf首先将数据放置在DDR中,再将缓冲区首地址和大小通过RPMsg发送至A核(RPMsg将缓冲区首地址和大小放入VRING,然后请求Msgbox中断,A核收到这个中断后,在其回调函数中使用RPMsg接口函数来从VRING中取出cmd),随后A核从cmd handler中获取缓冲区内的地址和长度,最后在应用层读取数据,从而完成双核间数据传输。3.2.2 效果展示

由上图,单次传输511.875KB数据,带宽大约为239~247Mbps。

4. 总结

总体而言,飞凌嵌入式的A核+RISC-V核DTU解决方案凭借T536核心板的多核架构和卓越性能,为配电自动化终端提供了强大的技术支持,这一方案不仅提升了供电可靠性和效率,还为配电系统的实时监控和高效管理提供了有力保障,是未来智能电网发展的重要方向。 -

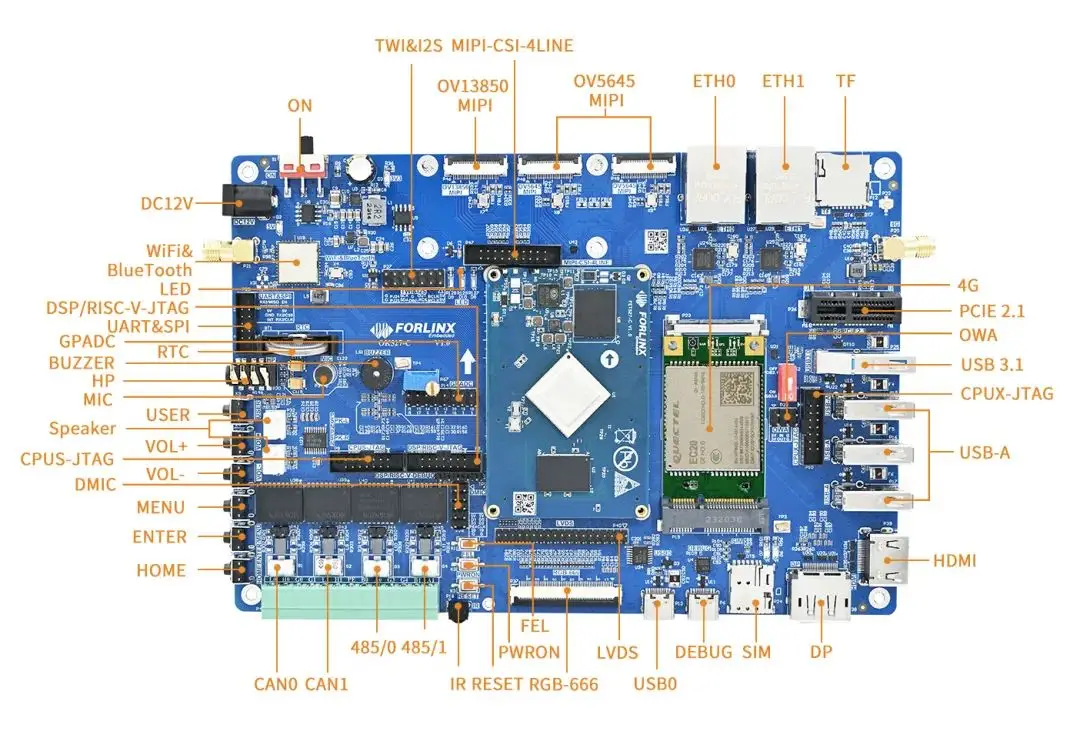

飞凌嵌入式携手全志,T536全国产核心板重磅发布发布在 飞凌嵌入式专区

以全志T536工业级处理器为引擎,驱动国产化创新,为千行百业提供降本增效新选择——飞凌嵌入式FET536-C核心板重磅发布!

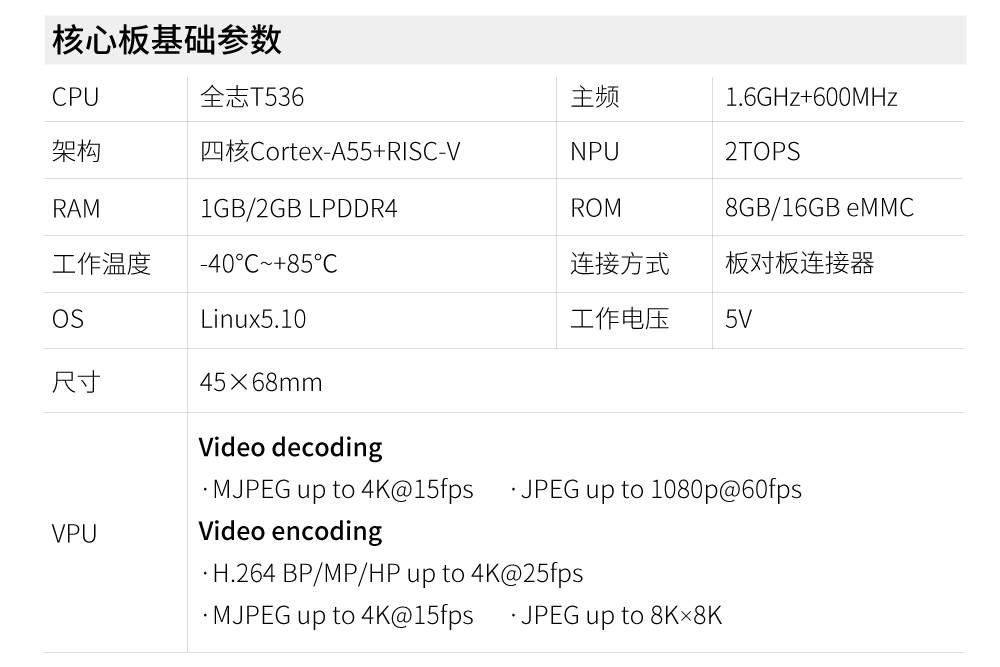

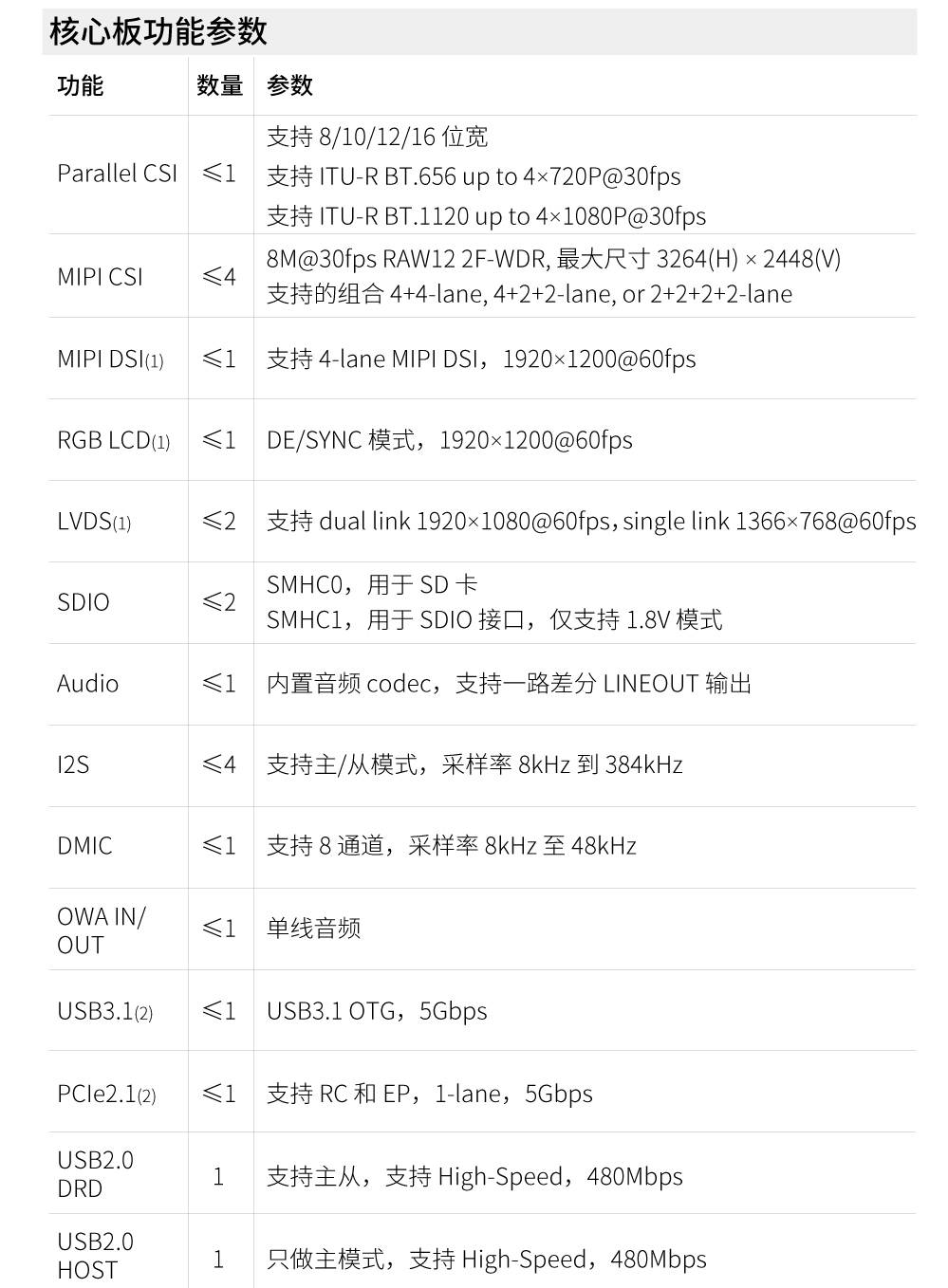

FET536-C全国产核心板

FET536-C核心板基于全志发布的T536工业级处理器开发设计。主频1.6GHz,集成四核Cortex-A55、64位玄铁E907 RISC-V MCU,提供高效的计算能力;支持2TOPSNPU、安全启动、国密算法IP、全通路ECC、AMP、Linux-RT等,还具备广泛的连接接口:USB、SDIO、UART、SPI、CAN-FD、Ethernet、ADC、LocalBus等一应俱全。除性价比超高的处理器外,核心板整板均采用工业级国产元器件,是集中器、FTU、DTU、充电桩、交通、机器人、工业控制等关键领域实现国产化降本的优质之选。

全志新一代高性能芯片

汇集了性能更高的应用内核、独立的RISC-V MCU,支持2TOPS NPU、安全启动、国密算法IP、全通路ECC、AMP、Linux-RT、LocalBus等可加速边缘的机器学习应用。

接口资源丰富

AMP&多核异构

集成四核Cortex-A55、64位玄铁E907 RISC-VMCU,支持Linux RT+FreeRTOS+裸代码,以同时满足高效能与实时性控制的需求。

NPU:2TOPS算力

内置了算力高达2TOPS的神经处理单元(NPU)为边缘计算应用提供了强大的支持。

引脚全部引出

满足各个领域不同产品的不同功能需求。

支持并行总线LocalBus

支持并行总线LocalBus,数据读写速率高16bit@100M or 32bit@50M,方便ARM和FPGA通讯。

安全特性

ISP 大幅提升图像质量

集成ISP技术,支持8M@30fps、WDR、3DNR等技术,可以提供清晰、准确的图像数据。

持续更新的用户资料

应用场景

FET536-C核心板物料100%国产化,核心板功能全面,可应用在集中器、DTU、充电桩、交通、机器人、工业控制等多个行业,以其高性能、多接口、工业级等综合优势,加之飞凌具备竞争力的价格优势及完备的售后技术支持,助力您的产品快速上市,走在行业前沿。

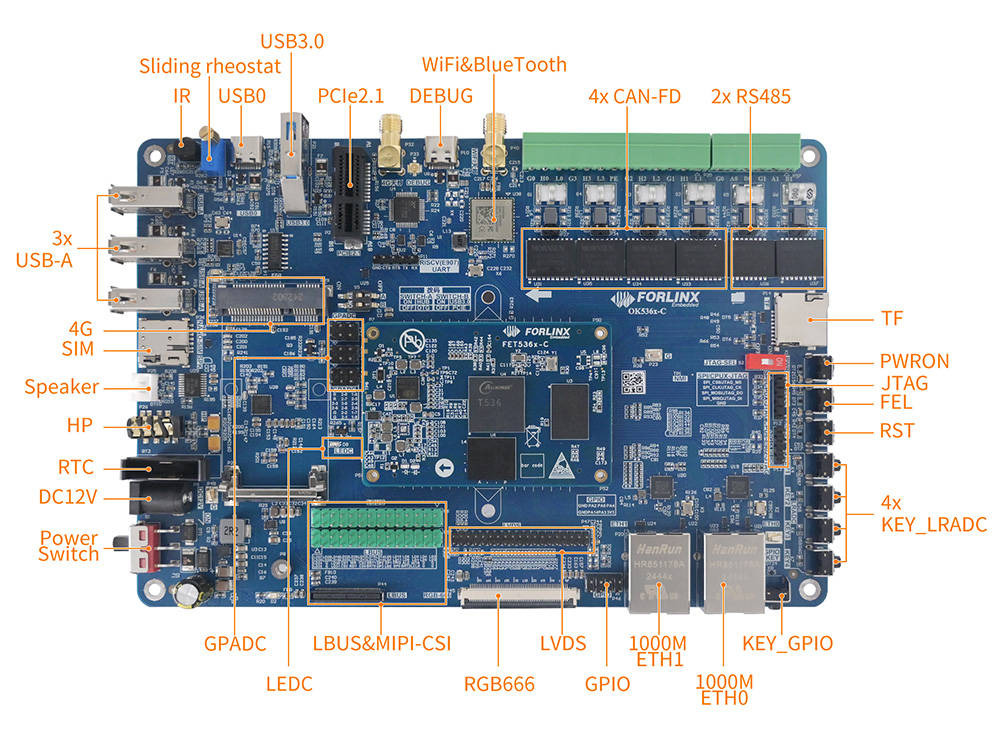

开发板接口图

参数

-

飞凌嵌入式T527核心板已适配Forlinx Desktop 22.04发布在 飞凌嵌入式专区

近日,飞凌嵌入式为FET527N-C核心板适配了全新升级的Forlinx Desktop 22.04操作系统,为用户体验带来了诸多显著的提升——不仅能够享受到更加流畅、稳定的操作体验,还能充分利用Forlinx Desktop 22.04所提供的丰富功能与创新特性提升工作效率与应用兼容性。

OK527N-C开发板运行Forlinx Desktop 22.041、系统与硬件双重赋能

飞凌嵌入式FET527N-C核心板搭载全志T527N处理器,集成了8个ARM Cortex-A55高性能核,同时内置1个RISC-V核和1个DSP核,具有2TOPS的NPU算力,能够为复杂应用和AI需求提供充足的算力支持。Forlinx Desktop 22.04操作系统则通过内核优化和资源管理策略,充分挖掘硬件潜能,与FET527N-C核心板紧密结合,在处理大数据、复杂算法等方面为用户带来更加流畅、高效的操作体验。

2、简单易用,高效开发

在Forlinx Desktop 22.04上,可以使用APT(Advanced Package Tool)作为其软件包管理工具,为用户提供了强大的包搜索、安装、升级和删除功能,让操作更简单,开发更高效。3、国产方案,稳定供应

飞凌嵌入式FET527N-C核心板在关键元件上实现了高度国产化,从内存、存储到电源管理芯片等,均采用了国内领先的技术和产品,有效降低了供应链风险,提升了产品的安全性和可控性(其中,2GB+16GB版的元器件为100%全国产)。FET527N-C核心板具有10~15年的生命周期,确保用户在长期的使用过程中能够获得稳定的硬件支持。

综合看来,FET527N-C核心板适配Forlinx Desktop 22.04,不仅为广大客户朋友提供了多一种选择,更为广大工程师用户带来更好的体验。

-

飞凌嵌入式T113-i开发板RISC-V核的实时应用方案发布在 飞凌嵌入式专区

随着市场对嵌入式设备的功能需求越来越高,集成了嵌入式处理器和实时处理器的主控方案日益增多,以便更好地平衡性能与效率——实时核负责高实时性任务,A核处理复杂任务,两核间需实时交换数据。然而在数据传输方面,传统串行接口尽管成本较低,但其传输速率相对较慢;反之,并行接口虽然传输速度快,但成本却比较高。因此,单芯片多核异构处理器就成为能够满足需求的理想选择。

RISC-V作为一种开源指令集架构,以其简洁性、一致性、可扩展性以及高编译效率,为实时性处理场景提供了强大的支持。将A核与RISC-V核结合作为单芯多核异构方案,可以有效利用RISC-V的这些优势,实现高性能与高实时性的有效结合。

本文将以飞凌嵌入式T113-i开发板为例,为大家介绍RISC-V核的资源和应用案例。

1、飞凌嵌入式T113-i开发板的RISC-V核

飞凌嵌入式T113-i开发板是一款基于全志T113-i工业级处理器开发的高性价比开发板,集成了双核Cortex-A7 CPU、64位玄铁C906 RISC-V和DSP,能够提供高效的计算能力和性价比。尤为值得一提的是,其内置的RISC-V核心作为一款超高能效的实时处理器,主频峰值可达1008MHz,并标准配备了内存管理单元,能够流畅运行RTOS系统或裸机程序,进一步提升了应用灵活性。1.1 RISC-V核的特性

(1) 最高主频可达1008MHz;

(2) 32KB指令缓存;

(3) 32KB数据缓存;

(4) 可运行于超大容量的DDR

... ...1.2 RISC-V核的接口资源

2、应用实例

2.1 SPI数据收发本案例为SPI回环测试,即将SPI的MOSI和MISO两个引脚短接进行数据收发。

(1) 功能介绍

(2) 效果实现

SPI发送和接收的FIFO均为64个,在底层hal库程序中,当数据长度小于64字节时,采用中断方式,当FIFO大于等于64字节时,采用DMA模式。

中断方式传输效果:

DMA方式传输效果:

在DMA传输方式下,SPI速率默认为5Mbit/s,案例中平均传输速率为580.43KB/s,即4.6Mbit/s,接近理论值。

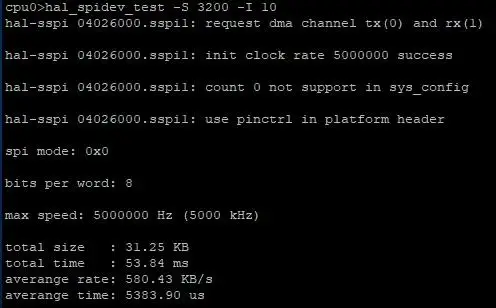

2.2 核间通信RPbuf

RPbuf是全志基于RPMsg所实现一套高带宽数据传输的框架。RPMsg是基于共享内存和Msgbox中断实现的一套核间通信机制,RPMsg除去头部的16字节数据外,单次最多可发送496字节有效数据。因此,全志基于RPMsg实现了一套大数据量传输机制RPbuf,实现原理是在DDR中放置传输的数据,通过RPMsg传输DDR的地址和大小。我们以单次32KB数据传输为例进行展示。

(1) 功能介绍

• VirtIO:一套虚拟化数据传输框架,用于管理共享内存VRING;

• VRING:由VirtIO管理的一个环形共享内存;

• Msgbox:全志提供的一套消息中断机制,已与linux内核中原生的mailbox框架适配;

• MSGBOX_IRQ:Msgbox中断;

• RPMsg:基于VirtIO管理的共享内存所实现一套少量数据传输的框架;

• RPbuf:全志基于RPMsg所实现一套大量数据传输的框架。由上图可知(以RISC-V核向A核发送数据为例),RPbuf首先将数据放置在DDR中,再将缓冲区首地址和大小通过RPMsg发送至A核(RPMsg将缓冲区首地址和大小放入VRING,然后请求Msgbox中断,A核收到这个中断后,在回调函数中使用RPMsg接口函数来从VRING中取出cmd)。

随后A核从cmd handler中获取缓冲区内的地址和长度,最后在应用层读取数据,从而完成双核间的数据传输。

(2) 效果展示

由上图测试效果可以看到,带宽大约为27~30Mbps。

以上就是飞凌嵌入式T113-i开发板RISC-V核部分外设的使用方法,是不是感觉和单片机的开发一样简单方便呢?

-

飞凌嵌入式FET527N-C核心板现已适配Android 13发布在 飞凌嵌入式专区

飞凌嵌入式FET527N-C核心板现已成功适配Android13,新系统的支持能够为用户提供更优质的使用体验。那么,运行Android13系统的FET527N-C核心板具有哪些突出的优势呢?

1、性能与兼容性提升

飞凌嵌入式FET527N-C核心板搭载了全志T527系列高性能处理器,8个ARM Cortex-A55核心以及内置的RISC-V核和DSP核相互协作,共同提供了出色的处理能力和能效比。而Android13系统的适配,则进一步提升了核心板的兼容性。2、应用生态丰富

Android13系统拥有庞大的应用生态支持,无论是娱乐软件、办公工具、工业产品还是其他领域的应用,几乎都能找到适合的应用开发组件。FET527N-C核心板适配Android13系统后,用户将能够享受到这些丰富多样的应用,满足多样化的需求。3、流畅度与稳定性提升

经过深度优化和适配,Android13系统可以在FET527N-C核心板上更加流畅的运行应用,减少了卡顿和延迟现象。同时,Android13系统加强了安全性和隐私保护,为用户的数据安全提供了更加坚实的保障。4、硬件加速特性

Android13系统支持更多的硬件加速特性,这使得FET527N-C核心板在图像处理、视频编码等方面表现出色。配合上FET527N-C核心板强大的性能和丰富的功能接口,能够带来更好的功能表现。5、用户定制化体验

Android13系统的易用性和个性化设置功能,使得用户可以根据自己的需求进行定制,因此能够更好地为HMI赋能,不论是在工控、电力、交通还是医疗行业,都可以让机器更智能地作业,与人类更高效地交互。6、国产化选料保障,稳定供应

此外,FET527N-C核心板在选料上实现了从内存到电源管理芯片再到每一颗阻容件的全面国产化,提升了产品的安全性和竞争力。同时,FET527N-C核心板具有10~15年生命周期,为您的产品提供持续供应保障。总结来说,飞凌嵌入式FET527N-C核心板与Android13系统的结合,为嵌入式设备领域带来了新的发展机遇。这一结合不仅提升了核心板的性能和兼容性,也为用户提供了更为丰富和流畅的使用体验。未来,飞凌嵌入式将继续致力于技术创新和产品研发,为千行百业提供更多高质量的解决方案。

-

FET113i-S核心板已支持RISC-V,打造国产化降本的更优解发布在 飞凌嵌入式专区

FET113i-S核心板是飞凌嵌入式基于全志T113-i处理器设计的国产工业级核心板,凭借卓越的稳定性和超高性价比,FET113i-S核心板得到了客户朋友们的广泛关注。作为一款拥有A7核+RISC-V核+DSP核的多核异构架构芯片,全志科技于近期释放了T113-i的RISC-V核(玄铁C906)资料,飞凌嵌入式也快速进行了适配。

1、什么是RISC-V?

RISC-V是一种基于精简指令集计算(RISC)原则的开放源代码指令集架构(ISA)。它由加州大学伯克利分校在2010年首次发布,并迅速获得了全球学术界和工业界的广泛关注和支持。RISC-V架构以其开放、简洁、可扩展的特性,正逐渐成为全球半导体产业中一股不可忽视的力量。2、T113-i的RISC-V有何优势?

(1)高效能与低功耗

RISC-V架构遵循精简指令集计算机的原则,通过简化硬件设计,提高执行效率,降低了开发成本。T113-i处理器中的RISC-V核能够高效地完成各种计算任务,同时保持较低的功耗,非常适合于资源受限的边缘计算环境。(2)模块化与可扩展性

RISC-V架构设计简洁,采用模块化设计,可以根据需求选择不同的指令集扩展。T113-i处理器中的RISC-V核支持多种标准化扩展指令集,如M(整数乘除法)、A(原子操作)、F/D/Q(单/双/四精度浮点运算)等,可以根据实际应用场景的需要进行灵活组合添加。(3)开放标准与无授权费用

RISC-V是开源的,允许任何人免费使用和扩展,无需授权费用。这极大地促进了技术的共享和创新,降低了产品的开发成本。(4)满足实时性需求

在T113-i的A7核、RISC-V核和DSP核可以同时运行,实现一芯多用,异构同时用。这种设计提高了系统的整体性能,并满足了多样化的应用场景需求。其中,RISC-V核可以匹配对实时性要求较高的应用场景,确保系统能够迅速响应并处理各种实时数据。3、国产化降本的优质之选

已完成RISC-V核适配的飞凌嵌入式FET113i-S核心板含税最低仅需88元;整板工业级品质使其可以应对更多更复杂的应用场景;全面的外设接口资源也让核心板兼具强大易用性和泛用性;此外,100%的元器件国产化率也意味着安全性和竞争力的提升——FET113i-S核心板是助力新基建领域实现国产化替代升级的优质之选。不仅产品本身的优势明显,飞凌嵌入式稳定的供应能力与强大的技术支持能力也是帮助客户项目快速落地、抢占市场先机的有利保障。

-

飞凌嵌入式FET527N-C核心板已适配OpenHarmony4.1发布在 飞凌嵌入式专区

近期,飞凌嵌入式为FET527N-C核心板适配了OpenHarmony4.1系统——进一步提升了核心板的兼容性、稳定性和安全性。

OpenHarmony4.1在应用开发方面展现了全新的开放能力,以更加清晰的逻辑和场景化视角提供给开发者丰富的API接口,应用开发能力得到了极大的丰富。在OpenHarmony4.1的赋能下,开发者能享受“一次开发,多端部署”的高效工作模式,并通过FET527N-C核心板大幅缩短项目开发周期,提升工作效率,更快响应市场变化。

亮点1:八核高性能工业“芯”

飞凌嵌入式为FET527N-C核心板搭载的全志T527N处理器集成了8个ARM Cortex-A55高性能核,同时内置1个RISC-V核和1个DSP核,这意味着它能够提供卓越的处理能力和超高能效比;此外还搭载了2TOPS算力NPU。出色的处理器性能可以满足各种复杂的应用需求,让您的项目更加智能、稳定和高效。

亮点2:100%元器件国产化

在核心板的选料上,飞凌嵌入式FET527N-C核心板实现了从内存到电源管理芯片再到每一颗阻容件的全部国产化。100%的国产化率意味着产品安全性和竞争力的提升,对产业链的优化和发展将起到重要的促进作用。FET527N-C核心板将为更多行业的国产化与智能化升级提供强大稳定的性能支持和长期稳定的供应保障。

亮点3:战略合作伙伴,α阶段参与开发

多年来,飞凌嵌入式与全志科技的合作愈加紧密,双方已基于T3、A40i、T507、T113-i、T527和T536共同推出了多款智能主控产品。并且作为全志战略合作伙伴,飞凌嵌入式在T527系列处理器的α阶段便参与开发,这意味着FET527N-C核心板拥有更高维度、更深层次的技术保障。

除了以上3大亮点外,FET527N-C核心板还经过了飞凌嵌入式实验室严格的工业环境测试,具备高稳定性和可靠性,可为您的产品稳定性保驾护航。对于追求更高效率、更高性能和更好品质的客户来说,适配OpenHarmony4.1的FET527N-C核心板无疑更具优势。

-

T536行业首发!飞凌嵌入式FET536-C/FET536-S核心板惊艳亮相发布在 飞凌嵌入式专区

9月24日下午,全志科技在2024中国国际工业博览会上隆重举办了【T536高性能智慧工业芯片】的全球首发发布会,T536处理器采用4核Cortex-A55+RISC-V架构,主频1.6GHz+600MHz,并搭载2TOPS算力NPU,这款强悍的重磅新品吸引了现场大量观众的关注。

与此同时,飞凌嵌入式基于T536处理器设计开发的FET536-C/FET536-S核心板及配套开发板作为行业首发产品在全志展位惊艳亮相!

1、行业首发,重磅登场

飞凌嵌入式FET536-C/FET536-S核心板作为业内首个搭载T536处理器的核心板产品意义非凡,不仅是飞凌嵌入式研发实力的体现,更意味着飞凌嵌入式与全志科技战略合作伙伴关系的进一步加深。2、高性能,更智能

FET536-C/FET536-S核心板基于全志工业级处理器T536设计,4核Cortex-A55(AMP)+RISC-V MCU,主频1.6GHz+600MHz,搭载2TOPS NPU,支持安全启动、国密算法IP、全通路ECC、AMP、Linux-RT、 Local Bus等。强大的性能以及多核异构架构,能够充分满足工业领域客户对高性能、高实时性主控的需求。3、接口丰富,满足更多领域需求

FET536-C/FET536-S核心板拥有丰富的接口资源,最多可支持CAN-FD×4、UART×17和千兆网×2等等,更够满足工业领域的众多需求,如控制器(PLC/数控机床/运动控制卡)、工业HMI、边缘计算网关、机器人、工业视觉设备、工控一体机、电力集中器、二次继电保护设备、充电桩等。FET536-C/FET536-S核心板惊艳亮相,展现了飞凌嵌入式在高性能智慧工业芯片应用领域的前瞻性布局,也为广大工业客户提供了的新的技术支撑与解决方案。未来,飞凌嵌入式将继续携手全志科技不断探索技术边界,积极创新,共同为工业领域带来更丰富更智能的产品。

FET536-C/FET536-S核心板即将发售,敬请期待!

-

飞凌嵌入式FET527-C核心板上新!低成本、高算力、新选择发布在 飞凌嵌入式专区

为了满足更多客户对于高性能、多架构、国产化主控的应用需求,飞凌嵌入式继FET527N-C核心板后,新近推出FET527-C核心板,为客户提供成本更优的主控新选择。

1、精准定位,助力更多应用

相较于已经上市的FET527N-C核心板,FET527-C核心板在设计上更加聚焦于那些对计算性能有高要求,但不直接涉及AI处理任务的工业场景。通过精简NPU实现了成本的优化,为用户提供了更加灵活且经济的选择。2、强大性能,满足多样需求

飞凌嵌入式FET527-C核心板搭载了8个ARM Cortex-A55高性能核心,数据处理能力达36.7KDMIPS。搭载的T527处理器采用新一代ARM G57 MC1 GPU,高内存带宽、低功耗,曼哈顿跑分高达14,支持高清编解码,支持4K+1080P双屏异显,这些强大的硬件配置确保了它在处理复杂工业任务时的高效、全能与稳定。无论是数据计算、任务处理还是其他高性能要求的应用场景,飞凌嵌入式FET527-C都能轻松应对,满足多样化的工业需求。

3、性价比之选,助力工业升级

飞凌嵌入式FET527-C核心板宽温版(配置2GB+32GB)的含税价格仅为298元起,工业级版本含税价318元起。这一极具竞争力的价格,使FET527-C核心板成为工业领域客户实现设备智能化升级和性能优化的高性价比之选。(注:FET527-C核心板2GB+16GB工业级现货发售中,更多配置将在10月中旬上线)

-

飞凌嵌入式技术创新日深圳站,8月26日见!发布在 飞凌嵌入式专区

飞凌嵌入式技术创新日(深圳站)将于8月26日举行,一场嵌入式前沿科技的高端局就在眼前。届时,将有多位重量级技术大咖出席,为大家分享最新的研究成果、独到的行业见解和典型的应用案例,紧密结合当前行业热点和前沿技术,干货满满,为您的业务开拓和项目开发助力。

精彩回顾

飞凌嵌入式技术创新日(北京站)

6月28日,飞凌嵌入式在北京举办了首场技术创新日活动,汇聚了近300位嵌入式技术领域的专家和企业代表,共享嵌入式技术的盛宴。现场展示了飞凌嵌入式丰富的产品线、实用的选型工具、全面的软件资源、ElfBoard教育品牌的成果以及合作伙伴NXP的创新应用方案等等内容,吸引了来宾们的驻足围观和交流。

在主会场,8位技术专家与嘉宾也带来了精彩的干货分享,深入解析了飞凌嵌入式全矩阵产品的特点和优势,分享了开源操作系统在嵌入式领域的应用前景,介绍了嵌入式行业案例和技术应用,讲解了异构多核处理器和机器学习在嵌入式系统中的应用......不仅展示了飞凌嵌入式的行业优势,也让与会者深刻感受到了嵌入式技术在千行百业中的广泛应用和巨大潜力。

无论是外场的展区还是内场的主题分享会,都体现了飞凌嵌入式对嵌入式技术发展的深刻理解和对技术创新的不懈追求,同时,也为客户朋友和行业伙伴提供了一个交流学习的机会。飞凌嵌入式技术创新日(深圳站),诚邀各位客户朋友和行业伙伴共襄盛会,共创嵌入式技术的美好未来!

时间:2024年8月26日

时间:2024年8月26日

地点:深圳威尼斯英迪格酒店一楼威尼斯宴会厅

地点:深圳威尼斯英迪格酒店一楼威尼斯宴会厅

(世界之窗地铁站A口东行200米) -

加入AWOL「体验官」 免费玩转T527开发板发布在 飞凌嵌入式专区

1. 八核高性能工业级国产芯

T527系列是全志科技为工业应用等领域研发的新一代国产处理器,有T527、T527N等多个不同型号,该处理器集成了8个ARM Cortex-A55高性能核,数据处理能力达36.7KDMIPS,内置1个RISC-V核和1个DSP核,HiFi4 DSP支持异构音效处理;还拥有2TOPS算力NPU,支持INT8/INT16,主流常用模型框架。

作为战略合作伙伴,飞凌嵌入式与全志科技多年来携手同行,此前已共同推出了FET113i-S、FETT507-C、FETA40i-C和FETT3-C共4款核心板产品,并且凭借稳定可靠的工业级品质和高性价比受到了市场的一致认可。

为了充分满足工业领域对高性能和AI算力日益增长的需求,双方再次深化合作,推出全新FET527N-C国产工业级核心板和OK527N-C开发板,为千行百业的智能化升级提供强大稳定的性能支持!

2. 报名通道

https://wj.qq.com/s2/14681348/aa11/

OK527N-C开发板产品体验官开启招募!

扫描上方二维码立即申请

就有机会免费玩转OK527N-C开发板

3. 体验官「特权」

1️⃣ “产品体验官”仅限5个名额;

2️⃣ 免费获得OK527N-C开发板(2GB+16GB)。

4. 入选要求

1️⃣ 活动面向从事嵌入式相关开发工作的工程师用户;

2️⃣ 有创作和分享的意愿与能力,在社媒平台发布过新品评测报告或项目笔记等内容,具有参考价值或可传播性。

5. 活动说明

1️⃣ 请按要求完整填写申请信息,更详实的“申请理由”将更有助于您入选;

2️⃣ 须在拿到板卡后1个月内撰写3篇内容,主题可参考以下方向:

开箱报告:包括产品开箱分享、板卡点亮和跑分测试等内容;

开发例程:基于OK527N-C开发板的开发案例,结合产品的特性和优势进行实践;

3️⃣ 完成内容并发布到全志在线论坛并分享到活动期间组建的活动群中;

4️⃣ 体验官发布的优质内容将会转载发布于飞凌嵌入式的官方自媒体平台;

5️⃣飞凌嵌入式的工作人员将通过电话与您联系,请确保预留正确的联系方式,并保持电话畅通。

6. 活动时间

1️⃣ 报名时间

2024年5月24日~2024年6月09日;

2️⃣ 发货时间

2024年6月15日

(报名期间飞凌嵌入式工作人员将与申请者进行沟通,具体发货时间以实际为准);

3️⃣ 试用及报告提交时间

2024年6月20日~2024年7月20日。

-

飞凌嵌入式FET113i-S核心板在国产FTU中的适配性分析发布在 飞凌嵌入式专区

智能电网建设的不断推进,使配电自动化成为了提升电网运行效率、保障供电质量的关键技术。在配电自动化系统中,馈线终端单元(FTU)作为连接电网与用户的重要节点,承担着实时监控、故障检测与隔离、远程控制等多项关键任务。

国内市场对于FTU的需求主要包括以下几个方面:主控的国产化、实时的故障诊断和保护控制、搭载可扩展的Linux系统以及低成本。由于FTU的性能直接关系到电网的安全与稳定,因此选择一款合适的FTU主控方案至关重要。

FET113i-S核心板在FTU中的适配性

针对以上需求,飞凌嵌入式推出的FET113i-S核心板可以成为电力FTU的理想主控方案。以下是FET113i-S核心板在FTU应用中的适配性分析:

1. 100%的元器件国产化

在核心板的选料上,飞凌嵌入式FET113i-S核心板实现了从内存、存储、电源管理芯片到每一颗阻容件的全部国产化,安全性和竞争力大大提升,能够满足电力行业对于主控的国产化要求。

2. 业内率先适配FTU所需接口和算法

FET113i-S核心板搭载的全志T113-i处理器集成了双核Cortex-A7 CPU、64位玄铁C906 RISC-V CPU和DSP,值得一提的是,飞凌嵌入式为DSP核率先适配了国产FTU所需的接口和FFT算法,客户无需进行繁琐的适配工作,即可将FET113i-S核心板直接应用于电力FTU中。同时,FFT算法的适配也确保了电力FTU能够准确、快速地分析电网的频谱和谐波成分,为故障检测和定位提供有力支持。

T113-i应用处理器框图3. 搭载可扩展的Linux系统

电力行业的特殊性决定了它对系统的稳定性和安全性有非常高的要求。Linux操作系统是一种开源的操作系统,具有稳定性高、安全性强、灵活性强等特点,因此在电网管理中有广泛的应用。飞凌嵌入式FET113i-S核心板运行Linux 5.4.61操作系统,可以提高FTU的效率和安全性,为电网运行提供有效支持。

4. 高性价比降低整体成本

FET113i-S核心板基础版本的配置就达到了【256MB+256MB】,且含税仅需88元。相较之下,飞凌嵌入式FET113i-S核心板在同类产品中更具性价比,优势更突出!

不仅FET113i-S核心板的产品力优势明显,飞凌嵌入式稳定的供应能力与强大的技术支持能力也是帮助客户项目快速落地、抢占市场先机的有利保障。综合看来,飞凌嵌入式FET113i-S核心板集诸多优势于一身,能够成为电力FTU的理想主控方案。

-

新品即将上市 | FET527N-C国产工业级高性能核心板先睹为快发布在 T Series

作为战略合作伙伴,飞凌嵌入式与全志科技多年来携手同行,共同推出了多款经典的智能主控产品。为了充分满足工业领域对高性能和AI算力日益增长的需求,双方再次深化合作,现联合推出全新FET527N-C国产工业级核心板,为千行百业的智能化升级提供强大稳定的性能支持!

1、FET527N-C核心板

飞凌嵌入式FET527N-C核心板基于全志T527系列高性能处理器开发设计,集成了8个ARM Cortex-A55高性能核,同时内置1个RISC-V核和1个DSP核。具有2TOPS算力的NPU,可为您的AI应用赋能。核心板采用板对板连接方式,可插拔式设计便于产品的安装与维护。产品通过飞凌嵌入式实验室严苛的工业环境测试,为您的产品稳定性保驾护航。同时,FET527N-C核心板具有10~15年生命周期,可为您的产品提供持续的供应保障。

2、八核超高性能工业级国产芯片

T527系列是全志科技为工业应用等领域研发的新一代国产处理器,有T527、T527N等多个不同型号,该处理器集成了8个ARM Cortex-A55高性能核,数据处理能力达36.7KDMIPS,内置1个RISC-V核和1个DSP核,HiFi4 DSP支持异构音效处理。

3、新一代低功耗ARM GPU

T527系列高性能处理器搭载新一代ARM G57 MC1 GPU,高内存带宽、低功耗,曼哈顿跑分高达14,综合算力比G52大幅提升约50%。

4、2TOPS算力NPU,支持INT8/INT16

飞凌嵌入式FET527N-C核心板拥有2TOPS算力NPU,支持INT8/INT16,主流常用模型框架,支持Conv、Activation、Pooling等40种算子以及自定义算子。

5、高清解码,显示增强

FET527N-C核心板支持H.264编解码、H.265解码,最大4K分辨率;RGB、MIPI DSI、LVDS(Dual link)、eDP组合兼容,支持4K+1080P双屏异显,满足多种场景多样化显示需求。

6、持续更新的用户资料

软硬件开发资料、常见问题手册、引脚复用对照表、硬件手册、测试例程、底板原理图等资料一应俱全,让您的开发更简单,生产更便捷。

7、广泛的行业应用

飞凌嵌入式FET527N-C核心板广泛适用于商显/收银、云电脑、机器人、工业智能、边缘计算网关、后装中控、商用车、工控机等众多领域,加之飞凌嵌入式具有竞争力的价格优势以及完备的售后技术支持,可助力您的产品快速上市,走在行业前沿。

8、OK527N-C开发板接口图

FET527N-C核心板通过4组80Pin板对板连接器与底板相连接组成OK527N-C开发板,丰富的功能接口可为您的开发测试提供极大便利。

9、FET527N-C核心板详细参数

飞凌嵌入式FET527N-C核心板即将上市,欢迎大家的持续关注。

-

飞凌嵌入式A40i-H核心板已适配“矿鸿OS”发布在 飞凌嵌入式专区

近日,飞凌嵌入式基于全志科技A40i-H打造的FETA40i-C核心板成功完成了“矿鸿OS”的系统适配,嵌入式核心板与“矿鸿”操作系统的结合与应用,将进一步推动煤矿行业的数字化、智能化进程。

矿鸿OS(矿山鸿蒙系统)是华为和国家能源集团联合推出的鸿蒙矿山操作系统,这是鸿蒙操作系统在消费者业务应用后,首次在工业领域实现商用。

矿鸿OS通过独特的“软总线”技术以及统一的HCP协议等关键技术,将不同厂家的设备互联互通,助力煤矿企业建设“智能感知、智能决策、自动执行”的煤矿智能化体系,从而逐步达成采煤、运煤、管理的自动化,最终实现无人化。

作为国内较早专业从事嵌入式技术的企业,飞凌嵌入式始终致力于为千行百业提供类型丰富、性能卓越的核心板产品。本次适配矿鸿OS的FETA40i-C核心板产品,已在煤矿行业有了多年的应用,丰富的功能接口与稳定的工业级品质也为矿鸿OS在极端环境中的稳定运行提供了坚实的基础。

飞凌嵌入式与矿鸿OS的结合不仅帮助矿企简化了系统集成的过程,降低了集成成本,还使得矿企能够更快速地部署和实施智能化解决方案。选择飞凌嵌入式,就是选择一个更智能、更高效、更安全的矿业解决方案。

-

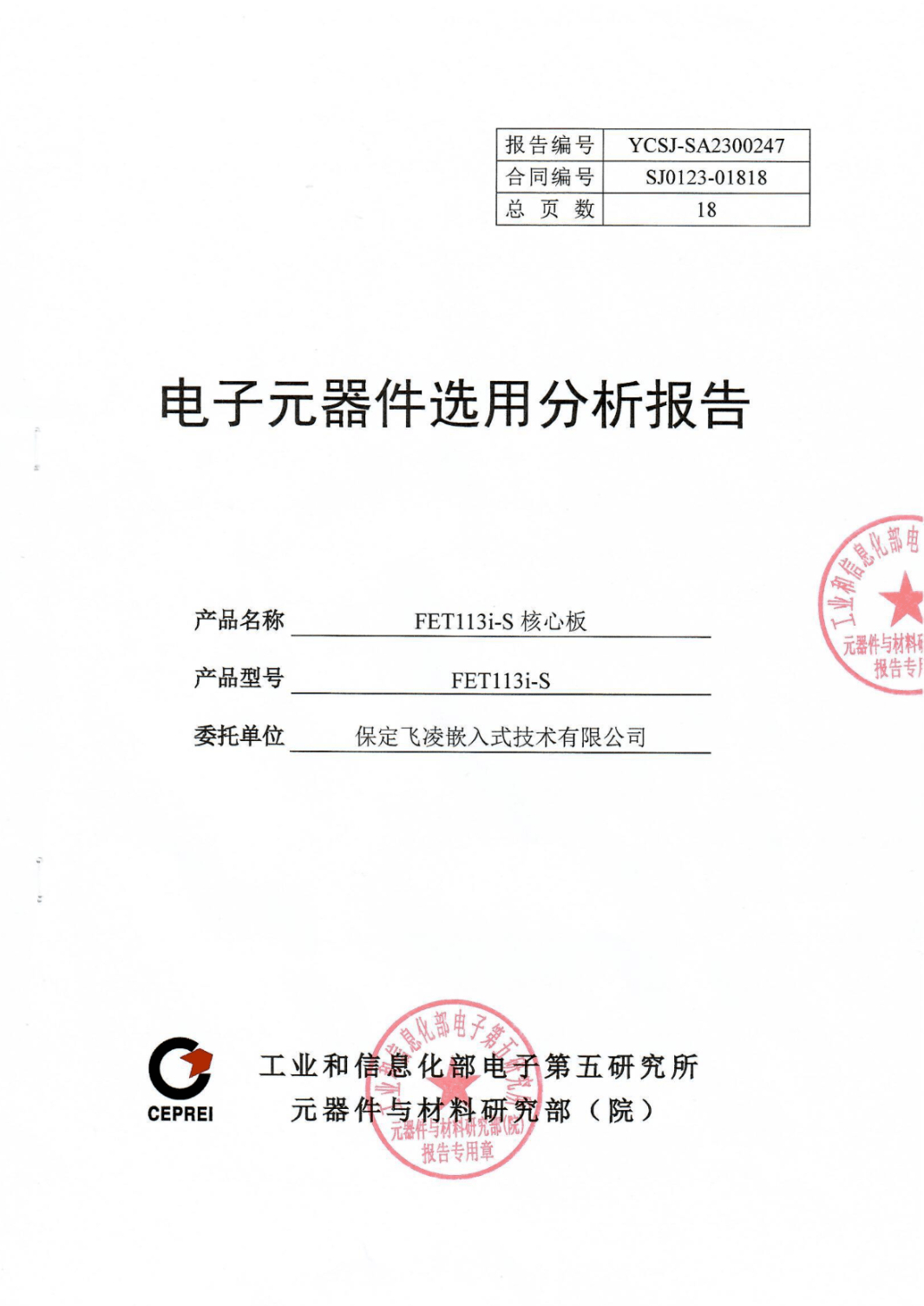

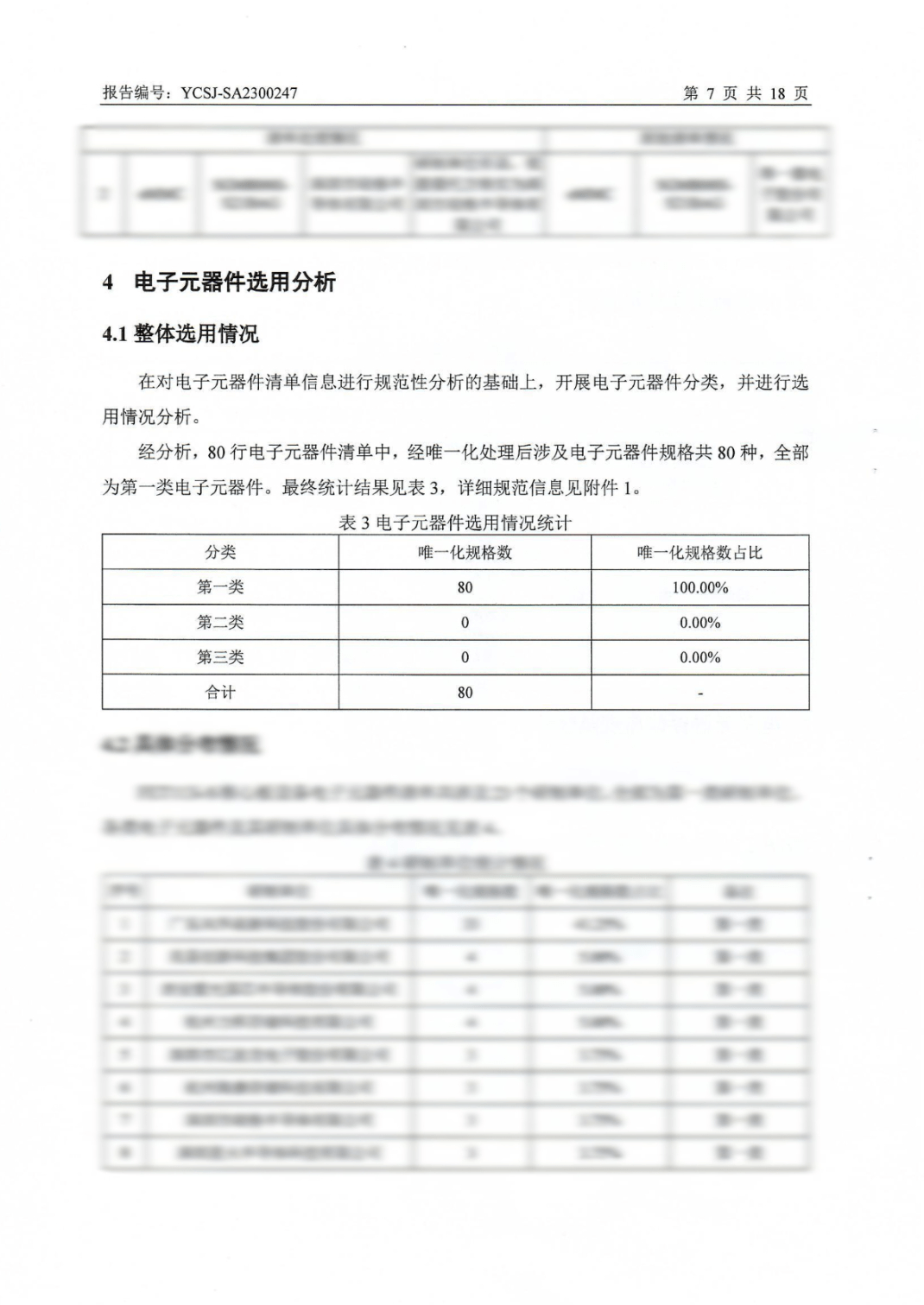

【权威认证】飞凌嵌入式FET113i-S核心板国产化率达100%发布在 飞凌嵌入式专区

经中国赛宝实验室的严格认证,飞凌嵌入式FET113i-S核心板的电子元器件国产化率达100%——这款超高性价比的全国产核心板为新基建领域的国产化替代升级注入了新动力。

关于【中国赛宝实验室】

中国电子产品可靠性与环境试验研究所(工业和信息化部电子第五研究所、中国赛宝实验室)始建于1955年,是中国最早从事可靠性研究的权威机构。作为工业和信息化部的直属单位,为部的行业管理和地方政府提供技术支撑,为电子信息企业提供技术支持与服务,每年服务企业过万家。

FET113i-S核心板

国产化降本升级趋势下更理想的选择

飞凌嵌入式FET113i-S核心板基于全志T113-i工业级处理器开发设计,主频1.2GHz,集成双核Cortex-A7 CPU、64位玄铁C906 RISC-V CPU 和 DSP,不仅能够提供高效的计算能力,还具备丰富的多媒体功能和齐全的接口资源,兼具强大易用性和泛用性,并且整板工业级品质使其可以应对更多更复杂的应用场景。同时,100%的国产化率也让FET113i-S核心板更具优势——不仅安全性和竞争力大大提升,对产业链的优化和整体发展也有着重要的促进作用,在新基建尤其是工业、电力、交通等关键领域,FET113i-S都展现出了极高的实用价值和广阔的市场前景。

除了产品本身的优势外,飞凌嵌入式强大的技术支持能力以及稳定的供应能力也是帮助客户项目快速落地的有利保障。

-

四大优势!这款T113-i全国产核心板更值得关注发布在 飞凌嵌入式专区

为了在「新基建」的浪潮中跑出新的中国速度,“国产化降本”已成为很多企业的选择,如果要选一款兼具“更低价、更灵活、更全能、全国产”多重优势的全能型SoM,飞凌嵌入式推出的FET113i-S核心板就是目前非常合适的选择。

1、更低价

飞凌嵌入式FET113i-S核心板基础版本的配置就达到了【256MB+256MB】,且含税仅需88元;更高配置的【512MB+8GB】版本含税价格为138元。相较之下,飞凌嵌入式FET113i-S核心板在同类产品中更具性价比,优势更突出!

2、 更灵活

FET113i-S核心板基于全志T113-i工业级处理器开发设计,配备多核心多架构——集成双核Cortex-A7 CPU、64位玄铁C906 RISC-V CPU和DSP,可通过软件控制核心的开启及关闭,A7核、RISC-V核、DSP核可同时运行。

Cortex-A7核用于运算控制,DSP核适用于多媒体、数字信号处理等应用,而RISC-V核又可以匹配对实时性要求较高的应用场景,一芯多用,异构同时用,使用更灵活。

3 、更全能

飞凌嵌入式FET113i-S核心板整板工业级品质,-40℃~+85℃的工作温度使其可以应对更多更复杂的应用场景。

不仅如此,FET113i-S核心板还拥有丰富的多媒体功能。支持H.265、MPEG-4、JPEG解码以及JPEG/MJPE格式编码;支持8位并行CSI、CVBS视频输入和CVBS、RGB、双通道LVDS、四通道MIPI DSI视频输出;通过对DSP的支持,也更适用于音频相关应用。

此外,FET113i-S还具备全面的外设接口资源,兼具强大易用性和泛用性,USB、SDIO、UART、SPl、CAN、Ethernet等一应俱全,可以轻松拓展出丰富的功能,满足更多领域对主控平台的功能需求。

4 、全国产

在核心板的选料上,飞凌嵌入式FET113i-S实现了从内存、存储、电源管理芯片到每一颗阻容件的全部国产化。100%的国产化率不仅意味着安全性和竞争力的提升,对产业链的优化和整体发展也有着重要的促进作用——FET113i-S核心板是助力新基建领域实现国产化替代升级的优质之选。

总结

拥有 更低价、更灵活、更全能、全国产 等多重优势的飞凌嵌入式FET113i-S核心板无疑是国产化降本升级的趋势下更为理想的主控选择。在新基建尤其是工业、电力、交通等关键领域,FET113i-S核心板展现出了极高的实用价值和广泛的市场前景。

不仅产品本身的优势明显,飞凌嵌入式稳定的供应能力与强大的技术支持能力也是帮助客户项目快速落地、抢占市场先机的有利保障。

-

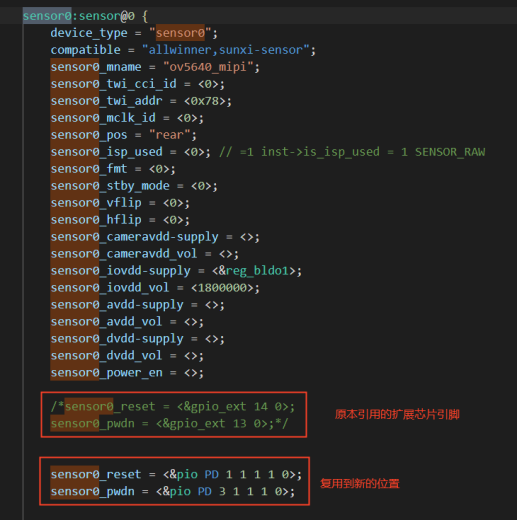

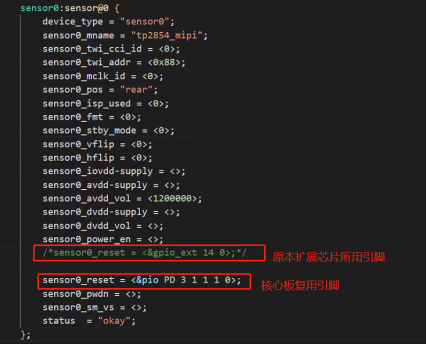

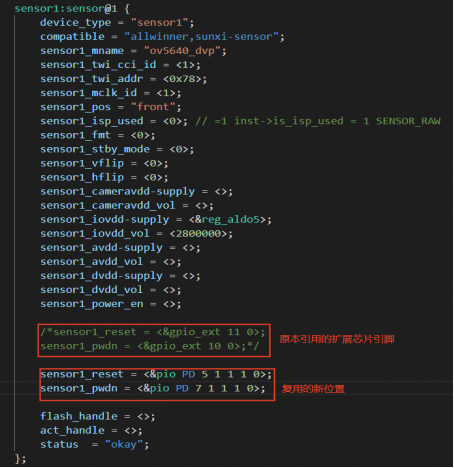

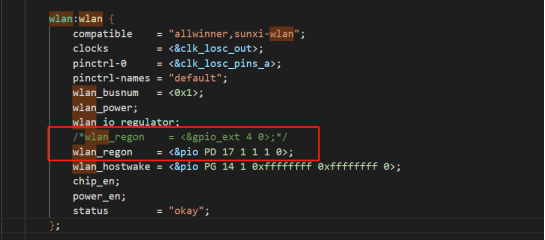

【开发教程】 OKT507去掉IO扩展芯片,保留扩展引脚功能发布在 飞凌嵌入式专区

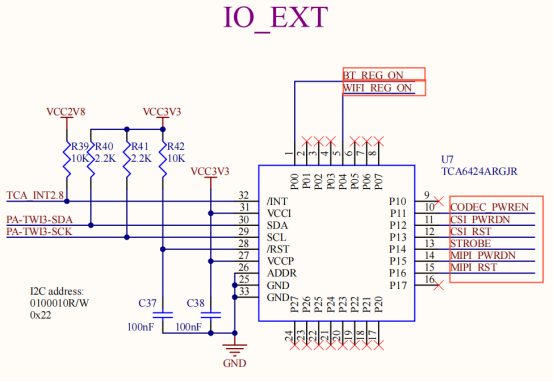

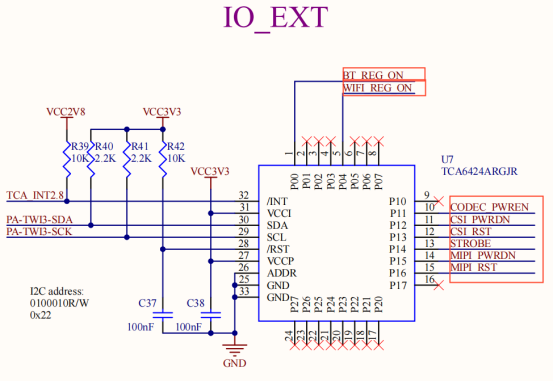

飞凌嵌入式推出的OKT507-C作为一款广受欢迎的开发板拥有丰富的接口资源,而实际上OKT507-C的CPU引脚资源是比较紧缺的,那么它是如何实现这么丰富的接口资源呢?

答案就是飞凌使用了一个IO扩展芯片——TCA6424A。这是一个24 位 I2C 和系统管理总线 (SMBus), 输入输出(I/O) 扩展器有中断输出、复位和配置寄存器。

受当前国际形势的影响,芯片行业形势非常严峻,为了满足更多客户需求,在降低成本的同时尽可能保留更多功能,飞凌为大家带来OKT507-C去掉IO扩展芯片后保留扩展引脚功能的实现的方法。

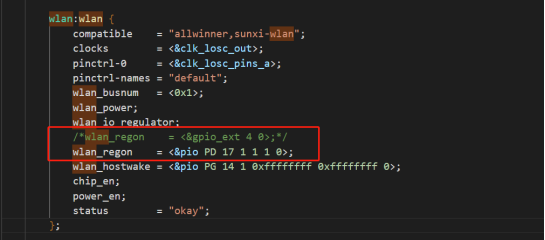

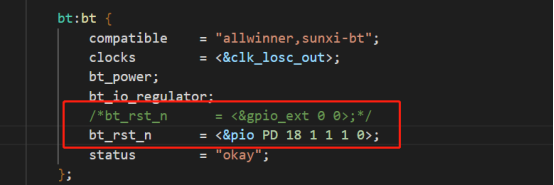

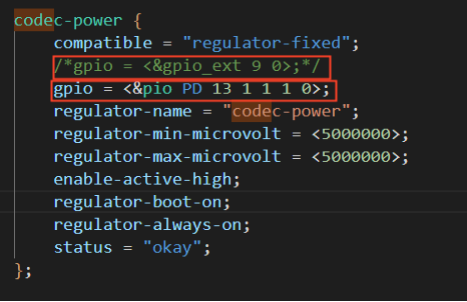

扩展芯片上的IO口被WiFi、蓝牙、MIPI摄像头TP2854、DVP摄像头和line-out口电源使能引脚引用,若想保留这些功能,就要使用核心板其他可复用为这些功能的引脚。

本文将选用开发板的LCD功能引脚来重新复用为这些功能,用户可根据自己的实际功能需求情况选择。方法参考如下:

1. 选用引脚

对应功能引脚如下表所示:

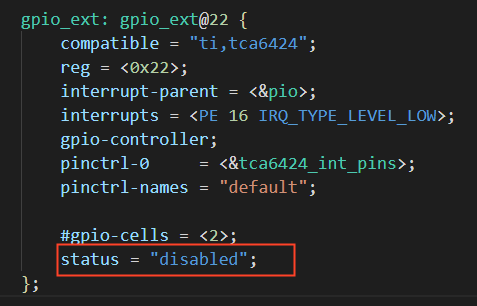

2. 关掉gpio_ext及复用引脚原来功能

修改设备树,将LCD功能关闭后,该组引脚即可用作普通的GPIO。修改路径如下:

vi OKT507-linux-sdk/kernel/linux4.9/arch/arm64/boot/dts/sunxi/OKT507-C Common.dtsi2.1 关掉IO扩展芯片功能

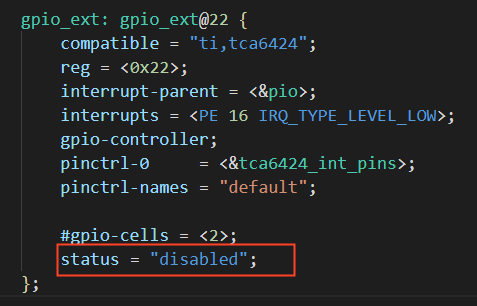

因为扩展芯片已经拆除,所以要关掉扩展芯片节点。

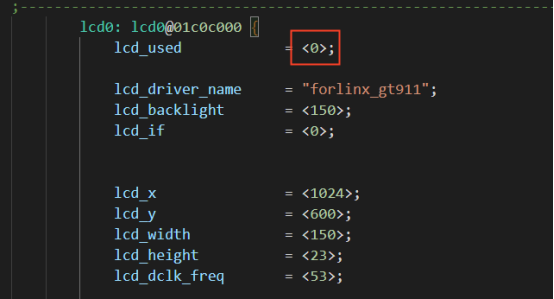

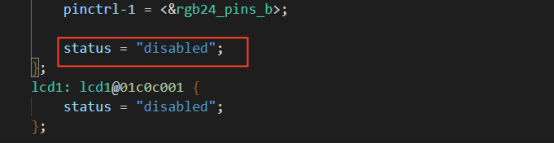

2.2 关闭需要复用引脚功能

关闭LCD功能,本文以选用LCD上的引脚用作功能复用,用户需根据实际情况关闭所用引脚功能。

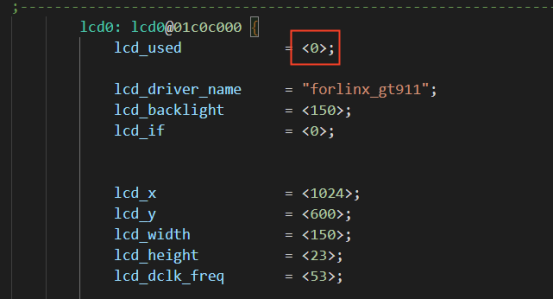

将lcd_used 改为 0

lcd0节点添加 status = “disabled”;

3. 更改设备节点中引用的GPIO

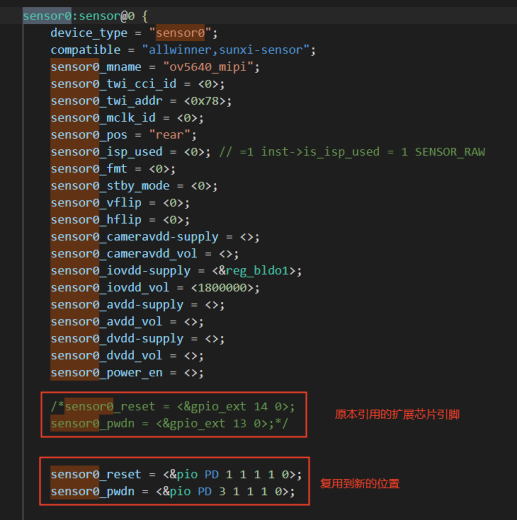

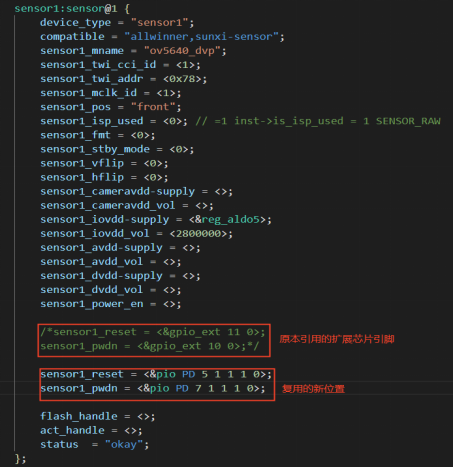

3.1 MIPI-5640引脚配置

路径如下:

vi OKT507-linux-sdk/kernel/linux-4.9/arch/arm64/boot/dts/sunxi/OKT507-C-Common.dtsi

3.2 TP2854引脚配置

路径如下:

vi OKT507-linux-sdk/kernel/linux-4.9/arch/arm64/boot/dts/sunxi/OKT507-C-Common-TP2854M.dtsi

需要注意的是,MIPI5640和TP2854共用一个MIPI接口,两个功能都用到了MIPI_PWRDN引脚,实际使用时只能选择一种功能,因此本文在两个功能测试时选的同一个引脚。

3.3 DVP-5640引脚配置

路径如下:

vi OKT507-linux-sdk/kernel/linux-4.9/arch/arm64/boot/dts/sunxi/OKT507-C-Common.dtsi

3.4 WiFi引脚配置

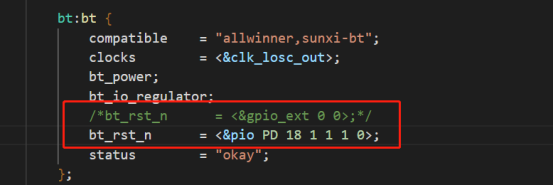

路径如下:

vi OKT507-linux-sdk/kernel/linux-4.9/arch/arm64/boot/dts/sunxi/OKT507-C-Common.dtsi

3.5 蓝牙引脚配置

路径如下:

vi OKT507-linux-sdk/kernel/linux-4.9/arch/arm64/boot/dts/sunxi/OKT507-C-Common.dtsi

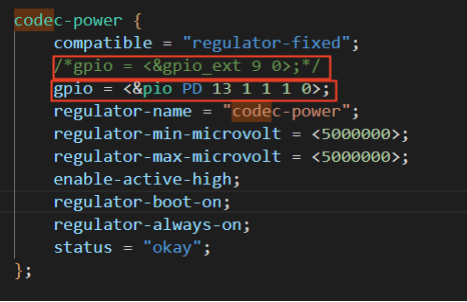

3.6 音频引脚

路径如下:

vi OKT507-linux-sdk/kernel/linux-4.9/arch/arm64/boot/dts/sunxi/OKT507-C-Common.dtsi

以上就是OKT507-C开发板去掉IO扩展芯片后保留扩展引脚功能的实现的方法,具体的测试方式请参考《OKT507-C_Linux_用户使用手册》,您在公众号首页咨询客服或联系您的销售工程师即可获取。

-

只需4步,让A40i-H开发板的Linux系统拥有中文显示发布在 飞凌嵌入式专区

如果你试着在Linux系统里面输入中文,那么将会有一片乱码呈现在你面前,这是因为Linux系统的默认语言是英文。但是如果可以显示中文的话,那么在使用过程中的便利程度一定会大大提升。今天小编就通过飞凌嵌入式的OKA40i-C开发板来为大家演示让Linux系统显示中文的修改方法。

STEP 1

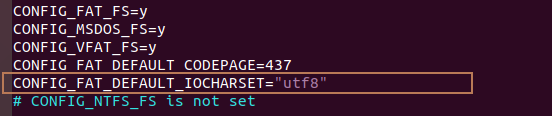

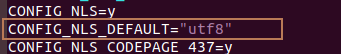

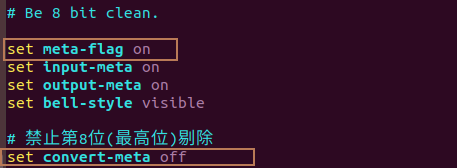

如果之前使用的是全源码编译方式对源码进行编译处理的,就可以直接往下走;如果之前有更改过源码部分,且使用的是单步编译,则需要重新解压一份OKA40i-C开发板的源码,进入该源码的lichee文件夹,执行sudo ./build.sh进行一次全编译,耗时会有点长,需要耐心的等待。STEP 2

在新的源码全编译的过程中,到之前使用的源码里面做一些准备工作吧;要是更改过程中遇到只读等权限问题,打开的时候加上sudo就好了。- 首先在lichee下面找到linux-3.10/.config这个配置文件,将里面的iso8859-1全部替换成utf8,就像下面这样,一共有两处。行前面的“-”表示去掉,“+”表示添加上。

FAT使用的默认输入/输出字符集:

-CONFIG_FAT_DEFAULT_IOCHARSET="iso8859-1" +CONFIG_FAT_DEFAULT_IOCHARSET="utf8"

挂载文件系统时使用的默认NLS

-CONFIG_NLS_DEFAULT=" iso8859-1" +CONFIG_NLS_DEFAULT="utf8"

-

out/sun8iw11p1/linux/common/buildroot/target/etc/inputrc

在上方lichee中的文件中添加两行命令:

-

lichee/out/sun8iw11p1/linux/common/buildroot/target/root

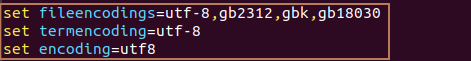

然后到上方路径下创建一个.vimrc文件,打开.vimrc文件,在里面添加上三行命令:

set fileencodings=utf-8,gb2312,gbk,gb18030

set termencoding=utf-8

set encoding=utf8

STEP 3

现在,新的源码已经全部编译完成了,在新源码的里面找到busybox-1.25.1这个文件夹。进入以下路径:lichee/out/sun8iw11p1/linux/common/buildroot/build/busybox-1.25.1

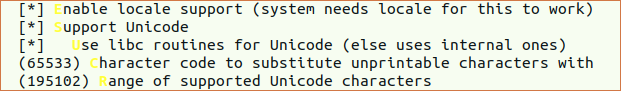

- 执行make menuconfig ARCH=arm进入busybox的图形化编辑界面。

Busybox Settings ---> General Configuration ---> [*] Enable locale support (system needs locale for this to work) [*] Support Unicode [*] Use libc routines for Unicode (else uses internal ones) (65533) Character code to substitute unprintable characters with (195102) Range of supported Unicode characters

更改好之后一路Exit退出,最后选择yes保存配置。

- 然后更改busybox-1.25.1文件夹路径下的文件

libbb / printable_string.c,

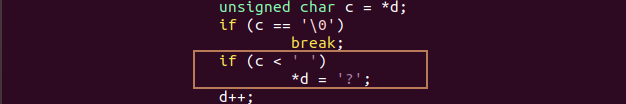

搜索0x7f,删除以下两行:

将这里更改为

-if (c < ' ' || c >= 0x7f) +if (c < ' ')

- 更改libbb/unicode.c文件,先找到这样一段:static char* FAST_FUNC。然后将里面的1022行和1030行进行修改:

将*d++ = (c >= ' ' && c < 0x7f) ? c : '?';

修改为*d++ = (c >= ' ') ? c : '?';

将if (c < ' ' || c >= 0x7f)

修改为if (c < ' ')

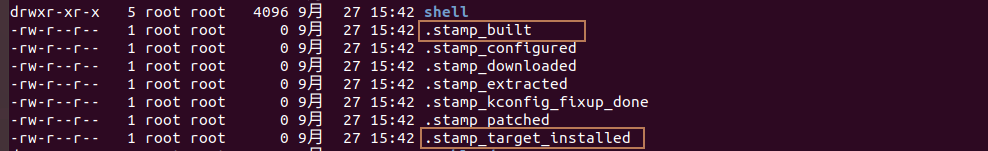

修改完成之后,删除.stamp_built文件和.stamp_target_installed文件,返回到lichee文件夹下面,重新进行全编译sudo ./build.sh操作。

在out/sun8iw11p1/linux/common/buildroot/target/bin路径后面会生成一个busybox的可执行文件,将这个叫busybox的可执行文件替换到需要中文源码的相同路径下面——

lichee/out/sun8iw11p1/linux/common/buildroot/target/bin里面。

STEP 4

最后,在需要中文的那一份源码里面进行内核编译,打包文件系统,打包镜像操作,再将镜像烧录到OKA40i-C开发板里面就可以显示中文了。sudo ./build.sh -m kernel

sudo ./build.sh -m pack_rootfs

sudo ./build.sh pack

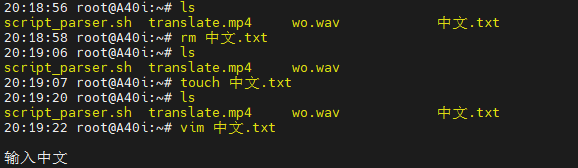

最后我们来验证一下。可以看到此时已经可以直接进行中文输入了,并且和windows对接的中文文件可以直接显示查看。

结语

Linux系统中文显示的更改其实就是更改内核的字符集和打开busybox的显示封锁,第一次编译好后,以后需要中文的busybox可以直接使用这次的busybox进行替换,节省了很多的工作量。更改完成之后就可以在OKA40i-C开发板的Linux系统上面编辑和查看中文了。 -

T507-H技术帖 | 去掉IO扩展芯片后保留扩展引脚功能的实现方法发布在 飞凌嵌入式专区

飞凌嵌入式推出的OKT507-C作为一款广受欢迎的开发板拥有丰富的功能接口,而实际上OKT507-C开发板的CPU引脚资源是比较紧缺的,那么它究竟是如何提供如此丰富的接口资源的呢?答案就是IO扩展芯片——TCA6424A。

这是一个24 位 I2C 和系统管理总线 (SMBus), 输入输出(I/O) 扩展器有中断输出、复位和配置寄存器。为了满足更多客户需求,在降低成本的同时尽可能保留更多功能,飞凌嵌入式为大家提供了OKT507-C去掉IO扩展芯片后保留扩展引脚功能的实现的方法。

扩展芯片上的IO口被WiFi、蓝牙、MIPI摄像头TP2854、DVP摄像头和line-out口电源使能引脚引用,若想保留这些功能,就要使用核心板其他可复用为这些功能的引脚。

本文将选用OKT507-C开发板的LCD功能引脚来重新复用为这些功能,用户可根据自己的实际功能需求情况选择。方法参考如下:

一、选用引脚:

对应功能引脚如下表所示:

二、关掉gpio_ext及复用引脚原来功能

修改设备树,将LCD功能关闭后,该组引脚即可用作普通的GPIO。修改路径如下:

vi OKT507-linux-sdk/kernel/linux4.9/arch/arm64/boot/dts/sunxi/OKT507-C Common.dtsi-

关掉IO扩展芯片功能:

-

关闭需要复用引脚功能:

关闭LCD功能,本文以选用LCD上的引脚用作功能复用,用户需根据实际情况关闭所用引脚功能。

将lcd_used 改为 0

lcd0节点添加 status = “disabled”;

三、更改设备节点中引用的GPIO

-

MIPI-5640引脚配置:

路径如下:

vi OKT507-linux-sdk/kernel/linux-4.9/arch/arm64/boot/dts/sunxi/OKT507-C-Common.dtsi

-

TP2854引脚配置:

路径如下:

vi OKT507-linux-sdk/kernel/linux-4.9/arch/arm64/boot/dts/sunxi/OKT507-C-Common-TP2854M.dtsi

需要注意的是,MIPI5640和TP2854共用一个MIPI接口,两个功能都用到了MIPI_PWRDN引脚,实际使用时只能选择一种功能,因此本文在两个功能测试时选的同一个引脚。

-

DVP-5640引脚配置:

路径如下:

vi OKT507-linux-sdk/kernel/linux-4.9/arch/arm64/boot/dts/sunxi/OKT507-C-Common.dtsi

-

WiFi引脚配置:

路径如下:

vi OKT507-linux-sdk/kernel/linux-4.9/arch/arm64/boot/dts/sunxi/OKT507-C-Common.dtsi

-

蓝牙引脚配置:

路径如下:

vi OKT507-linux-sdk/kernel/linux-4.9/arch/arm64/boot/dts/sunxi/OKT507-C-Common.dtsi

-

音频引脚:

路径如下:

vi OKT507-linux-sdk/kernel/linux-4.9/arch/arm64/boot/dts/sunxi/OKT507-C-Common.dtsi

以上就是OKT507-C开发板去掉IO扩展芯片后保留扩展引脚功能的实现的方法,本文使用的思路和方法仅供参考使用,其它Arm开发板虽然芯片不同,但思路和方法有很多的共性,希望对您在板卡的使用中能够有所帮助。

-

-

A40i应用笔记 | 3种常见的网卡软件问题以及排查思路发布在 飞凌嵌入式专区

在飞凌嵌入式OKA40i-C开发板上虽然只有一个网口,但全志A40i-H处理器本身是有两个网络控制器的,因此在飞凌嵌入式提供的产品资料中提供了双网口解决方案。有的工程师小伙伴在开发过程中会遇见一些网卡的设计问题,今天小编为大家分享3种在使用OKA40i-C开发板时容易遇到的网卡软件问题以及排查思路。

一、问题分析:

问题描述1——

以太网初始化报错 No phy found在执行ifconfig eth0 up命令时,出现"No phy found"异常log。

问题分析:

出现"No phy found",常见原因是供给phy使用的25M时钟异常,导致phy工作不正常,gmac驱动通过mdio接门也读不到phy的设备信息。或者MDIO引脚配置不正确或者phy地址不正确;再就是MDIO没做上拉电阻,GMAC读取不到phy设备信息,用示波器量一下MDIO波形是否正确;再或是phy芯片复位失败,需要更换phy芯片复位上拉电阻。

排查步骤:

(1) 检查phy供电是否正常;

(2) 检查phy使用的25M时钟(Soc ephy25M或外部晶振)是否正常;

(3) 检查phy-mode是否按板级实际情况配置(mii/rmii/rgmii);

(4) 检查MDIO是否有上拉电阻;

(5) 检查MDIO引脚配置是否正确;

(6) eMAC phy地址是否和硬件一致;

(7) 检查复位上拉电阻是否和原理参考方案一致。MDIO通讯正常验证:

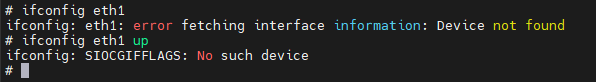

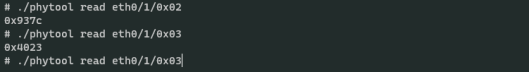

使用phytool工具读取0x02 0x03寄存器 是否正确读取PHY芯片ID,读取成功,代表MDIO通讯正常。问题描述2——

以太网初始化报错NO SUCN DEVICE执行ifconfig -a/ifconfig eth0/ifconfig eth0 up命令,找不到eth0设备。

问题分析:

以太网模块配置未生效或存在GPIO冲突。排查步骤:

步骤1:抓取内核启动log,搜索"gmac"关键字段,检查gmac驱动是否probe成功;

步骤2:若内核启动log显示mac控制器probe失败,常见原因是GPIO资源冲突导致。解决方法:

GPIO冲突会有报错信息,根据报错信息,查看GPIO冲突引脚。查看以太网模块是否配置。

问题描述3——

以太网初始化报错Initialize hardware error

执行ifconfig eth0 up命令,出现"Initialize hardware error"异常log。问题分析:

出现"Initialize hardware error",一般是由于phy没有输出RX CLK至MAC控制器,导致MAC控制器内部soft reset失败,常见原因是phy供电异常或25M时钟异常;或者是检查数据引脚的时钟是否正确,RMILL RX CLK TX CLK 是否是正确时钟。

排查步骤:

用示波器抓取rx_clk时钟波形,查看是否保持25M时钟稳定,如果出现25M/2.5M 来回跳动。即MAC与phy未link成功。解决方法:

软件上可通过在phy复位之后,设置寄存器0 固定为100M全双工,可link成功。目前可这样解决问题:

在drivers/net/ethernet/allwinner/sunxi-gmac.c 中 geth_phy_init函数中 phy_connect_direct 之前加入phy_write(phydev, 0x0, 0x2100)。以上是我们在OKA40i-C开发板的使用过程中常见网卡设计问题,有些可能是因为大家在参考方案时出现了配置问题,或者是因为芯片输出的信号不正常导致。大家在参考OKA40i-C开发板的双网口方案时,可以查看本文章整理的问题点,说不定就是您现在项目中遇见的bug。

接下来,小编将给大家介绍一些常用的网卡软件问题对应的排查手段。

二、排查手段:

这些排查手段可以帮助您在调试phy时有一个基本的调试思路,提到的一些工具可以帮助您快速定位并且解决网卡问题。

(1) 检查menuconfig及dts以太网配置是否打开;

(2) 检查phy-mode配置是否与PHY和GMAC之间的物理接口匹配,如rgmii、rmii等;

(3) 检查GPIO配置是否正确,如IO复用功能、驱动能力等;

(4) 使用phytool工具读取phy ID 验证MDIO是否正确。如下图示例,能够正常读取JL11x1的phy ID则代表MDIO通讯正常。

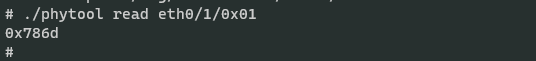

使用phytool工具读取phy状态寄存器,查看phy芯片状态。以JL11x1为例,如0x01状态寄存器读取值为0x786d,说明link成功并且工作正常。

以上就是小编为大家整理的关于OKA40i-C开发板双网口方案的网卡软件问题分析以及排查方向,希望能够为您的项目开发有所帮助。

-

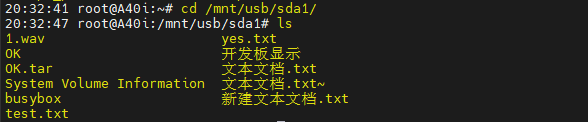

为T507-H开发板配置Samba服务,高效实现跨系统的文件共享发布在 飞凌嵌入式专区

作为一款经典的国产芯,全志T507-H芯片被广泛应用于车载电子、电力、医疗、工业控制、物联网、智能终端等诸多领域当中,而在各种复杂的嵌入式Linux应用场景当中,“打通ARM板卡与Windows设备间的壁垒以实现跨平台的文件共享”是一项不能被忽视的重要功能,那么该如何做到这一点呢?

我们可以使用Samba,这是一款在Linux系统上实现SMB的免费软件,可以在不同操作系统之间实现文件和打印机的共享。使用Samba可以方便地在Linux、Windows和Mac等不同平台之间共享文件,大大提高了文件的传输效率。

下面小编为大家介绍如何在飞凌嵌入式OKT507-C开发板上架设Samba服务。

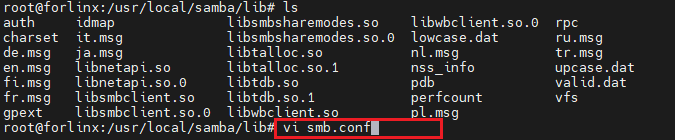

01-编译源码

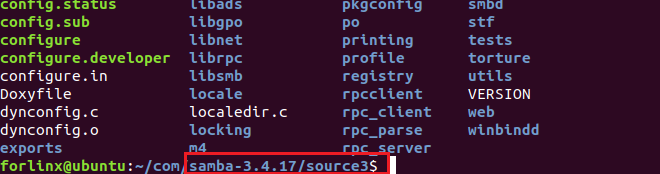

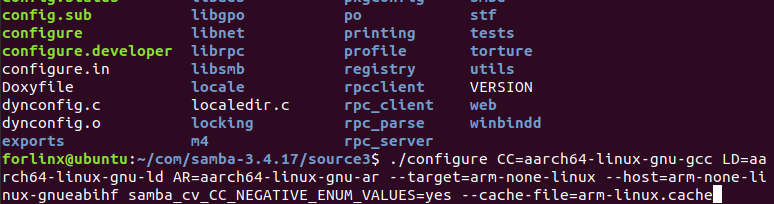

下载Samba源码包,进入source3 路径:

- 配置configure:

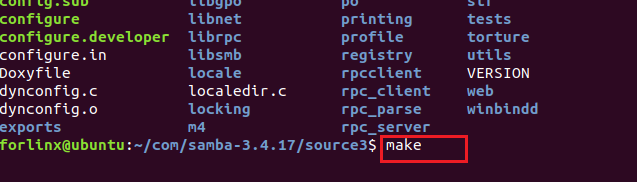

./configure CC=aarch64-linux-gnu-gcc LD=aarch64-linux-gnu-ld AR=aarch64-linux-gnu-ar --target=arm-none-linux --host=arm-none-linux-gnueabihf samba_cv_CC_NEGATIVE_ENUM_VALUES=yes --cache-file=arm-linux.cache- 编译源码(只能单线程编译,不加-j参数):

make

- make install 生成安装文件:

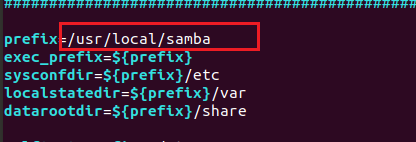

Makefile中指定安装路径

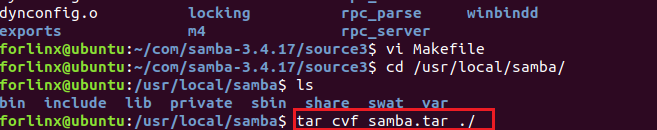

samba-3.4.17/source3$make install

- 在安装路径下打包生成文件:

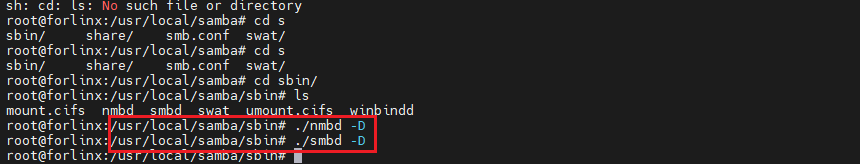

02-配置服务

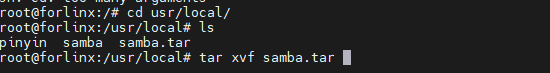

- 将压缩包解压到如下路径:

- 在如下路径新建配置文件:

- 编辑文件内容:

[global]

workgroup = root security = user client lanman auth = yes lanman auth = yes map to guest = bad user guest account = root[project]

comment = project path = / available = yes browseable = yes public = yes guest ok = yes writable = yes- 添加库文件

将如下路径的动态链接库文件拷贝到板子的/lib目录:

- 启动服务

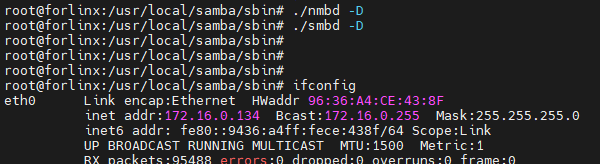

03-应用服务

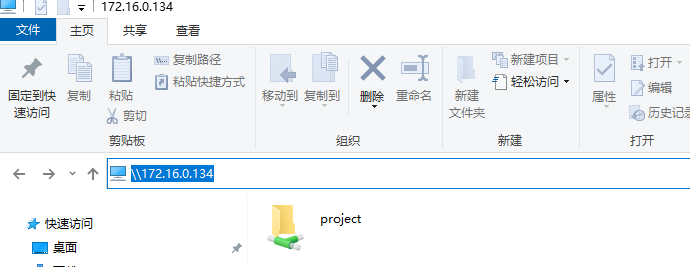

- OKT507-C开发板(Linux板卡)和Windows主机共享文件:

(1)启动Samba服务,配置与主机同一网段的IP:

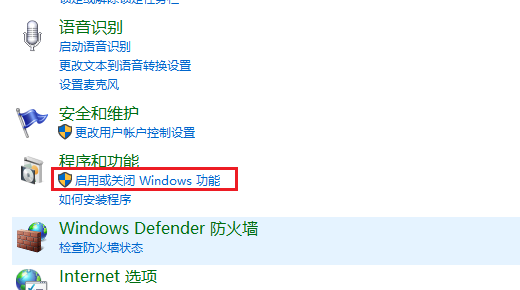

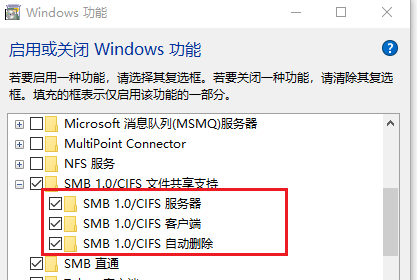

(2)在Windows主机中添加Samba的支持:

打开控制面板进入如下界面:

勾选如下三个选项:

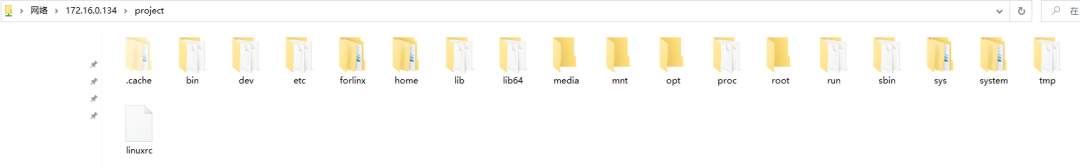

(3)在文件管理器输入\服务端 IP,回车即可看到共享路径:

- Linux板卡与Ubuntu虚拟机共享目录:

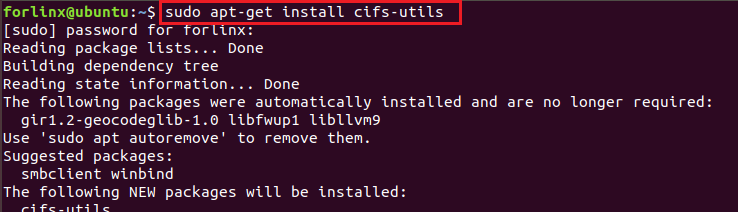

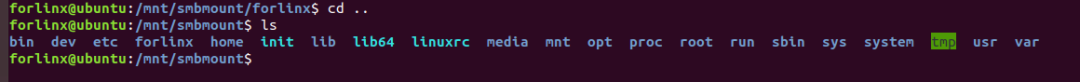

(1)安装cifs-utils:

(2)创建挂载点:

(3)挂载共享目录:

到这里,我们就完成了在飞凌嵌入式OKT507-C开发板上架设Samba服务,并且顺利地使这款Linux板卡与Windows主机和Ubuntu虚拟机进行文件共享了。当然,不同主控平台板卡的具体操作会有差异,但整体思路是一致的,希望本文提供的方法能够对屏幕前工程师朋友们的项目开发有所帮助。