@alb702 感谢您提供的编码,真的。祝福您。

smbzd 发布的帖子

-

回复: F1C200S TX Empty trigger 设置成1/2触发要怎么做?发布在 其它全志芯片讨论区

@alb702 感谢您一直以来的帮助。关于驱动的片段,我十分感兴趣,如果能提供就真是帮大忙了。非常感谢您的慷慨

-

回复: F1C200S TX Empty trigger 设置成1/2触发要怎么做?发布在 其它全志芯片讨论区

即使是在接受到THEM(tx FIFOS holding register empty)中断之后才改变控制引脚的电平,仍然是在处于数据未发送完全的情形下就把控制引脚提前改变,导致数据传输不完全

-

回复: F1C200S TX Empty trigger 设置成1/2触发要怎么做?发布在 其它全志芯片讨论区

@alb702 感谢回复!我在实现一个功能,控制485的in/out转换的gpio脚在合适的时候处于它应该在的电平:发送时拉高,接受时拉低。

现在遇到的问题是:通过示波器发现,发送数据时控制引脚提前转换电平,导致数据没有完全发完。

我想知道有没有什么好方法知道串口的数据在物理上什么时候实际地发送完成,然后尽量在1MS内的转换控制引脚的电平 -

回复: F1C200S TX Empty trigger 设置成1/2触发要怎么做?发布在 其它全志芯片讨论区

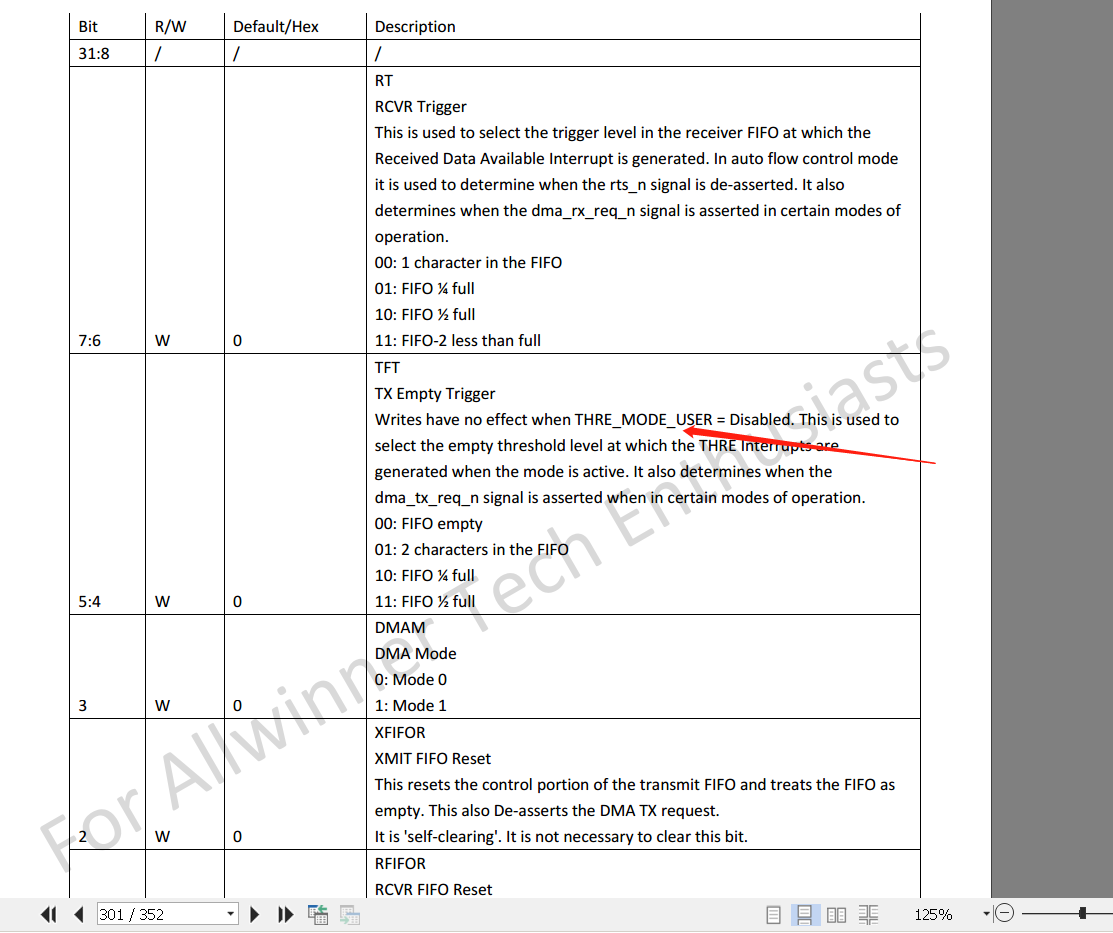

帮帮孩子吧。我在串口写FCR,在terminal用devmem写FCR,都写不动FIFO的TX Empty Trigger。是不是f1c100s、f1c200s根本就不让修改它?

帮帮孩子吧。我在串口写FCR,在terminal用devmem写FCR,都写不动FIFO的TX Empty Trigger。是不是f1c100s、f1c200s根本就不让修改它? -

F1C200S TX Empty trigger 设置成1/2触发要怎么做?发布在 其它全志芯片讨论区

我想把发送FIFO设置成1/2空就触发中断,但一直修改不了。我估计是THRE_MODE_USER没有启用,但在用户手册上没有找到它的使用说明。

请问要怎么做才能修改发送FIFO的中断触发模式呢?

-

T507 应用主线内核,uboot引导kernel卡在starting kernel发布在 Linux

请问各位,不知道T507的主线内核6.6要怎么开early_print或者earlycon来debug这个问题呢?

-

回复: f1c100s无法使用PF2的串口RX0功能发布在 其它全志芯片讨论区

@zenghc 在 f1c100s无法使用PF2的串口RX0功能 中说:

如题,IO资源比较紧张,将PF2设置成串口的RX0,无法接收到串口数据。PF4设置为TX0,可以发送数据。将PF2设置为通用IO口,输入和输出功能正常。请问是否需要特殊的配置,才能将PF2设置为RX0?

PF2应该是只能设置成TX,不能设置成RX。具体可以看一下用户手册或者规格书上关于引脚复用的表

-

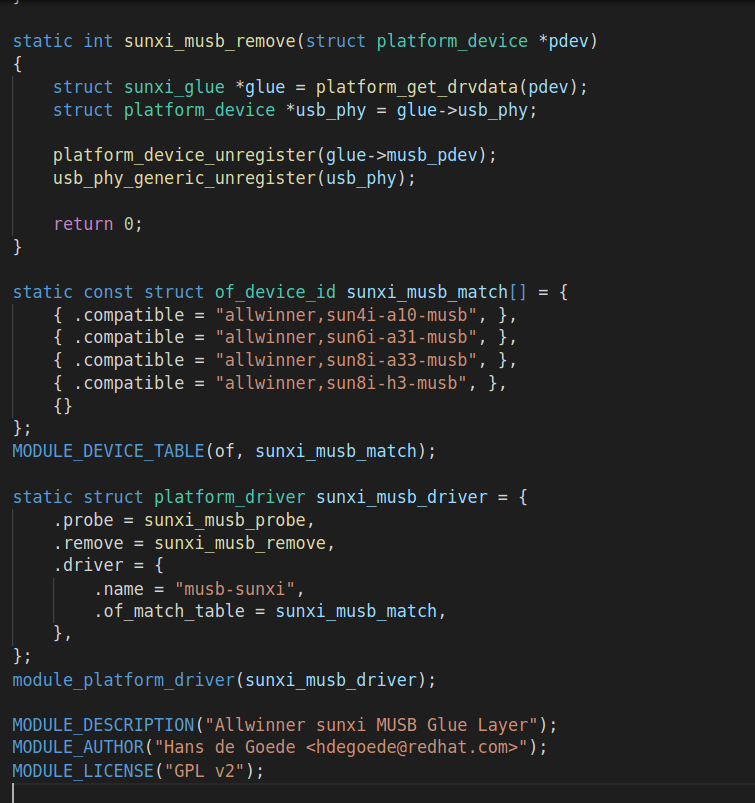

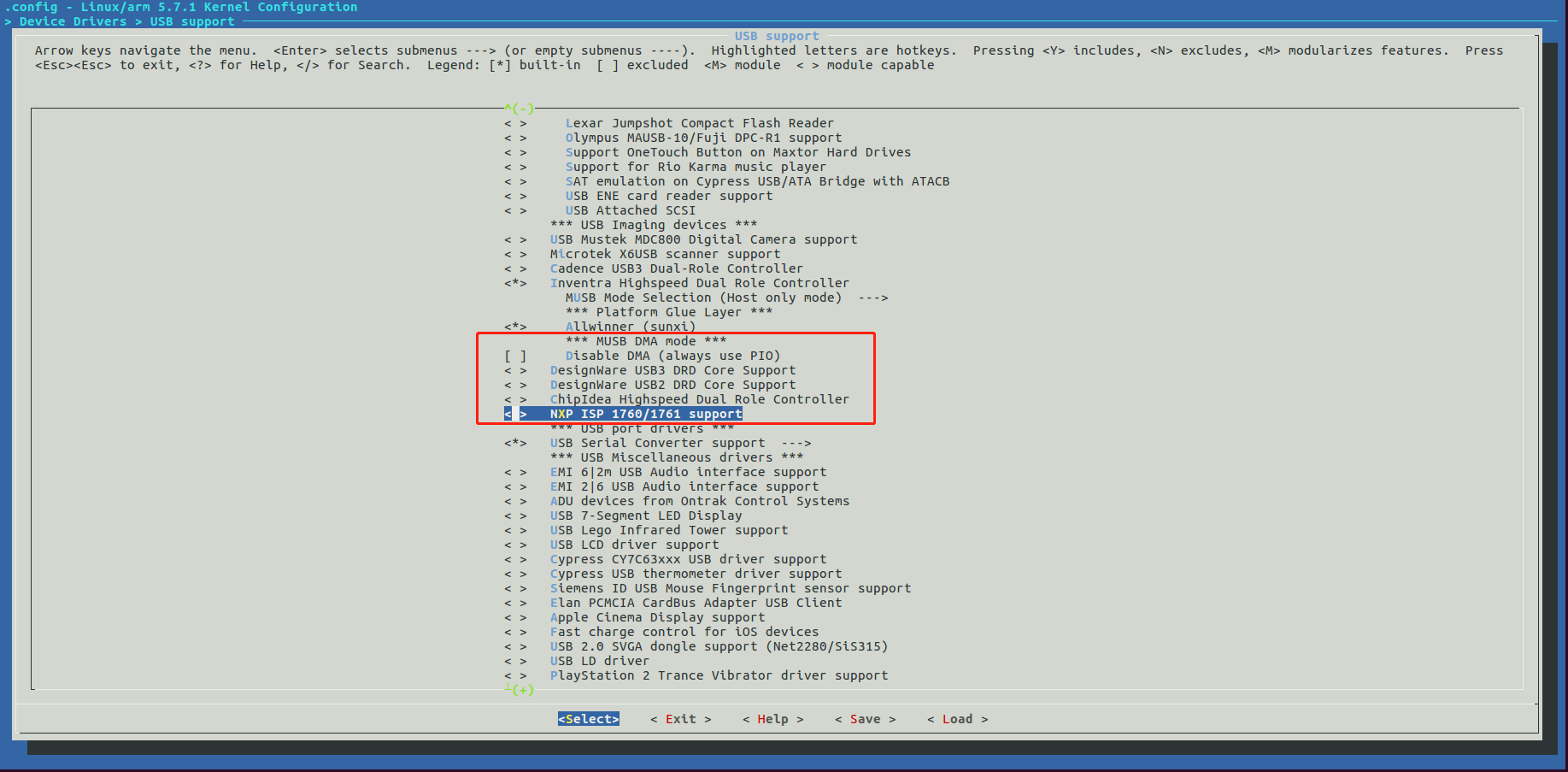

回复: f1c100s USB问题请教发布在 其它全志芯片讨论区

@alb702 感谢回复。我不太清楚在哪里确定是DMA还是PIO模式,但在menuconfig上我没有勾选Disable DMA,我猜测应该是DMA模式的。

是需要禁用DMA么? -

f1c100s USB问题请教发布在 其它全志芯片讨论区

f1c100s上跑主线linux5.7。使用在使用USB的过程中发现有以下问题:从U盘读取文件放到SD卡,计算MD5,源文件与复制文件校验码一致。但从SD卡读文件放到U盘上,就有10%的概率文件会出错。是USB驱动有问题么?下面是我的设备树文件:

// SPDX-License-Identifier: (GPL-2.0+ OR X11) /* * Copyright 2018 Icenowy Zheng <icenowy@aosc.io> * Copyright 2018 Mesih Kilinc <mesihkilinc@gmail.com> */ #include <dt-bindings/clock/suniv-ccu-f1c100s.h> #include <dt-bindings/reset/suniv-ccu-f1c100s.h> #include <dt-bindings/interrupt-controller/irq.h> / { #address-cells = <1>; #size-cells = <1>; interrupt-parent = <&intc>; clocks { #address-cells = <1>; #size-cells = <1>; ranges; osc24M: clk-24M { #clock-cells = <0>; compatible = "fixed-clock"; clock-frequency = <24000000>; clock-output-names = "osc24M"; }; osc32k: clk-32k { #clock-cells = <0>; compatible = "fixed-clock"; clock-frequency = <32768>; clock-output-names = "osc32k"; }; fake100M: clk-100M { #clock-cells = <0>; compatible = "fixed-clock"; clock-frequency = <100000000>; clock-output-names = "fake-100M"; }; }; cpus { cpu { compatible = "arm,arm926ej-s"; device_type = "cpu"; }; }; soc { compatible = "simple-bus"; #address-cells = <1>; #size-cells = <1>; ranges; sram-controller@1c00000 { compatible = "allwinner,suniv-f1c100s-system-control", "allwinner,sun4i-a10-system-control"; reg = <0x01c00000 0x30>; #address-cells = <1>; #size-cells = <1>; ranges; sram_d: sram@10000 { compatible = "mmio-sram"; reg = <0x00010000 0x1000>; #address-cells = <1>; #size-cells = <1>; ranges = <0 0x00010000 0x1000>; otg_sram: sram-section@0 { compatible = "allwinner,suniv-f1c100s-sram-d", "allwinner,sun4i-a10-sram-d"; reg = <0x0000 0x1000>; status = "disabled"; }; }; }; ccu: clock@1c20000 { compatible = "allwinner,suniv-f1c100s-ccu"; reg = <0x01c20000 0x400>; clocks = <&osc24M>, <&osc32k>; clock-names = "hosc", "losc"; #clock-cells = <1>; #reset-cells = <1>; }; intc: interrupt-controller@1c20400 { compatible = "allwinner,suniv-f1c100s-ic"; reg = <0x01c20400 0x400>; interrupt-controller; #interrupt-cells = <1>; }; pio: pinctrl@1c20800 { compatible = "allwinner,suniv-f1c100s-pinctrl"; reg = <0x01c20800 0x400>; interrupts = <38>, <39>, <40>; clocks = <&ccu 37>, <&osc24M>, <&osc32k>; clock-names = "apb", "hosc", "losc"; gpio-controller; interrupt-controller; #interrupt-cells = <3>; #gpio-cells = <3>; uart0_pe_pins: uart0-pe-pins { pins = "PE0", "PE1"; function = "uart0"; }; mmc0_pins: mmc0-pins { pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5"; function = "mmc0"; }; }; timer@1c20c00 { compatible = "allwinner,suniv-f1c100s-timer"; reg = <0x01c20c00 0x90>; interrupts = <13>; clocks = <&osc24M>; }; wdt: watchdog@1c20ca0 { compatible = "allwinner,suniv-f1c100s-wdt", "allwinner,sun4i-a10-wdt"; reg = <0x01c20ca0 0x20>; }; uart0: serial@1c25000 { compatible = "snps,dw-apb-uart"; reg = <0x01c25000 0x400>; interrupts = <1>; reg-shift = <2>; reg-io-width = <4>; clocks = <&ccu 38>; resets = <&ccu 24>; status = "disabled"; }; uart1: serial@1c25400 { compatible = "snps,dw-apb-uart"; reg = <0x01c25400 0x400>; interrupts = <2>; reg-shift = <2>; reg-io-width = <4>; clocks = <&ccu 39>; resets = <&ccu 25>; status = "disabled"; }; uart2: serial@1c25800 { compatible = "snps,dw-apb-uart"; reg = <0x01c25800 0x400>; interrupts = <3>; reg-shift = <2>; reg-io-width = <4>; clocks = <&ccu 40>; resets = <&ccu 26>; status = "disabled"; }; mmc0: mmc@1c0f000 { compatible = "allwinner,suniv-f1c100s-mmc", "allwinner,sun7i-a20-mmc"; reg = <0x01c0f000 0x1000>; clocks = <&ccu CLK_BUS_MMC0>, <&ccu CLK_MMC0>, <&ccu CLK_MMC0_OUTPUT>, <&ccu CLK_MMC0_SAMPLE>; clock-names = "ahb", "mmc", "output", "sample"; resets = <&ccu RST_BUS_MMC0>; reset-names = "ahb"; interrupts = <23>; pinctrl-names = "default"; pinctrl-0 = <&mmc0_pins>; status = "disabled"; #address-cells = <1>; #size-cells = <0>; }; usb_otg: usb@1c13000 { // compatible = "allwinner,suniv-musb"; compatible = "allwinner,sun4i-a10-musb"; reg = <0x01c13000 0x0400>; clocks = <&ccu CLK_BUS_OTG>; resets = <&ccu RST_BUS_OTG>; interrupts = <26>; interrupt-names = "mc"; phys = <&usbphy 0>; phy-names = "usb"; extcon = <&usbphy 0>; allwinner,sram = <&otg_sram 1>; status = "disabled"; }; usbphy: phy@1c13400 { // compatible = "allwinner,suniv-usb-phy"; compatible = "allwinner,sun4i-a10-usb-phy"; reg = <0x01c13400 0x10>; reg-names = "phy_ctrl"; clocks = <&ccu CLK_USB_PHY0>; clock-names = "usb0_phy"; resets = <&ccu RST_USB_PHY0>; reset-names = "usb0_reset"; #phy-cells = <1>; status = "disabled"; }; }; };