D1-H 有哪些CSR 地址是怎么分布的?

-

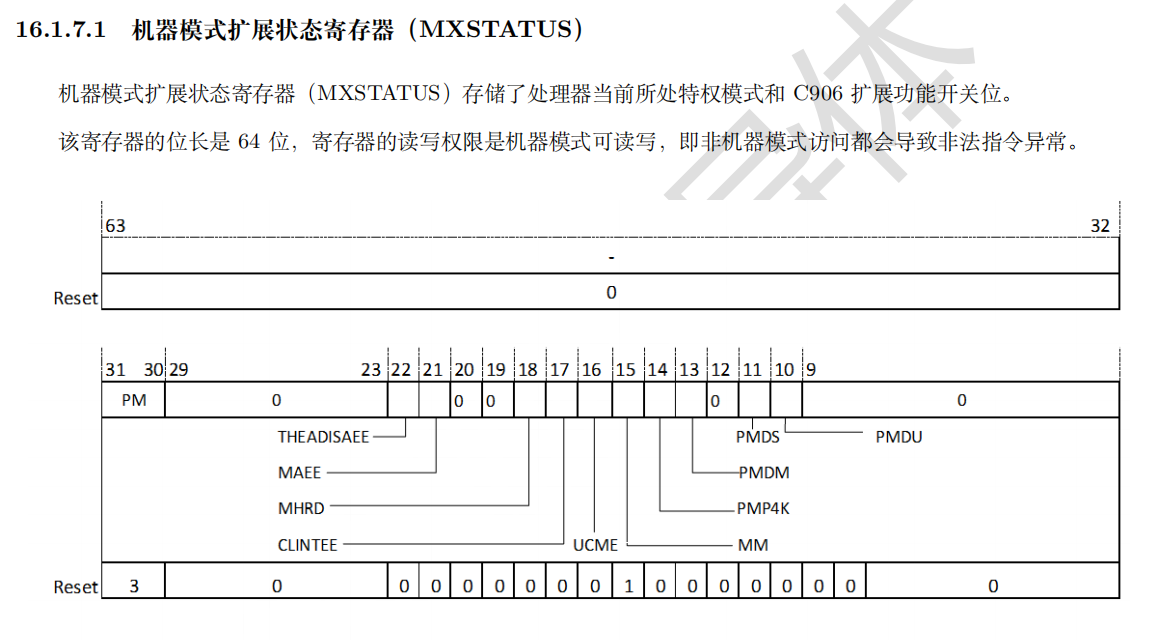

/*enable theadisaee*/ li t1, EN_THEADISAEE csrs 0x7c0, t1 /* mxstatus */mxstatus 代表什么意思? 在手册和spec里面没有找到。

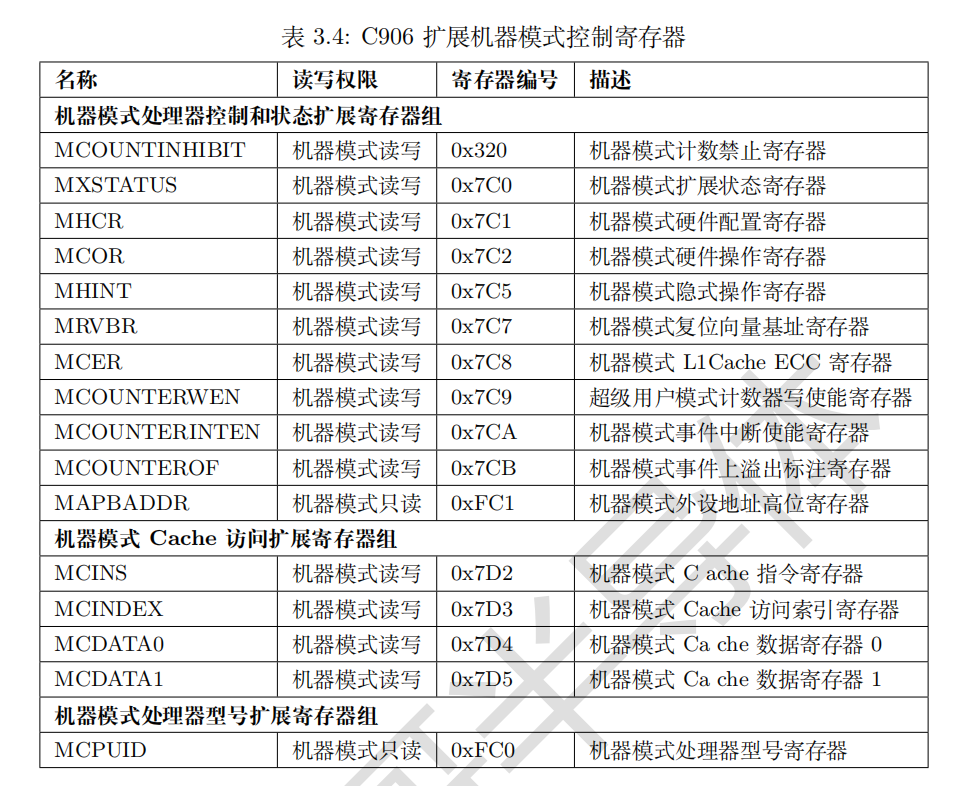

#define CSR_MCOR 0x7c2

#define CSR_MHCR 0x7c1

#define CSR_MCCR2 0x7c3

#define CSR_MHINT 0x7c5

#define CSR_MXSTATUS 0x7c0

#define CSR_PLIC_BASE 0xfc1

#define CSR_MRMR 0x7c6

#define CSR_MRVBR 0x7c7这些地址是怎么哪里来的?

-

MXSTATUS 是机器模式扩展状态寄存器

地址定义:

其设置方法如下:

(0:1) CACHE_SEL=2’b11时,选中指令和数据高速缓存

(4) INV=1时高速缓存进行无效化

(16) BHT_INV=1时分支历史表内的数据进行无效化

(17) TB_INV=1时分支目标缓冲器内的数据进行无效化

csr_write(CSR_MCOR, 0x70013);(0) IE=1时Icache打开

(1) DE=1时Dcache打开

(2) WA=1时数据高速缓存为write allocate模式 (c906不支持)

(3) WB=1时数据高速缓存为写回模式 (c906固定为1)

(4) RS=1时返回栈开启

(5) BPE=1时预测跳转开启

(6) BTB=1时分支目标预测开启

(8) WBR=1时支持写突发传输写 (c906固定为1)

(12) L0BTB=1时第一级分支目标预测开启

csr_write(CSR_MHCR, 0x11ff);(15) MM为1时支持非对齐访问,硬件处理非对齐访问

(16) UCME为1时,用户模式可以执行扩展的cache操作指令

(17) CLINTEE为1时,CLINT发起的超级用户软件中断和计时器中断可以被响应

(21) MAEE为1时MMU的pte中扩展地址属性位,用户可以配置页面的地址属性

(22) THEADISAEE为1时可以使用C906扩展指令集

csr_set(CSR_MXSTATUS, 0x638000);(2) DPLD=1,dcache预取开启

(3,4,5,6,7) AMR=1,时,在出现连续3条缓存行的存储操作时后续连续地址的存储操作不再写入L1Cache

(8) IPLD=1ICACHE预取开启

(9) LPE=1循环加速开启

(13,14) DPLD为2时,预取8条缓存行

csr_write(CSR_MHINT, 0x16e30c);这些C906核心的寄存器资料均位于《Xuantie_C906_R1S0_User_Manual.pdf》 文档中,可以前往平头哥开源芯片平台下载。

Copyright © 2024 深圳全志在线有限公司 粤ICP备2021084185号 粤公网安备44030502007680号