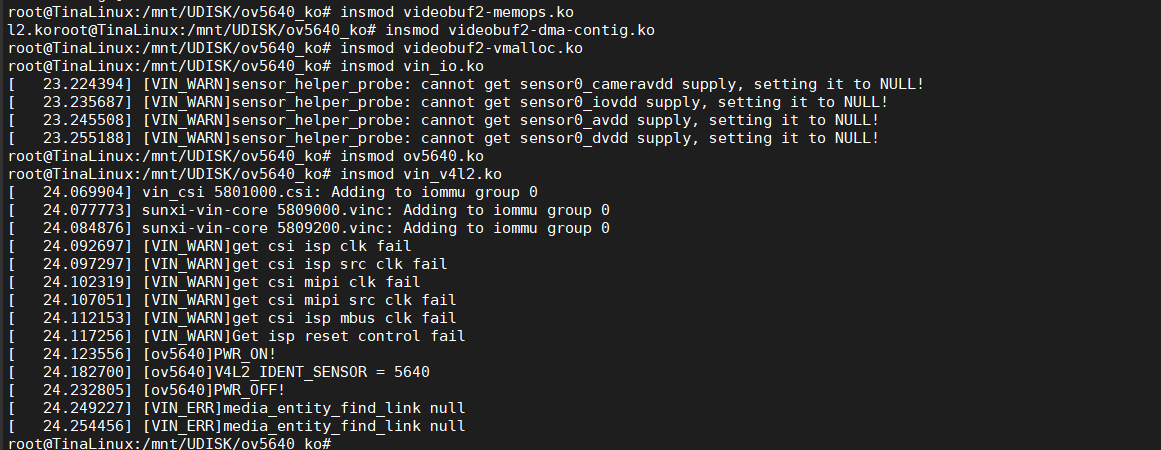

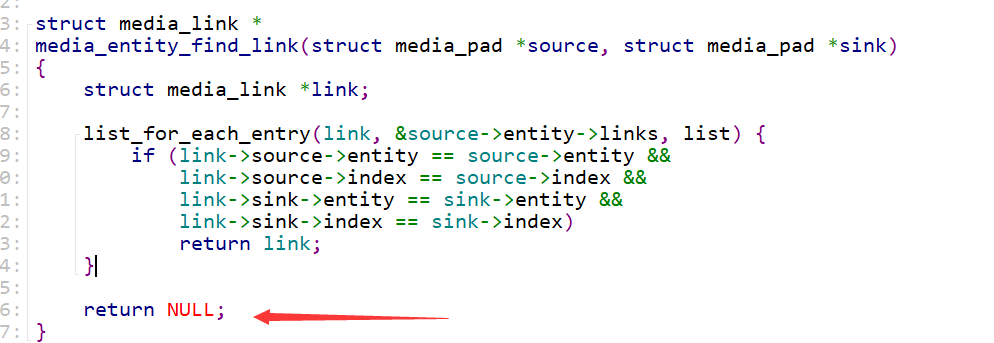

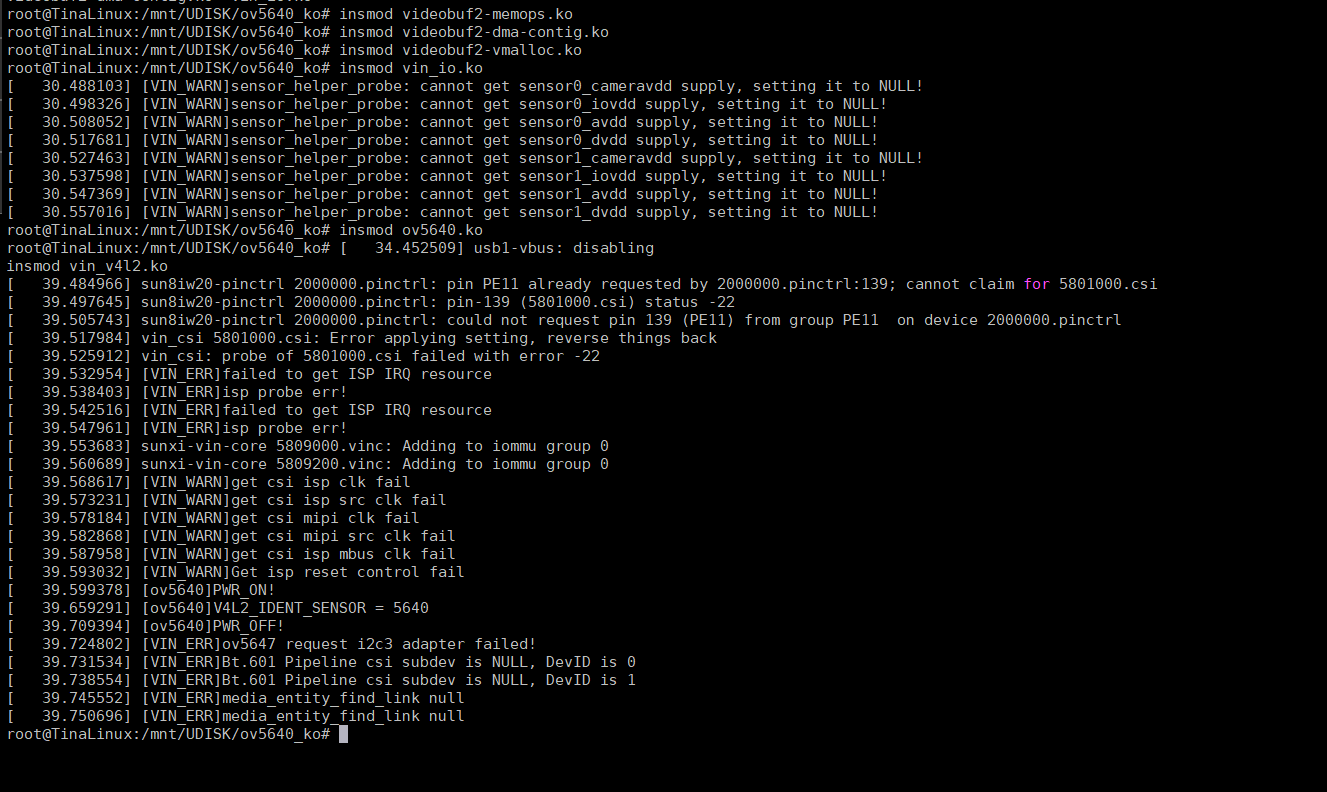

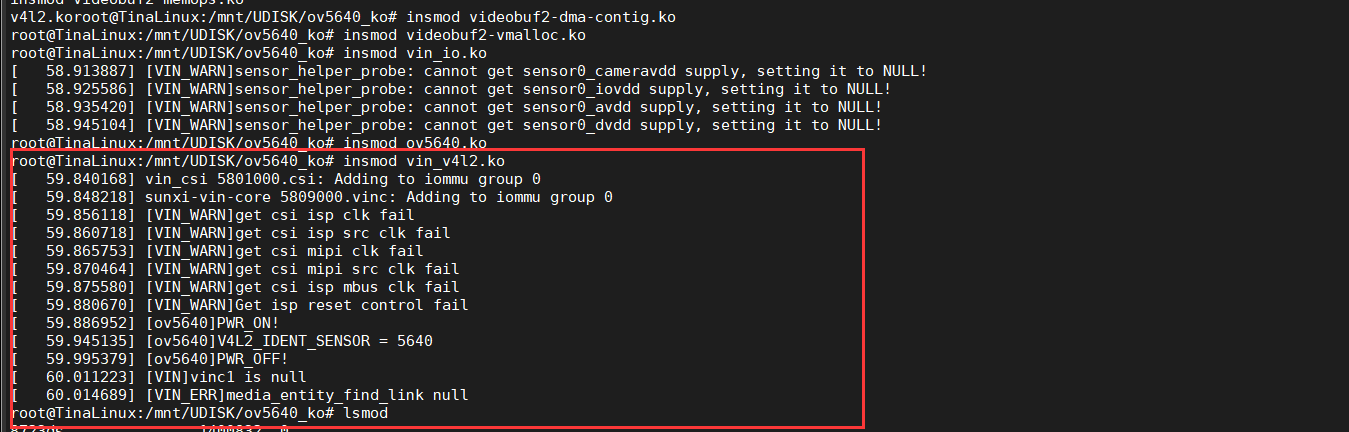

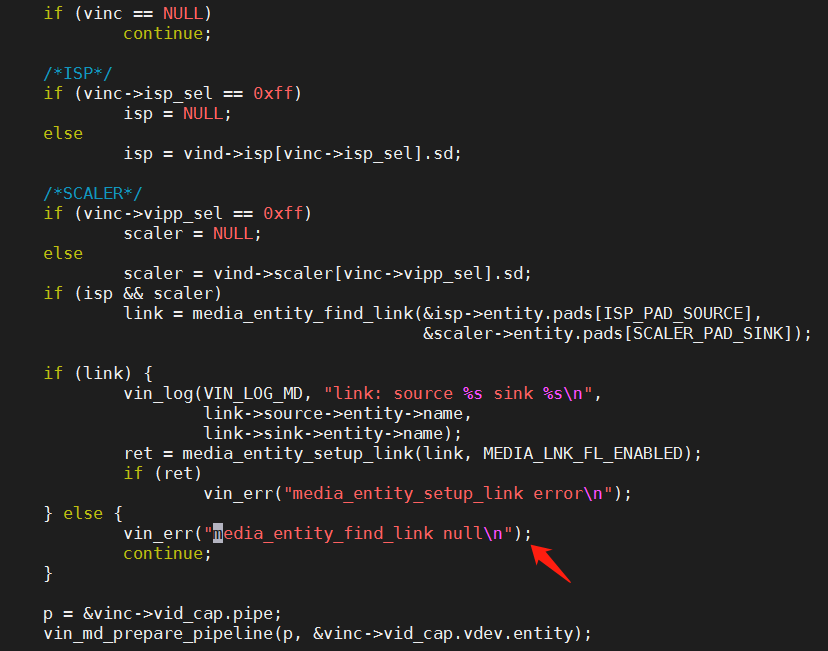

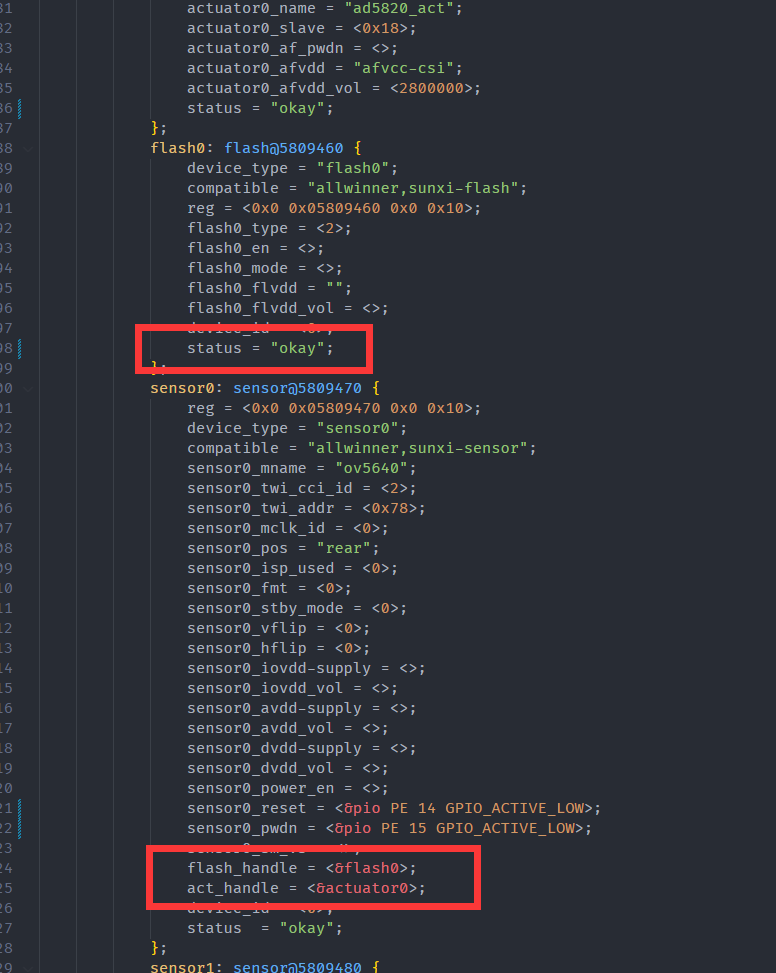

T113 ov5640加载驱动报错,PE11申请不到,被占用了。

-

T113 ov5640加载驱动报错,PE11申请不到,被占用了。

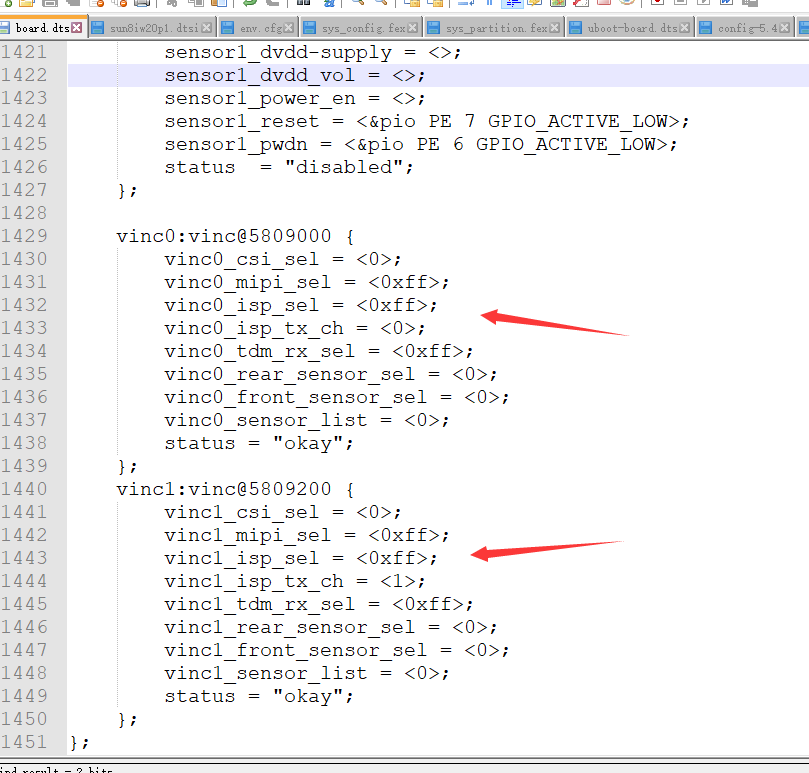

board.dts

/* * Allwinner Technology CO., Ltd. sun8iw20p1 platform * * modify base on juno.dts */ /* optee used 7MB: SHM 2M: OS: 1M: TA:4M*/ /memreserve/ 0x41B00000 0x00100000; #include <dt-bindings/clock/sun8iw20-ccu.h> #include <dt-bindings/clock/sun8iw20-r-ccu.h> #include <dt-bindings/clock/sun8iw20-rtc.h> #include <dt-bindings/reset/sun8iw20-ccu.h> #include <dt-bindings/reset/sun8iw20-r-ccu.h> #include <dt-bindings/interrupt-controller/arm-gic.h> #include <dt-bindings/gpio/gpio.h> #include <dt-bindings/gpio/sun4i-gpio.h> #include <dt-bindings/thermal/thermal.h> #include <dt-bindings/power/r528-power.h> / { model = "sun8iw20"; compatible = "allwinner,sun8iw20p1"; interrupt-parent = <&gic>; #address-cells = <2>; #size-cells = <2>; aliases { serial0 = &uart0; serial1 = &uart1; serial2 = &uart2; serial3 = &uart3; serial4 = &uart4; serial5 = &uart5; spi0 = &spi0; spi1 = &spi1; twi0 = &twi0; twi1 = &twi1; twi2 = &twi2; twi3 = &twi3; mmc0 = &sdc0; mmc2 = &sdc2; pwm = &pwm; pwm0 = &pwm0; pwm1 = &pwm1; pwm2 = &pwm2; pwm3 = &pwm3; pwm4 = &pwm4; pwm5 = &pwm5; pwm6 = &pwm6; pwm7 = &pwm7; ir0 = &s_cir0; ve0 = &ve; tv0 = &tv0; tvd = &tvd; tvd0 = &tvd0; share_space0 = &share_space0; }; chosen { bootargs = "earlyprintk=sunxi-uart,0x2500000 loglevel=8 initcall_debug=0 console=ttyS0 init=/init"; //bootargs = "loglevel=8 initcall_debug=0 console=ttyS0 init=/init"; linux,initrd-start = <0x0 0x0>; linux,initrd-end = <0x0 0x0>; }; firmware { optee { compatible = "linaro,optee-tz"; method = "smc"; }; }; cpus { enable-method = "allwinner,sun8iw20p1"; #address-cells = <1>; #size-cells = <0>; cpu0: cpu@0 { device_type = "cpu"; compatible = "arm,cortex-a7","arm,armv7"; reg = <0x0>; enable-method = "psci"; clocks = <&ccu CLK_CPUX>; dynamic-power-coefficient = <156>; cpu-idle-states = <&CPU_SLEEP &CLUSTER_SLEEP>; operating-points-v2 = <&cpu_opp_table>; #cooling-cells = <2>; }; cpu1: cpu@1 { device_type = "cpu"; compatible = "arm,cortex-a7","arm,armv7"; reg = <0x1>; enable-method = "psci"; clocks = <&ccu CLK_CPUX>; cpu-idle-states = <&CPU_SLEEP &CLUSTER_SLEEP>; operating-points-v2 = <&cpu_opp_table>; #cooling-cells = <2>; }; idle-states { entry-method = "arm,psci"; CPU_SLEEP: cpu-sleep { compatible = "arm,idle-state"; arm,psci-suspend-param = <0x0010000>; entry-latency-us = <46>; exit-latency-us = <59>; min-residency-us = <3570>; local-timer-stop; }; CLUSTER_SLEEP: cluster-sleep { compatible = "arm,idle-state"; arm,psci-suspend-param = <0x1010000>; entry-latency-us = <47>; exit-latency-us = <74>; min-residency-us = <5000>; local-timer-stop; }; }; }; psci { compatible = "arm,psci-1.0"; method = "smc"; }; dump_reg: dump_reg@20000 { compatible = "allwinner,sunxi-dump-reg"; reg = <0x0 0x00020000 0x0 0x0004>; /* 0x00020000: dump_reg test addr, 0x0004: dump_reg test size */ }; cpu_opp_table: cpu-opp-table { compatible = "allwinner,sun50i-operating-points"; nvmem-cells = <&speedbin_efuse>, <&cpubin_efuse>; nvmem-cell-names = "speed", "bin"; opp-shared; opp@480000000 { opp-hz = /bits/ 64 <480000000>; clock-latency-ns = <244144>; /* 8 32k periods */ opp-microvolt-a0 = <900000>; opp-microvolt-a1 = <900000>; opp-microvolt-a2 = <900000>; opp-microvolt-b0 = <950000>; opp-supported-hw = <0x3>; }; opp@720000000 { opp-hz = /bits/ 64 <720000000>; clock-latency-ns = <244144>; /* 8 32k periods */ opp-microvolt-a0 = <900000>; opp-microvolt-a1 = <900000>; opp-microvolt-a2 = <900000>; opp-microvolt-b0 = <950000>; opp-supported-hw = <0x3>; }; opp@912000000 { opp-hz = /bits/ 64 <912000000>; clock-latency-ns = <244144>; /* 8 32k periods */ opp-microvolt-a0 = <950000>; opp-microvolt-a1 = <900000>; opp-microvolt-a2 = <900000>; opp-microvolt-b0 = <950000>; opp-supported-hw = <0x3>; }; opp@1008000000 { opp-hz = /bits/ 64 <1008000000>; clock-latency-ns = <244144>; /* 8 32k periods */ opp-microvolt-a0 = <1000000>; opp-microvolt-a1 = <900000>; opp-microvolt-a2 = <900000>; opp-microvolt-b0 = <950000>; opp-supported-hw = <0x3>; }; opp@1104000000 { opp-hz = /bits/ 64 <1104000000>; clock-latency-ns = <244144>; /* 8 32k periods */ opp-microvolt-a0 = <1050000>; opp-microvolt-a1 = <950000>; opp-microvolt-a2 = <950000>; opp-microvolt-b0 = <950000>; opp-supported-hw = <0x3>; }; opp@1200000000 { opp-hz = /bits/ 64 <1200000000>; clock-latency-ns = <244144>; /* 8 32k periods */ opp-microvolt-a0 = <1100000>; opp-microvolt-a1 = <1000000>; opp-microvolt-a2 = <1000000>; opp-supported-hw = <0x1>; }; }; dcxo24M: dcxo24M_clk { #clock-cells = <0>; compatible = "fixed-clock"; clock-frequency = <24000000>; clock-output-names = "dcxo24M"; }; rc_16m: rc16m_clk { #clock-cells = <0>; compatible = "fixed-clock"; clock-frequency = <16000000>; clock-accuracy = <300000000>; clock-output-names = "rc-16m"; }; ext_32k: ext32k_clk { #clock-cells = <0>; compatible = "fixed-clock"; clock-frequency = <32768>; clock-output-names = "ext-32k"; }; dram: dram { compatible = "allwinner,dram"; clocks = <&ccu CLK_PLL_DDR0>; clock-names = "pll_ddr"; }; memory@40000000 { device_type = "memory"; reg = <0x00000000 0x40000000 0x00000000 0x20000000>; }; share_space0: share_space@42100000 { #address-cells = <1>; #size-cells = <1>; deice_tpye = "share_space0"; /* dsp write addr and len */ /* arm write addr and len */ /* dsp log addr and len */ /* reserve */ reg = < 0x42100000 0x00001000 0x42101000 0x00001000 0x42102000 0x0000E000 0x00000000 0x00000000>; }; gic: interrupt-controller@3020000 { compatible = "arm,cortex-a15-gic", "arm,cortex-a9-gic"; #interrupt-cells = <3>; #address-cells = <0>; device_type = "gic"; interrupt-controller; reg = <0x0 0x03021000 0 0x1000>, /* GIC Dist */ <0x0 0x03022000 0 0x2000>, /* GIC CPU */ <0x0 0x03024000 0 0x2000>, /* GIC VCPU Control */ <0x0 0x03026000 0 0x2000>; /* GIC VCPU */ interrupts = <GIC_PPI 9 0xf04>; /* GIC Maintenence IRQ */ }; timer_arch { compatible = "arm,armv7-timer"; interrupts = <GIC_PPI 13 (GIC_CPU_MASK_SIMPLE(2) | IRQ_TYPE_LEVEL_LOW)>, <GIC_PPI 14 (GIC_CPU_MASK_SIMPLE(2) | IRQ_TYPE_LEVEL_LOW)>, <GIC_PPI 11 (GIC_CPU_MASK_SIMPLE(2) | IRQ_TYPE_LEVEL_LOW)>, <GIC_PPI 10 (GIC_CPU_MASK_SIMPLE(2) | IRQ_TYPE_LEVEL_LOW)>; clock-frequency = <24000000>; arm,cpu-registers-not-fw-configured; interrupt-parent = <&gic>; arm,no-tick-in-suspend; }; pmu { compatible = "arm,cortex-a7-pmu"; interrupts = <GIC_SPI 172 4>, <GIC_SPI 173 4>; }; power: power-management@ff000000 { compatible = "allwinner,r528-pmu", "syscon", "simple-mfd"; reg = <0x0 0x07001000 0x0 0x400>; pd: power-controller { compatible = "allwinner,r528-power-controller"; clocks = <&r_ccu CLK_R_PPU>; clock-names = "ppu"; resets = <&r_ccu RST_R_PPU>; reset-names = "ppu_rst"; #power-domain-cells = <1>; #address-cells = <1>; #size-cells = <0>; /* These power domains are grouped by VD_SYS */ pd_ve@R528_PD_VE { reg = <R528_PD_VE>; }; }; }; mmu_aw: iommu@2010000 { compatible = "allwinner,sunxi-iommu"; reg = <0x0 0x02010000 0x0 0x1000>; interrupts = <GIC_SPI 64 IRQ_TYPE_LEVEL_HIGH>; interrupt-names = "iommu-irq"; clocks = <&ccu CLK_BUS_IOMMU>; clock-names = "iommu"; #iommu-cells = <2>; status = "okay"; }; reg_pio1_8: pio-18 { compatible = "regulator-fixed"; regulator-name = "pio-18"; regulator-min-microvolt = <1800000>; regulator-max-microvolt = <1800000>; }; reg_pio3_3: pio-33 { compatible = "regulator-fixed"; regulator-name = "pio-33"; regulator-min-microvolt = <3300000>; regulator-max-microvolt = <3300000>; }; thermal-zones { cpu_thermal_zone: cpu_thermal_zone { polling-delay-passive = <500>; polling-delay = <1000>; thermal-sensors = <&ths 0>; sustainable-power = <589>; cpu_trips: trips { cpu_threshold: trip-point@0 { temperature = <70000>; type = "passive"; hysteresis = <0>; }; cpu_target: trip-point@1 { temperature = <90000>; type = "passive"; hysteresis = <0>; }; cpu_crit: cpu_crit@0 { temperature = <110000>; type = "critical"; hysteresis = <0>; }; }; cooling-maps { map0 { trip = <&cpu_target>; cooling-device = <&cpu0 THERMAL_NO_LIMIT THERMAL_NO_LIMIT>; contribution = <1024>; }; }; }; }; soc: soc@3000000 { compatible = "simple-bus"; #address-cells = <2>; #size-cells = <2>; ranges; device_type = "soc"; sram_ctrl: sram_ctrl@3000000 { compatible = "allwinner,sram_ctrl"; reg = <0x0 0x3000000 0 0x16C>; soc_ver { offset = <0x24>; mask = <0x7>; shift = <0>; ver_a = <0x18590000>; ver_b = <0x18590002>; ver_d = <0x18590003>; }; soc_id { offset = <0x200>; mask = <0x1>; shift = <22>; }; soc_bin { offset = <0x0>; mask = <0x3ff>; shift = <0x0>; }; }; rtc_ccu: rtc_ccu@7090000 { compatible = "allwinner,sun8iw20-rtc-ccu"; device_type = "rtc-ccu"; reg = <0x0 0x07090000 0x0 0x320>; /* The same as rtc */ #clock-cells = <1>; }; ccu: ccu@2001000 { compatible = "allwinner,sun8iw20-ccu"; reg = <0x0 0x02001000 0x0 0x1000>; clocks = <&dcxo24M>, <&rtc_ccu CLK_OSC32K>, <&rtc_ccu CLK_IOSC>; clock-names = "hosc", "losc", "iosc"; #clock-cells = <1>; #reset-cells = <1>; }; r_ccu: r_ccu@7010000 { compatible = "allwinner,sun8iw20-r-ccu"; reg = <0x0 0x07010000 0x0 0x240>; clocks = <&dcxo24M>, <&rtc_ccu CLK_OSC32K>, <&rtc_ccu CLK_IOSC>, <&ccu CLK_PLL_PERIPH0>; clock-names = "hosc", "losc", "iosc", "pll-periph0"; #clock-cells = <1>; #reset-cells = <1>; }; rtc: rtc@7090000 { compatible = "allwinner,sun8iw20-rtc"; device_type = "rtc"; wakeup-source; reg = <0x0 0x07090000 0x0 0x320>; interrupts = <GIC_SPI 144 IRQ_TYPE_LEVEL_HIGH>; clocks = <&r_ccu CLK_R_AHB_BUS_RTC>, <&rtc_ccu CLK_RTC_1K>, <&rtc_ccu CLK_RTC_SPI>; clock-names = "r-ahb-rtc", "rtc-1k", "rtc-spi"; resets = <&r_ccu RST_R_AHB_BUS_RTC>; gpr_cur_pos = <6>; }; dma:dma-controller@3002000 { compatible = "allwinner,sun8iw20-dma"; reg = <0x0 0x03002000 0x0 0x1000>; interrupts = <GIC_SPI 50 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_DMA>, <&ccu CLK_MBUS_DMA>; clock-names = "bus", "mbus"; dma-channels = <8>; dma-requests = <48>; resets = <&ccu RST_BUS_DMA>; #dma-cells = <1>; }; soc_timer0: timer@2050000 { compatible = "allwinner,sun4i-a10-timer"; device_type = "soc_timer"; reg = <0x0 0x02050000 0x0 0xA0>; interrupt-parent = <&gic>; interrupts = <GIC_SPI 59 IRQ_TYPE_LEVEL_HIGH>; clocks = <&dcxo24M>; }; wdt: watchdog@20500A0 { compatible = "allwinner,sun6i-a31-wdt"; reg = <0x0 0x020500A0 0x0 0x20>; /* In Timers Spec */ interrupts = <GIC_SPI 63 IRQ_TYPE_LEVEL_HIGH>; /* In GIC Spec */ }; mbus0: mbus-controller@3102000 { compatible = "allwinner,sun8i-mbus"; reg = <0x0 0x03102000 0x0 0x1000>; /* In SDRAM Controller Spec: DRAMC Common Register */ #mbus-cells = <1>; }; pio: pinctrl@2000000 { compatible = "allwinner,sun8iw20-pinctrl"; reg = <0x0 0x02000000 0x0 0x500>; interrupts = <GIC_SPI 69 IRQ_TYPE_LEVEL_HIGH>, /* AW1859_GIC_Spec: GPIOB: 101-32=69 */ <GIC_SPI 71 IRQ_TYPE_LEVEL_HIGH>, <GIC_SPI 73 IRQ_TYPE_LEVEL_HIGH>, <GIC_SPI 75 IRQ_TYPE_LEVEL_HIGH>, <GIC_SPI 77 IRQ_TYPE_LEVEL_HIGH>, <GIC_SPI 79 IRQ_TYPE_LEVEL_HIGH>; device_type = "pio"; clocks = <&ccu CLK_APB0>, <&dcxo24M>, <&rtc_ccu CLK_OSC32K>; clock-names = "apb", "hosc", "losc"; gpio-controller; #gpio-cells = <3>; interrupt-controller; #interrupt-cells = <3>; #size-cells = <0>; vcc-pf-supply = <®_pio1_8>; vcc-pfo-supply = <®_pio3_3>; test_pins_a: test_pins@0 { allwinner,pins = "PB0", "PB1"; allwinner,function = "test"; allwinner,muxsel = <0x9>; allwinner,drive = <1>; allwinner,pull = <1>; }; test_pins_b: test_pins@1 { pins = "PB0", "PB1"; function = "io_disabled"; allwinner,muxsel = <0xF>; allwinner,drive = <1>; allwinner,pull = <1>; }; csi_mclk0_pins_a: csi_mclk0@0 { pins = "PE3"; function = "csi0"; drive-strength = <10>; }; csi_mclk0_pins_b: csi_mclk0@1 { pins = "PE3"; function = "gpio_in"; }; csi0_pins_a: csi0@0 { pins = "PE2", "PE0", "PE1", "PE4", "PE5", "PE6", "PE7", "PE8", "PE9", "PE10", "PE11"; function = "ncsi0"; drive-strength = <10>; }; csi0_pins_b: csi0@1 { pins = "PE2", "PE0", "PE1", "PE4", "PE5", "PE6", "PE7", "PE8", "PE9", "PE10", "PE11"; function = "io_disabled"; drive-strength = <10>; }; lvds0_pins_a: lvds0@0 { pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD8", "PD9"; function = "lvds0"; drive-strength = <30>; bias-disable; }; lvds0_pins_b: lvds0@1 { pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD8", "PD9"; function = "io_disabled"; drive-strength = <30>; bias-disable; }; rgb24_pins_a: rgb24@0 { pins = "PB2", "PB3", "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", \ "PB4", "PB5", "PD6", "PD7", "PD8", "PD9", "PD10", "PD11", \ "PB6", "PB7", "PD12", "PD13", "PD14", "PD15", "PD16", "PD17", \ "PD18", "PD19", "PD20", "PD21"; function = "lcd0"; drive-strength = <30>; bias-disable; }; rgb24_pins_b: rgb24@1 { pins = "PB2", "PB3", "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", \ "PB4", "PB5", "PD6", "PD7", "PD8", "PD9", "PD10", "PD11", \ "PB6", "PB7", "PD12", "PD13", "PD14", "PD15", "PD16", "PD17", \ "PD18", "PD19", "PD20", "PD21"; function = "io_disabled"; bias-disable; }; rgb18_pins_a: rgb18@0 { pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", \ "PD6", "PD7", "PD8", "PD9", "PD10", "PD11", \ "PD12", "PD13", "PD14", "PD15", "PD16", "PD17", \ "PD18", "PD19", "PD20", "PD21"; function = "lcd0"; drive-strength = <30>; bias-disable; }; rgb18_pins_b: rgb18@1 { pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", \ "PD6", "PD7", "PD8", "PD9", "PD10", "PD11", \ "PD12", "PD13", "PD14", "PD15", "PD16", "PD17", \ "PD18", "PD19", "PD20", "PD21"; function = "io_disabled"; bias-disable; }; dsi2lane_pins_a: dsi2lane@0 { pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5"; function = "dsi"; drive-strength = <30>; bias-disable; }; dsi2lane_pins_b: dsi2lane@1 { pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5"; function = "io_disabled"; bias-disable; }; dsi4lane_pins_a: dsi4lane@0 { pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD8", "PD9"; function = "dsi"; drive-strength = <30>; bias-disable; }; dsi4lane_pins_b: dsi4lane@1 { pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD8", "PD9"; function = "io_disabled"; bias-disable; }; }; pinctrl_test: pinctrl_test@0 { reg = <0x0 0x0 0x0 0x0>; compatible = "allwinner,sunxi-pinctrl-test"; device_type = "pinctrl-test"; /* For pin state selecting test */ pinctrl-0 = <&test_pins_a>; pinctrl-1 = <&test_pins_b>; pinctrl-names = "default", "sleep"; /* For pin basic_function/irq test */ test-gpios = <&pio PB 0 GPIO_ACTIVE_LOW>; interrupt-parent = <&pio>; interrupts = <PB 1 IRQ_TYPE_LEVEL_HIGH>; }; uart0: uart@2500000 { compatible = "allwinner,sun8i-uart"; device_type = "uart0"; reg = <0x0 0x02500000 0x0 0x400>; interrupts = <GIC_SPI 2 IRQ_TYPE_LEVEL_HIGH>; sunxi,uart-fifosize = <64>; clocks = <&ccu CLK_BUS_UART0>; clock-names = "uart0"; resets = <&ccu RST_BUS_UART0>; uart0_port = <0>; uart0_type = <2>; status = "disabled"; }; uart1: uart@2500400 { compatible = "allwinner,sun8i-uart"; device_type = "uart1"; reg = <0x0 0x02500400 0x0 0x400>; interrupts = <GIC_SPI 3 IRQ_TYPE_LEVEL_HIGH>; sunxi,uart-fifosize = <256>; clocks = <&ccu CLK_BUS_UART1>; clock-names = "uart1"; resets = <&ccu RST_BUS_UART1>; uart1_port = <1>; uart1_type = <4>; status = "okay"; }; uart2: uart@2500800 { compatible = "allwinner,sun8i-uart"; device_type = "uart2"; reg = <0x0 0x02500800 0x0 0x400>; interrupts = <GIC_SPI 4 IRQ_TYPE_LEVEL_HIGH>; sunxi,uart-fifosize = <256>; clocks = <&ccu CLK_BUS_UART2>; clock-names = "uart2"; resets = <&ccu RST_BUS_UART2>; uart2_port = <2>; uart2_type = <4>; status = "disabled"; }; uart3: uart@2500c00 { compatible = "allwinner,sun8i-uart"; device_type = "uart3"; reg = <0x0 0x02500c00 0x0 0x400>; interrupts = <GIC_SPI 5 IRQ_TYPE_LEVEL_HIGH>; sunxi,uart-fifosize = <256>; clocks = <&ccu CLK_BUS_UART3>; clock-names = "uart3"; resets = <&ccu RST_BUS_UART3>; uart3_port = <3>; uart3_type = <4>; status = "disabled"; }; uart4: uart@2501000 { compatible = "allwinner,sun8i-uart"; device_type = "uart4"; reg = <0x0 0x02501000 0x0 0x400>; interrupts = <GIC_SPI 6 IRQ_TYPE_LEVEL_HIGH>; sunxi,uart-fifosize = <256>; clocks = <&ccu CLK_BUS_UART4>; clock-names = "uart4"; resets = <&ccu RST_BUS_UART4>; uart4_port = <4>; uart4_type = <2>; status = "disabled"; }; uart5: uart@2501400 { compatible = "allwinner,sun8i-uart"; device_type = "uart5"; reg = <0x0 0x02501400 0x0 0x400>; interrupts = <GIC_SPI 7 IRQ_TYPE_LEVEL_HIGH>; sunxi,uart-fifosize = <256>; clocks = <&ccu CLK_BUS_UART5>; clock-names = "uart5"; resets = <&ccu RST_BUS_UART5>; uart5_port = <5>; uart5_type = <2>; status = "disabled"; }; cryptoengine: ce@03040000 { compatible = "allwinner,sunxi-ce"; device_name = "ce"; reg = <0x0 0x03040000 0x0 0xa0>, /* non-secure space */ <0x0 0x03040800 0x0 0xa0>; /* secure space */ interrupts = <GIC_SPI 52 IRQ_TYPE_EDGE_RISING>, /*non-secure*/ <GIC_SPI 53 IRQ_TYPE_EDGE_RISING>; /* secure*/ clock-frequency = <400000000>; /* 400MHz */ clocks = <&ccu CLK_BUS_CE>, <&ccu CLK_CE>, <&ccu CLK_MBUS_CE>, <&ccu CLK_PLL_PERIPH0_2X>; clock-names = "bus_ce", "ce_clk", "mbus_ce", "pll_periph0_2x"; resets = <&ccu RST_BUS_CE>; status = "okay"; }; gmac0: eth@4500000 { compatible = "allwinner,sunxi-gmac"; reg = <0x0 0x04500000 0x0 0x10000>, <0x0 0x03000030 0x0 0x4>; interrupts = <GIC_SPI 46 IRQ_TYPE_LEVEL_HIGH>; interrupt-names = "gmacirq"; clocks = <&ccu CLK_BUS_EMAC0>, <&ccu CLK_EMAC0_25M>; clock-names = "gmac", "ephy"; resets = <&ccu RST_BUS_EMAC0>; device_type = "gmac0"; gmac-power0; gmac-power1; gmac-power2; status = "disabled"; }; sdc2: sdmmc@4022000 { compatible = "allwinner,sunxi-mmc-v4p6x"; device_type = "sdc2"; reg = <0x0 0x04022000 0x0 0x1000>; interrupts = <GIC_SPI 42 IRQ_TYPE_LEVEL_HIGH>; clocks = <&dcxo24M>, <&ccu CLK_PLL_PERIPH0_2X>, <&ccu CLK_MMC2>, <&ccu CLK_BUS_MMC2>; clock-names = "osc24m","pll_periph","mmc","ahb"; resets = <&ccu RST_BUS_MMC2>; reset-names = "rst"; pinctrl-names = "default","sleep"; pinctrl-0 = <&sdc2_pins_a>; pinctrl-1 = <&sdc2_pins_b>; bus-width = <4>; req-page-count = <2>; cap-mmc-highspeed; cap-cmd23; mmc-cache-ctrl; non-removable; /*max-frequency = <200000000>;*/ max-frequency = <50000000>; cap-erase; mmc-high-capacity-erase-size; no-sdio; no-sd; /*-- speed mode --*/ /*sm0: DS26_SDR12*/ /*sm1: HSSDR52_SDR25*/ /*sm2: HSDDR52_DDR50*/ /*sm3: HS200_SDR104*/ /*sm4: HS400*/ /*-- frequency point --*/ /*f0: CLK_400K*/ /*f1: CLK_25M*/ /*f2: CLK_50M*/ /*f3: CLK_100M*/ /*f4: CLK_150M*/ /*f5: CLK_200M*/ sdc_tm4_sm0_freq0 = <0>; sdc_tm4_sm0_freq1 = <0>; sdc_tm4_sm1_freq0 = <0x00000000>; sdc_tm4_sm1_freq1 = <0>; sdc_tm4_sm2_freq0 = <0x00000000>; sdc_tm4_sm2_freq1 = <0>; sdc_tm4_sm3_freq0 = <0x05000000>; sdc_tm4_sm3_freq1 = <0x00000005>; sdc_tm4_sm4_freq0 = <0x00050000>; sdc_tm4_sm4_freq1 = <0x00000004>; sdc_tm4_sm4_freq0_cmd = <0>; sdc_tm4_sm4_freq1_cmd = <0>; /*vmmc-supply = <®_3p3v>;*/ /*vqmc-supply = <®_3p3v>;*/ /*vdmc-supply = <®_3p3v>;*/ /*vmmc = "vcc-card";*/ /*vqmc = "";*/ /*vdmc = "";*/ /*sunxi-power-save-mode;*/ }; sdc0: sdmmc@4020000 { compatible = "allwinner,sunxi-mmc-v5p3x"; device_type = "sdc0"; reg = <0x0 0x04020000 0x0 0x1000>; interrupts = <GIC_SPI 40 IRQ_TYPE_LEVEL_HIGH>; clocks = <&dcxo24M>, <&ccu CLK_PLL_PERIPH0_2X>, <&ccu CLK_MMC0>, <&ccu CLK_BUS_MMC0>; clock-names = "osc24m","pll_periph","mmc","ahb"; resets = <&ccu RST_BUS_MMC0>; reset-names = "rst"; pinctrl-names = "default","mmc_1v8","sleep","uart_jtag"; pinctrl-0 = <&sdc0_pins_a>; pinctrl-1 = <&sdc0_pins_b>; pinctrl-2 = <&sdc0_pins_c>; pinctrl-3 = <&sdc0_pins_d &sdc0_pins_e>; max-frequency = <50000000>; bus-width = <4>; req-page-count = <2>; /*non-removable;*/ /*broken-cd;*/ /*cd-inverted*/ /*cd-gpios = <&pio PF 6 GPIO_ACTIVE_LOW>;*/ /* vmmc-supply = <®_3p3v>;*/ /* vqmc-supply = <®_3p3v>;*/ /* vdmc-supply = <®_3p3v>;*/ /*vmmc = "vcc-card";*/ /*vqmc = "";*/ /*vdmc = "";*/ cap-sd-highspeed; cap-wait-while-busy; no-sdio; no-mmc; /*sd-uhs-sdr50;*/ /*sd-uhs-ddr50;*/ /*cap-sdio-irq;*/ /*keep-power-in-suspend;*/ /*ignore-pm-notify;*/ /*sunxi-power-save-mode;*/ /*sunxi-dly-400k = <1 0 0 0>; */ /*sunxi-dly-26M = <1 0 0 0>;*/ /*sunxi-dly-52M = <1 0 0 0>;*/ /*sunxi-dly-52M-ddr4 = <1 0 0 0>;*/ /*sunxi-dly-52M-ddr8 = <1 0 0 0>;*/ /*sunxi-dly-104M = <1 0 0 0>;*/ /*sunxi-dly-208M = <1 0 0 0>;*/ /*sunxi-dly-104M-ddr = <1 0 0 0>;*/ /*sunxi-dly-208M-ddr = <1 0 0 0>;*/ }; sdc1: sdmmc@4021000 { compatible = "allwinner,sunxi-mmc-v5p3x"; device_type = "sdc1"; reg = <0x0 0x04021000 0x0 0x1000>; interrupts = <GIC_SPI 41 IRQ_TYPE_LEVEL_HIGH>; clocks = <&dcxo24M>, <&ccu CLK_PLL_PERIPH0_2X>, <&ccu CLK_MMC1>, <&ccu CLK_BUS_MMC1>; clock-names = "osc24m","pll_periph","mmc","ahb"; resets = <&ccu RST_BUS_MMC1>; reset-names = "rst"; pinctrl-names = "default","sleep"; pinctrl-0 = <&sdc1_pins_a>; pinctrl-1 = <&sdc1_pins_b>; max-frequency = <50000000>; bus-width = <4>; /*broken-cd;*/ /*cd-inverted*/ /*cd-gpios = <&pio PG 6 6 1 2 0>;*/ /* vmmc-supply = <®_3p3v>;*/ /* vqmc-supply = <®_3p3v>;*/ /* vdmc-supply = <®_3p3v>;*/ /*vmmc = "vcc-card";*/ /*vqmc = "";*/ /*vdmc = "";*/ cap-sd-highspeed; no-mmc; /*sd-uhs-sdr50;*/ /*sd-uhs-ddr50;*/ /*sd-uhs-sdr104;*/ /*cap-sdio-irq;*/ keep-power-in-suspend; /*ignore-pm-notify;*/ /*sunxi-power-save-mode;*/ /*sunxi-dly-400k = <1 0 0 0 0>; */ /*sunxi-dly-26M = <1 0 0 0 0>;*/ /*sunxi-dly-52M = <1 0 0 0 0>;*/ sunxi-dly-52M-ddr4 = <1 0 0 0 2>; /*sunxi-dly-52M-ddr8 = <1 0 0 0 0>;*/ sunxi-dly-104M = <1 0 0 0 1>; /*sunxi-dly-208M = <1 1 0 0 0>;*/ sunxi-dly-208M = <1 0 0 0 1>; /*sunxi-dly-104M-ddr = <1 0 0 0 0>;*/ /*sunxi-dly-208M-ddr = <1 0 0 0 0>;*/ status = "okay"; }; tpadc: tpadc@2009c00 { compatible = "allwinner,tp_key"; reg = <0x0 0x02009c00 0x0 0x400>; interrupts = <GIC_SPI 78 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_TPADC>, <&ccu CLK_BUS_TPADC>; clock-names = "mod", "bus"; clock-frequency = <1000000>; resets = <&ccu RST_BUS_TPADC>; status = "disabled"; }; rtp:rtp@2009c00 { compatible = "allwinner,sun8i-ts"; reg = <0x0 0x02009c00 0x0 0x400>; clocks = <&ccu CLK_TPADC>, <&ccu CLK_BUS_TPADC>; clock-names = "mod", "bus"; clock-frequency = <1000000>; resets = <&ccu RST_BUS_TPADC>; interrupts = <GIC_SPI 62 IRQ_TYPE_LEVEL_HIGH>; }; spi0: spi@4025000 { #address-cells = <1>; #size-cells = <0>; compatible = "allwinner,sun8i-spi"; device_type = "spi0"; reg = <0x0 0x04025000 0x0 0x1000>; interrupts = <GIC_SPI 15 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_PLL_PERIPH0>, <&ccu CLK_SPI0>, <&ccu CLK_BUS_SPI0>; clock-names = "pll", "mod", "bus"; resets = <&ccu RST_BUS_SPI0>; clock-frequency = <100000000>; spi0_cs_number = <1>; spi0_cs_bitmap = <1>; dmas = <&dma 22>, <&dma 22>; dma-names = "tx", "rx"; status = "disabled"; }; spi1: spi@4026000 { #address-cells = <1>; #size-cells = <0>; compatible = "allwinner,sun8i-spi"; device_type = "spi1"; reg = <0x0 0x04026000 0x0 0x1000>; interrupts = <GIC_SPI 16 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_PLL_PERIPH0>, <&ccu CLK_SPI1>, <&ccu CLK_BUS_SPI1>; clock-names = "pll", "mod", "bus"; resets = <&ccu RST_BUS_SPI1>; clock-frequency = <100000000>; spi1_cs_number = <1>; spi1_cs_bitmap = <1>; dmas = <&dma 23>, <&dma 23>; dma-names = "tx", "rx"; status = "disabled"; }; ve: ve@1c0e000 { compatible = "allwinner,sunxi-cedar-ve"; reg = <0x0 0x01c0e000 0x0 0x1000>, <0x0 0x03000000 0x0 0x10>, <0x0 0x03001000 0x0 0x1000>; interrupts = <GIC_SPI 66 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_VE>, <&ccu CLK_VE>, <&ccu CLK_MBUS_VE>; clock-names = "bus_ve", "ve", "mbus_ve"; resets = <&ccu RST_BUS_VE>; power-domains = <&pd R528_PD_VE>; iommus = <&mmu_aw 0 1>; status = "okay"; }; twi0: twi@2502000{ #address-cells = <1>; #size-cells = <0>; compatible = "allwinner,sun8i-twi"; device_type = "twi0"; reg = <0x0 0x02502000 0x0 0x400>; interrupts = <GIC_SPI 9 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_I2C0>; resets = <&ccu RST_BUS_I2C0>; clock-names = "bus"; clock-frequency = <400000>; status = "disabled"; }; twi1: twi@2502400{ #address-cells = <1>; #size-cells = <0>; compatible = "allwinner,sun8i-twi"; device_type = "twi1"; reg = <0x0 0x02502400 0x0 0x400>; interrupts = <GIC_SPI 10 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_I2C1>; resets = <&ccu RST_BUS_I2C1>; clock-names = "bus"; clock-frequency = <200000>; status = "disabled"; }; twi2: twi@2502800{ #address-cells = <1>; #size-cells = <0>; compatible = "allwinner,sun8i-twi"; device_type = "twi2"; reg = <0x0 0x02502800 0x0 0x400>; interrupts = <GIC_SPI 11 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_I2C2>; resets = <&ccu RST_BUS_I2C2>; clock-names = "bus"; clock-frequency = <100000>; status = "disabled"; }; twi3: twi@2502c00{ #address-cells = <1>; #size-cells = <0>; compatible = "allwinner,sun8i-twi"; device_type = "twi3"; reg = <0x0 0x02502c00 0x0 0x400>; interrupts = <GIC_SPI 12 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_I2C3>; resets = <&ccu RST_BUS_I2C3>; clock-names = "bus"; clock-frequency = <100000>; status = "disabled"; }; ledc: ledc@2008000 { #address-cells = <1>; #size-cells = <0>; compatible = "allwinner,sunxi-leds"; reg = <0x0 0x02008000 0x0 0x400>; interrupts = <GIC_SPI 20 IRQ_TYPE_LEVEL_HIGH>; interrupt-names = "ledcirq"; clocks = <&ccu CLK_LEDC>, <&ccu CLK_BUS_LEDC>; clock-names = "clk_ledc", "clk_cpuapb"; dmas = <&dma 42>, <&dma 42>; dma-names = "rx", "tx"; resets = <&ccu RST_BUS_LEDC>; reset-names = "ledc_reset"; status = "disable"; }; pwm: pwm@2000c00 { #pwm-cells = <0x3>; compatible = "allwinner,sunxi-pwm"; reg = <0x0 0x02000c00 0x0 0x400>; clocks = <&ccu CLK_BUS_PWM>; resets = <&ccu RST_BUS_PWM>; pwm-number = <8>; pwm-base = <0x0>; sunxi-pwms = <&pwm0>, <&pwm1>, <&pwm2>, <&pwm3>, <&pwm4>, <&pwm5>, <&pwm6>, <&pwm7>; }; pwm0: pwm0@2000c10 { compatible = "allwinner,sunxi-pwm0"; pinctrl-names = "active", "sleep"; reg = <0x0 0x02000c10 0x0 0x4>; reg_base = <0x02000c00>; }; pwm1: pwm1@2000c11 { compatible = "allwinner,sunxi-pwm1"; pinctrl-names = "active", "sleep"; reg = <0x0 0x02000c11 0x0 0x4>; reg_base = <0x02000c00>; }; pwm2: pwm2@2000c12 { compatible = "allwinner,sunxi-pwm2"; pinctrl-names = "active", "sleep"; reg = <0x0 0x02000c12 0x0 0x4>; reg_base = <0x02000c00>; }; pwm3: pwm3@2000c13 { compatible = "allwinner,sunxi-pwm3"; pinctrl-names = "active", "sleep"; reg = <0x0 0x02000c13 0x0 0x4>; reg_base = <0x02000c00>; }; pwm4: pwm4@2000c14 { compatible = "allwinner,sunxi-pwm4"; pinctrl-names = "active", "sleep"; reg = <0x0 0x02000c14 0x0 0x4>; reg_base = <0x02000c00>; }; pwm5: pwm5@2000c15 { compatible = "allwinner,sunxi-pwm5"; pinctrl-names = "active", "sleep"; reg = <0x0 0x02000c15 0x0 0x4>; reg_base = <0x02000c00>; }; pwm6: pwm6@2000c16 { compatible = "allwinner,sunxi-pwm6"; pinctrl-names = "active", "sleep"; reg = <0x0 0x02000c16 0x0 0x4>; reg_base = <0x02000c00>; }; pwm7: pwm7@2000c17 { compatible = "allwinner,sunxi-pwm7"; pinctrl-names = "active", "sleep"; reg = <0x0 0x02000c17 0x0 0x4>; reg_base = <0x02000c00>; }; lcd_fb0: lcd_fb0@0 { compatible = "allwinner,sunxi-lcd_fb0"; pinctrl-names = "active","sleep"; status = "okay"; }; keyboard0: keyboard@2009800 { compatible = "allwinner,keyboard_1350mv"; reg = <0x0 0x02009800 0x0 0x400>; interrupts = <GIC_SPI 61 IRQ_TYPE_EDGE_RISING>; clocks = <&ccu CLK_BUS_LRADC>; clock-names = "mclk"; resets = <&ccu RST_BUS_LRADC>; key_cnt = <5>; key0 = <210 115>; key1 = <410 114>; key2 = <590 139>; key3 = <750 28>; key4 = <880 172>; wakeup-source; status = "okay"; }; sid@3006000 { compatible = "allwinner,sun8iw20p1-sid", "allwinner,sunxi-sid"; reg = <0x0 0x03006000 0 0x1000>; #address-cells = <1>; #size-cells = <1>; secure_status { reg = <0x0 0>; offset = <0xa0>; size = <0x4>; }; chipid { reg = <0x0 0>; offset = <0x200>; size = <0x10>; }; rotpk { reg = <0x0 0>; offset = <0x140>; size = <0x4>; }; speedbin_efuse: speedbin@00 { reg = <0x00 4>; }; cpubin_efuse: cpubin@28 { reg = <0x28 4>; }; ths_calib: calib@14 { reg = <0x14 8>; }; }; gpadc: gpadc@2009000 { compatible = "allwinner,sunxi-gpadc"; reg = <0x0 0x02009000 0x0 0x400>; interrupts = <GIC_SPI 57 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_GPADC>; clock-names = "bus"; resets = <&ccu RST_BUS_GPADC>; status = "okay"; }; vind0: vind@5800800 { compatible = "allwinner,sunxi-vin-media", "simple-bus"; #address-cells = <2>; #size-cells = <2>; ranges; device_id = <0>; csi_top = <336000000>; csi_isp = <327000000>; reg = <0x0 0x05800800 0x0 0x200>, <0x0 0x05800000 0x0 0x800>; clocks = <&ccu CLK_CSI_TOP>, <&ccu CLK_PLL_VIDEO1_2X>, <&ccu CLK_CSI0_MCLK>, <&dcxo24M>, <&ccu CLK_PLL_VIDEO1>, <&ccu CLK_BUS_CSI>, <&ccu CLK_MBUS_CSI>; clock-names = "csi_top", "csi_top_src", "csi_mclk0", "csi_mclk0_24m", "csi_mclk0_pll", "csi_bus", "csi_mbus"; resets = <&ccu RST_BUS_CSI>; reset-names = "csi_ret"; pinctrl-names = "mclk0-default", "mclk0-sleep"; pinctrl-0 = <&csi_mclk0_pins_a>; pinctrl-1 = <&csi_mclk0_pins_b>; status = "okay"; csi0: csi@5801000{ compatible = "allwinner,sunxi-csi"; reg = <0x0 0x05801000 0x0 0x1000>; interrupts = <GIC_SPI 100 IRQ_TYPE_LEVEL_HIGH>; pinctrl-names = "default","sleep"; pinctrl-0 = <&csi0_pins_a>; pinctrl-1 = <&csi0_pins_b>; device_id = <0>; iommus = <&mmu_aw 1 1>; status = "okay"; }; isp0: isp@5809410 { compatible = "allwinner,sunxi-isp"; reg = <0x0 0x05809410 0x0 0x10>; device_id = <0xfe>; status = "okay"; }; isp1: isp@5809420 { compatible = "allwinner,sunxi-isp"; reg = <0x0 0x05809420 0x0 0x10>; device_id = <0xff>; status = "okay"; }; scaler0: scaler@5809430 { compatible = "allwinner,sunxi-scaler"; reg = <0x0 0x05809430 0x0 0x10>; device_id = <0xfe>; status = "okay"; }; scaler1: scaler@5809440 { compatible = "allwinner,sunxi-scaler"; reg = <0x0 0x05809440 0x0 0x10>; device_id = <0xff>; status = "okay"; }; actuator0: actuator@5809450 { compatible = "allwinner,sunxi-actuator"; device_type = "actuator0"; reg = <0x0 0x05809450 0x0 0x10>; actuator0_name = "ad5820_act"; actuator0_slave = <0x18>; actuator0_af_pwdn = <>; actuator0_afvdd = "afvcc-csi"; actuator0_afvdd_vol = <2800000>; status = "disabled"; }; flash0: flash@5809460 { device_type = "flash0"; compatible = "allwinner,sunxi-flash"; reg = <0x0 0x05809460 0x0 0x10>; flash0_type = <2>; flash0_en = <>; flash0_mode = <>; flash0_flvdd = ""; flash0_flvdd_vol = <>; device_id = <0>; status = "disabled"; }; sensor0: sensor@5809470 { reg = <0x0 0x05809470 0x0 0x10>; device_type = "sensor0"; compatible = "allwinner,sunxi-sensor"; sensor0_mname = "ov5640"; sensor0_twi_cci_id = <2>; sensor0_twi_addr = <0x78>; sensor0_mclk_id = <0>; sensor0_pos = "rear"; sensor0_isp_used = <0>; sensor0_fmt = <0>; sensor0_stby_mode = <0>; sensor0_vflip = <0>; sensor0_hflip = <0>; sensor0_iovdd-supply = <>; sensor0_iovdd_vol = <>; sensor0_avdd-supply = <>; sensor0_avdd_vol = <>; sensor0_dvdd-supply = <>; sensor0_dvdd_vol = <>; sensor0_power_en = <>; sensor0_reset = <&pio PE 9 GPIO_ACTIVE_LOW>; sensor0_pwdn = <&pio PE 8 GPIO_ACTIVE_LOW>; sensor0_sm_vs = <>; flash_handle = <&flash0>; act_handle = <&actuator0>; device_id = <0>; status = "okay"; }; sensor1: sensor@5809480 { reg = <0x0 0x05809480 0x0 0x10>; device_type = "sensor1"; compatible = "allwinner,sunxi-sensor"; sensor1_mname = "ov5647"; sensor1_twi_cci_id = <3>; sensor1_twi_addr = <0x6c>; sensor1_mclk_id = <1>; sensor1_pos = "front"; sensor1_isp_used = <0>; sensor1_fmt = <0>; sensor1_stby_mode = <0>; sensor1_vflip = <0>; sensor1_hflip = <0>; sensor1_iovdd-supply = <>; sensor1_iovdd_vol = <>; sensor1_avdd-supply = <>; sensor1_avdd_vol = <>; sensor1_dvdd-supply = <>; sensor1_dvdd_vol = <>; sensor1_power_en = <>; sensor1_reset = <&pio PE 7 GPIO_ACTIVE_LOW>; sensor1_pwdn = <&pio PE 6 GPIO_ACTIVE_LOW>; sensor1_sm_vs = <>; flash_handle = <>; act_handle = <>; device_id = <1>; status = "okay"; }; vinc0: vinc@5809000 { compatible = "allwinner,sunxi-vin-core"; device_type = "vinc0"; reg = <0x0 0x05809000 0x0 0x200>; interrupts = <GIC_SPI 95 IRQ_TYPE_LEVEL_HIGH>; vinc0_csi_sel = <0>; vinc0_mipi_sel = <0xff>; vinc0_isp_sel = <0>; vinc0_tdm_rx_sel = <0xff>; vinc0_rear_sensor_sel = <0>; vinc0_front_sensor_sel = <0>; vinc0_sensor_list = <0>; device_id = <0>; iommus = <&mmu_aw 1 1>; status = "okay"; }; vinc1: vinc@5809200 { device_type = "vinc1"; compatible = "allwinner,sunxi-vin-core"; reg = <0x0 0x05809200 0x0 0x200>; interrupts = <GIC_SPI 96 IRQ_TYPE_LEVEL_HIGH>; vinc1_csi_sel = <0>; vinc1_mipi_sel = <0xff>; vinc1_isp_sel = <1>; vinc1_tdm_rx_sel = <0xff>; vinc1_rear_sensor_sel = <0>; vinc1_front_sensor_sel = <0>; vinc1_sensor_list = <0>; device_id = <1>; iommus = <&mmu_aw 1 1>; status = "okay"; }; }; s_cir0: s_cir@7040000 { compatible = "allwinner,s_cir"; reg = <0x0 0x07040000 0x0 0x400>; interrupts = <GIC_SPI 151 IRQ_TYPE_LEVEL_HIGH>; clocks = <&r_ccu CLK_R_APB0_BUS_IRRX>, <&dcxo24M>, <&r_ccu CLK_R_APB0_IRRX>; clock-names = "bus", "pclk", "mclk"; resets = <&r_ccu RST_R_APB0_BUS_IRRX>; status = "disabled"; }; ir1: ir@2003000 { compatible = "allwinner,irtx"; reg = <0x0 0x02003000 0x0 0x400>; interrupts = <GIC_SPI 19 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_IR_TX>, <&dcxo24M>, <&ccu CLK_IR_TX>; clock-names = "bus", "pclk", "mclk"; resets = <&ccu RST_BUS_IR_TX>; status = "disabled"; }; di: deinterlace@5400000 { compatible = "allwinner,sunxi-deinterlace"; reg = <0x0 0x05400000 0x0 0x0000ffff>; interrupts = <GIC_SPI 88 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_DI>, <&ccu CLK_BUS_DI>, <&ccu CLK_PLL_PERIPH0_2X>; clock-names = "clk_di", "pll_periph", "clk_bus_di"; resets = <&ccu RST_BUS_DI>; reset-names = "rst_bus_di"; assigned-clocks = <&ccu CLK_DI>; assigned-clock-parents = <&ccu CLK_PLL_PERIPH0_2X>; assigned-clock-rates = <300000000>; iommus = <&mmu_aw 4 1>; status = "okay"; }; g2d: g2d@5410000 { compatible = "allwinner,sunxi-g2d"; reg = <0x0 0x05410000 0x0 0x3ffff>; interrupts = <GIC_SPI 89 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_G2D>, <&ccu CLK_G2D>, <&ccu CLK_MBUS_G2D>; clock-names = "bus", "g2d", "mbus_g2d"; resets = <&ccu RST_BUS_G2D>; iommus = <&mmu_aw 3 1>; status = "okay"; }; disp: disp@5000000 { compatible = "allwinner,sunxi-disp"; reg = <0x0 0x05000000 0x0 0x3fffff>, /* de0 */ <0x0 0x05460000 0x0 0xfff>, /*display_if_top*/ <0x0 0x05461000 0x0 0xfff>, /* tcon-lcd0 */ <0x0 0x05470000 0x0 0xfff>, /* tcon-tv */ <0x0 0x05450000 0x0 0x1fff>; /* dsi0*/ interrupts = <GIC_SPI 90 IRQ_TYPE_LEVEL_HIGH>,/*tcon-lcd0*/ <GIC_SPI 91 IRQ_TYPE_LEVEL_HIGH>,/*tcon-tv */ <GIC_SPI 92 IRQ_TYPE_LEVEL_HIGH>;/*dsi*/ clocks = <&ccu CLK_DE0>, <&ccu CLK_DE0>, <&ccu CLK_BUS_DE0>, <&ccu CLK_BUS_DE0>, <&ccu CLK_BUS_DPSS_TOP0>, <&ccu CLK_BUS_DPSS_TOP0>, <&ccu CLK_MIPI_DSI>, <&ccu CLK_BUS_MIPI_DSI>, <&ccu CLK_TCON_LCD0>, <&ccu CLK_TCON_TV>, <&ccu CLK_BUS_TCON_LCD0>, <&ccu CLK_BUS_TCON_TV>, <&ccu CLK_MIPI_DSI>, <&ccu CLK_BUS_MIPI_DSI>; clock-names = "clk_de0", "clk_de1", "clk_bus_de0", "clk_bus_de1", "clk_bus_dpss_top0", "clk_bus_dpss_top1", "clk_mipi_dsi0", "clk_bus_mipi_dsi0", "clk_tcon0", "clk_tcon1",/*tcon-tv actually*/ "clk_bus_tcon0", "clk_bus_tcon1",/*tcon-tv actually*/ "clk_mipi_dsi0", "clk_bus_mipi_dsi0"; resets = <&ccu RST_BUS_DE0>, <&ccu RST_BUS_DE0>, <&ccu RST_BUS_DPSS_TOP0>, <&ccu RST_BUS_DPSS_TOP0>, <&ccu RST_BUS_MIPI_DSI>, <&ccu RST_BUS_TCON_LCD0>, <&ccu RST_BUS_TCON_TV>, <&ccu RST_BUS_LVDS0>; reset-names = "rst_bus_de0", "rst_bus_de1", "rst_bus_dpss_top0", "rst_bus_dpss_top1", "rst_bus_mipi_dsi0", "rst_bus_tcon0", "rst_bus_tcon1", "rst_bus_lvds0"; assigned-clocks = <&ccu CLK_DE0>, <&ccu CLK_MIPI_DSI>, <&ccu CLK_TCON_LCD0>, <&ccu CLK_TCON_TV>; assigned-clock-parents = <&ccu CLK_PLL_PERIPH0_2X>, <&ccu CLK_PLL_PERIPH0>, <&ccu CLK_PLL_VIDEO0_4X>, <&ccu CLK_PLL_VIDEO1_4X>; assigned-clock-rates = <300000000>, <150000000>, <0>, <0>; boot_disp = <0>; boot_disp1 = <0>; boot_disp2 = <0>; fb_base = <0>; iommus = <&mmu_aw 2 0>; status = "okay"; }; lcd0: lcd0@5461000 { compatible = "allwinner,sunxi-lcd0"; reg = <0x0 0x05461000 0x0 0xfff>; pinctrl-names = "active","sleep"; status = "okay"; }; tv0: tv0@5600000 { compatible = "allwinner,sunxi-tv"; reg = <0x0 0x05600000 0x0 0x3fff>, <0x0 0x05604000 0x0 0x3fff>; clocks = <&ccu CLK_BUS_TVE_TOP>, <&ccu CLK_TVE>, <&ccu CLK_BUS_TVE>; clock-names = "clk_bus_tve_top", "clk_tve", "clk_bus_tve"; resets = <&ccu RST_BUS_TVE_TOP>, <&ccu RST_BUS_TVE>; reset-names = "rst_bus_tve_top", "rst_bus_tve"; device_type = "tv0"; pinctrl-names = "active","sleep"; status = "okay"; }; hwspinlock: hwspinlock@0x3005000 { compatible = "allwinner,sunxi-hwspinlock"; reg = <0x0 0x3005000 0x0 0x1000>; #hwlock-cells = <1>; clocks = <&ccu CLK_BUS_SPINLOCK>; clock-names = "clk_hwspinlock_bus"; resets = <&ccu RST_BUS_SPINLOCK>; reset-names = "rst"; num-locks = <32>; status = "disabled"; }; /* old msgbox in dts msgbox: msgbox@3003000 { compatible = "sunxi,msgbox-amp"; reg = <0x0 0x03003000 0x0 0x1000>, <0x0 0x01701000 0x0 0x1000>, <0x0 0x0601f000 0x0 0x1000>; interrupts = <GIC_SPI 0 IRQ_TYPE_LEVEL_HIGH>, <GIC_SPI 123 IRQ_TYPE_LEVEL_HIGH>, <GIC_SPI 130 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_MSGBOX0>; rpmsg_id = "sunxi,dsp-msgbox","sunxi,dsp-power-msgbox"; resets = <&ccu RST_BUS_MSGBOX0>; reset-names = "rst"; msgbox_amp_counts = <3>; msgbox_amp_local = <0>; rpmsg_amp_remote-0 = <1>; rpmsg_read_channel-0 = <1>; rpmsg_write_channel-0 = <1>; rpmsg_amp_remote-1 = <1>; rpmsg_read_channel-1 = <0>; rpmsg_write_channel-1 = <0>; }; */ msgbox: msgbox@3003000 { compatible = "allwinner,sun8iw20-msgbox"; #mbox-cells = <1>; reg = <0x0 0x03003000 0x0 0x1000>, <0x0 0x01701000 0x0 0x1000>, <0x0 0x0601f000 0x0 0x1000>; interrupts = <GIC_SPI 0 IRQ_TYPE_LEVEL_HIGH>, <GIC_SPI 123 IRQ_TYPE_LEVEL_HIGH>, <GIC_SPI 130 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_MSGBOX0>; resets = <&ccu RST_BUS_MSGBOX0>; reset-names = "rst"; local_id = <0>; status = "okay"; }; hdmi: hdmi@5500000 { compatible = "allwinner,sunxi-hdmi"; reg = <0x0 0x05500000 0x0 0xfffff>; interrupts = <GIC_SPI 93 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_HDMI>, <&ccu CLK_HDMI_24M>, <&ccu CLK_HDMI_CEC>, <&ccu CLK_TCON_TV>; clock-names = "clk_bus_hdmi", "clk_ddc", "clk_cec", "clk_tcon_tv"; resets = <&ccu RST_BUS_HDMI_SUB>, <&ccu RST_BUS_HDMI_MAIN>; reset-names = "rst_bus_sub", "rst_bus_main"; assigned-clocks = <&ccu CLK_HDMI_CEC>; assigned-clock-parents = <&ccu CLK_HDMI_CEC_32K>; assigned-clock-rates = <0>; status = "okay"; }; usbc0:usbc0@0 { device_type = "usbc0"; compatible = "allwinner,sunxi-otg-manager"; usb_port_type = <2>; usb_detect_type = <1>; usb_id_gpio; usb_det_vbus_gpio; usb_regulator_io = "nocare"; usb_wakeup_suspend = <0>; usb_luns = <3>; usb_serial_unique = <0>; usb_serial_number = "20080411"; rndis_wceis = <1>; status = "okay"; }; udc:udc-controller@0x04100000 { compatible = "allwinner,sunxi-udc"; reg = <0x0 0x04100000 0x0 0x1000>, /*udc base*/ <0x0 0x00000000 0x0 0x100>; /*sram base*/ interrupts = <GIC_SPI 29 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_OTG>; clock-names = "bus_otg"; resets = <&ccu RST_BUS_OTG>, <&ccu RST_USB_PHY0>; reset-names = "otg", "phy"; status = "okay"; }; ehci0:ehci0-controller@0x04101000 { compatible = "allwinner,sunxi-ehci0"; reg = <0x0 0x04101000 0x0 0xFFF>, /*hci0 base*/ <0x0 0x00000000 0x0 0x100>, /*sram base*/ <0x0 0x04100000 0x0 0x1000>; /*otg base*/ interrupts = <GIC_SPI 30 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_EHCI0>; clock-names = "bus_hci"; resets = <&ccu RST_BUS_EHCI0>, <&ccu RST_USB_PHY0>; reset-names = "hci", "phy"; hci_ctrl_no = <0>; status = "okay"; }; ohci0:ohci0-controller@0x04101400 { compatible = "allwinner,sunxi-ohci0"; reg = <0x0 0x04101400 0x0 0xFFF>, /*hci0 base*/ <0x0 0x00000000 0x0 0x100>, /*sram base*/ <0x0 0x04100000 0x0 0x1000>; /*otg base*/ interrupts = <GIC_SPI 31 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_OHCI0>, <&ccu CLK_USB_OHCI0>; clock-names = "bus_hci", "ohci"; resets = <&ccu RST_BUS_OHCI0>, <&ccu RST_USB_PHY0>; reset-names = "hci", "phy"; hci_ctrl_no = <0>; status = "okay"; }; usbc1:usbc1@0 { device_type = "usbc1"; usb_regulator_io = "nocare"; usb_wakeup_suspend = <0>; status = "disable"; }; ehci1:ehci1-controller@0x04200000 { compatible = "allwinner,sunxi-ehci1"; reg = <0x0 0x04200000 0x0 0xFFF>, /*ehci1 base*/ <0x0 0x00000000 0x0 0x100>, /*sram base*/ <0x0 0x04100000 0x0 0x1000>; /*otg base*/ interrupts = <GIC_SPI 33 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_EHCI1>; clock-names = "bus_hci"; resets = <&ccu RST_BUS_EHCI1>, <&ccu RST_USB_PHY1>; reset-names = "hci", "phy"; hci_ctrl_no = <1>; status = "disable"; }; ohci1:ohci1-controller@0x04200400 { compatible = "allwinner,sunxi-ohci1"; reg = <0x0 0x04200400 0x0 0xFFF>, /*ohci1 base*/ <0x0 0x00000000 0x0 0x100>, /*sram base*/ <0x0 0x04100000 0x0 0x1000>; /*otg base*/ interrupts = <GIC_SPI 34 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_OHCI1>, <&ccu CLK_USB_OHCI1>; clock-names = "bus_hci", "ohci"; resets = <&ccu RST_BUS_OHCI1>, <&ccu RST_USB_PHY1>; reset-names = "hci", "phy"; hci_ctrl_no = <1>; status = "disable"; }; /* codec addr: 0x02030000, the others is invalid to avoid build warining */ codec:codec@2030000 { #sound-dai-cells = <0>; compatible = "allwinner,sunxi-internal-codec"; reg = <0x0 0x02030000 0x0 0x34c>; clocks = <&ccu CLK_PLL_AUDIO0>, <&ccu CLK_PLL_AUDIO1_DIV5>, <&ccu CLK_AUDIO_DAC>, <&ccu CLK_AUDIO_ADC>, <&ccu CLK_BUS_AUDIO_CODEC>; clock-names = "pll_audio0", "pll_audio1_div5", "audio_clk_dac", "audio_clk_adc", "audio_clk_bus"; resets = <&ccu RST_BUS_AUDIO_CODEC>; rx_sync_en = <0x00>; device_type = "codec"; status = "okay"; }; dummy_cpudai:dummy_cpudai@203034c { compatible = "allwinner,sunxi-dummy-cpudai"; reg = <0x0 0x0203034c 0x0 0x4>; tx_fifo_size = <128>; rx_fifo_size = <256>; dac_txdata = <0x02030020>; adc_txdata = <0x02030040>; playback_cma = <128>; capture_cma = <256>; device_type = "cpudai"; dmas = <&dma 7>, <&dma 7>; dma-names = "tx", "rx"; status = "okay"; }; sndcodec:sound@2030340 { compatible = "allwinner,sunxi-codec-machine"; reg = <0x0 0x02030340 0x0 0x4>; interrupts = <GIC_SPI 25 IRQ_TYPE_LEVEL_HIGH>; sunxi,audio-codec = <&codec>; sunxi,cpudai-controller = <&dummy_cpudai>; device_type = "sndcodec"; status = "okay"; }; sunxi_rpaf_dsp0:rpaf-dsp@203034c { compatible = "allwinner,rpaf-dsp0"; device_type = "sunxi_rpaf_dsp0"; dsp_id = <0x0>; status = "okay"; }; /* dmic addr: 0x02031000, the others is invalid to avoid build warining */ dmic:dmic@2031000{ #sound-dai-cells = <0>; compatible = "allwinner,sunxi-dmic"; reg = <0x0 0x02031000 0x0 0x50>; clocks = <&ccu CLK_PLL_AUDIO0>, /* 98.304M / 90.3168M */ <&ccu CLK_DMIC>, <&ccu CLK_BUS_DMIC>; clock-names = "pll_audio", "dmic", "dmic_bus"; resets = <&ccu RST_BUS_DMIC>; dmas = <&dma 8>; dma-names = "rx"; interrupts = <GIC_SPI 24 IRQ_TYPE_LEVEL_HIGH>; clk_parent = <0x1>; capture_cma = <256>; data_vol = <0xB0>; rx_chmap = <0x76543210>; rx_sync_en = <0x00>; device_type = "dmic"; status = "disabled"; }; dmic_codec:sound@2031050{ #sound-dai-cells = <0>; compatible = "dmic-codec"; reg = <0x0 0x02031050 0x0 0x4>; num-channels = <8>; }; sounddmic:sounddmic@2031060 { reg = <0x0 0x02031060 0x0 0x4>; compatible = "sunxi,simple-audio-card"; simple-audio-card,name = "snddmic"; simple-audio-card,capture_only; status = "disabled"; /* simple-audio-card,format = "i2s"; */ simple-audio-card,cpu { sound-dai = <&dmic>; }; simple-audio-card,codec { sound-dai = <&dmic_codec>; }; }; /* daudio0 addr: 0x02032000, the others is invalid to avoid build warining */ daudio0:daudio@2032000 { #sound-dai-cells = <0>; compatible = "allwinner,sunxi-daudio"; reg = <0x0 0x02032000 0x0 0xa0>; clocks = <&ccu CLK_PLL_AUDIO0>, /* 98.304M / 90.3168M */ <&ccu CLK_I2S0>, <&ccu CLK_BUS_I2S0>; clock-names = "pll_audio", "i2s0", "i2s0_bus"; resets = <&ccu RST_BUS_I2S0>; dmas = <&dma 3>, <&dma 3>; dma-names = "tx", "rx"; interrupts = <GIC_SPI 26 IRQ_TYPE_LEVEL_HIGH>; pinctrl_used = <0x01>; sign_extend = <0x00>; tx_data_mode = <0x00>; rx_data_mode = <0x00>; msb_lsb_first = <0x00>; pcm_lrck_period = <0x80>; slot_width_select = <0x20>; frametype = <0x00>; tdm_config = <0x01>; tdm_num = <0x00>; mclk_div = <0x00>; clk_parent = <0x00>; capture_cma = <128>; playback_cma = <128>; tx_num = <4>; tx_chmap1 = <0x76543210>; tx_chmap0 = <0xFEDCBA98>; rx_num = <4>; rx_chmap3 = <0x03020100>; rx_chmap2 = <0x07060504>; rx_chmap1 = <0x0B0A0908>; rx_chmap0 = <0x0F0E0D0C>; asrc_function_en = <0x00>; rx_sync_en = <0x00>; device_type = "daudio0"; status = "disabled"; }; sounddaudio0: sounddaudio0@20320a0 { reg = <0x0 0x020320a0 0x0 0x4>; compatible = "sunxi,simple-audio-card"; simple-audio-card,name = "snddaudio0"; simple-audio-card,format = "i2s"; status = "disabled"; /* simple-audio-card,frame-master = <&daudio0_master>; */ /* simple-audio-card,bitclock-master = <&daudio0_master>; */ /* simple-audio-card,bitclock-inversion; */ /* simple-audio-card,frame-inversion; */ simple-audio-card,cpu { sound-dai = <&daudio0>; }; }; /* daudio1 addr: 0x02033000, the others is invalid to avoid build warining */ daudio1:daudio@2033000 { #sound-dai-cells = <0>; compatible = "allwinner,sunxi-daudio"; reg = <0x0 0x02033000 0x0 0xa0>; clocks = <&ccu CLK_PLL_AUDIO0>, /* 98.304M / 90.3168M */ <&ccu CLK_I2S1>, <&ccu CLK_BUS_I2S1>; clock-names = "pll_audio", "i2s1", "i2s1_bus"; resets = <&ccu RST_BUS_I2S1>; dmas = <&dma 4>, <&dma 4>; dma-names = "tx", "rx"; interrupts = <GIC_SPI 27 IRQ_TYPE_LEVEL_HIGH>; pinctrl_used = <0x01>; sign_extend = <0x00>; tx_data_mode = <0x00>; rx_data_mode = <0x00>; msb_lsb_first = <0x00>; pcm_lrck_period = <0x80>; slot_width_select = <0x20>; frametype = <0x00>; tdm_config = <0x01>; tdm_num = <0x01>; mclk_div = <0x00>; clk_parent = <0x00>; capture_cma = <128>; playback_cma = <128>; tx_num = <4>; tx_chmap1 = <0x76543210>; tx_chmap0 = <0xFEDCBA98>; rx_num = <4>; rx_chmap3 = <0x03020100>; rx_chmap2 = <0x07060504>; rx_chmap1 = <0x0B0A0908>; rx_chmap0 = <0x0F0E0D0C>; asrc_function_en = <0x00>; rx_sync_en = <0x00>; device_type = "daudio1"; status = "disabled"; }; sounddaudio1: sounddaudio1@20330a0 { reg = <0x0 0x020330a0 0x0 0x4>; compatible = "sunxi,simple-audio-card"; simple-audio-card,name = "snddaudio1"; simple-audio-card,format = "i2s"; status = "disabled"; simple-audio-card,cpu { sound-dai = <&daudio1>; }; }; /* daudio2 addr: 0x02034000, the others is invalid to avoid build warining */ daudio2:daudio@2034000 { #sound-dai-cells = <0>; compatible = "allwinner,sunxi-daudio"; reg = <0x0 0x02034000 0x0 0xa0>; clocks = <&ccu CLK_PLL_AUDIO0>, /* 98.304M / 90.3168M */ <&ccu CLK_I2S2>, <&ccu CLK_BUS_I2S2>, <&ccu CLK_PLL_AUDIO0_4X>, <&ccu CLK_I2S2_ASRC>; resets = <&ccu RST_BUS_I2S2>; dmas = <&dma 5>, <&dma 5>; dma-names = "tx", "rx"; interrupts = <GIC_SPI 28 IRQ_TYPE_LEVEL_HIGH>; pinctrl_used = <0x01>; daudio_type = <0x00>; sign_extend = <0x00>; tx_data_mode = <0x00>; rx_data_mode = <0x00>; msb_lsb_first = <0x00>; pcm_lrck_period = <0x80>; slot_width_select = <0x20>; frametype = <0x00>; tdm_config = <0x01>; tdm_num = <0x02>; mclk_div = <0x01>; clk_parent = <0x00>; capture_cma = <128>; playback_cma = <128>; tx_num = <4>; tx_chmap1 = <0x76543210>; tx_chmap0 = <0xFEDCBA98>; rx_num = <4>; rx_chmap3 = <0x03020100>; rx_chmap2 = <0x07060504>; rx_chmap1 = <0x0B0A0908>; rx_chmap0 = <0x0F0E0D0C>; asrc_function_en = <0x00>; rx_sync_en = <0x00>; device_type = "daudio2"; status = "disabled"; }; sounddaudio2: sounddaudio2@20340a0 { reg = <0x0 0x020340a0 0x0 0x4>; compatible = "sunxi,simple-audio-card"; simple-audio-card,name = "snddaudio2"; simple-audio-card,format = "i2s"; status = "disabled"; simple-audio-card,cpu { sound-dai = <&daudio2>; }; }; hdmiaudio: hdmiaudio@20340a4 { #sound-dai-cells = <0>; reg = <0x0 0x020340a4 0x0 0x4>; compatible = "allwinner,sunxi-hdmiaudio"; status = "disabled"; }; /* spdif addr: 0x02036000, the others is invalid to avoid build warining */ spdif:spdif@2036000 { #sound-dai-cells = <0>; compatible = "allwinner,sunxi-spdif"; reg = <0x0 0x02036000 0x0 0x58>; clocks = <&ccu CLK_PLL_AUDIO0_4X>, /* 90.3168M */ <&ccu CLK_SPDIF_TX>, <&ccu CLK_BUS_SPDIF>, <&ccu CLK_PLL_AUDIO1>, /* 98.304M */ <&ccu CLK_PLL_AUDIO1_DIV5>, <&ccu CLK_PLL_PERIPH0>, <&ccu CLK_SPDIF_RX>; clock-names = "pll_audio0", "spdif", "spdif_bus", "pll_audio1", "pll_audio1_div5", "pll_periph", "spdif_rx"; resets = <&ccu RST_BUS_SPDIF>; dmas = <&dma 2>, <&dma 2>; dma-names = "tx", "rx"; interrupts = <GIC_SPI 23 IRQ_TYPE_LEVEL_HIGH>; clk_parent = <0x1>; playback_cma = <128>; capture_cma = <128>; rx_sync_en = <0>; device_type = "spdif"; status = "disabled"; }; soundspdif:soundspdif@203605c { reg = <0x0 0x0203605c 0x0 0x4>; compatible = "sunxi,simple-audio-card"; simple-audio-card,name = "sndspdif"; status = "disabled"; /* simple-audio-card,format = "i2s"; */ simple-audio-card,cpu { sound-dai = <&spdif>; }; simple-audio-card,codec { /*snd-soc-dummy*/ }; }; ths: ths@02009400 { compatible = "allwinner,sun8iw20p1-ths"; reg = <0x0 0x02009400 0x0 0x400>; clocks = <&ccu CLK_BUS_THS>; clock-names = "bus"; resets = <&ccu RST_BUS_THS>; nvmem-cells = <&ths_calib>; nvmem-cell-names = "calibration"; #thermal-sensor-cells = <1>; }; tvd: tvd@05c00000 { compatible = "allwinner,sunxi-tvd"; reg = <0x0 0x05c00000 0x0 0x00010000>;/*tvd_top*/ interrupts = <GIC_SPI 107 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_BUS_TVD_TOP>, <&ccu CLK_MBUS_TVIN>; clock-names = "clk_bus_tvd_top", "clk_mbus_tvd"; resets = <&ccu RST_BUS_TVD_TOP>; reset-names = "rst_bus_tvd_top"; tvd-number = <1>; tvds = <&tvd0>; status = "okay"; }; tvd0: tvd0@05c01000 { compatible = "allwinner,sunxi-tvd0"; reg = <0x0 0x05c01000 0x0 0x00010000>; interrupts = <GIC_SPI 107 IRQ_TYPE_LEVEL_HIGH>; clocks = <&ccu CLK_TVD>, <&ccu CLK_BUS_TVD>; clock-names = "clk_tvd0","clk_bus_tvd0"; resets = <&ccu RST_BUS_TVD>; reset-names = "rst_bus_tvd0"; assigned-clocks = <&ccu CLK_TVD>; assigned-clock-parents = <&ccu CLK_PLL_VIDEO1>; tvd_used = <1>; tvd_if = <0>; status = "okay"; }; }; };sun8iw20p1.dtsi