f1c100s USB问题请教

-

f1c100s上跑主线linux5.7。使用在使用USB的过程中发现有以下问题:从U盘读取文件放到SD卡,计算MD5,源文件与复制文件校验码一致。但从SD卡读文件放到U盘上,就有10%的概率文件会出错。是USB驱动有问题么?下面是我的设备树文件:

// SPDX-License-Identifier: (GPL-2.0+ OR X11) /* * Copyright 2018 Icenowy Zheng <icenowy@aosc.io> * Copyright 2018 Mesih Kilinc <mesihkilinc@gmail.com> */ #include <dt-bindings/clock/suniv-ccu-f1c100s.h> #include <dt-bindings/reset/suniv-ccu-f1c100s.h> #include <dt-bindings/interrupt-controller/irq.h> / { #address-cells = <1>; #size-cells = <1>; interrupt-parent = <&intc>; clocks { #address-cells = <1>; #size-cells = <1>; ranges; osc24M: clk-24M { #clock-cells = <0>; compatible = "fixed-clock"; clock-frequency = <24000000>; clock-output-names = "osc24M"; }; osc32k: clk-32k { #clock-cells = <0>; compatible = "fixed-clock"; clock-frequency = <32768>; clock-output-names = "osc32k"; }; fake100M: clk-100M { #clock-cells = <0>; compatible = "fixed-clock"; clock-frequency = <100000000>; clock-output-names = "fake-100M"; }; }; cpus { cpu { compatible = "arm,arm926ej-s"; device_type = "cpu"; }; }; soc { compatible = "simple-bus"; #address-cells = <1>; #size-cells = <1>; ranges; sram-controller@1c00000 { compatible = "allwinner,suniv-f1c100s-system-control", "allwinner,sun4i-a10-system-control"; reg = <0x01c00000 0x30>; #address-cells = <1>; #size-cells = <1>; ranges; sram_d: sram@10000 { compatible = "mmio-sram"; reg = <0x00010000 0x1000>; #address-cells = <1>; #size-cells = <1>; ranges = <0 0x00010000 0x1000>; otg_sram: sram-section@0 { compatible = "allwinner,suniv-f1c100s-sram-d", "allwinner,sun4i-a10-sram-d"; reg = <0x0000 0x1000>; status = "disabled"; }; }; }; ccu: clock@1c20000 { compatible = "allwinner,suniv-f1c100s-ccu"; reg = <0x01c20000 0x400>; clocks = <&osc24M>, <&osc32k>; clock-names = "hosc", "losc"; #clock-cells = <1>; #reset-cells = <1>; }; intc: interrupt-controller@1c20400 { compatible = "allwinner,suniv-f1c100s-ic"; reg = <0x01c20400 0x400>; interrupt-controller; #interrupt-cells = <1>; }; pio: pinctrl@1c20800 { compatible = "allwinner,suniv-f1c100s-pinctrl"; reg = <0x01c20800 0x400>; interrupts = <38>, <39>, <40>; clocks = <&ccu 37>, <&osc24M>, <&osc32k>; clock-names = "apb", "hosc", "losc"; gpio-controller; interrupt-controller; #interrupt-cells = <3>; #gpio-cells = <3>; uart0_pe_pins: uart0-pe-pins { pins = "PE0", "PE1"; function = "uart0"; }; mmc0_pins: mmc0-pins { pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5"; function = "mmc0"; }; }; timer@1c20c00 { compatible = "allwinner,suniv-f1c100s-timer"; reg = <0x01c20c00 0x90>; interrupts = <13>; clocks = <&osc24M>; }; wdt: watchdog@1c20ca0 { compatible = "allwinner,suniv-f1c100s-wdt", "allwinner,sun4i-a10-wdt"; reg = <0x01c20ca0 0x20>; }; uart0: serial@1c25000 { compatible = "snps,dw-apb-uart"; reg = <0x01c25000 0x400>; interrupts = <1>; reg-shift = <2>; reg-io-width = <4>; clocks = <&ccu 38>; resets = <&ccu 24>; status = "disabled"; }; uart1: serial@1c25400 { compatible = "snps,dw-apb-uart"; reg = <0x01c25400 0x400>; interrupts = <2>; reg-shift = <2>; reg-io-width = <4>; clocks = <&ccu 39>; resets = <&ccu 25>; status = "disabled"; }; uart2: serial@1c25800 { compatible = "snps,dw-apb-uart"; reg = <0x01c25800 0x400>; interrupts = <3>; reg-shift = <2>; reg-io-width = <4>; clocks = <&ccu 40>; resets = <&ccu 26>; status = "disabled"; }; mmc0: mmc@1c0f000 { compatible = "allwinner,suniv-f1c100s-mmc", "allwinner,sun7i-a20-mmc"; reg = <0x01c0f000 0x1000>; clocks = <&ccu CLK_BUS_MMC0>, <&ccu CLK_MMC0>, <&ccu CLK_MMC0_OUTPUT>, <&ccu CLK_MMC0_SAMPLE>; clock-names = "ahb", "mmc", "output", "sample"; resets = <&ccu RST_BUS_MMC0>; reset-names = "ahb"; interrupts = <23>; pinctrl-names = "default"; pinctrl-0 = <&mmc0_pins>; status = "disabled"; #address-cells = <1>; #size-cells = <0>; }; usb_otg: usb@1c13000 { // compatible = "allwinner,suniv-musb"; compatible = "allwinner,sun4i-a10-musb"; reg = <0x01c13000 0x0400>; clocks = <&ccu CLK_BUS_OTG>; resets = <&ccu RST_BUS_OTG>; interrupts = <26>; interrupt-names = "mc"; phys = <&usbphy 0>; phy-names = "usb"; extcon = <&usbphy 0>; allwinner,sram = <&otg_sram 1>; status = "disabled"; }; usbphy: phy@1c13400 { // compatible = "allwinner,suniv-usb-phy"; compatible = "allwinner,sun4i-a10-usb-phy"; reg = <0x01c13400 0x10>; reg-names = "phy_ctrl"; clocks = <&ccu CLK_USB_PHY0>; clock-names = "usb0_phy"; resets = <&ccu RST_USB_PHY0>; reset-names = "usb0_reset"; #phy-cells = <1>; status = "disabled"; }; }; }; -

@smbzd 在 f1c100s USB问题请教 中说:

linux5.7

关于DTS,唯一的问题是 :

// compatible = "allwinner,suniv-musb";

compatible = "allwinner,sun4i-a10-musb";您使用什么驱动程序?

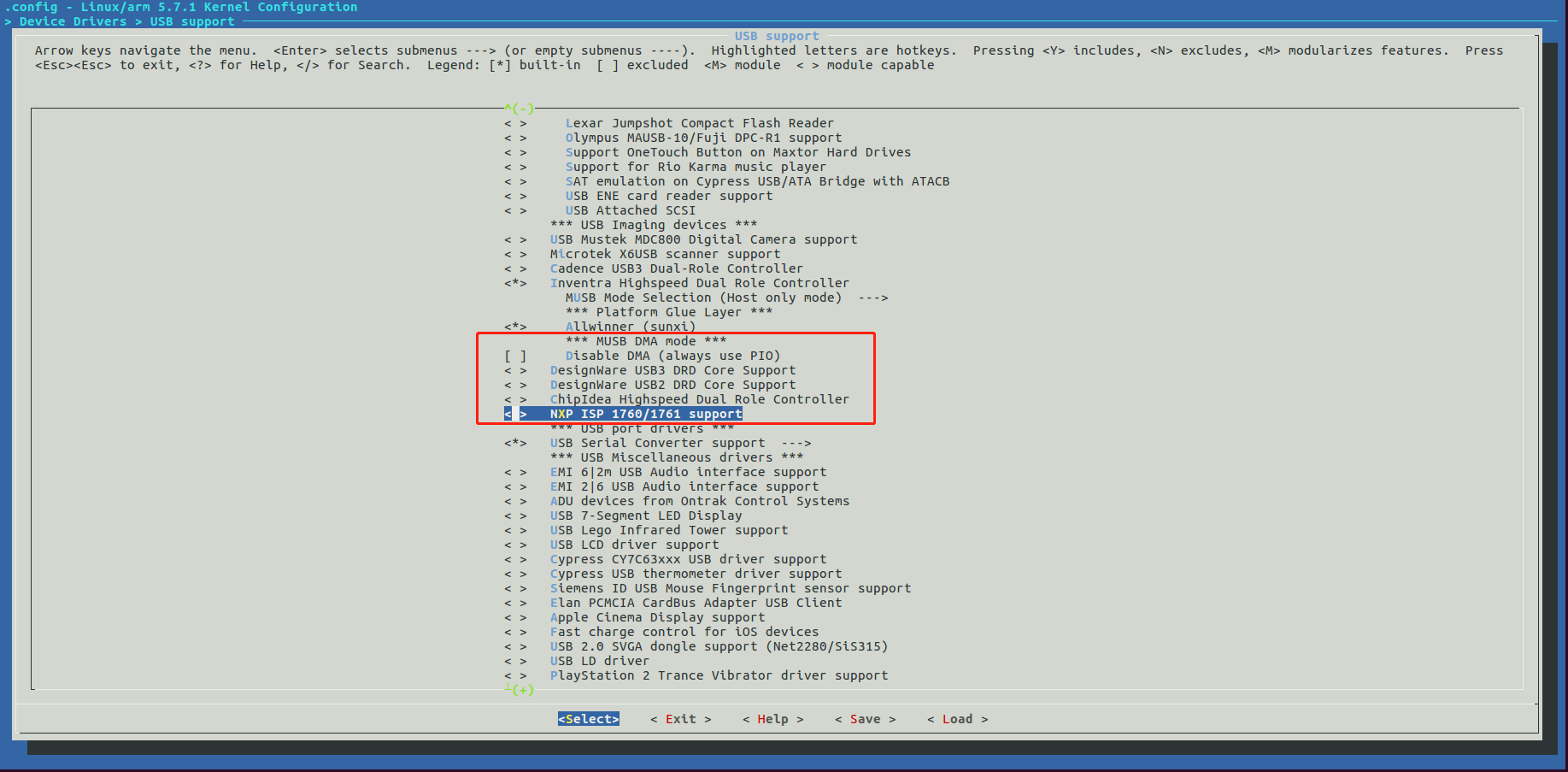

MUSB 设置是什么:DMA 还是 PIO?

-

@alb702 感谢回复。我不太清楚在哪里确定是DMA还是PIO模式,但在menuconfig上我没有勾选Disable DMA,我猜测应该是DMA模式的。

是需要禁用DMA么? -

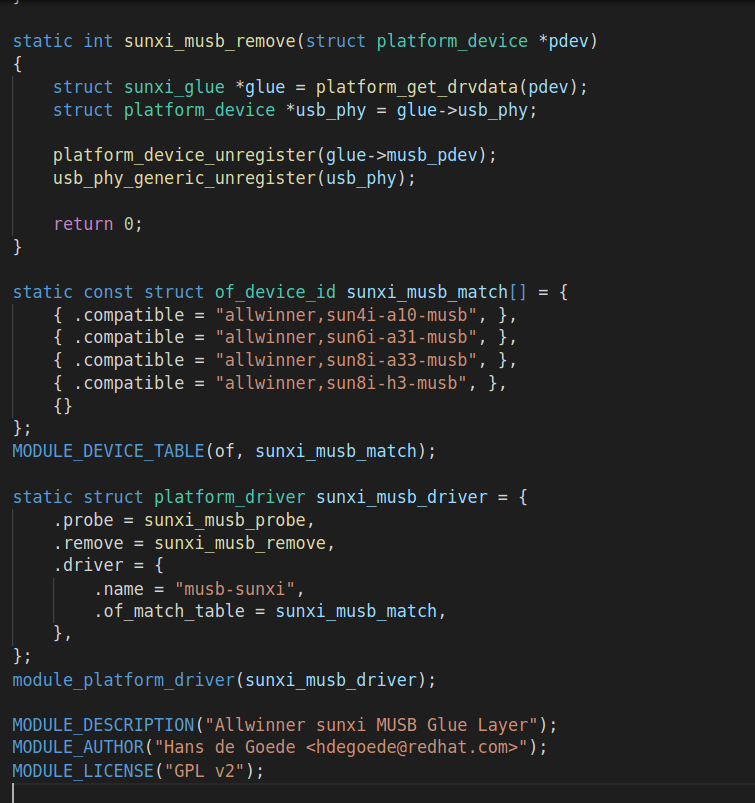

@alb702 驱动程序用的是musb-sunxi

-

@smbzd 在 f1c100s USB问题请教 中说:

musb-sunxi

你有DMA。 一切安好。 这可能不是这里的问题。

Linux 文档说您可以在 SCSI 协议中启用数据完整性检查。

https://docs.kernel.org/block/data-integrity.html : Block Layer Integrity API

您可以尝试这个方法来澄清问题。

-

@alb702 好的,非常感谢您的建议。我会尝试一下

Copyright © 2024 深圳全志在线有限公司 粤ICP备2021084185号 粤公网安备44030502007680号