实测52.4MB/s!全志T3+FPGA的CSI通信案例分享!

-

CSI总线介绍与优势

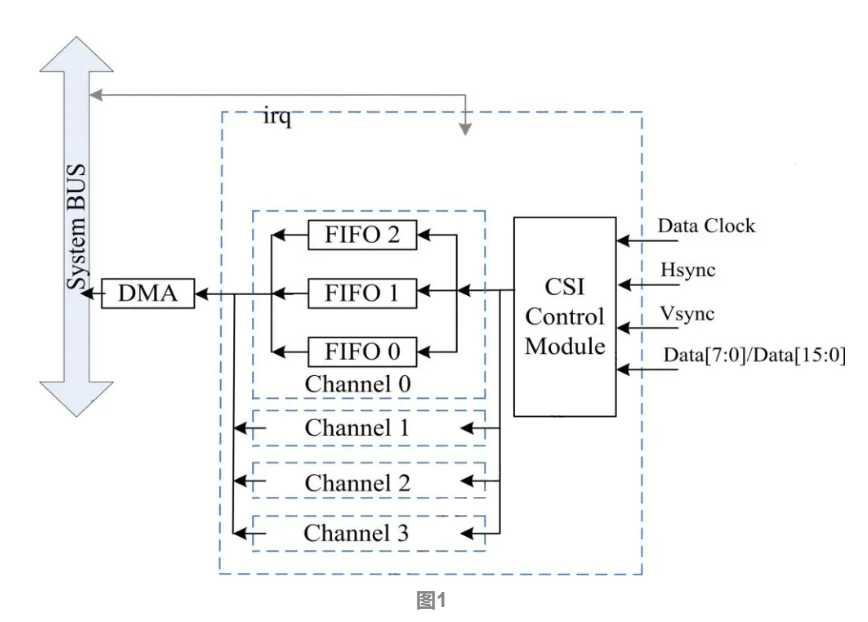

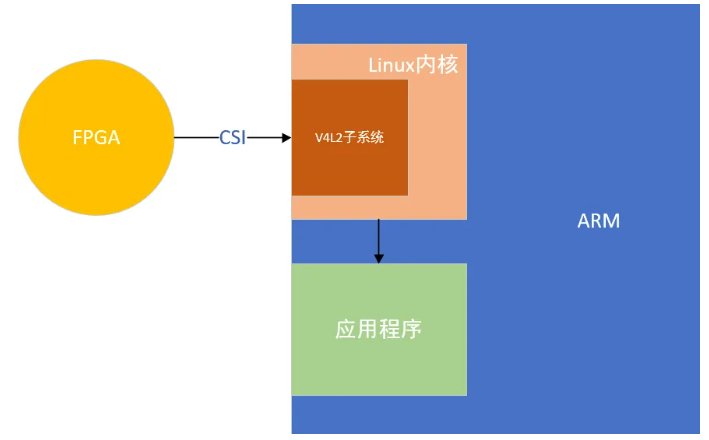

CSI(CMOS sensor parallel interfaces)总线是一种用于连接图像传感器和处理器的并行通信接口,应用于工业自动化、能源电力、智慧医疗等领域,CSI总线接口示意图如下所示(以全志科技T3处理器的CSI0为例)。

高带宽:CSI总线支持高速数据传输,可以满足多通道高速AD数据的传输需求。

开发难度低:CSI总线采用并行数据和控制信号分离方式,时序简单,FPGA端接口开发难度低。

低成本:CSI总线采用并行传输方式,FPGA端使用资源少,对FPGA器件资源要求低。

国产ARM + FPGA架构介绍与优势

近年来,随着中国新基建、中国制造2025规划的持续推进,单ARM处理器越来越难胜任工业现场的功能要求,特别是如今能源电力、工业控制、智慧医疗等行业,往往更需要ARM + FPGA架构的处理器平台来实现例如多路/高速AD采集、多路网口、多路串口、多路/高速并行DI/DO、高速数据并行处理等特定功能,因此ARM + FPGA架构处理器平台愈发受市场欢迎。

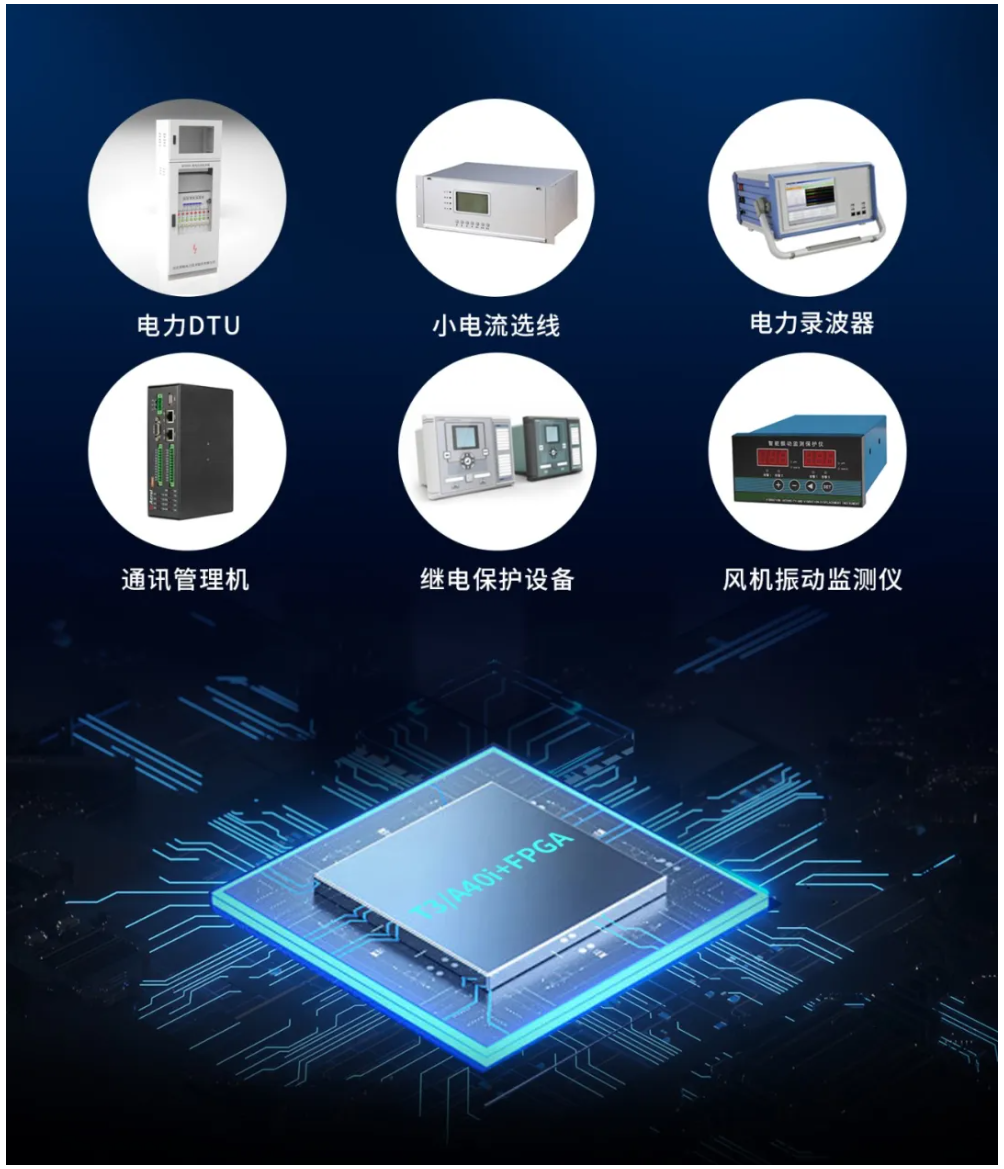

创龙科技SOM-TLT3F是一款基于全志科技T3四核ARM Cortex-A7处理器 + 紫光同创Logos PGL25G/PGL50G FPGA设计的异构多核全国产工业核心板,ARM Cortex-A7处理单元主频高达 1.2GHz。核心板ARM、FPGA、ROM、RAM、电源、晶振、连接器等所有元器件均采用国产工业级方案,国产化率100%。

全志T3为准车规级芯片,四核ARM Cortex-A7架构,主频高达1.2GHz,支持双路网口、八路UART、SATA大容量存储接口,同时支持4路显示、GPU以及1080P H.264视频硬件编解码。另外,创龙科技已在T3平台适配国产嵌入式系统翼辉SylixOS,真正实现软硬件国产化。

国产ARM + FPGA的CSI通信案例介绍

本章节主要介绍全志科技T3与紫光同创Logos基于CSI的ARM + FPGA通信方案,使用的硬件平台为:创龙科技TLT3F-EVM工业评估板。

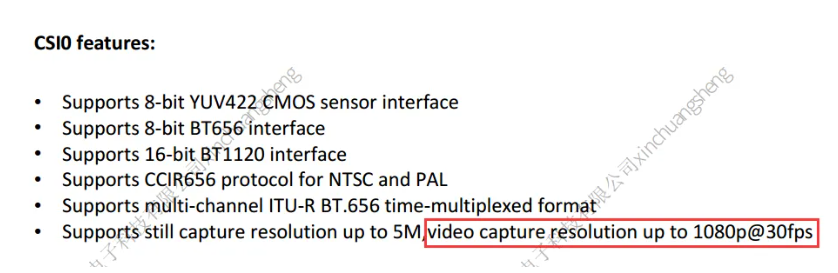

该案例实现T3(ARM Cortex-A7)与FPGA的CSI通信功能。案例使用的CSI0总线,最高支持分辨率为1080P@30fps,数据位宽为8bit,如下图所示。CSI0理论传输带宽为:1920 x 1080 x 8bit x 30fps ≈ 59MB/s。

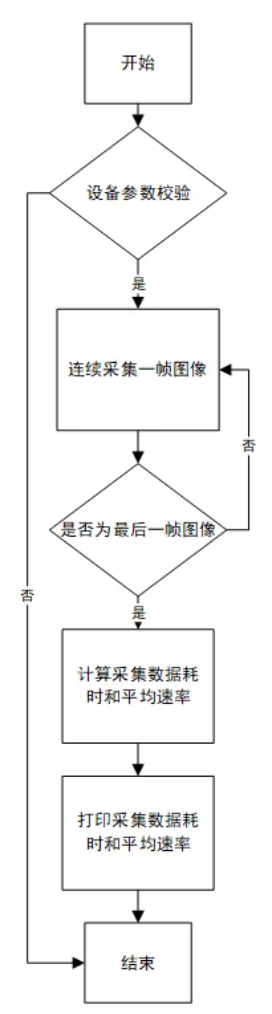

功能框图与程序流程图,如下图所示。

ARM端案例csi_test案例说明

ARM端案例csi_test主要功能如下:

(1)基于Linux子系统V4L2;

(2)通过CSI总线,采集指定帧数数据;

(3)计算总耗时;

(4)打印平均采集速率,并校验最后一帧图像的数据。FPGA端案例parallel_csi_tx案例说明

FPGA端案例parallel_csi_tx主要功能如下:

(1)将测试数据(0x00~0xFF)写入FIFO;

(2)从FIFO读出数据,按行与帧的方式、1024x512的分辨率,通过CSI总线发送至ARM端。

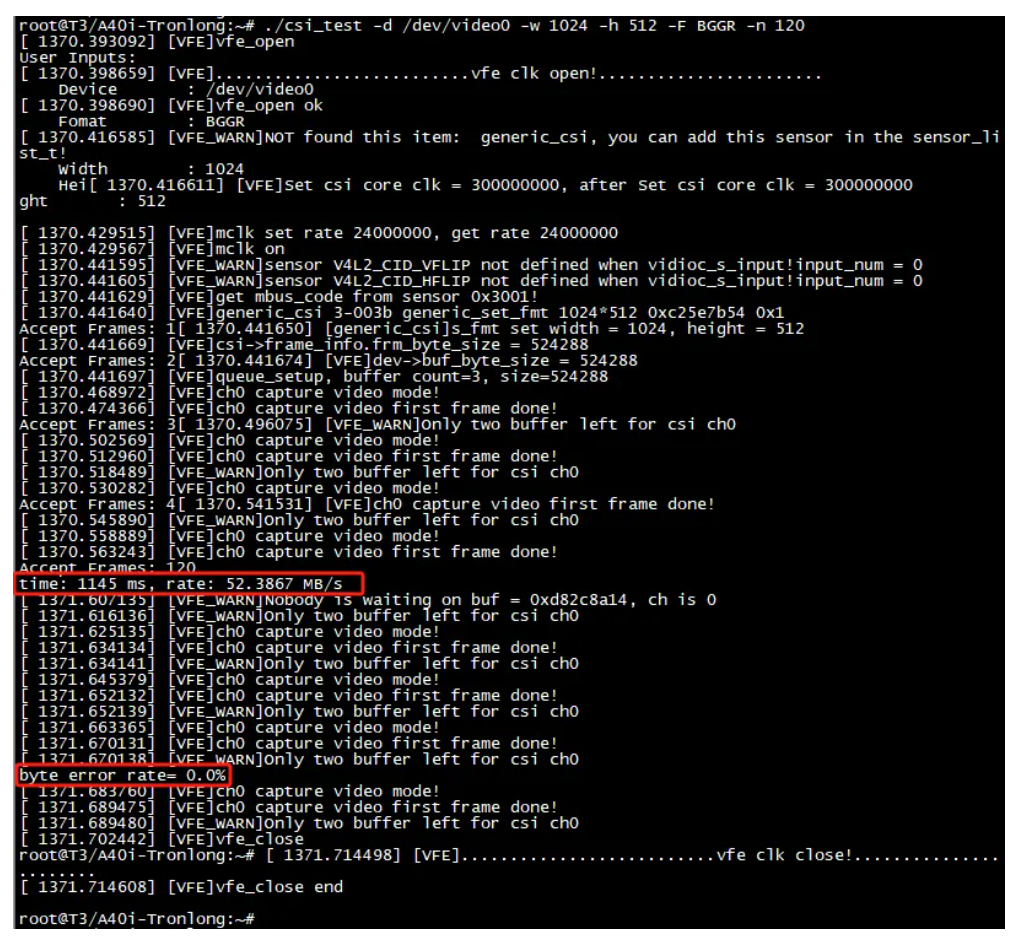

案例测试演示

FPGA程序将CSI_PCLK设置为65MHz,测试数据写入FIFO的时钟FIFO_WR_CLK设置为59MHz。由于FPGA端需将数据写入FIFO再从FIFO读出后发送,每一行与每一帧之间的间隔时间会受FIFO写入的速率影响,因此CSI通信的实际理论传输带宽应为:(59MHz x 8bit / 8)MB/s = 59MB/s。从上图可知,本次实测传输速率约为52.4MB/s,误码率为0,接近理论通信速率。

Copyright © 2024 深圳全志在线有限公司 粤ICP备2021084185号 粤公网安备44030502007680号