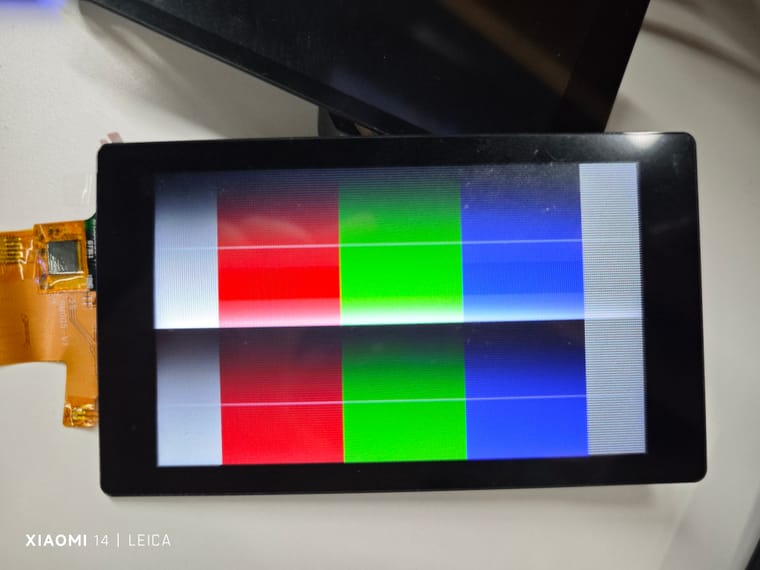

V853S mipi LCD显示驱动调试,colorbar显示异常

-

V853S调试mipi显示驱动时,colorbar输出如下图,顺序有点乱;有大佬知道这是哪块的问题么(驱动,dts),看论坛里大家说是驱动初始化配置的问题,不知大佬能否提供调试思路。

1、echo 2 > /sys/class/disp/disp/attr/colorbar

2、echo 1 > /sys/class/disp/disp/attr/colorbar

3、echo 7 > /sys/class/disp/disp/attr/colorbar

-

dclk过高,屏幕分屏了?

这里提供一个py脚本计算分频系数,这里对应的是HV屏,DSI也可以参考def find_closest_clock(target_clock, clock_list): clock_list = sorted(clock_list) low, high = 0, len(clock_list) - 1 closest = clock_list[low] while low <= high: mid = (low + high) // 2 if clock_list[mid] < target_clock: low = mid + 1 elif clock_list[mid] > target_clock: high = mid - 1 else: return clock_list[mid] if abs(clock_list[mid] - target_clock) < abs(closest - target_clock): closest = clock_list[mid] return closest def calculate_divisor(clock_need, clock_list, min_divisor=6): is_perfect = True for i in clock_list: for j in range(0, 255): if (clock_need * j) == i: closest_clock = i divisor = j return closest_clock, divisor, is_perfect is_perfect = False closest_clock = find_closest_clock(clock_need, clock_list) if closest_clock == 0: return None, None, None divisor = closest_clock // clock_need if divisor < min_divisor: min_diff = float('inf') best_clock = None for clock in clock_list: if clock >= clock_need * min_divisor: current_divisor = clock // clock_need if current_divisor < min_divisor: continue diff = abs(clock - clock_need * current_divisor) if diff < min_diff: min_diff = diff best_clock = clock if best_clock is not None: return best_clock, best_clock // clock_need, is_perfect return closest_clock, divisor, is_perfect clock_list = [ 408, 420, 432, 444, 456, 468, 480, 492, 504, 516, 528, 540, 552, 564, 576, 588, 600, 612, 624, 636, 648, 660, 672, 684, 696, 708, 720, 732, 744, 756, 768, 780, 792, 804, 816, 828, 840, 852, 864, 876, 888, 900, 912, 924, 936, 948, 960, 972, 984, 996, 1008, 1020, 1032, 1044, 1056, 1068, 1080, 1092, 1104, 1116, 1128, 1140, 1152, 1164, 1176, 1188, 1200, 1212, 1224, 1236, 1248, 1260, 1272, 1284, 1296, 1308, 1320, 1332, 1344, 1356, 1368, 1380, 1392, 1404, 1416, 1428, 1440, 1452, 1464, 1476, 1488, 1500, 1512, 1524, 1536, 1548, 1560, 1572, 1584, 1596, 1608, 1620, 1632, 1644, 1656, 1668, 1680, 1692 ] clock_need = int(input("请输入需要的时钟(MHz): ")) closest_clock, divisor, is_perfect = calculate_divisor(clock_need, clock_list) if is_perfect: print(f"父时钟: {closest_clock}MHz, 分频系数: {divisor}, 分频后的频率: {closest_clock / divisor}MHz") else: print(f"无法找到完美,最近的父时钟: {closest_clock}, 分频系数: {divisor}, 分频后的频率: {closest_clock / divisor}MHz") print("请修改分频系数表 clk_tbl 中 HV 分频系数为: {LCD_IF_HV, " + hex(divisor) + ", 1, 1, 0}")

Copyright © 2024 深圳全志在线有限公司 粤ICP备2021084185号 粤公网安备44030502007680号