【玩转多核异构】T153核心板RISC-V核的实时性应用解析

-

在智能硬件功能持续升级的当下,传统单片机以及传统的MPU都面临着“力不从心”的困境——多网络协同、多串口并发、多通道无线通信等复杂需求,以及文件管理、数据加密、人机交互、数据压缩等增强功能,单核方案已难以全面承载。

在这样的背景下,“管理核+实时核”的双核异构架构的方案逐渐脱颖而出,成为破局关键。因此,选择一款集成度高、通信效率优、成本可控的多核异构主控平台,就成为破解当前困局的更优答案。

1、FET153-S核心板

飞凌嵌入式FET153-S核心板基于全志T153处理器设计,面向工业与电力应用。该处理器集成四核Cortex-A7与一颗独立64位玄铁E907 RISC-V MCU,具备丰富的接口资源与工业级可靠性,完美契合现代FTU对处理性能与实时性的双重需求。此外,T153处理器还提供10路UART、24路GPADC、6路TWI接口、30路PWM等接口,这些接口为多样化应用提供灵活性。

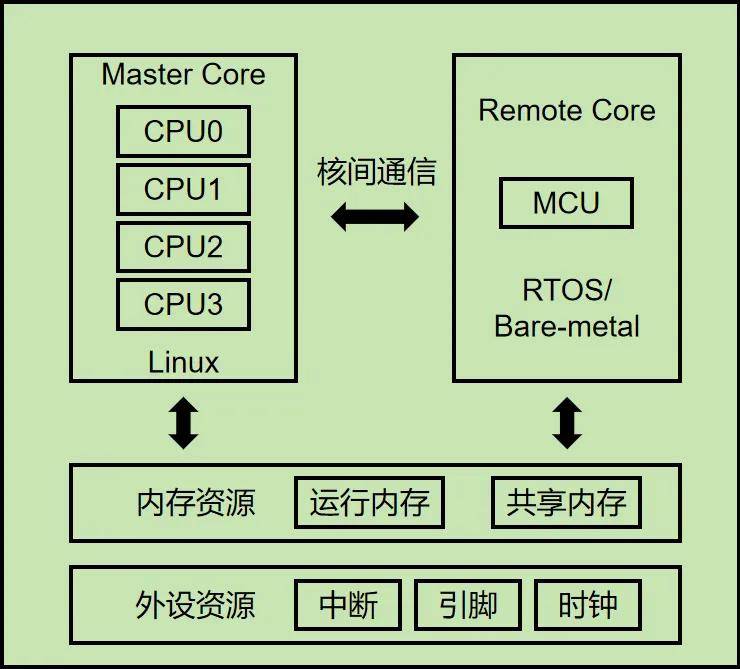

01、实时方案: AP+MCU系统架构

飞凌嵌入式FET153-S核心板支持AP+MCU模式的实时方案。AP+MCU系统架构为Linux+MCU RTOS/Bare-metal。运行LinuxAP处理器核心作为主核(Master Core);运行RTOS/Bare-metal的MCU处理器核心作为从核(Remote Core)。主核负责整个多核异构系统中共享资源的划分和管理,并运行主站服务程序。

02、RISC-V核的接口资源

注:上表中功能均已测试通过。

2、应用实例

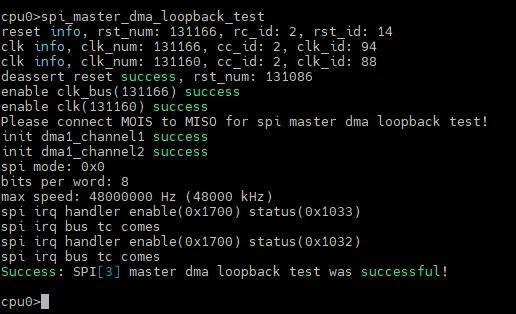

01、SPI数据收发

① 功能介绍

本案例为SPI外回环测试,即将SPI的MOSI和MISO两个引脚短接进行数据收发。

② 效果展现

传输效果:

AD采样芯片采用两线制串行总线接口进行数据传输,其标称典型通信速率可达20MHz级别。该两线制串行总线在电气特性和时序规范上与标准SPI接口高度契合,支持主从模式下的全双工同步通信板载SPI控制器支持最高通信速率达50MHz,SPI硬件控制器能够精确生成满足AD芯片建立时间和保持时间要求的时钟信号,确保数据传输的可靠性。

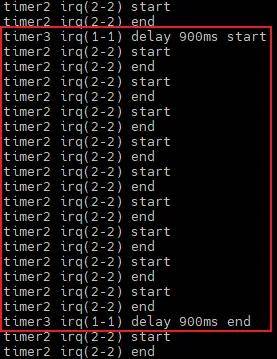

02、中断嵌套

本案例采用两个定时器进行测试。① 功能介绍

② 效果展现

测试方法:配置两个不同优先级的定时器,低优先级定时器(timer3)定时1s,回调中延迟900ms,以此达到延迟退出中断的时间。高优先级定时器(timer2)定时100ms,中断回调中不加延时。注意:在RISC-V核中,中断优先级为数字越大,优先级越高。

现象如下:在低优先级中断中,被高优先级的中断打断,并且执行完高优先级中断后程序回到低优先级中断中继续执行。

03、核间通信RPMgs

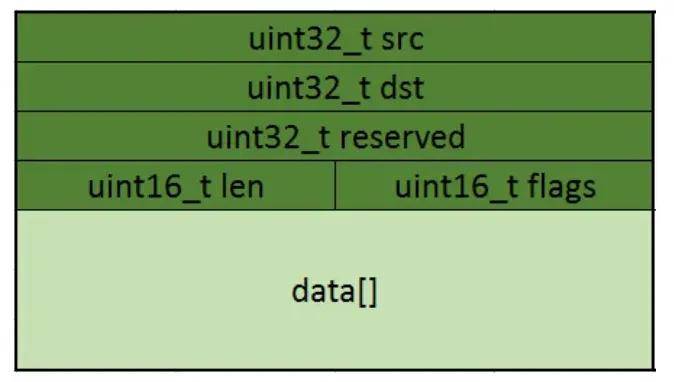

① 标准框架RPMsg是一种基于Virtio的消息总线,构建于Virtio框架之上,用于实现处理器间的消息传递。每个RPMsg通道包含本地源地址和远程目标地址,消息可在两者之间传输。

Virtio提供了共享内存管理与虚拟设备支持,其核心是成对的vring(环形缓冲区),分别用于发送和接收消息。这两个vring共同构成一个环形队列,vring缓冲区即为处理器间的共享内存区域。当共享内存中有新消息到达时,mailbox框架会通知相应处理器进行接收处理。

② 通信流程

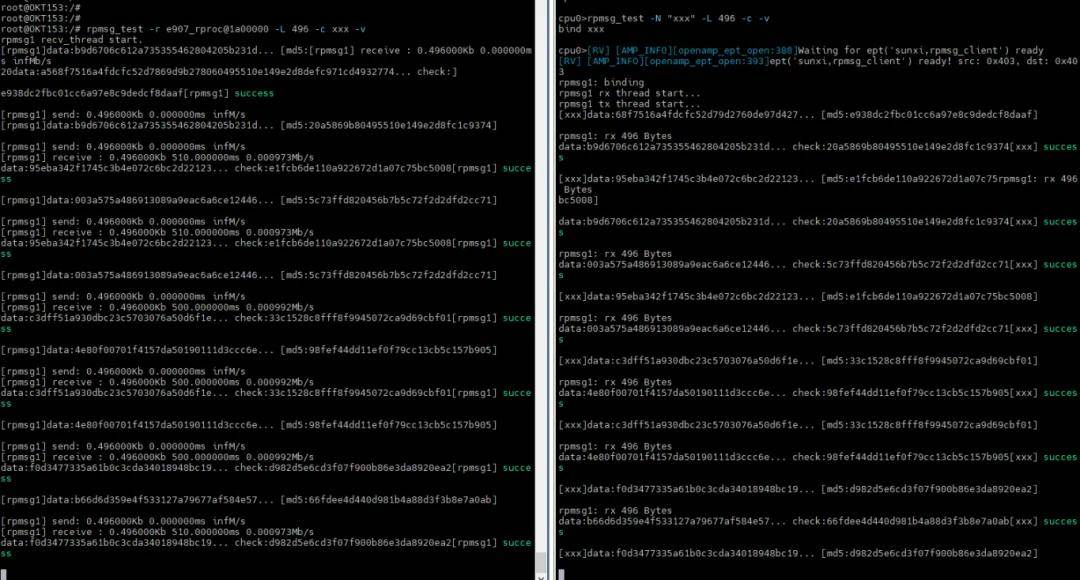

在RPMsg中,只有在主处理器发送第一条消息以后,双核之间才可以进行核间通信,才可以互发数据。因此,当创建debugfs节点后,主处理器在 rpmsg_test_probe() 函数中调用 rpmsg_send() 函数主动向远端处理器发送第一条信息:

在DSP端调用rpmsg_test_init() 接口,并创建rpmsg端点;

在主处理器的debugfs节点的write函数中先从用户层得到要传输的数据,并调用rpmsg_send()函数发送至DSP;

DSP在接收到数据之后,调用callback函数,将接收到数据显示出来;

DS中调用rpmsg_test_send()接口(内部真实调用rpmsg_send() 函数),发送数据至主处理器;

在主处理器接收到数据之后,callback回调会调用 rpmsg_test_cb()函数,将接收到的数据显示出来,完成 CPUX→DSP、DSP→CPUX通信的完整回路。

RPMsg每次发送的最大数据长度为512Bytes,由于RPMsg还带有16Bytes的数据头,因此一次性传输的最大数据量为496Bytes。

③ 通信流程

普通传输:乒乓示例

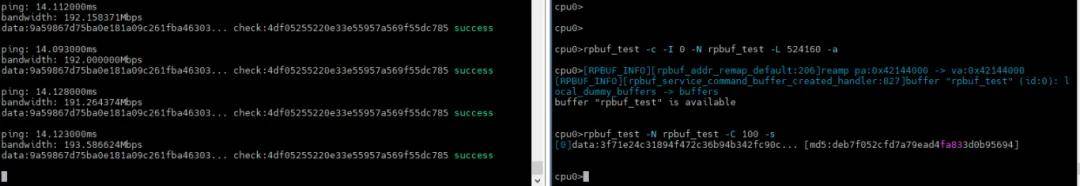

大数据传输:

在实际应用中,原始RPMsg框架在通信传输方面存在一定的局限性,主要表现为单次数据负载上限较低,默认仅为496字节。以传输1MB数据为例,需拆分为约2114次发送操作方可完成。每次数据传输需触发两次中断,累计中断次数高达4228次,频繁的中断处理引入了显著的性能开销。同时,实测单次传输496字节耗时约1.05毫秒,综合上述因素,完成1MB数据的传输总耗时约为2.2秒,该传输效率在当前应用场景下难以满足用户对实时性与吞吐量的要求。全志科技在RPMsg基础上增加了RPBuf大数据传输的框架,如下图所示。

以上就是小编为大家带来的飞凌嵌入式FET153-S核心板RISC-V的使用方法。它的异构多核架构展现出了卓越的通信性能,能够为诸多应用提供高效可靠的核心支撑,特别适用于对实时性和稳定性要求极高的智能应用场景。

Copyright © 2024 深圳全志在线有限公司 粤ICP备2021084185号 粤公网安备44030502007680号