@xiaowenge 升级升级升级升级升级升级升级升级升级升级升级升级

yozad 发布的最佳帖子

yozad 发布的最新帖子

-

T507怎么修改boot0里面的DRAM配置?发布在 T Series

因为买的飞x家的开发板,但是他们家的uboot是不开源的,所以想着从全志的公版SDK中的u-boot-2018试着将uboot驱动起来替换掉他家的uboot。

核心板用的是江波龙的EMMC(8G)和力积的A3T4GF40BBF(四片,共2GB)。

烧飞x的固件,boot0日志如下:

[87]HELLO! BOOT0 is starting!

[90]BOOT0 commit : 75fd24e

[93]set pll start

[95]periph0 has been enabled

[98]set pll end

[101]PMU: AXP858

[106]dram return write ok

[108]board init ok

[110]debug:rtc h-m-s value:0x32325

[114]DRAM BOOT DRIVE INFO: V0.648

[117]the chip id is 0x7c00

[120]chip id check OK

[123]DRAM_VCC set to 1500 mv

[126]DRAM CLK =672 MHZ

[128]DRAM Type =3 (3:DDR3,4:DDR4,7:LPDDR3,8:LPDDR4)

[137]Actual DRAM SIZE =2048 M

[140]DRAM SIZE =2048 MBytes, para1 = 30fa, para2 = 8001000, dram_tpr13 = 6041

[153]DRAM simple test OK.

[155]rtc standby flag is 0x0, super standby flag is 0x0

[161]dram size =2048

[164]Use rtc to store dram tuning para

[168]card no is 2

[169]sdcard 2 line count 8

[172][mmc]: mmc driver ver 2020-07-21-202106151039

[183][mmc]: Wrong media type 0x0, but host is sdc2, try mmc first

[189][mmc]: Try MMC card 2

[213][mmc]: RMCA OK!

[215][mmc]: bias 4

[219][mmc]: MMC 5.1

[221][mmc]: HSSDR52/SDR25 8 bit

[224][mmc]: 50000000 Hz

[227][mmc]: 7456 MB

[229][mmc]: SD/MMC 2 init OK!!!

[263]Loading boot-pkg Succeed(index=0).

[266]Entry_name = u-boot

[276]Entry_name = monitor

[280]Entry_name = dtb

[283]tunning data addr:0x4a0003e8

[287]Jump to second Boot.

NOTICE: BL3-1: v1.0(debug):be96482

NOTICE: BL3-1: Built : 18:32:32, 2021-04-21

NOTICE: BL3-1 commit: 8

NOTICE: cpuidle init version V2.0

ERROR: Error initializing runtime service tspd_fast

NOTICE: BL3-1: Preparing for EL3 exit to normal world

NOTICE: BL3-1: Next image address = 0x4a000000

▒OTICE: BL3-1: Next image spsr = 0x1d3U-Boot 2018.05 (Jul 25 2024 - 12:28:34 +0800) Allwinner Technology

现在直接烧写evb板子的固件,日志如下:

[118]HELLO! BOOT0 is starting!

[121]BOOT0 commit : c52ec7a

[124]set pll start

[127]periph0 has been enabled

[130]set pll end

[132]PMU: AXP858

[142]vaild para:1 select dram para0

[146]board init ok[148]DRAM BOOT DRIVE INFO: V0.651

[151]the chip id is 0x7c00

[154]chip id check OK

[156]DRAM_VCC set to 1500 mv

[159]DRAM CLK =672 MHZ

[162]DRAM Type =3 (3:DDR3,4:DDR4,7:LPDDR3,8:LPDDR4)

[170]Actual DRAM SIZE =128 M

[173]DRAM SIZE =128 MBytes, para1 = 20f7, para2 = 801000, dram_tpr13 = 6041

[186]DRAM simple test OK.

[189]rtc standby flag is 0x0, super standby flag is 0x0

[194]dram size =128

[197]Use rtc to store dram tuning para

[201]card no is 2

[203]sdcard 2 line count 8

[206][mmc]: mmc driver ver 2020-07-21-202106151039

[216][mmc]: Wrong media type 0x0, but host is sdc2, try mmc first

[222][mmc]: Try MMC card 2

[247][mmc]: RMCA OK!

[249][mmc]: bias 4

[253][mmc]: MMC 5.1

[255][mmc]: HSSDR52/SDR25 8 bit

[258][mmc]: 50000000 Hz

[260][mmc]: 7456 MB

[262][mmc]: SD/MMC 2 init OK!!!

[294]Loading boot-pkg Succeed(index=0).

[298]Entry_name = u-boot

[307]Entry_name = monitor

[311]Entry_name = dtb

[315]tunning data addr:0x4a0003e8

[318]Jump to second Boot.

NOTICE: BL3-1: v1.0(debug):f0130ea

NOTICE: BL3-1: Built : 10:23:13, 2022-04-14

NOTICE: BL3-1 commit: 8

NOTICE: cpuidle init version V2.0

ERROR: Error initializing runtime service tspd_fast

NOTICE: BL3-1: Preparing for EL3 exit to normal world

NOTICE: BL3-1: Next image address = 0x4a000000

▒OTICE: BL3-1: Next image spsr = 0x1d3从日志可以看出,evb的固件DRAM SIZE识别到的有问题,所以刷机之后无法启动。

请教各位大神,这个要怎么修改呢? -

T507 PWM互补输出发布在 T Series

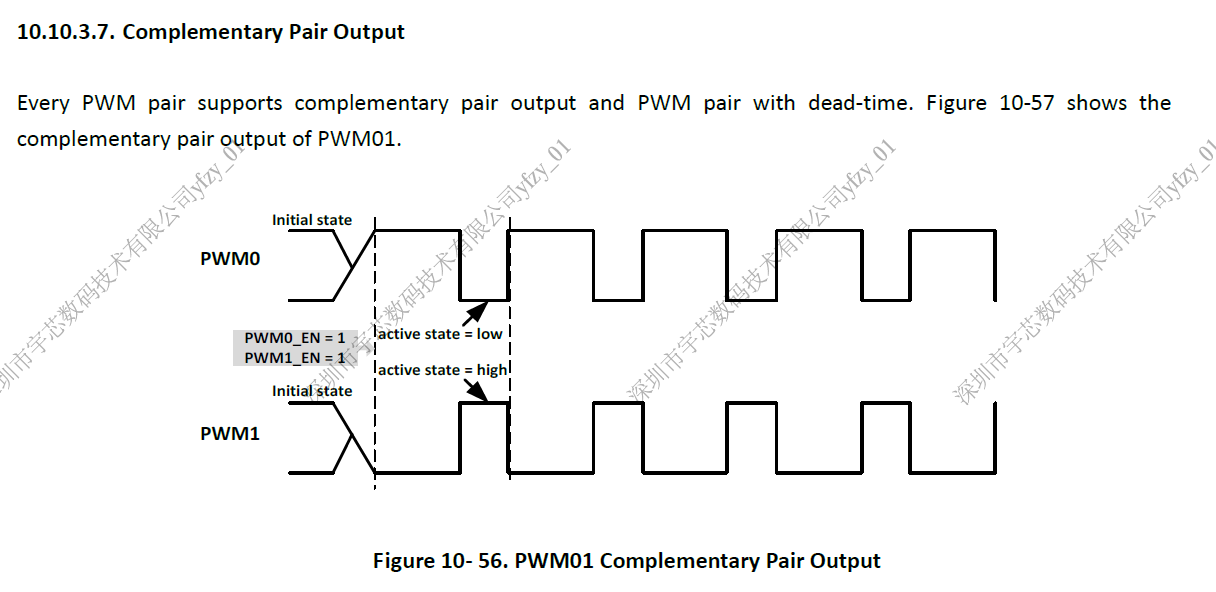

需求:全志T507,把PI12、PI13复用为PWM2、PWM3,想要让PWM2、3互补输出。

T507手册上支持pwm互补输出

看源码需要在设备树里面配置"bind_pwm"和"dead_time",获取死区时间和“互补输出绑定的pwm??”,这里的bind_pwm不是很理解。

static int sunxi_pwm_get_config(struct platform_device *pdev, struct sunxi_pwm_config *config) { struct device_node *np = pdev->dev.of_node; int ret = 0; /* read register config */ pr_info("sunxi_pwm_get_config %s\n", np->name); ret = of_property_read_u32(np, "bind_pwm", &config->bind_pwm); if (ret < 0) { /*if there is no bind pwm,set 255, dual pwm invalid!*/ config->bind_pwm = 255; ret = 0; } ret = of_property_read_u32(np, "dead_time", &config->dead_time); if (ret < 0) { /*if there is bind pwm, but not set dead time,set bind pwm 255,dual pwm invalid!*/ config->bind_pwm = 255; ret = 0; } pr_info("bind_pwm=%d,dead_time=%d\n", config->bind_pwm, config->dead_time); ret = of_property_read_u32(np, "clk_bypass_output", &config->clk_bypass_output); if (ret < 0) { /*if use pwm as the internal clock source!*/ config->clk_bypass_output = 0; ret = 0; } of_node_put(np); return ret; } static int sunxi_pwm_config(struct pwm_chip *chip, struct pwm_device *pwm, int duty_ns, int period_ns) { int bind_num; struct sunxi_pwm_chip *pc = to_sunxi_pwm_chip(chip); //这里可以根据bind_num选择是否互补输出 bind_num = pc->config[pwm->pwm - chip->base].bind_pwm; if (bind_num == 255) sunxi_pwm_config_single(chip, pwm, duty_ns, period_ns); else sunxi_pwm_config_dual(chip, pwm, duty_ns, period_ns, bind_num); return 0; }但是按照源码里面增加“bind_pwm”和“dead_time”

pwm2: pwm2@0300a000 { pinctrl-names = "active", "sleep"; pinctrl-0 = <&pwm2_pin_a>; pinctrl-1 = <&pwm2_pin_b>; bind_pwm = 2; dead_time = 1000; status = "okay"; };编译报错

Error: arch/arm64/boot/dts/sunxi/CII-Common.dtsi:543.15-16 syntax error FATAL ERROR: Unable to parse input tree make[2]: *** [scripts/Makefile.lib:313: arch/arm64/boot/dts/sunxi/board.dtb] Error 1 make[1]: *** [scripts/Makefile.build:648: arch/arm64/boot/dts/sunxi] Error 2 make: *** [arch/arm64/Makefile:153: dtbs] Error 2 make: *** Waiting for unfinished jobs.... CHK kernel/config_data.h ERROR: build kernel Failed INFO: mkkernel failed请问怎么配置才能让pwm互补输出?