大家好,

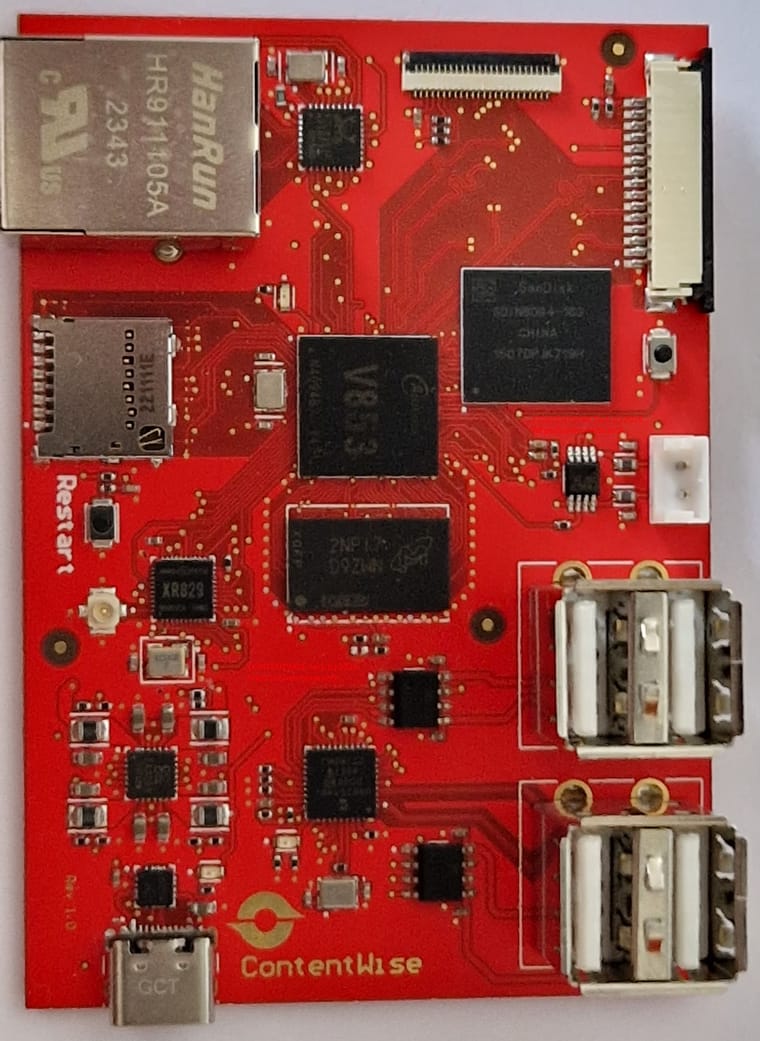

我们已经用 V853 创建了一个小板,并希望 Syterkit 能够工作。 正如您从包含的日志中看到的那样,我们的 DRAM 在 Tina Linux 中工作没有问题。 但是使用 Syterkit 时初始化失败。 我希望你们能提供一些可能存在问题的反馈。

Hi everyone,

we have created a small board with V853 and would like to get Syterkit working. Our DRAM works without problems in Tina Linux as you can see from the included log. However when using Syterkit initialization fails. I would love some feedback from you guys what might be wrong.

Tina boot log

[26]HELLO! BOOT0 is starting!

[29]BOOT0 commit : 2a3ec52022

[32]set pll start

[34]periph0 has been enabled

[37]set pll end

[39][pmu]: bus read error

[42]board init ok

[44]DRAM use external ZQ!!

[46]chip id check OK

[48]POWER SETTING ERROR!

[51]trefi:7.8ms

[53][AUTO DEBUG] single rank and full DQ!

[57]trefi:7.8ms

[60][AUTO DEBUG] rank 0 row = 15

[63][AUTO DEBUG] rank 0 bank = 8

[66][AUTO DEBUG] rank 0 page size = 2 KB

[70]DRAM BOOT DRIVE INFO: V0.16

[73]DRAM CLK = 936 MHz

[75]DRAM Type = 3 (2:DDR2,3:DDR3)

[78]DRAMC ZQ value: 0x7b7bfb

[81]DRAM ODT value: 0x42.

[85]DRAM SIZE =512 M

[87]dram_tpr4:0x0

[94]DRAM simple test OK.

[96]rtc standby flag is 0x0, super standby flag is 0x0

[101]dram size =512

[104]audio:avcc calibration

[106]card no is 0

[108]sdcard 0 line count 4

[111][mmc]: mmc driver ver 2021-12-27 10:07

Syterkit boot output

dram_para_t dram_para = {

.dram_clk = 936,

.dram_type = 3,

.dram_zq = 0x7b7bfb,

.dram_odt_en = 0x1,

.dram_para1 = 0x0010f2,

.dram_para2 = 0x0,

.dram_mr0 = 0x1c70,

.dram_mr1 = 0x42,

.dram_mr2 = 0x18,

.dram_mr3 = 0x0,

.dram_tpr0 = 0x004A2195,

.dram_tpr1 = 0x02423190,

.dram_tpr2 = 0x0008B061,

.dram_tpr3 = 0xB4787896,

.dram_tpr4 = 0x0,

.dram_tpr5 = 0x48484848,

.dram_tpr6 = 0x48,

.dram_tpr7 = 0x1621121e,

.dram_tpr8 = 0x0,

.dram_tpr9 = 0x0,

.dram_tpr10 = 0x0,

.dram_tpr11 = 0x00420000,

.dram_tpr12 = 0x00000048,

.dram_tpr13 = 0x34010100,

};

[ 0.034503][T] GPIO: MUX pin = 233, num in bank = 9, addr = 0x02000154, val = 0xffffff5f, set cfg = 5

[ 0.044185][T] GPIO: MUX pin = 234, num in bank = 10, addr = 0x02000154, val = 0xfffff55f, set cfg = 5

[ 0.054237][I] _____ _ _____ __

[ 0.059290][I] | __|_ _| |_ ___ ___| | |_| |_

[ 0.064342][I] |__ | | | _| -_| _| -| | _|

[ 0.069438][I] |_____|_ |_| |___|_| |__|__|_|_|

[ 0.074508][I] |___|

[ 0.079578][I] ***********************************

[ 0.084648][I] SyterKit v0.2.3 Commit: 31e0ef3

[ 0.089406][I] github.com/YuzukiHD/SyterKit

[ 0.094511][I] ***********************************

[ 0.099572][I] Built by: arm-none-eabi-gcc

[ 0.104018][I]

[ 0.105943][D] periph0 has been enabled

[ 0.109889][D] sunxi clock init end

[ 0.113542][D] cpu clk reg (#0x500): 0x03000301

[ 0.118329][D] DRAM BOOT DRIVE INFO: V0.24

[ 0.122634][D] DRAM CLK = 936 MHz

[ 0.126057][D] DRAM Type = 3 (2:DDR2,3:DDR3)

[ 0.130529][D] DRAMC ZQ value: 0x7b7bfb

[ 0.134533][D] DRAM only have internal ZQ

[ 0.139585][D] DX0 state: 3

[ 0.142426][D] DX1 state: 0

[ 0.145338][E] ERROR: auto scan dram rank & width failed

[ 0.150901][E] auto_scan_dram_config() FAILED

[ 0.155752][T] MMU: CR = 0x00c51879

[ 0.034481][T] GPIO: MUX pin = 233, num in bank = 9, addr = 0x02000154, val = 0xffffff5f, set cfg = 5

[ 0.044128][T] GPIO: MUX pin = 234, num in bank = 10, addr = 0x02000154, val = 0xfffff55f, set cfg = 5

Syterkit different params

syterKit .dram_tpr13 = 0x34000100

[ 0.054110][I] _____ _ _____ _ _

[ 0.059163][I] | __|_ _| |_ ___ ___| | |_| |_

[ 0.064198][I] |__ | | | _| -_| _| -| | _|

[ 0.069251][I] |_____|_ |_| |___|_| |__|__|_|_|

[ 0.074304][I] |___|

[ 0.079348][I] ***********************************

[ 0.084418][I] SyterKit v0.2.3 Commit: 31e0ef3

[ 0.089176][I] github.com/YuzukiHD/SyterKit

[ 0.094229][I] ***********************************

[ 0.099290][I] Built by: arm-none-eabi-gcc

[ 0.103675][I]

[ 0.105574][D] periph0 has been enabled

[ 0.109537][D] sunxi clock init end

[ 0.113165][D] cpu clk reg (#0x500): 0x03000301

[ 0.117908][D] DRAM BOOT DRIVE INFO: V0.24

[ 0.122204][D] DRAM CLK = 936 MHz

[ 0.125671][D] DRAM Type = 3 (2:DDR2,3:DDR3)

[ 0.130169][D] DRAMC ZQ value: 0x7b7bfb

[ 0.134230][D] ZQ value = 0x2f

[ 0.138287][E] ZQ calibration error, check external 240 ohm resistor

[ 0.144889][E] ERROR: auto scan dram rank & width failed

[ 0.150461][E] auto_scan_dram_config() FAILED

[ 0.155329][T] MMU: CR = 0x00c51879