@chengwei_peng 好像改了也没用。

shz18877605430 发布的帖子

-

T113-s3获取ov5640下枚举格式失败发布在 MR Series

各位大佬救救急!!!

T113-s3获取ov5640下枚举格式失败,再if(0 != ioctl(fd,VIDIOC_ENUM_FMT,&fmtdesc))处直接break掉了。

说明一下:ov5640正常使用没有问题,能拍照,已测试过的。

#include <sys/types.h> #include <sys/stat.h> #include <fcntl.h> #include <sys/ioctl.h> #include <unistd.h> #include <stdio.h> #include <string.h> #include <linux/types.h> #include <linux/videodev2.h> /* ./app_ov5640 </dev/video0>*/ int main(int argc,char **argv) { int fd; struct v4l2_fmtdesc fmtdesc; struct v4l2_frmsizeenum fsenum; int fmt_index = 0; int frame_index = 0; if(argc != 2){ printf("Usage %s </dev/videoX>,print format detail for video device\n",argv[0]); return -1; } /* open */ fd = open(argv[1],O_RDWR); if(fd < 0){ printf("can not open %s\n",argv[1]); return -1; } while(1) { /* 枚举格式 */ fmtdesc.index = fmt_index; //比如从0开始 fmtdesc.type = V4L2_BUF_TYPE_VIDEO_CAPTURE; //指定type为"捕获" if(0 != ioctl(fd,VIDIOC_ENUM_FMT,&fmtdesc)) break; frame_index = 0; while(1) { /* 枚举这种个格式所支持的帧大小*/ memset(&fsenum,0,sizeof(struct v4l2_frmsizeenum)); fsenum.pixel_format = fmtdesc.pixelformat; fsenum.index = frame_index; if(ioctl(fd,VIDIOC_ENUM_FRAMESIZES,&fsenum) == 0){ printf("format %s,%d, framesize %d: %d x %d\n",fmtdesc.description,fmtdesc.pixelformat,frame_index,fsenum.discrete.width,fsenum.discrete.height); }else{ break; } frame_index++; } fmt_index++; } return 0; } -

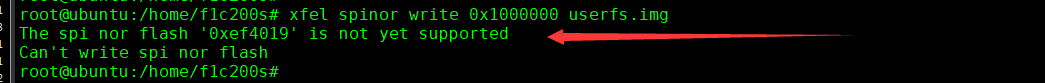

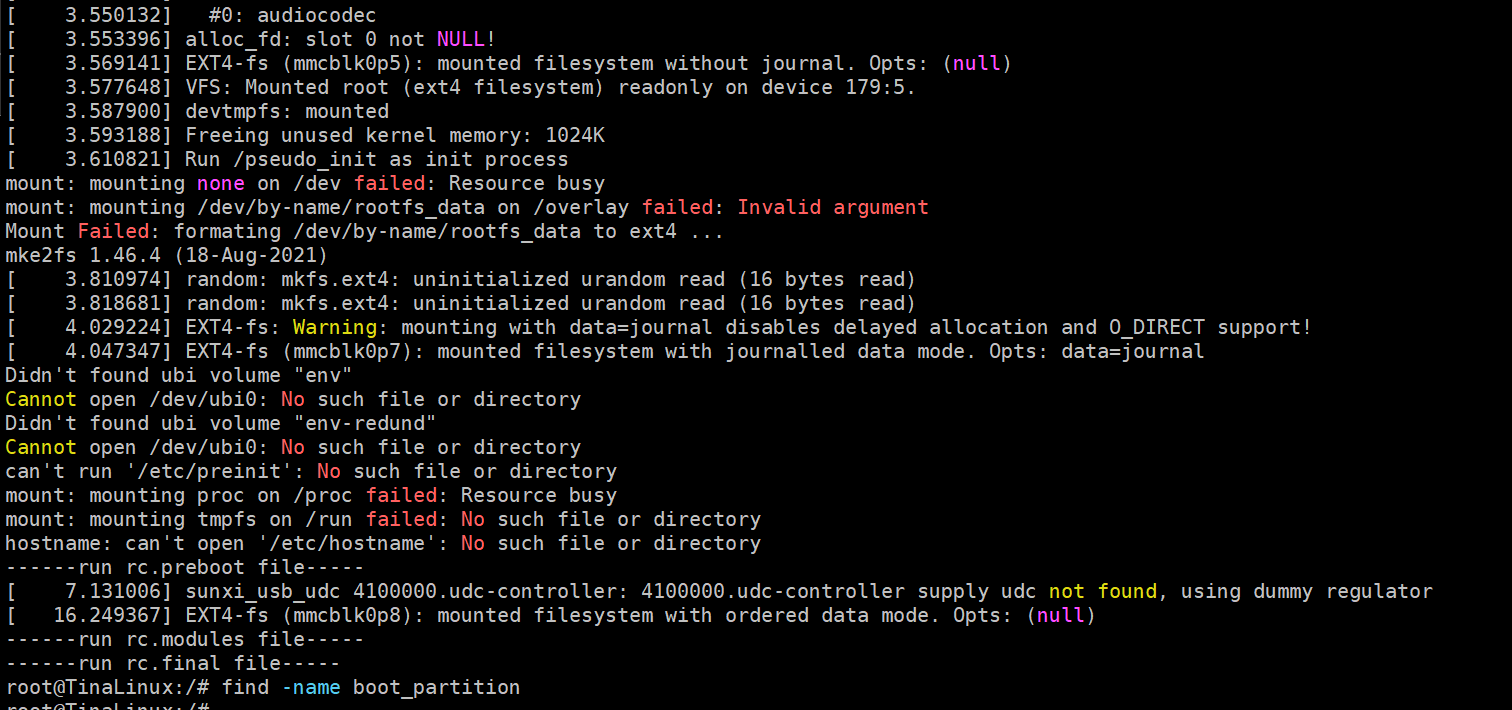

T113 切换存储,nand flash切换到SD卡启动,挂载文件系统报错发布在 MR Series

nand flash切换到SD卡启动,挂载分区的时候报错,文件系统均改为ext4le ,内核已开启ext4文件系统,以及make menuconfig下的e2fprogs,但是还是不行,配置如下:

env

#kernel command arguments earlyprintk=sunxi-uart,0x02500C00 initcall_debug=0 console=ttyS3,115200 nand_root=/dev/ubiblock0_5 mmc_root=/dev/mmcblk0p5 mtd_name=sys rootfstype=squashfs root_partition=rootfs boot_partition=boot init=/sbin/init loglevel=8 cma=8M mac= wifi_mac= bt_mac= specialstr= keybox_list=widevine,ec_key,ec_cert1,ec_cert2,ec_cert3,rsa_key,rsa_cert1,rsa_cert2,rsa_cert3 dsp0_partition=dsp0 rootdelay=2 #set kernel cmdline if boot.img or recovery.img has no cmdline we will use this setargs_nand=setenv bootargs ubi.mtd=${mtd_name} ubi.block=0,${root_partition} earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${nand_root} rootfstype=${rootfstype} init=${init} partitions=${partitions} cma=${cma} snum=${snum} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} specialstr=${specialstr} gpt=1 setargs_nand_ubi=setenv bootargs ubi.mtd=${mtd_name} ubi.block=0,${root_partition} earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${nand_root} rootfstype=${rootfstype} init=${init} partitions=${partitions} cma=${cma} snum=${snum} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} specialstr=${specialstr} gpt=1 setargs_mmc=setenv bootargs earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${mmc_root} init=${init} partitions=${partitions} cma=${cma} snum=${snum} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} specialstr=${specialstr} gpt=1 #nand command syntax: sunxi_flash read address partition_name read_bytes #0x4007f800 = 0x40080000(kernel entry) - 0x800(boot.img header 2k) #boot_dsp0=sunxi_flash read 45000000 ${dsp0_partition};bootr 45000000 0 0 #boot_normal=sunxi_flash read 45000000 ${boot_partition};bootm 45000000 boot_dsp0=sunxi_flash read 40000000 ${dsp0_partition};bootr 40000000 0 0 boot_normal=sunxi_flash read 41000000 ${boot_partition};bootm 41000000 boot_recovery=sunxi_flash read 43000000 recovery;bootm 43000000 boot_fastboot=fastboot #uboot system env config bootdelay=1 #default bootcmd, will change at runtime according to key press #default nand boot bootcmd=run setargs_mmc boot_normalsys_config

;---------------------------------------------------------------------------------- ;storage_type = boot medium, 0-nand, 1-sd, 2-emmc, 3-nor, 4-emmc3, 5-spinand -1(defualt)auto scan ;---------------------------------------------------------------------------------- [target] boot_clock = 1008 storage_type = 1 nand_use_ubi = 0board.dts

&spi0 { clock-frequency = <100000000>; pinctrl-0 = <&spi0_pins_a &spi0_pins_b>; pinctrl-1 = <&spi0_pins_c>; pinctrl-names = "default", "sleep"; /*spi-supply = <®_dcdc1>;*/ spi_slave_mode = <0>; spi0_cs_number = <1>; spi0_cs_bitmap = <1>; status = "disabled"; spi-nand@0 { compatible = "spi-nand"; spi-max-frequency=<100000000>; reg = <0x0>; spi-rx-bus-width=<0x04>; spi-tx-bus-width=<0x04>; status="disabled"; }; spi-nor@0 { compatible = "jedec,spi-nor"; spi-max-frequency=<30000000>; reg = <0x0>; spi-rx-bus-width=<0x01>; spi-tx-bus-width=<0x01>; status="disabled"; }; }; &sdc0 { bus-width = <4>; cd-gpios = <&pio PF 6 (GPIO_ACTIVE_LOW | GPIO_PULL_UP)>; /*non-removable;*/ /*broken-cd;*/ /*cd-inverted;*/ /*data3-detect;*/ /*card-pwr-gpios = <&pio PH 14 1 1 2 0xffffffff>;*/ cd-used-24M; cap-sd-highspeed; /*sd-uhs-sdr50;*/ /*sd-uhs-ddr50;*/ /*sd-uhs-sdr104;*/ no-sdio; //no-mmc; sunxi-power-save-mode; /*sunxi-dis-signal-vol-sw;*/ max-frequency = <150000000>; ctl-spec-caps = <0x8>; /*vmmc-supply = <®_dcdc1>;*/ /*vqmmc33sw-supply = <®_dcdc1>;*/ /*vdmmc33sw-supply = <®_dcdc1>;*/ /*vqmmc18sw-supply = <®_eldo1>;*/ /*vdmmc18sw-supply = <®_eldo1>;*/ status = "okay"; };syslog如下:

-

T113主线,内核读分区失败。发布在 Linux

参照了“T113的主线linux(最新gcc+awboot+最新kernel+最新buildroot)”,发现内核起来之后,读分区的时候失败了,日志如下所示。各位大佬指点指点一下,谢谢。

[ 1.115794] [drm] Initialized sun4i-drm 1.0.0 20150629 for display-engine on minor 0 [ 1.125610] spi-nand spi0.0: GigaDevice SPI NAND was found. [ 1.131241] spi-nand spi0.0: 128 MiB, block size: 128 KiB, page size: 2048, OOB size: 128 [ 1.140134] 4 fixed-partitions partitions found on MTD device spi0.0 [ 1.146506] Creating 4 MTD partitions on "spi0.0": [ 1.151335] 0x000000000000-0x000000040000 : "awboot" [ 1.156617] ------------[ cut here ]------------ [ 1.161243] kernel BUG at drivers/dma/dmaengine.h:54! [ 1.166290] Internal error: Oops - BUG: 0 [#1] SMP ARM [ 1.171424] Modules linked in: [ 1.174482] CPU: 0 PID: 0 Comm: swapper/0 Not tainted 6.1.0-rc3-443875-gb466df90d48f-dirty #3 [ 1.182998] Hardware name: Generic DT based system [ 1.187782] PC is at sun6i_dma_interrupt+0x1a8/0x1ac [ 1.192759] LR is at sun6i_dma_interrupt+0xec/0x1ac [ 1.197639] pc : [<c04a362c>] lr : [<c04a3570>] psr: 60000193 [ 1.203898] sp : c0d01d68 ip : 0626c000 fp : 00000000 [ 1.209116] r10: 00000000 r9 : 00000010 r8 : c11ff440 [ 1.214333] r7 : 00000000 r6 : c122810c r5 : c11ff640 r4 : 00000007 [ 1.220852] r3 : c122810c r2 : c1b32b80 r1 : 00000000 r0 : c1228168 [ 1.227372] Flags: nZCv IRQs off FIQs on Mode SVC_32 ISA ARM Segment none [ 1.234586] Control: 10c5387d Table: 4000406a DAC: 00000051 [ 1.240323] Register r0 information: non-slab/vmalloc memory [ 1.245980] Register r1 information: NULL pointer [ 1.250679] Register r2 information: slab kmalloc-128 start c1b32b80 pointer offset 0 size 128 [ 1.256689] spi_master spi0: spi0.0: timeout transferring 1 bytes@100000000Hz for 110(100)ms [ 1.259295] Register r3 information: non-slab/vmalloc memory [ 1.267737] spi-nand spi0.0: SPI transfer failed: -110 [ 1.273363] Register r4 information: non-paged memory [ 1.278504] spi_master spi0: failed to transfer one message from queue [ 1.283533] Register r5 information: slab kmalloc-512 start c11ff600 pointer offset 64 size 512 [ 1.290560] 0x000000040000-0x000000080000 : "dtb" [ 1.298740] Register r6 information: non-slab/vmalloc memory [ 1.298747] Register r7 information: NULL pointer [ 1.298752] Register r8 information: slab kmalloc-512 start c11ff400 pointer offset 64 size 512 [ 1.298768] Register r9 information: zero-size pointer [ 1.298773] Register r10 information: NULL pointer [ 1.332396] Register r11 information: NULL pointer [ 1.337183] Register r12 information: non-paged memory [ 1.342316] Process swapper/0 (pid: 0, stack limit = 0x(ptrval)) [ 1.348316] Stack: (0xc0d01d68 to 0xc0d02000) [ 1.352672] 1d60: c04a3484 c113b080 c092766c 00000000 0000001e c12ed000 [ 1.360841] 1d80: c0d01dd8 00000018 40000006 c016a854 c1b26500 00000001 c12ed000 c092766c [ 1.369010] 1da0: c12ed06c c0c5d208 c880a00c c016a9ac c12ed000 c092766c c880a000 c016f1e4 [ 1.377178] 1dc0: c0d052fc c0d7a978 c880a000 c016a108 c0d052fc c046c77c c0c5ddfc c0d01e08 [ 1.385347] 1de0: 00000000 c0d01e3c c0c5de40 c0d08100 00000018 c08b8a08 c015d428 20000113 [ 1.393517] 1e00: ffffffff c0100ba8 c0d03c88 c0d03c8c c0d03c8c ffffffff c122814c c1228150 [ 1.401686] 1e20: c1228150 c6ec7328 c0c5de40 00000040 00000018 40000006 0000000c c0d01e58 [ 1.406688] spi_master spi0: spi0.0: timeout transferring 1 bytes@100000000Hz for 110(100)ms [ 1.409854] 1e40: 00000000 c015d428 20000113 ffffffff 00000051 7610cb08 00000000 c883569c [ 1.418289] spi-nand spi0.0: SPI transfer failed: -110 [ 1.426436] 1e60: c1228150 ffffffff 00000000 7610cb08 c122810c c0121a08 c04a3484 c113b080 [ 1.431573] spi_master spi0: failed to transfer one message from queue [ 1.439723] 1e80: c092766c c122814c c11ff53c c0121cb8 00000000 c0d03098 00000100 c0d08100 [ 1.439732] 1ea0: c0d01eb0 c0d03080 00000018 c0101384 c880a00c c0d01ee8 c0d03080 c0c5b3b0 [ 1.462566] 1ec0: 0000000a c0c5de40 c0c5b324 ffff8b43 c0d03d40 04200002 c880a000 c016a108 [ 1.470735] 1ee0: c0d052fc c0d08100 60000013 ffffffff c0d01f4c 00000056 c0d08100 c0c44a68 [ 1.478904] 1f00: 00000000 c01221e0 c0107464 c01222a0 c0107464 c0100ba8 00000005 00000000 [ 1.487073] 1f20: 00000d99 c01160c0 00000000 c0d04f0c c0d08100 c0d04f54 00000056 00000000 [ 1.495241] 1f40: c0c44a68 00000000 c0d03d80 c0d01f68 c0107460 c0107464 60000013 ffffffff [ 1.503410] 1f60: 00000051 c0d04f0c 00000000 c08bfb9c 00000000 c01555b4 000000ec c0d04ec0 [ 1.511579] 1f80: 10c0387d c0e1a678 00000056 c01558e8 c0d0c244 c08b8e34 c0def040 c0c00a98 [ 1.519747] 1fa0: c0def040 c0c010cc ffffffff ffffffff 00000000 c0c006ec c0d08100 00000000 [ 1.527916] 1fc0: 00000000 c0c44a68 7616ca08 00000000 00000000 c0c00420 00000051 10c0387d [ 1.536086] 1fe0: ffffffff 44000000 410fc075 10c5387d 00000000 00000000 00000000 00000000 [ 1.544260] sun6i_dma_interrupt from __handle_irq_event_percpu+0x44/0x118 [ 1.546682] spi_master spi0: spi0.0: timeout transferring 1 bytes@100000000Hz for 110(100)ms [ 1.551149] __handle_irq_event_percpu from handle_irq_event+0x44/0x8c [ 1.559584] spi-nand spi0.0: SPI transfer failed: -110 [ 1.566082] handle_irq_event from handle_fasteoi_irq+0x98/0x18c [ 1.571229] spi_master spi0: failed to transfer one message from queue [ 1.577203] handle_fasteoi_irq from generic_handle_domain_irq+0x28/0x38 [ 1.577220] generic_handle_domain_irq from gic_handle_irq+0x74/0x88 [ 1.584144] 0x000000080000-0x000000800000 : "kernel" [ 1.590420] gic_handle_irq from generic_handle_arch_irq+0x34/0x44 [ 1.590437] generic_handle_arch_irq from __irq_svc+0x88/0xb0 [ 1.613643] Exception stack(0xc0d01e08 to 0xc0d01e50) [ 1.618693] 1e00: c0d03c88 c0d03c8c c0d03c8c ffffffff c122814c c1228150 [ 1.626862] 1e20: c1228150 c6ec7328 c0c5de40 00000040 00000018 40000006 0000000c c0d01e58 [ 1.635028] 1e40: 00000000 c015d428 20000113 ffffffff [ 1.640075] __irq_svc from wake_up_var+0x50/0x94 [ 1.644788] wake_up_var from tasklet_clear_sched+0x4c/0xa8 [ 1.650359] tasklet_clear_sched from tasklet_action_common.constprop.0+0xc0/0x108 [ 1.657931] tasklet_action_common.constprop.0 from __do_softirq+0x104/0x27c [ 1.664981] __do_softirq from __irq_exit_rcu+0xa4/0xc8 [ 1.670210] __irq_exit_rcu from irq_exit+0x8/0x10 [ 1.675006] irq_exit from __irq_svc+0x88/0xb0 [ 1.679454] Exception stack(0xc0d01f18 to 0xc0d01f60) [ 1.684500] 1f00: 00000005 00000000 [ 1.692669] 1f20: 00000d99 c01160c0 00000000 c0d04f0c c0d08100 c0d04f54 00000056 00000000 [ 1.700838] 1f40: c0c44a68 00000000 c0d03d80 c0d01f68 c0107460 c0107464 60000013 ffffffff [ 1.706686] spi_master spi0: spi0.0: timeout transferring 1 bytes@100000000Hz for 110(100)ms [ 1.709002] __irq_svc from arch_cpu_idle+0x38/0x3c [ 1.717442] spi-nand spi0.0: SPI transfer failed: -110 [ 1.722292] arch_cpu_idle from default_idle_call+0x24/0x34 [ 1.727433] spi_master spi0: failed to transfer one message from queue [ 1.732980] default_idle_call from do_idle+0xa4/0x120 [ 1.744622] do_idle from cpu_startup_entry+0x18/0x1c [ 1.749673] cpu_startup_entry from rest_init+0xa8/0xac [ 1.754899] rest_init from arch_post_acpi_subsys_init+0x0/0x8 [ 1.760744] Code: e28800fc 1afffff2 ebf1f9c1 eafffff0 (e7f001f2) [ 1.766832] ---[ end trace 0000000000000000 ]--- [ 1.771443] Kernel panic - not syncing: Fatal exception in interrupt [ 1.777792] CPU1: stopping [ 1.780501] CPU: 1 PID: 0 Comm: swapper/1 Tainted: G D 6.1.0-rc3-443875-gb466df90d48f-dirty #3 [ 1.790490] Hardware name: Generic DT based system [ 1.795277] unwind_backtrace from show_stack+0x10/0x14 [ 1.800508] show_stack from dump_stack_lvl+0x40/0x4c [ 1.805559] dump_stack_lvl from do_handle_IPI+0xec/0x124 [ 1.810959] do_handle_IPI from ipi_handler+0x18/0x20 [ 1.816011] ipi_handler from handle_percpu_devid_irq+0x78/0x134 [ 1.822019] handle_percpu_devid_irq from generic_handle_domain_irq+0x28/0x38 [ 1.829156] generic_handle_domain_irq from gic_handle_irq+0x74/0x88 [ 1.835512] gic_handle_irq from generic_handle_arch_irq+0x34/0x44 [ 1.841692] generic_handle_arch_irq from call_with_stack+0x18/0x20 [ 1.847965] call_with_stack from __irq_svc+0x98/0xb0 [ 1.853021] Exception stack(0xc8849f68 to 0xc8849fb0) [ 1.858069] 9f60: 00000005 00000000 000012d1 c01160c0 00000001 c0d04f0c [ 1.866237] 9f80: c104ee80 c0d04f54 4000406a 410fc075 00000000 00000000 c0d03d80 c8849fb8 [ 1.874403] 9fa0: c0107460 c0107464 60000013 ffffffff [ 1.879447] __irq_svc from arch_cpu_idle+0x38/0x3c [ 1.884329] arch_cpu_idle from default_idle_call+0x24/0x34 [ 1.889908] default_idle_call from do_idle+0xa4/0x120 [ 1.895049] do_idle from cpu_startup_entry+0x18/0x1c [ 1.900100] cpu_startup_entry from secondary_start_kernel+0x118/0x120 [ 1.906626] secondary_start_kernel from 0x401015a0 [ 1.911510] ---[ end Kernel panic - not syncing: Fatal exception in interrupt ]--- -

回复: 编译buildroot,编译出来的程序没法放到T113上运行。发布在 其它全志芯片讨论区

@shz18877605430 各位大佬,用什么交叉工具链能编译出可以在tina T113板子上运行呢?

-

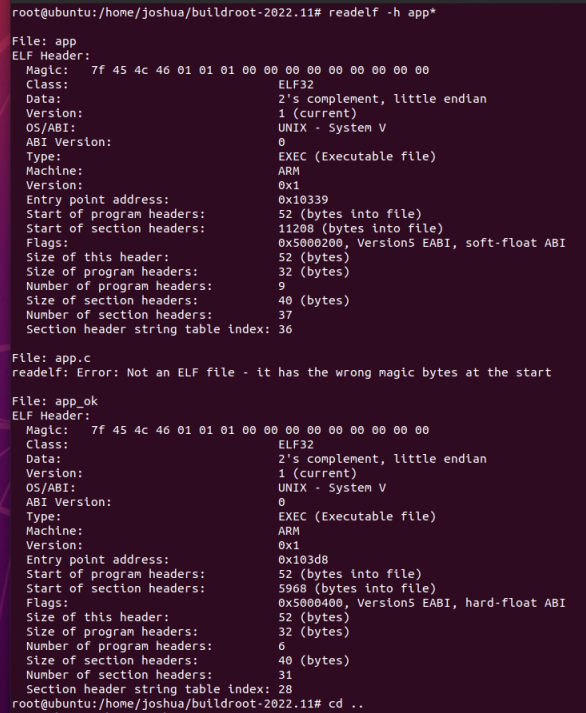

编译buildroot,编译出来的程序没法放到T113上运行。发布在 其它全志芯片讨论区

各位大佬,指点一下。

自己下载了buildroot-2022.05.2,然后用了gcc-linaro-7.2.1-2017.11-x86_64_arm-linux-gnueabi 的交叉编译链,编译出来的vsftpd再开发板上无法运行。

但是我自己写了一个APP程序,用了和buildroot一样的工具链编译,编译出来的程序无法再开发板上运行,如果用sdk下的编译器是可以再板子上运行。其中,图中所示第一个app是不可以运行的。app_ok是可以运行的。

-

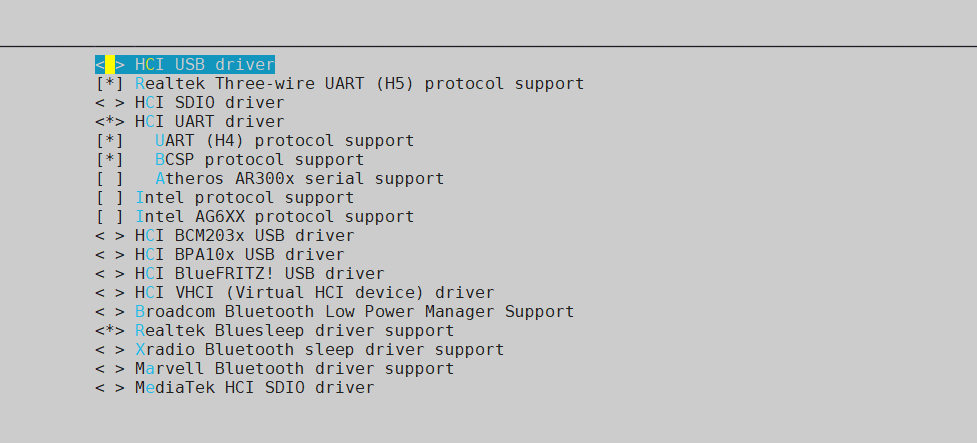

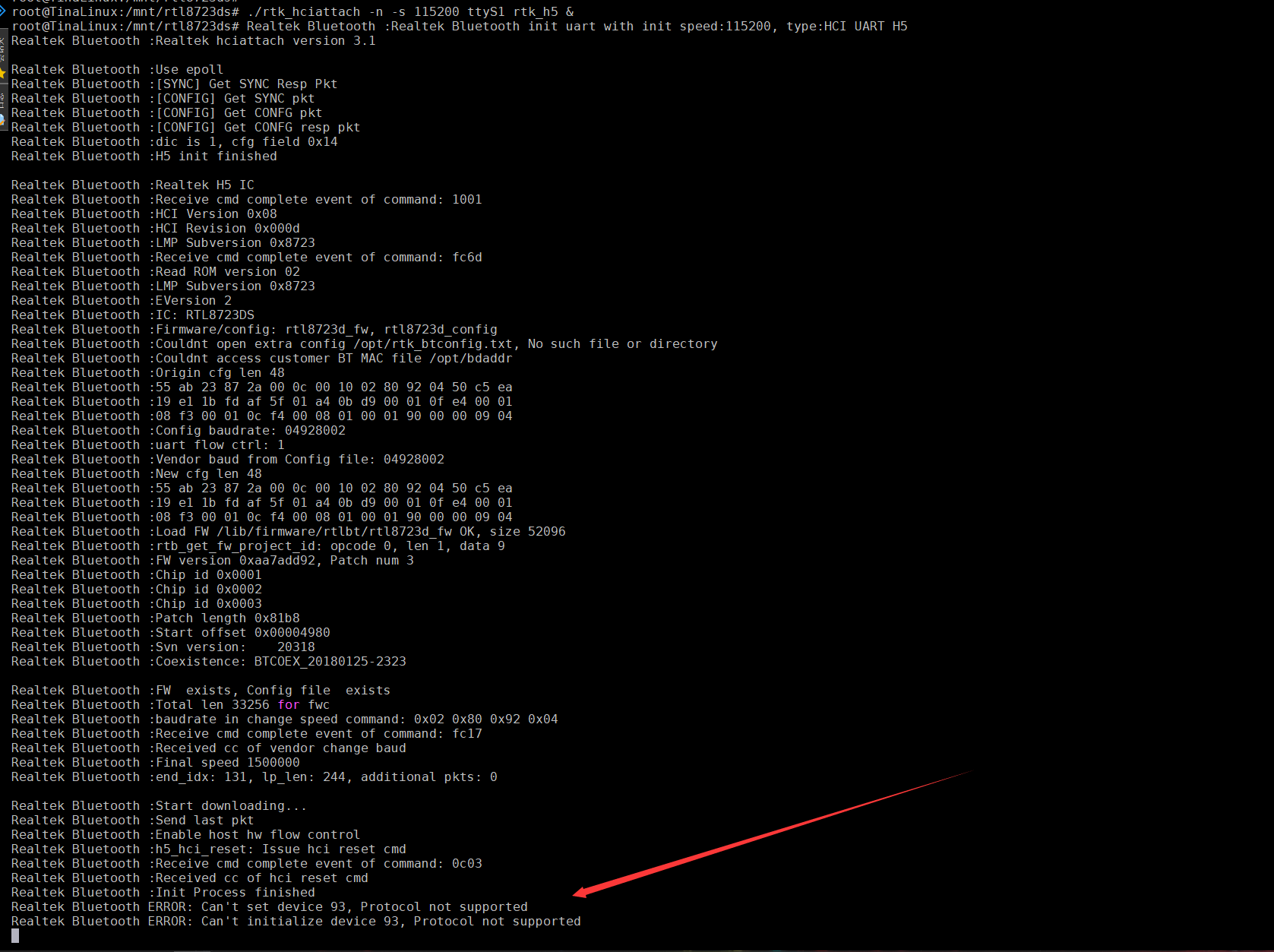

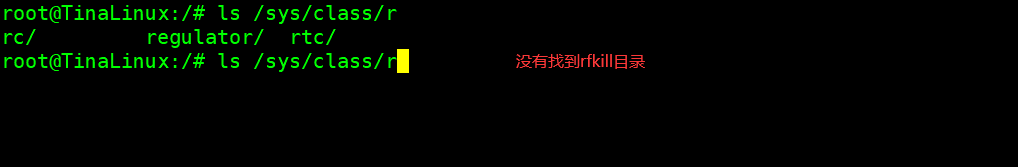

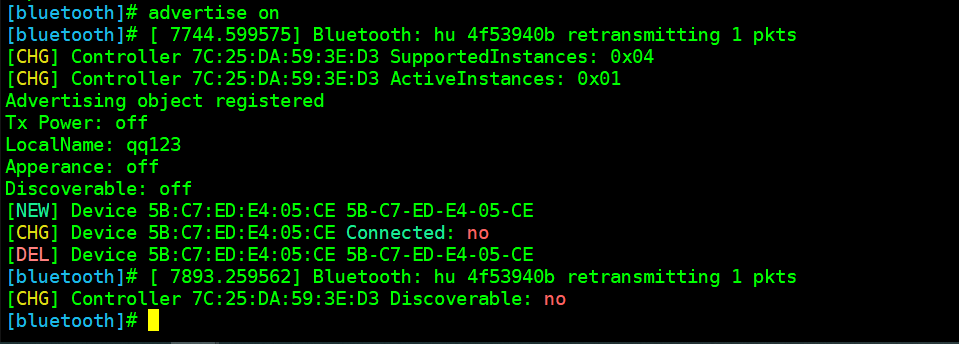

F133启动rtk_hciattach报错发布在 MR Series

大佬们,帮忙看看,运行rtk_hciattach -n -s 115200 ttyS1 rtk_h5 & 出现了ERROR: Can't set device 93, Protocol not supported 。

-

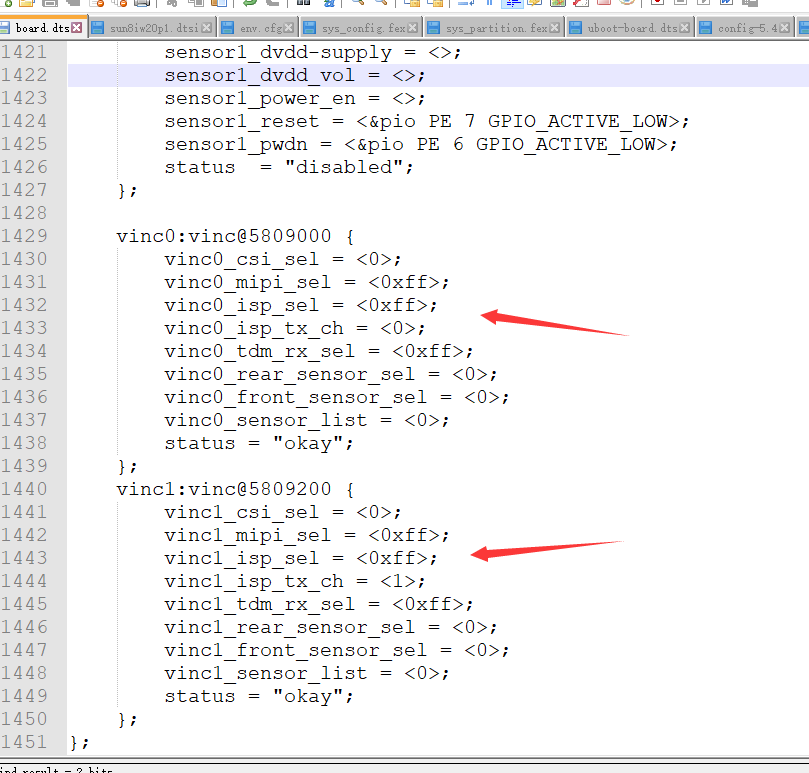

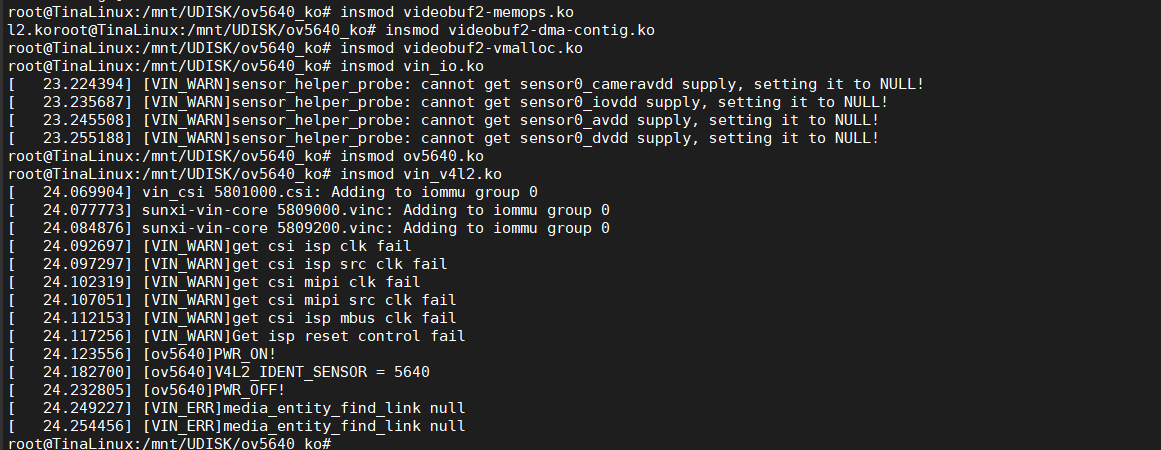

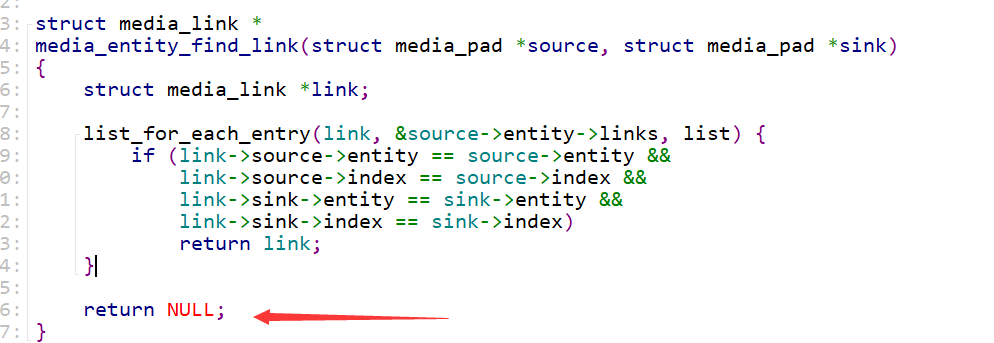

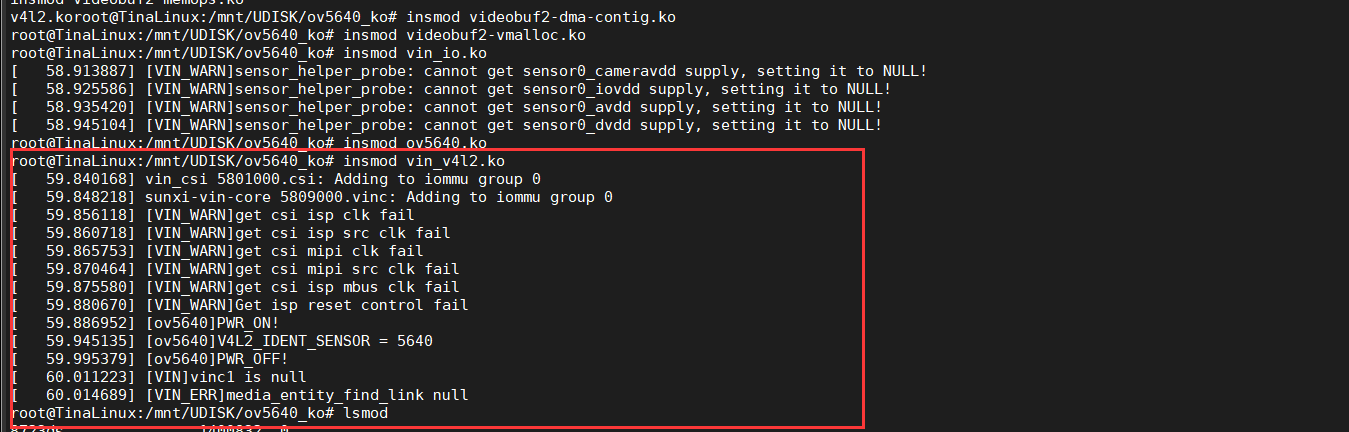

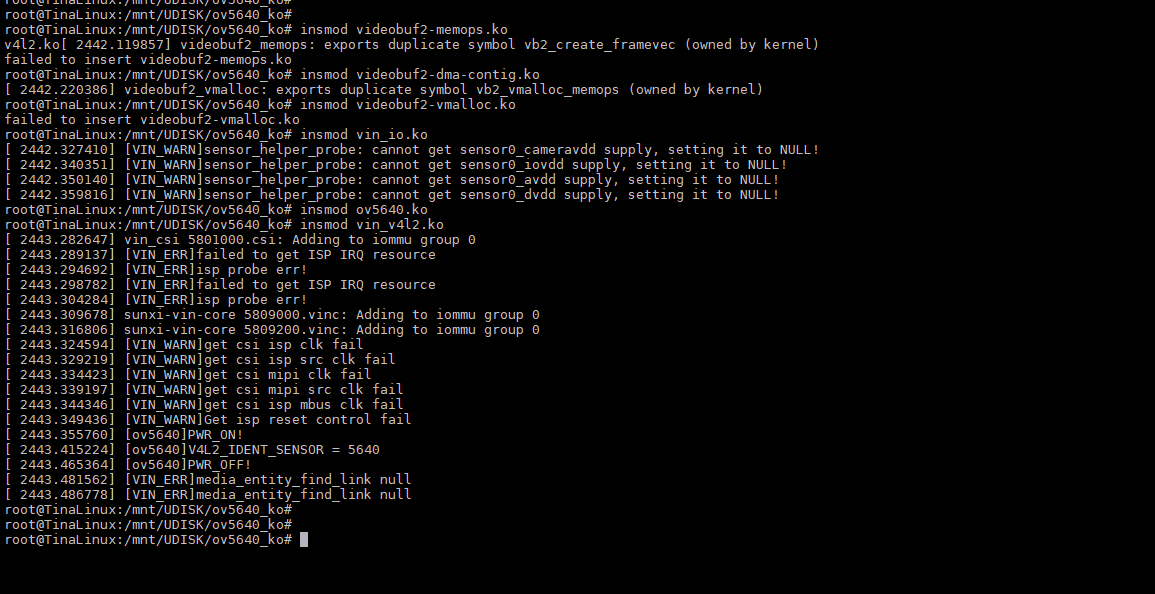

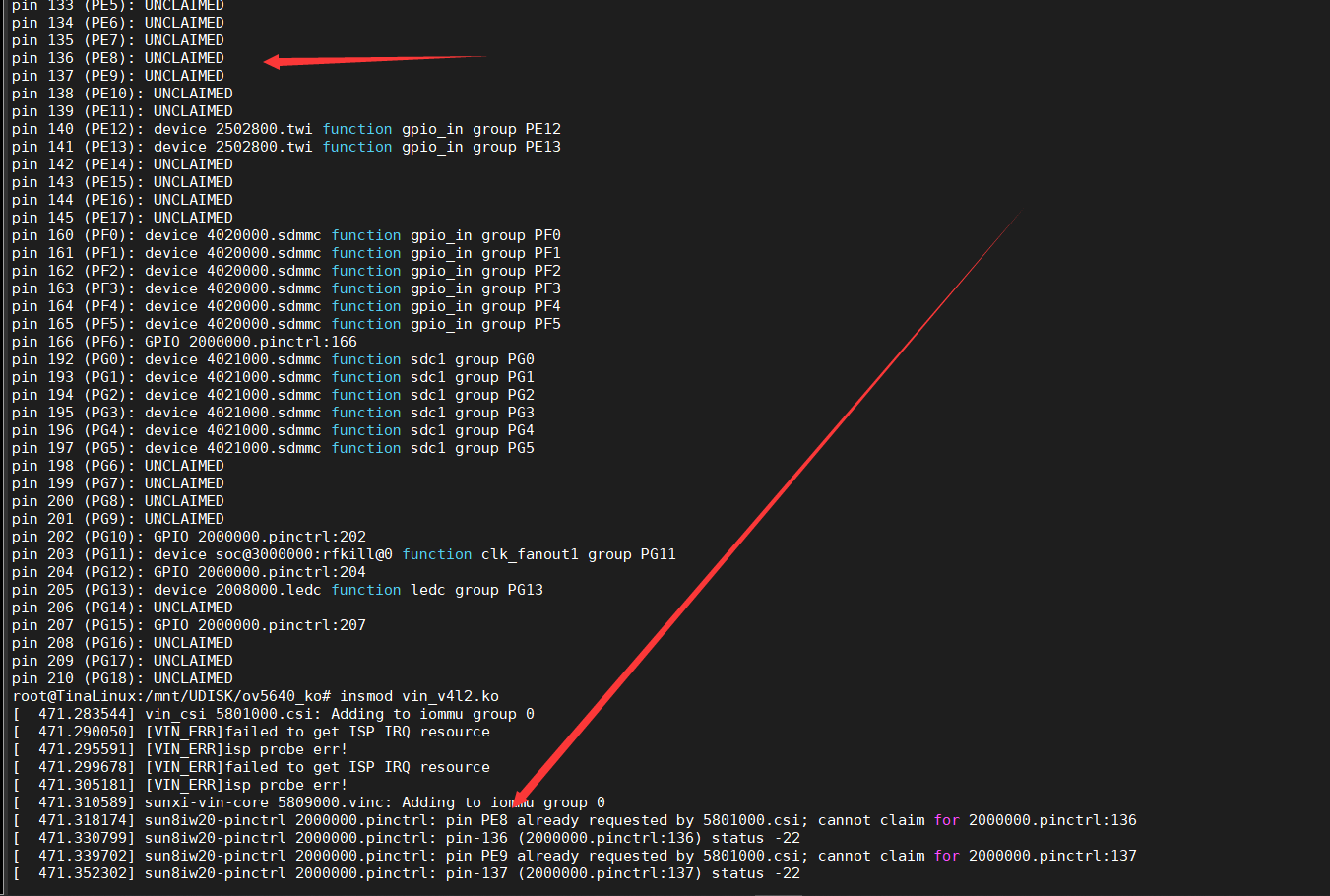

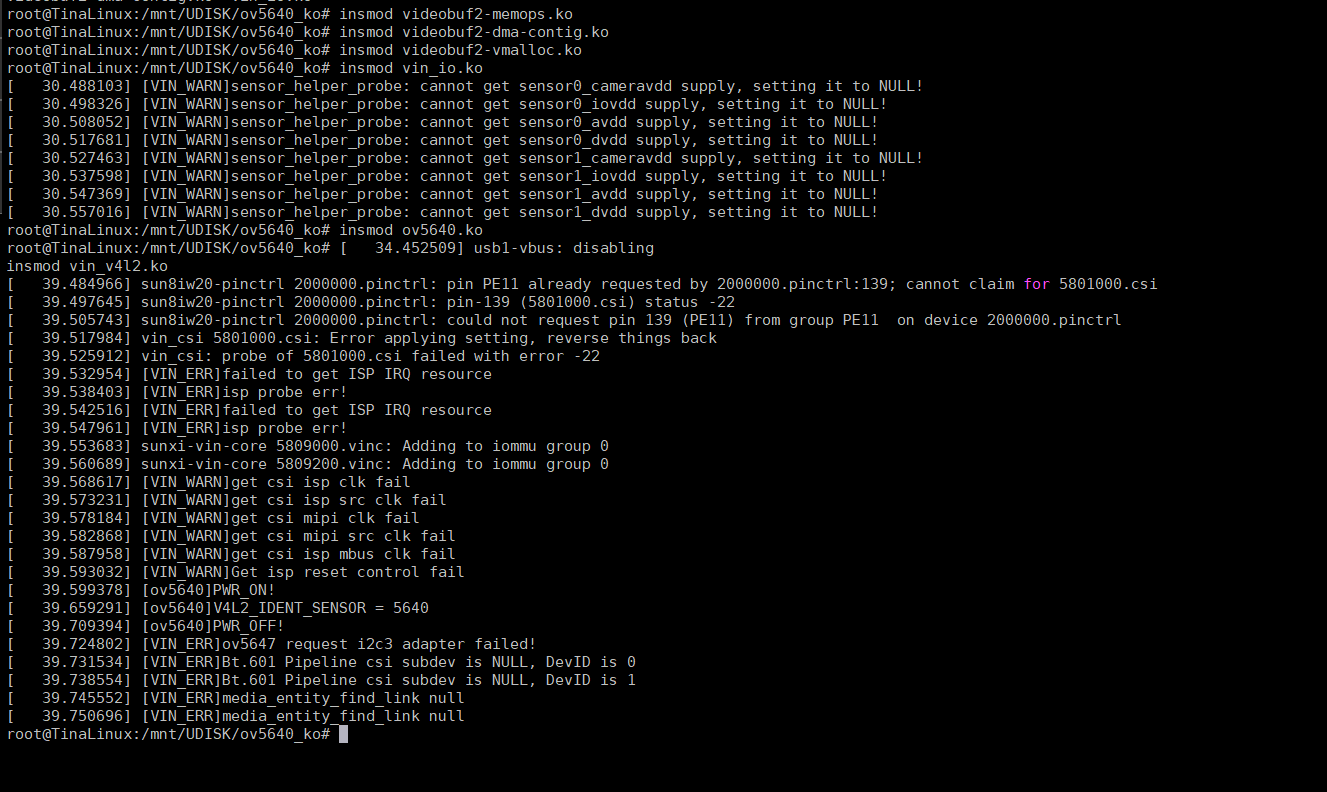

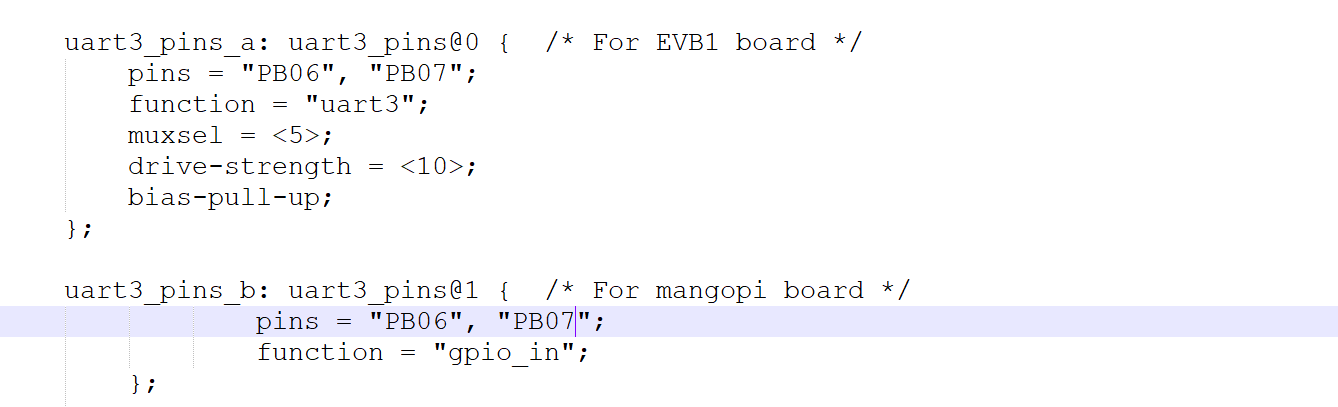

全志T113-s3使用ov5640加载insmod vin_v4l2.ko报错发布在 MR Series

全志T113-s3使用ov5640加载insmod vin_v4l2.ko报错,各位大佬救救急,搞了很久了,一直没有眉目。

配置如下:

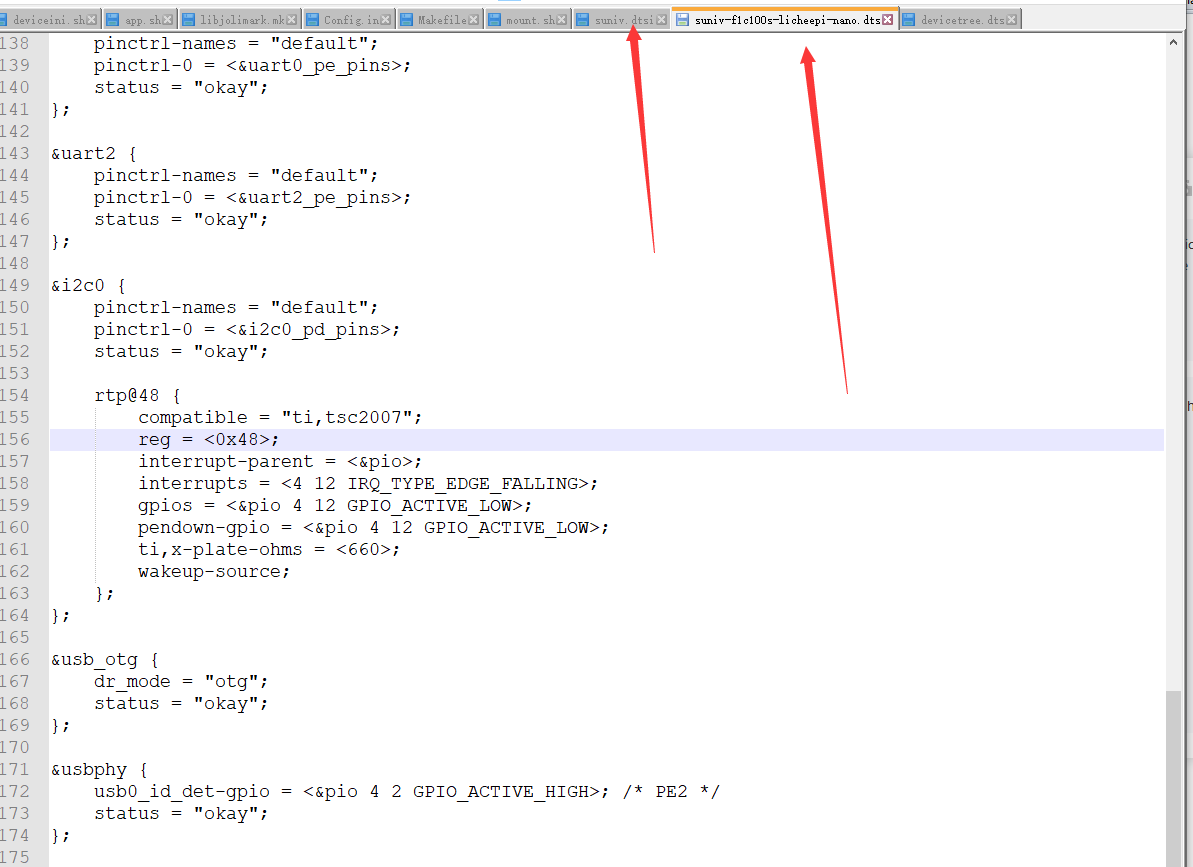

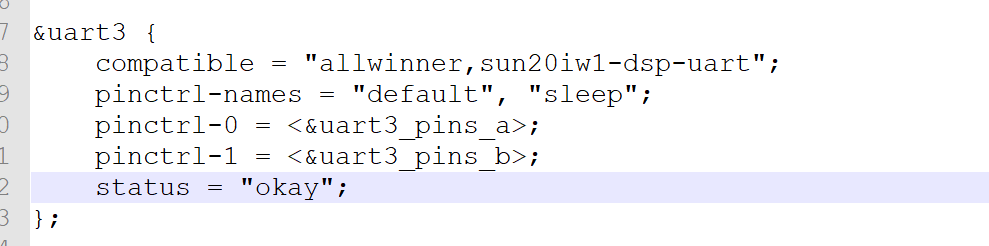

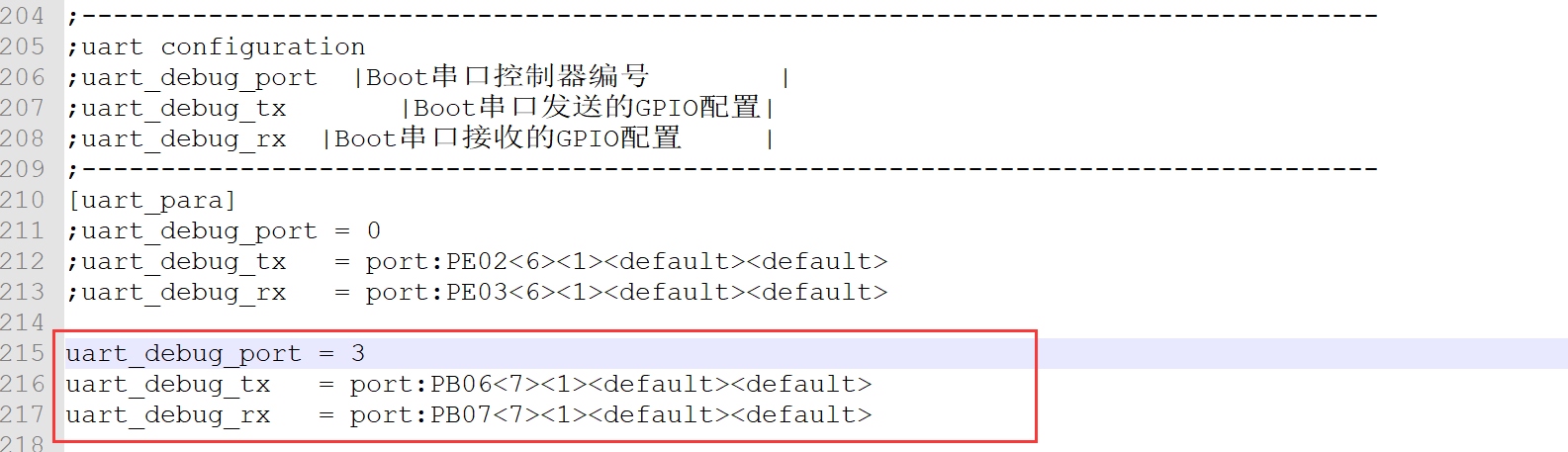

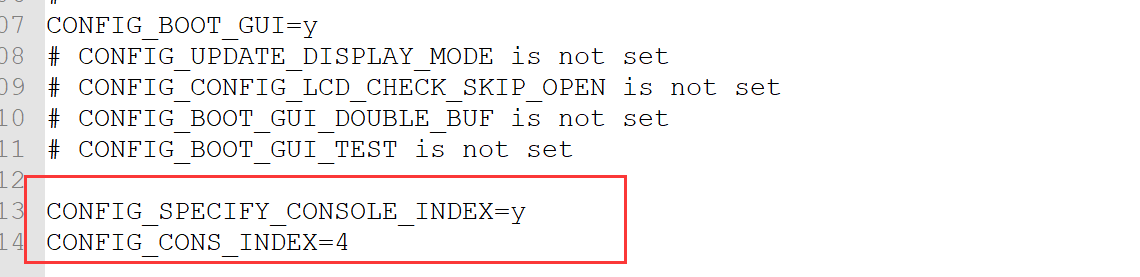

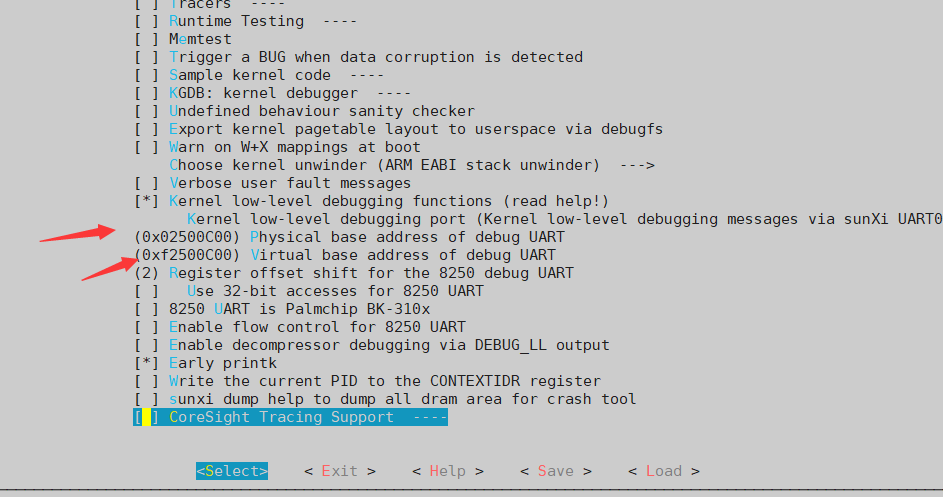

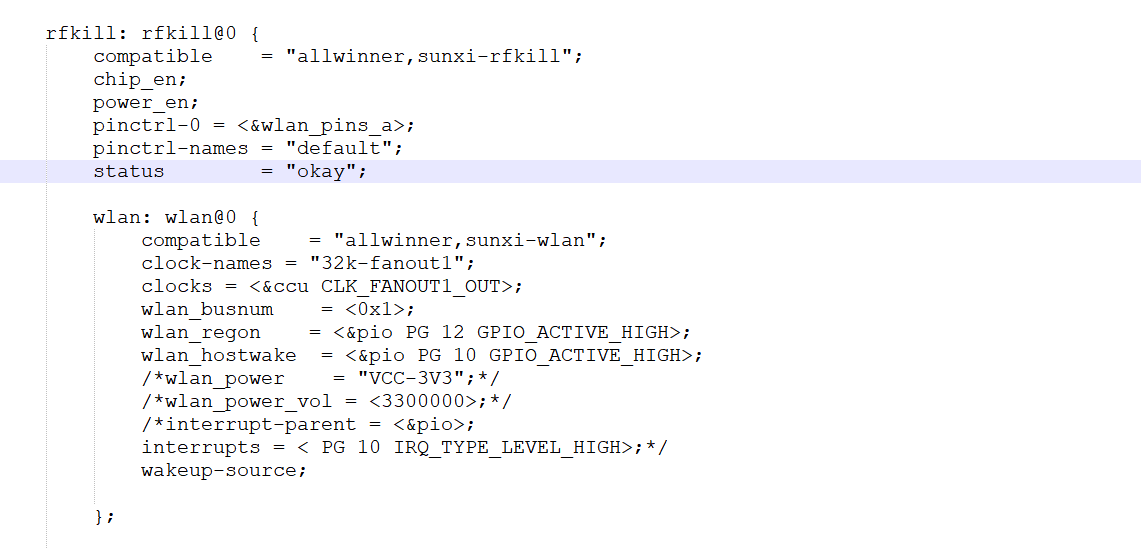

board.dts

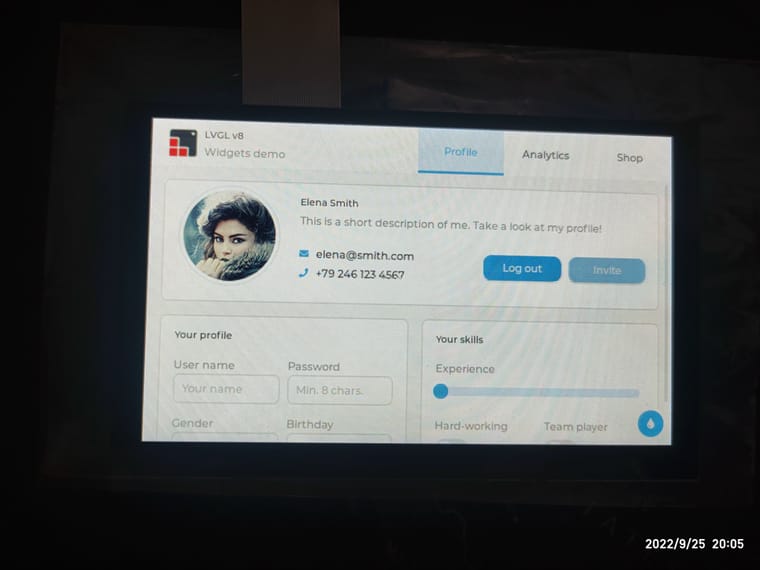

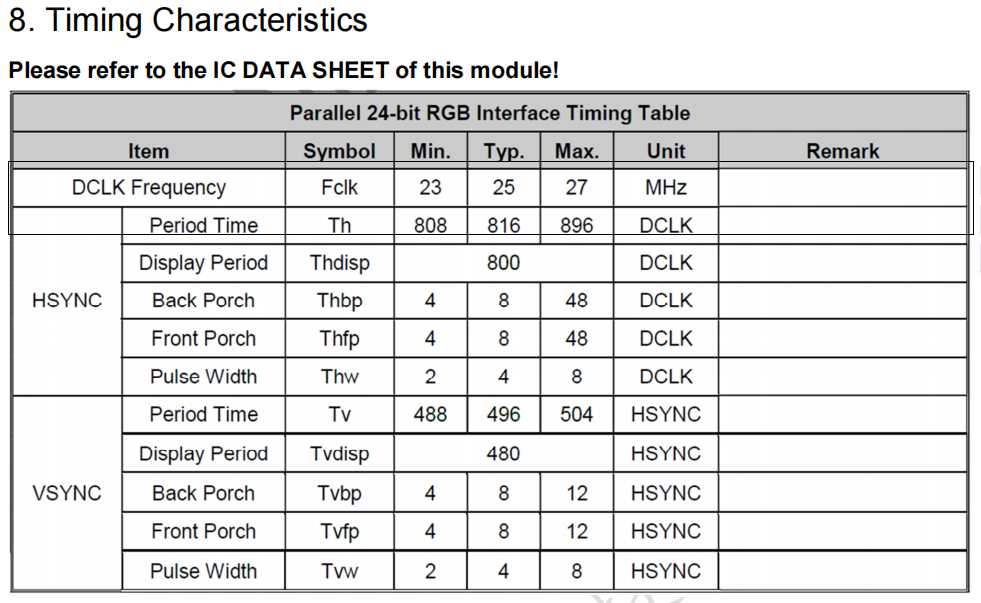

/* * Allwinner Technology CO., Ltd. */ /dts-v1/; /* optee used 7MB: SHM 2M: OS: 1M: TA:4M*/ /memreserve/ 0x41B00000 0x00100000; /* DSP used 1MB */ /*/memreserve/ 0x42000000 0x00100000;*/ #include "sun8iw20p1.dtsi" /{ model = "sun8iw20"; compatible = "allwinner,r528", "arm,sun8iw20p1"; reg_vdd_cpu: vdd-cpu { compatible = "sunxi-pwm-regulator"; pwms = <&pwm 3 5000 0>; regulator-name = "vdd_cpu"; regulator-min-microvolt = <810000>; regulator-max-microvolt = <1160000>; regulator-ramp-delay = <25>; regulator-always-on; regulator-boot-on; status = "okay"; }; reg_usb1_vbus: usb1-vbus { compatible = "regulator-fixed"; regulator-name = "usb1-vbus"; regulator-min-microvolt = <5000000>; regulator-max-microvolt = <5000000>; regulator-enable-ramp-delay = <1000>; gpio = <&pio PB 3 GPIO_ACTIVE_HIGH>; enable-active-high; }; }; &cpu0 { cpu-supply = <®_vdd_cpu>; }; &pio { sdc0_pins_a: sdc0@0 { allwinner,pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5"; allwinner,function = "sdc0"; allwinner,muxsel = <2>; allwinner,drive = <3>; allwinner,pull = <1>; pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5"; function = "sdc0"; drive-strength = <30>; bias-pull-up; power-source = <3300>; }; sdc0_pins_b: sdc0@1 { pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5"; function = "sdc0"; drive-strength = <30>; bias-pull-up; power-source = <1800>; }; sdc0_pins_c: sdc0@2 { pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5"; function = "gpio_in"; }; /* TODO: add jtag pin */ sdc0_pins_d: sdc0@3 { pins = "PF2", "PF4"; function = "uart0"; drive-strength = <10>; bias-pull-up; }; sdc0_pins_e: sdc0@4 { pins = "PF0", "PF1", "PF3", "PF5"; function = "jtag"; drive-strength = <10>; bias-pull-up; }; sdc1_pins_a: sdc1@0 { pins = "PG0", "PG1", "PG2", "PG3", "PG4", "PG5"; function = "sdc1"; drive-strength = <30>; bias-pull-up; }; sdc1_pins_b: sdc1@1 { pins = "PG0", "PG1", "PG2", "PG3", "PG4", "PG5"; function = "gpio_in"; }; sdc2_pins_a: sdc2@0 { allwinner,pins = "PC2", "PC3", "PC4", "PC5", "PC6", "PC7"; allwinner,function = "sdc2"; allwinner,muxsel = <3>; allwinner,drive = <3>; allwinner,pull = <1>; pins = "PC2", "PC3", "PC4", "PC5", "PC6", "PC7"; function = "sdc2"; drive-strength = <30>; bias-pull-up; }; sdc2_pins_b: sdc2@1 { pins = "PC2", "PC3", "PC4", "PC5", "PC6", "PC7"; function = "gpio_in"; }; wlan_pins_a:wlan@0 { pins = "PG11"; function = "clk_fanout1"; }; uart0_pins_a: uart0_pins@0 { /* For EVB1 board */ pins = "PF2", "PF4"; function = "uart0"; drive-strength = <10>; bias-pull-up; }; uart0_pins_b: uart0_pins@1 { /* For EVB1 board */ pins = "PF2", "PF4"; function = "gpio_in"; }; uart1_pins_a: uart1_pins@0 { /* For EVB1 board */ pins = "PG6", "PG7", "PG8", "PG9"; function = "uart1"; drive-strength = <10>; bias-pull-up; }; uart1_pins_b: uart1_pins { /* For EVB1 board */ pins = "PG6", "PG7", "PG8", "PG9"; function = "gpio_in"; }; uart2_pins_a: uart2_pins@0 { /* For EVB1 board */ pins = "PC0", "PC1"; function = "uart2"; drive-strength = <10>; bias-pull-up; }; uart2_pins_b: uart2_pins@1 { /* For EVB1 board */ pins = "PC0", "PC1"; function = "gpio_in"; }; uart3_pins_a: uart3_pins@0 { /* For awol nezha board */ pins = "PB6", "PB7"; function = "uart3"; muxsel = <7>; drive-strength = <10>; bias-pull-up; }; uart3_pins_b: uart3_pins@1 { /* For awol nezha board */ pins = "PB6", "PB7"; function = "gpio_in"; }; twi0_pins_a: twi0@0 { pins = "PB10", "PB11"; /*sck sda*/ function = "twi0"; drive-strength = <10>; }; twi0_pins_b: twi0@1 { pins = "PB10", "PB11"; function = "gpio_in"; }; twi1_pins_a: twi1@0 { pins = "PB4", "PB5"; function = "twi1"; drive-strength = <10>; }; twi1_pins_b: twi1@1 { pins = "PB4", "PB5"; function = "gpio_in"; }; twi2_pins_a: twi2@0 { pins = "PE12", "PE13"; function = "twi2"; drive-strength = <10>; }; twi2_pins_b: twi2@1 { pins = "PE12", "PE13"; function = "gpio_in"; }; twi3_pins_a: twi3@0 { pins = "PE6", "PE7"; function = "twi3"; drive-strength = <10>; }; twi3_pins_b: twi3@1 { pins = "PE6", "PE7"; function = "gpio_in"; }; dmic_pins_a: dmic@0 { /* DMIC_PIN: CLK, DATA0, DATA1, DATA2, DATA3*/ pins = "PB12", "PB11", "PB10", "PE14", "PB8"; function = "dmic"; drive-strength = <20>; bias-disable; }; dmic_pins_b: dmic@1 { pins = "PB12", "PB11", "PB10", "PE14", "PB8"; function = "io_disabled"; drive-strength = <20>; bias-disable; }; daudio0_pins_a: daudio0@0 { pins = "PE17", "PE16", "PE15", "PE14", "PE13"; function = "i2s0"; drive-strength = <20>; bias-disable; }; daudio0_pins_b: daudio0_sleep@0 { pins = "PE17", "PE16", "PE15", "PE14", "PE13"; function = "io_disabled"; drive-strength = <20>; bias-disable; }; daudio1_pins_a: daudio1@0 { pins = "PG11", "PG12", "PG13", "PG14", "PG15"; function = "i2s1"; drive-strength = <20>; bias-disable; }; daudio1_pins_b: daudio1_sleep@0 { pins = "PG11", "PG12", "PG13", "PG14", "PG15"; function = "io_disabled"; drive-strength = <20>; bias-disable; }; daudio2_pins_a: daudio2@0 { /* I2S_PIN: MCLK, BCLK, LRCK */ pins = "PF6", "PF3", "PF5"; function = "i2s2"; drive-strength = <20>; bias-disable; }; daudio2_pins_b: daudio2@1 { /* I2S_PIN: DOUT0 */ pins = "PF1"; function = "i2s2_dout"; drive-strength = <20>; bias-disable; }; daudio2_pins_c: daudio2@2 { /* I2S_PIN: DIN0 */ pins = "PF0"; function = "i2s2_din"; drive-strength = <20>; bias-disable; }; daudio2_pins_d: daudio2_sleep@0 { pins = "PF6", "PF3", "PF5", "PF1", "PF0"; function = "io_disabled"; drive-strength = <20>; bias-disable; }; spdif_pins_a: spdif@0 { /* SPDIF_PIN: SPDIF_OUT */ pins = "PG18"; function = "spdif"; drive-strength = <20>; bias-disable; }; spdif_pins_b: spdif_sleep@0 { pins = "PG18"; function = "io_disabled"; drive-strength = <20>; bias-disable; }; spi0_pins_a: spi0@0 { pins = "PC2", "PC4", "PC5"; /* clk, mosi, miso */ function = "spi0"; muxsel = <2>; drive-strength = <10>; }; spi0_pins_b: spi0@1 { pins = "PC3", "PC7", "PC6"; function = "spi0"; muxsel = <2>; drive-strength = <10>; bias-pull-up; /* cs, hold, wp should be pulled up */ }; spi0_pins_c: spi0@2 { pins = "PC2", "PC3", "PC4", "PC5","PC6", "PC7"; function = "gpio_in"; muxsel = <0>; drive-strength = <10>; }; spi1_pins_a: spi1@0 { pins = "PD11", "PD12", "PD13"; /* clk, mosi, miso */ function = "spi1"; drive-strength = <10>; }; spi1_pins_b: spi1@1 { pins = "PD10", "PD14", "PD15"; function = "spi1"; drive-strength = <10>; bias-pull-up; /* cs, hold, wp should be pulled up */ }; spi1_pins_c: spi1@2 { pins = "PD10", "PD11", "PD12", "PD13","PD14", "PD15"; function = "gpio_in"; drive-strength = <10>; }; ledc_pins_a: ledc@0 { pins = "PG13"; function = "ledc"; drive-strength = <10>; }; ledc_pins_b: ledc@1 { pins = "PG13"; function = "gpio_in"; }; pwm0_pin_a: pwm0@0 { pins = "PD16"; function = "pwm0"; drive-strength = <10>; bias-pull-up; }; pwm0_pin_b: pwm0@1 { pins = "PD16"; function = "gpio_in"; bias-disable; }; pwm2_pin_a: pwm2@0 { pins = "PD18"; function = "pwm2"; drive-strength = <10>; bias-pull-up; }; pwm2_pin_b: pwm2@1 { pins = "PD18"; function = "gpio_out"; }; pwm7_pin_a: pwm7@0 { pins = "PD22"; function = "pwm7"; drive-strength = <10>; bias-pull-up; }; pwm7_pin_b: pwm7@1 { pins = "PD22"; function = "gpio_in"; }; s_cir0_pins_a: s_cir@0 { pins = "PB7"; function = "ir"; drive-strength = <10>; bias-pull-up; }; s_cir0_pins_b: s_cir@1 { pins = "PB7"; function = "gpio_in"; }; ir1_pins_a: ir1@0 { pins = "PB0"; function = "ir"; drive-strength = <10>; bias-pull-up; }; ir1_pins_b: ir1@1 { pins = "PB0"; function = "gpio_in"; }; }; &uart0 { pinctrl-names = "default", "sleep"; pinctrl-0 = <&uart0_pins_a>; pinctrl-1 = <&uart0_pins_b>; status = "disabled"; }; &uart1 { pinctrl-names = "default", "sleep"; pinctrl-0 = <&uart1_pins_a>; pinctrl-1 = <&uart1_pins_b>; status = "disabled"; }; &uart2 { pinctrl-names = "default", "sleep"; pinctrl-0 = <&uart2_pins_a>; pinctrl-1 = <&uart2_pins_b>; status = "disabled"; }; /* for debug */ &uart3 { pinctrl-names = "default", "sleep"; pinctrl-0 = <&uart3_pins_a>; pinctrl-1 = <&uart3_pins_b>; status = "okay"; }; /* for dsp debug &uart3 { compatible = "allwinner,sun20iw1-dsp-uart"; pinctrl-names = "default", "sleep"; pinctrl-0 = <&uart3_pins_a>; pinctrl-1 = <&uart3_pins_b>; status = "okay"; }; */ &soc { card0_boot_para@2 { /* * Avoid dtc compiling warnings. * @TODO: Developer should modify this to the actual value */ reg = <0x0 0x2 0x0 0x0>; device_type = "card0_boot_para"; card_ctrl = <0x0>; card_high_speed = <0x1>; card_line = <0x4>; pinctrl-0 = <&sdc0_pins_a>; }; card2_boot_para@3 { /* * Avoid dtc compiling warnings. * @TODO: Developer should modify this to the actual value */ reg = <0x0 0x3 0x0 0x0>; device_type = "card2_boot_para"; card_ctrl = <0x2>; card_high_speed = <0x1>; card_line = <0x4>; pinctrl-0 = <&sdc2_pins_a>; /*pinctrl-0 = <&sdc0_pins_a>;*/ /*sdc_ex_dly_used = <0x2>;*/ sdc_io_1v8 = <0x1>; /*sdc_type = "tm4";*/ sdc_tm4_hs200_max_freq = <150>; sdc_tm4_hs400_max_freq = <100>; sdc_ex_dly_used = <2>; /*sdc_tm4_win_th = <8>;*/ /*sdc_dis_host_caps = <0x180>;*/ }; rfkill: rfkill@0 { compatible = "allwinner,sunxi-rfkill"; chip_en; power_en; pinctrl-0 = <&wlan_pins_a>; pinctrl-names = "default"; status = "okay"; wlan: wlan@0 { compatible = "allwinner,sunxi-wlan"; clock-names = "32k-fanout1"; clocks = <&ccu CLK_FANOUT1_OUT>; wlan_busnum = <0x1>; wlan_regon = <&pio PG 12 GPIO_ACTIVE_HIGH>; wlan_hostwake = <&pio PG 10 GPIO_ACTIVE_HIGH>; /*wlan_power = "VCC-3V3";*/ /*wlan_power_vol = <3300000>;*/ /*interrupt-parent = <&pio>; interrupts = < PG 10 IRQ_TYPE_LEVEL_HIGH>;*/ wakeup-source; }; bt: bt@0 { compatible = "allwinner,sunxi-bt"; clock-names = "32k-fanout1"; clocks = <&ccu CLK_FANOUT1_OUT>; /*bt_power_num = <0x01>;*/ /*bt_power = "axp803-dldo1";*/ /*bt_io_regulator = "axp803-dldo1";*/ /*bt_io_vol = <3300000>;*/ /*bt_power_vol = <330000>;*/ bt_rst_n = <&pio PG 15 GPIO_ACTIVE_LOW>; status = "okay"; }; }; btlpm: btlpm@0 { compatible = "allwinner,sunxi-btlpm"; uart_index = <0x1>; bt_wake = <&pio PG 15 GPIO_ACTIVE_HIGH>; bt_hostwake = <&pio PG 14 GPIO_ACTIVE_HIGH>; status = "okay"; }; addr_mgt: addr_mgt@0 { compatible = "allwinner,sunxi-addr_mgt"; type_addr_wifi = <0x0>; type_addr_bt = <0x0>; type_addr_eth = <0x0>; status = "okay"; }; }; &sdc2 { non-removable; bus-width = <4>; mmc-ddr-1_8v; mmc-hs200-1_8v; no-sdio; no-sd; ctl-spec-caps = <0x308>; cap-mmc-highspeed; sunxi-power-save-mode; sunxi-dis-signal-vol-sw; mmc-bootpart-noacc; max-frequency = <150000000>; /*vmmc-supply = <®_dcdc1>;*/ /*emmc io vol 3.3v*/ /*vqmmc-supply = <®_aldo1>;*/ /*emmc io vol 1.8v*/ /*vqmmc-supply = <®_eldo1>;*/ status = "disabled"; }; &sdc0 { bus-width = <4>; cd-gpios = <&pio PF 6 (GPIO_ACTIVE_LOW | GPIO_PULL_UP)>; /*non-removable;*/ /*broken-cd;*/ /*cd-inverted;*/ /*data3-detect;*/ /*card-pwr-gpios = <&pio PH 14 1 1 2 0xffffffff>;*/ cd-used-24M; cap-sd-highspeed; /*sd-uhs-sdr50;*/ /*sd-uhs-ddr50;*/ /*sd-uhs-sdr104;*/ no-sdio; no-mmc; sunxi-power-save-mode; /*sunxi-dis-signal-vol-sw;*/ max-frequency = <150000000>; ctl-spec-caps = <0x8>; /*vmmc-supply = <®_dcdc1>;*/ /*vqmmc33sw-supply = <®_dcdc1>;*/ /*vdmmc33sw-supply = <®_dcdc1>;*/ /*vqmmc18sw-supply = <®_eldo1>;*/ /*vdmmc18sw-supply = <®_eldo1>;*/ status = "okay"; }; &sdc1 { bus-width = <4>; no-mmc; no-sd; cap-sd-highspeed; /*sd-uhs-sdr12*/ /*sd-uhs-sdr25;*/ /*sd-uhs-sdr50;*/ /*sd-uhs-ddr50;*/ /*sd-uhs-sdr104;*/ /*sunxi-power-save-mode;*/ /*sunxi-dis-signal-vol-sw;*/ cap-sdio-irq; keep-power-in-suspend; ignore-pm-notify; max-frequency = <150000000>; ctl-spec-caps = <0x8>; status = "okay"; }; /* tvd configuration used (create device, 0: do not create device, 1: create device) agc_auto_enable (0: agc manual mode,agc_manual_value is valid; 1: agc auto mode) agc_manual_value (agc manual value, default value is 64) cagc_enable (cagc 0: disable, 1: enable) fliter_used (3d fliter 0: disable, 1: enable) support two PMU power (tvd_power0, tvd_power1) support two GPIO power (tvd_gpio0, tvd_gpio1) NOTICE: If tvd need pmu power or gpio power,params need be configured under [tvd] tvd_sw (the switch of all tvd driver.) tvd_interface (0: cvbs, 1: ypbpr,) tvd_format (0:TVD_PL_YUV420 , 1: MB_YUV420, 2: TVD_PL_YUV422) tvd_system (0:ntsc, 1:pal) tvd_row (total row number in multi channel mode 1-2) tvd_column (total column number in multi channel mode 1-2) tvd_channelx_en (0:disable, 1~4:position in multi channel mode,In single channel mode,mean enable) tvd_row*tvd_column is the total tvd channel number to be used in multichannel mode +--------------------+--------------------+ | | | | | | | 1 | 2 | | | | | | | +--------------------+--------------------+ | | | | | | | 3 | 4 | | | | | | | +--------------------+--------------------+ */ &tvd { tvd_sw = <1>; tvd_interface = <0>; tvd_format = <0>; tvd_system = <1>; tvd_row = <1>; tvd_column = <1>; tvd_channel0_en = <1>; tvd_channel1_en = <0>; tvd_channel2_en = <0>; tvd_channel3_en = <0>; /*tvd_gpio0 = <&pio PD 22 GPIO_ACTIVE_HIGH>;*/ /*tvd_gpio1 = <&pio PD 23 GPIO_ACTIVE_HIGH>;*/ /*tvd_gpio2 = <&pio PD 24 GPIO_ACTIVE_HIGH>;*/ /* dc1sw-supply = <®_dc1sw>;*/ /* eldo3-supply = <®_eldo3>;*/ /*tvd_power0 = "dc1sw"*/ /*tvd_power1 = "eldo3"*/ }; &tvd0 { used = <1>; agc_auto_enable = <1>; agc_manual_value = <64>; cagc_enable = <1>; fliter_used = <1>; }; /* Audio Driver modules */ &sunxi_rpaf_dsp0 { status = "disabled"; }; /* if audiocodec is used, sdc0 and uart0 should be closed to enable PA. */ &codec { /* MIC and headphone gain setting */ mic1gain = <0x1F>; mic2gain = <0x1F>; mic3gain = <0x1F>; /* ADC/DAC DRC/HPF func enabled */ /* 0x1:DAP_HP_EN; 0x2:DAP_SPK_EN; 0x3:DAP_HPSPK_EN */ adcdrc_cfg = <0x0>; adchpf_cfg = <0x1>; dacdrc_cfg = <0x0>; dachpf_cfg = <0x0>; /* Volume about */ digital_vol = <0x00>; lineout_vol = <0x1a>; headphonegain = <0x03>; /* Pa enabled about */ pa_level = <0x01>; pa_pwr_level = <0x01>; pa_msleep_time = <0x78>; /* gpio-spk = <&pio PF 2 GPIO_ACTIVE_HIGH>;*/ /* gpio-spk-pwr = <&pio PF 4 GPIO_ACTIVE_HIGH>; */ /* CMA config about */ playback_cma = <128>; capture_cma = <256>; /* regulator about */ /* avcc-supply = <®_aldo1>; */ /* hpvcc-supply = <®_eldo1>; */ status = "okay"; }; &sndcodec { hp_detect_case = <0x00>; jack_enable = <0x01>; status = "okay"; }; &dummy_cpudai { status = "okay"; }; &dmic { pinctrl-names = "default","sleep"; pinctrl-0 = <&dmic_pins_a>; pinctrl-1 = <&dmic_pins_b>; status = "disabled"; }; &dmic_codec { status = "disabled"; }; &sounddmic { status = "disabled"; }; /*----------------------------------------------------------------------------- * pcm_lrck_period 16/32/64/128/256 * slot_width_select 16bits/20bits/24bits/32bits * frametype 0 --> short frame = 1 clock width; * 1 --> long frame = 2 clock width; * tdm_config 0 --> pcm * 1 --> i2s * mclk_div 0 --> not output * 1/2/4/6/8/12/16/24/32/48/64/96/128/176/192 * (set mclk as external codec clk source, freq is pll_audio/mclk_div) * pinctrl_used 0 --> I2S/PCM use for internal * 1 --> I2S/PCM use for external audio * daudio_type: 0 --> external audio type *---------------------------------------------------------------------------*/ &daudio0 { mclk_div = <0x01>; frametype = <0x00>; tdm_config = <0x01>; sign_extend = <0x00>; msb_lsb_first = <0x00>; pcm_lrck_period = <0x80>; slot_width_select = <0x20>; pinctrl-names = "default", "sleep"; pinctrl-0 = <&daudio0_pins_a>; pinctrl-1 = <&daudio0_pins_b>; pinctrl_used = <0x0>; status = "disabled"; }; /*----------------------------------------------------------------------------- * simple-audio-card,name name of sound card, e.g. * "snddaudio0" --> use for external audio * sound-dai "snd-soc-dummy" --> use for I2S * "ac108" --> use for external audio of ac108 *---------------------------------------------------------------------------*/ &sounddaudio0 { /* simple-audio-card,format = "i2s"; */ /* simple-audio-card,frame-master = <&daudio0_master>; */ /* simple-audio-card,bitclock-master = <&daudio0_master>; */ /* simple-audio-card,bitclock-inversion; */ /* simple-audio-card,frame-inversion; */ status = "disabled"; daudio0_master: simple-audio-card,codec { /* sound-dai = <&ac108>; */ }; }; &daudio1 { mclk_div = <0x01>; frametype = <0x00>; tdm_config = <0x01>; sign_extend = <0x00>; msb_lsb_first = <0x00>; pcm_lrck_period = <0x80>; slot_width_select = <0x20>; pinctrl-names = "default", "sleep"; pinctrl-0 = <&daudio1_pins_a>; pinctrl-1 = <&daudio1_pins_b>; pinctrl_used = <0x0>; status = "disabled"; }; &sounddaudio1 { status = "disabled"; daudio1_master: simple-audio-card,codec { /* sound-dai = <&ac108>; */ }; }; &daudio2 { mclk_div = <0x01>; frametype = <0x00>; tdm_config = <0x01>; sign_extend = <0x00>; tx_data_mode = <0x00>; rx_data_mode = <0x00>; msb_lsb_first = <0x00>; pcm_lrck_period = <0x80>; slot_width_select = <0x20>; asrc_function_en = <0x00>; pinctrl-names = "default", "sleep"; pinctrl-0 = <&daudio2_pins_a &daudio2_pins_b &daudio2_pins_c>; pinctrl-1 = <&daudio2_pins_d>; pinctrl_used = <0x1>; daudio_type = <0x0>; status = "disabled"; }; &sounddaudio2 { status = "disabled"; daudio2_master: simple-audio-card,codec { /* sound-dai = <&ac108>; */ }; }; &spdif { pinctrl-names = "default","sleep"; pinctrl-0 = <&spdif_pins_a>; pinctrl-1 = <&spdif_pins_b>; status = "disabled"; }; &soundspdif { status = "disabled"; }; /* *usb_port_type: usb mode. 0-device, 1-host, 2-otg. *usb_detect_type: usb hotplug detect mode. 0-none, 1-vbus/id detect, 2-id/dpdm detect. *usb_detect_mode: 0-thread scan, 1-id gpio interrupt. *usb_id_gpio: gpio for id detect. *usb_det_vbus_gpio: gpio for id detect. gpio or "axp_ctrl"; *usb_wakeup_suspend:0-SUPER_STANDBY, 1-USB_STANDBY. */ &usbc0 { device_type = "usbc0"; usb_port_type = <0x2>; usb_detect_type = <0x1>; usb_detect_mode = <0>; usb_id_gpio = <&pio PB 8 GPIO_ACTIVE_HIGH>; enable-active-high; usb_det_vbus_gpio = <&pio PB 9 GPIO_ACTIVE_LOW>; usb_wakeup_suspend = <0>; usb_serial_unique = <0>; usb_serial_number = "20080411"; rndis_wceis = <1>; status = "okay"; }; &ehci0 { drvvbus-supply = <®_usb1_vbus>; }; &ohci0 { drvvbus-supply = <®_usb1_vbus>; }; &usbc1 { device_type = "usbc1"; usb_port_type = <0x01>; sb_detect_type = <0x1>; usb_regulator_io = "nocare"; usb_wakeup_suspend = <0>; status = "okay"; }; &ehci1 { status = "okay"; }; &ohci1 { status = "okay"; }; &twi0 { clock-frequency = <400000>; pinctrl-0 = <&twi0_pins_a>; pinctrl-1 = <&twi0_pins_b>; pinctrl-names = "default", "sleep"; status = "disabled"; eeprom@50 { compatible = "atmel,24c16"; reg = <0x50>; status = "disabled"; }; }; &twi1 { clock-frequency = <400000>; pinctrl-0 = <&twi1_pins_a>; pinctrl-1 = <&twi1_pins_b>; pinctrl-names = "default", "sleep"; status = "disabled"; }; &twi2 { clock-frequency = <400000>; pinctrl-0 = <&twi2_pins_a>; pinctrl-1 = <&twi2_pins_b>; pinctrl-names = "default", "sleep"; dmas = <&dma 45>, <&dma 45>; dma-names = "tx", "rx"; status = "okay"; /* pcf8574-usage: * only use gpio0~7, 0 means PP0. * pin set: * gpios = <&pcf8574 0 GPIO_ACTIVE_LOW>; * interrupt set: * interrupt-parent = <&pcf8574>; * interrupts = <0 IRQ_TYPE_EDGE_FALLING>; */ /*pcf8574: gpio@38 { compatible = "nxp,pcf8574"; reg = <0x38>; gpio_base = <2020>; gpio-controller; #gpio-cells = <2>; interrupt-controller; #interrupt-cells = <2>; interrupt-parent = <&pio>; interrupts = <PB 2 IRQ_TYPE_EDGE_FALLING>; status = "disabled"; }; */ ctp@38 { compatible = "focaltech,fts"; reg = <0x38>; status = "okay"; interrupt-parent = <&pio>; interrupts = <PB 3 IRQ_TYPE_LEVEL_LOW>; focaltech,reset-gpio = <&pio PB 2 GPIO_ACTIVE_HIGH>; focaltech,irq-gpio = <&pio PB 3 IRQ_TYPE_LEVEL_LOW>; focaltech,max-touch-number = <2>; focaltech,display-coords = <0 0 800 480>; focaltech,reg_vdd = <®_pio3_3>; focaltech,reg_avdd = <®_pio3_3>; }; }; &twi3 { clock-frequency = <400000>; pinctrl-0 = <&twi3_pins_a>; pinctrl-1 = <&twi3_pins_b>; pinctrl-names = "default", "sleep"; status = "disabled"; }; /* &gmac0 { phy-mode = "rmii"; use_ephy25m = <0>; pinctrl-0 = <&gmac_pins_a>; pinctrl-1 = <&gmac_pins_b>; pinctrl-names = "default", "sleep"; phy-rst = <&pio PE 10 GPIO_ACTIVE_HIGH>; status = "okay"; };*/ &spi0 { clock-frequency = <100000000>; pinctrl-0 = <&spi0_pins_a &spi0_pins_b>; pinctrl-1 = <&spi0_pins_c>; pinctrl-names = "default", "sleep"; /*spi-supply = <®_dcdc1>;*/ spi_slave_mode = <0>; spi0_cs_number = <1>; spi0_cs_bitmap = <1>; status = "okay"; spi-nand@0 { compatible = "spi-nand"; spi-max-frequency=<100000000>; reg = <0x0>; spi-rx-bus-width=<0x04>; spi-tx-bus-width=<0x04>; status="okay"; }; spi-nor@0 { compatible = "jedec,spi-nor"; spi-max-frequency=<30000000>; reg = <0x0>; spi-rx-bus-width=<0x01>; spi-tx-bus-width=<0x01>; status="disabled"; }; }; &spi1 { clock-frequency = <100000000>; pinctrl-0 = <&spi1_pins_a &spi1_pins_b>; pinctrl-1 = <&spi1_pins_c>; pinctrl-names = "default", "sleep"; spi_slave_mode = <0>; status = "disabled"; spi_board1@0 { device_type = "spi_board1"; compatible = "rohm,dh2228fv"; spi-max-frequency = <0x5f5e100>; reg = <0x0>; spi-rx-bus-width = <0x4>; spi-tx-bus-width = <0x4>; status = "disabled"; }; }; &ledc { pinctrl-names = "default", "sleep"; pinctrl-0 = <&ledc_pins_a>; pinctrl-1 = <&ledc_pins_b>; led_count = <3>; output_mode = "GRB"; reset_ns = <84>; t1h_ns = <800>; t1l_ns = <320>; t0h_ns = <300>; t0l_ns = <800>; wait_time0_ns = <84>; wait_time1_ns = <84>; wait_data_time_ns = <600000>; status = "okay"; }; &keyboard0 { key0 = <210 0x160>; wakeup-source; status = "disabled"; }; /*---------------------------------------------------------------------------------- disp init configuration disp_mode (0:screen0<screen0,fb0>) screenx_output_type (0:none; 1:lcd; 2:tv; 3:hdmi;5:vdpo) screenx_output_mode (used for hdmi output, 0:480i 1:576i 2:480p 3:576p 4:720p50) (5:720p60 6:1080i50 7:1080i60 8:1080p24 9:1080p50 10:1080p60) screenx_output_format (for hdmi, 0:RGB 1:yuv444 2:yuv422 3:yuv420) screenx_output_bits (for hdmi, 0:8bit 1:10bit 2:12bit 2:16bit) screenx_output_eotf (for hdmi, 0:reserve 4:SDR 16:HDR10 18:HLG) screenx_output_cs (for hdmi, 0:undefined 257:BT709 260:BT601 263:BT2020) screenx_output_dvi_hdmi (for hdmi, 0:undefined 1:dvi mode 2:hdmi mode) screen0_output_range (for hdmi, 0:default 1:full 2:limited) screen0_output_scan (for hdmi, 0:no data 1:overscan 2:underscan) screen0_output_aspect_ratio (for hdmi, 8-same as original picture 9-4:3 10-16:9 11-14:9) fbx format (4:RGB655 5:RGB565 6:RGB556 7:ARGB1555 8:RGBA5551 9:RGB888 10:ARGB8888 12:ARGB4444) fbx pixel sequence (0:ARGB 1:BGRA 2:ABGR 3:RGBA) fb0_scaler_mode_enable(scaler mode enable, used FE) fbx_width,fbx_height (framebuffer horizontal/vertical pixels, fix to output resolution while equal 0) lcdx_backlight (lcd init backlight,the range:[0,256],default:197 lcdx_yy (lcd init screen bright/contrast/saturation/hue, value:0~100, default:50/50/57/50) lcd0_contrast (LCD contrast, 0~100) lcd0_saturation (LCD saturation, 0~100) lcd0_hue (LCD hue, 0~100) framebuffer software rotation setting: disp_rotation_used: (0:disable; 1:enable,you must set fbX_width to lcd_y, set fbX_height to lcd_x) degreeX: (X:screen index; 0:0 degree; 1:90 degree; 3:270 degree) degreeX_Y: (X:screen index; Y:layer index 0~15; 0:0 degree; 1:90 degree; 3:270 degree) devX_output_type : config output type in bootGUI framework in UBOOT-2018. (0:none; 1:lcd; 2:tv; 4:hdmi;) devX_output_mode : config output resolution(see include/video/sunxi_display2.h) of bootGUI framework in UBOOT-2018 devX_screen_id : config display index of bootGUI framework in UBOOT-2018 devX_do_hpd : whether do hpd detectation or not in UBOOT-2018 chn_cfg_mode : Hardware DE channel allocation config. 0:single display with 6 channel, 1:dual display with 4 channel in main display and 2 channel in second display, 2:dual display with 3 channel in main display and 3 channel in second in display. ----------------------------------------------------------------------------------*/ &disp { disp_init_enable = <1>; disp_mode = <0>; screen0_output_type = <1>; screen0_output_mode = <4>; screen1_output_type = <3>; screen1_output_mode = <4>; screen1_output_format = <0>; screen1_output_bits = <0>; screen1_output_eotf = <4>; screen1_output_cs = <257>; screen1_output_dvi_hdmi = <2>; screen1_output_range = <2>; screen1_output_scan = <0>; screen1_output_aspect_ratio = <8>; dev0_output_type = <1>; dev0_output_mode = <4>; dev0_screen_id = <0>; dev0_do_hpd = <0>; dev1_output_type = <4>; dev1_output_mode = <10>; dev1_screen_id = <1>; dev1_do_hpd = <1>; def_output_dev = <0>; hdmi_mode_check = <1>; disp_rotation_used = <1>; degree0 = <0>; fb0_format = <0>; fb0_buffer_num = <1>; /*fb0_width = <800>;*/ /*fb0_height = <480>;*/ /*read from lcd*/ fb1_format = <0>; fb1_width = <0>; fb1_height = <0>; chn_cfg_mode = <1>; disp_para_zone = <1>; /*VCC-LCD*/ /* dc1sw-supply = <®_dc1sw>;*/ /*VCC-DSI*/ /* eldo3-supply = <®_eldo3>;*/ /*VCC-PD*/ /* dcdc1-supply = <®_dcdc1>;*/ }; /*---------------------------------------------------------------------------------- ;lcd0 configuration ;lcd_if: 0:hv(sync+de); 1:8080; 2:ttl; 3:lvds; 4:dsi; 5:edp; 6:extend dsi ;lcd_hv_if 0:Parallel RGB; 8:Serial RGB; 10:Dummy RGB; 11: RGB Dummy;12:CCIR656 ;lcd_hv_clk_phase 0:0 degree;1:90 degree;2:180 degree;3:270 degree ;lcd_hv_sync_polarity 0:vs low,hs low; 1:vs high,hslow; 2:vs low,hs high; 3:vs high,hs high ;lcd_hv_syuv_seq 0:YUYV; 1:YVYU; 2:UYVY; 3:VYUY ;lcd_cpu_if 0:18bit/1 cycle parallel(RGB666); 4:16bit/1cycle parallel (RGB565) ; 6:18bit/3 cycle parallel(RGB666); 7:16bit/2cycle parallel (RGB565) ;lcd_cpu_te 0:frame auto trigger; 1:frame triggered by te rising edge; 2:frame triggered by te falling edge; ;lcd_dsi_if 0:video mode; 1: Command mode; 2:video burst mode ;lcd_dsi_te 0:frame auto trigger; 1:frame triggered by te rising edge; 2:frame triggered by te falling edge; ;lcd_x: lcd horizontal resolution ;lcd_y: lcd vertical resolution ;lcd_width: width of lcd in mm ;lcd_height: height of lcd in mm ;lcd_dclk_freq: in MHZ unit ;lcd_pwm_freq: in HZ unit ;lcd_pwm_pol: lcd backlight PWM polarity ;lcd_pwm_max_limit lcd backlight PWM max limit(<=255) ;lcd_hbp: hsync back porch(pixel) + hsync plus width(pixel); ;lcd_ht: hsync total cycle(pixel) ;lcd_vbp: vsync back porch(line) + vysnc plus width(line) ;lcd_vt: vysnc total cycle(line) ;lcd_hspw: hsync plus width(pixel) ;lcd_vspw: vysnc plus width(pixel) ;lcd_lvds_if: 0:single link; 1:dual link ;lcd_lvds_colordepth: 0:8bit; 1:6bit ;lcd_lvds_mode: 0:NS mode; 1:JEIDA mode ;lcd_frm: 0:disable; 1:enable rgb666 dither; 2:enable rgb656 dither ;lcd_io_phase: 0:noraml; 1:intert phase(0~3bit: vsync phase; 4~7bit:hsync phase; ; 8~11bit:dclk phase; 12~15bit:de phase) ;lcd_gamma_en lcd gamma correction enable ;lcd_bright_curve_en lcd bright curve correction enable ;lcd_cmap_en lcd color map function enable ;deu_mode 0:smoll lcd screen; 1:large lcd screen(larger than 10inch) ;lcdgamma4iep: Smart Backlight parameter, lcd gamma vale * 10; ; decrease it while lcd is not bright enough; increase while lcd is too bright ;smart_color 90:normal lcd screen 65:retina lcd screen(9.7inch) ;Pin setting for special function ie.LVDS, RGB data or vsync ; name(donot care) = port:PD12<pin function><pull up or pull down><drive ability><output level> ;Pin setting for gpio: ; lcd_gpio_X = port:PD12<pin function><pull up or pull down><drive ability><output level> ;Pin setting for backlight enable pin ; lcd_bl_en = port:PD12<pin function><pull up or pull down><drive ability><output level> ;fsync setting, pulse to csi ;lcd_fsync_en (0:disable fsync,1:enable) ;lcd_fsync_act_time (active time of fsync, unit:pixel) ;lcd_fsync_dis_time (disactive time of fsync, unit:pixel) ;lcd_fsync_pol (0:positive;1:negative) ;gpio config: <&pio for cpu or &r_pio for cpus, port, port num, pio function, pull up or pull down(default 0), driver level(default 1), data> ;For dual link lvds: use lvds2link_pins_a and lvds2link_pins_b instead ;For rgb24: use rgb24_pins_a and rgb24_pins_b instead ;For lvds1: use lvds1_pins_a and lvds1_pins_b instead ;For lvds0: use lvds0_pins_a and lvds0_pins_b instead ;----------------------------------------------------------------------------------*/ &lcd0 { // 800 * 480 RGB LCD lcd_used = <1>; lcd_driver_name = "default_lcd"; lcd_backlight = <50>; lcd_if = <0>; lcd_x = <800>; lcd_y = <480>; lcd_width = <108>; lcd_height = <65>; lcd_dclk_freq = <24>; lcd_pwm_used = <1>; lcd_pwm_ch = <9>; lcd_pwm_freq = <50000>; lcd_pwm_pol = <0>; lcd_hbp = <12>; lcd_ht = <816>; lcd_hspw = <4>; lcd_vbp = <12>; lcd_vt = <496>; lcd_vspw = <4>; lcd_lvds_if = <0>; lcd_lvds_colordepth = <1>; lcd_lvds_mode = <0>; lcd_frm = <0>; lcd_io_phase = <0x0000>; lcd_gamma_en = <0>; lcd_bright_curve_en = <0>; lcd_cmap_en = <0>; deu_mode = <0>; lcdgamma4iep = <22>; smart_color = <90>; pinctrl-0 = <&rgb18_pins_a>; pinctrl-1 = <&rgb18_pins_b>; }; &pwm0 { pinctrl-names = "active", "sleep"; pinctrl-0 = <&pwm0_pin_a>; pinctrl-1 = <&pwm0_pin_b>; status = "okay"; }; &pwm2 { pinctrl-names = "active", "sleep"; pinctrl-0 = <&pwm2_pin_a>; pinctrl-1 = <&pwm2_pin_b>; status = "okay"; }; &pwm7 { pinctrl-names = "active", "sleep"; pinctrl-0 = <&pwm7_pin_a>; pinctrl-1 = <&pwm7_pin_b>; status = "okay"; }; &rtp { allwinner,tp-sensitive-adjust = <0xf>; allwinner,filter-type = <0x1>; allwinner,ts-attached; status = "disabled"; }; &tpadc { key_cnt = <5>; key1 = <420 115>; key2 = <870 114>; key3 = <1290 119>; key4 = <1630 373>; key5 = <1950 28>; status = "disabled"; }; &gpadc { channel_num = <1>; channel_select = <0x01>; channel_data_select = <0>; channel_compare_select = <0x01>; channel_cld_select = <0x01>; channel_chd_select = <0>; channel0_compare_lowdata = <1600000>; channel0_compare_higdata = <1200000>; channel1_compare_lowdata = <460000>; channel1_compare_higdata = <1200000>; key_cnt = <5>; key0_vol = <210>; key0_val = <0x19c>; key1_vol = <410>; key1_val = <0x197>; key2_vol = <590>; key2_val = <158>; key3_vol = <750>; key3_val = <28>; key4_vol = <880>; key4_val = <28>; status = "okay"; wakeup-source; }; &s_cir0 { pinctrl-names = "default", "sleep"; pinctrl-0 = <&s_cir0_pins_a>; pinctrl-1 = <&s_cir0_pins_b>; ir_protocol_used = <0>; ir_addr_code0 = <0x0>; status = "okay"; }; &ir1 { pinctrl-names = "default", "sleep"; pinctrl-0 = <&ir1_pins_a>; pinctrl-1 = <&ir1_pins_b>; status = "disabled"; }; &vind0 { csi_top = <378000000>; csi_isp = <327000000>; status = "okay"; /* enable twi and ver1 spi-nand max freq 30M */ actuator0: actuator@5809450 { device_type = "actuator0"; actuator0_name = "ad5820_act"; actuator0_slave = <0x18>; actuator0_af_pwdn = <>; actuator0_afvdd = "afvcc-csi"; actuator0_afvdd_vol = <2800000>; status = "okay"; }; flash0: flash@5809460 { device_type = "flash0"; flash0_type = <2>; flash0_en = <>; flash0_mode = <>; flash0_flvdd = ""; flash0_flvdd_vol = <>; device_id = <0>; status = "okay"; }; sensor0: sensor@5809470 { reg = <0x0 0x05809470 0x0 0x10>; device_type = "sensor0"; compatible = "allwinner,sunxi-sensor"; sensor0_mname = "ov5640"; sensor0_twi_cci_id = <2>; sensor0_twi_addr = <0x78>; sensor0_mclk_id = <0>; sensor0_pos = "rear"; sensor0_isp_used = <0>; sensor0_fmt = <0>; sensor0_stby_mode = <0>; sensor0_vflip = <0>; sensor0_hflip = <0>; sensor0_iovdd-supply = <>; sensor0_iovdd_vol = <>; sensor0_avdd-supply = <>; sensor0_avdd_vol = <>; sensor0_dvdd-supply = <>; sensor0_dvdd_vol = <>; sensor0_power_en = <>; sensor0_reset = <>; sensor0_pwdn = <>; sensor0_sm_vs = <>; flash_handle = <&flash0>; act_handle = <&actuator0>; device_id = <0>; status = "okay"; }; sensor1:sensor@5809480 { device_type = "sensor1"; sensor1_mname = "ov5640"; compatible = "allwinner,sunxi-sensor"; sensor1_twi_cci_id = <1>; sensor1_twi_addr = <0x6c>; sensor1_mclk_id = <1>; sensor1_pos = "front"; sensor1_isp_used = <0>; sensor1_fmt = <0>; sensor1_stby_mode = <0>; sensor1_vflip = <0>; sensor1_hflip = <0>; sensor1_iovdd-supply = <>; sensor1_iovdd_vol = <>; sensor1_avdd-supply = <>; sensor1_avdd_vol = <>; sensor1_dvdd-supply = <>; sensor1_dvdd_vol = <>; sensor1_power_en = <>; sensor1_reset = <&pio PE 7 GPIO_ACTIVE_LOW>; sensor1_pwdn = <&pio PE 6 GPIO_ACTIVE_LOW>; status = "disabled"; }; vinc0:vinc@5809000 { vinc0_csi_sel = <0>; vinc0_mipi_sel = <0xff>; vinc0_isp_sel = <0>; vinc0_isp_tx_ch = <0>; vinc0_tdm_rx_sel = <0xff>; vinc0_rear_sensor_sel = <0>; vinc0_front_sensor_sel = <0>; vinc0_sensor_list = <0>; status = "okay"; }; vinc1:vinc@5809200 { vinc1_csi_sel = <0>; vinc1_mipi_sel = <0xff>; vinc1_isp_sel = <0>; vinc1_isp_tx_ch = <1>; vinc1_tdm_rx_sel = <0xff>; vinc1_rear_sensor_sel = <0>; vinc1_front_sensor_sel = <0>; vinc1_sensor_list = <0>; status = "okay"; }; };sun8iw20p1.dtsi