使用命令mboot编译boot0和uboot已经成功,产生的文件四uboot.bin

想使用sunxi_fel uboot命令下载到ram调试 提示

\u-boot.bin

Warning: no 'soc_sram_info' data for your SoC (id=1859)

SPL: eGON header is not found

spl头文件没有找到,应该用什么指令才可以产生包含spl的uboot呢,请教

使用命令mboot编译boot0和uboot已经成功,产生的文件四uboot.bin

想使用sunxi_fel uboot命令下载到ram调试 提示

\u-boot.bin

Warning: no 'soc_sram_info' data for your SoC (id=1859)

SPL: eGON header is not found

spl头文件没有找到,应该用什么指令才可以产生包含spl的uboot呢,请教

把CPU频率超频到了1.752GHz ddr超频到1.164G,老化测试了几个小时很稳定,没任何报错,芯片表面温度为49℃,室温为26℃

\ | /

- RT - Thread Operating System

/ | \ 4.1.0 build Sep 20 2022 10:33:12

2006 - 2022 Copyright by RT-Thread team

hello rt-thread 10:23:02

msh >CPU_clk=1752MHz

CPU_clk=1752MHz

DDR_clk=1164MHz

msh >core_mark

Benchmark started, please make sure it runs for at least 10s.

2K performance run parameters for coremark.

CoreMark Size : 666

Total ticks : 9352

Total time (secs): 9.352000

Iterations/Sec : 5346.449957

ERROR! Must execute for at least 10 secs for a valid result!

Iterations : 50000

Compiler version : GCC6.3.1 20170215 (release) [ARM/embedded-6-branch revision 245512]

Compiler flags :

Memory location : STACK

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0xa14c

Errors detected

msh >memory_perf 0x46000000 0x100000

MemoryPerf version 1.0.0

Copyright (c) 2022 SummerGift (summergift2019@gmail.com)

Licensed under the MIT License version.

Memory performance testing start...

address: 0x46000000, length: 0x100000, iterations: 200

Data length : 209 MB.

--------------------------------------

8-bit write speed test begin.

Spend time : 0.165000 s.

8-bit write speed: 1271.001221 M/s.

8-bit read speed test begin.

Spend time : 0.406000 s.

8-bit Read speed: 516.539917 M/s.

--------------------------------------

16-bit write speed test begin.

Spend time : 0.083000 s.

16-bit write speed: 2526.689209 M/s.

16-bit read speed test begin.

Spend time : 0.234000 s.

16-bit Read speed: 896.218811 M/s.

--------------------------------------

32-bit write speed test begin.

Spend time : 0.054000 s.

32-bit Write speed: 3883.614746 M/s.

32-bit read speed test begin.

Spend time : 0.133000 s.

32-bit Read speed: 1576.806030 M/s.

Memory performance completed.

最高测试了稳定的频率为 1.8G和1.2G,表面温度为62℃

\ | /

- RT - Thread Operating System

/ | \ 4.1.0 build Sep 20 2022 10:33:12

2006 - 2022 Copyright by RT-Thread team

hello rt-thread 10:33:28

msh >CPU_clk=1800MHz

CPU_clk=1800MHz

DDR_clk=1200MHz

msh >core_mark

Benchmark started, please make sure it runs for at least 10s.

2K performance run parameters for coremark.

CoreMark Size : 666

Total ticks : 9147

Total time (secs): 9.147000

Iterations/Sec : 5466.273095

ERROR! Must execute for at least 10 secs for a valid result!

Iterations : 50000

Compiler version : GCC6.3.1 20170215 (release) [ARM/embedded-6-branch revision 245512]

Compiler flags :

Memory location : STACK

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0xa14c

Errors detected

msh >memory_perf 0x46000000 0x100000

MemoryPerf version 1.0.0

Copyright (c) 2022 SummerGift (summergift2019@gmail.com)

Licensed under the MIT License version.

Memory performance testing start...

address: 0x46000000, length: 0x100000, iterations: 200

Data length : 209 MB.

--------------------------------------

8-bit write speed test begin.

Spend time : 0.164000 s.

8-bit write speed: 1278.751221 M/s.

8-bit read speed test begin.

Spend time : 0.399000 s.

8-bit Read speed: 525.601990 M/s.

--------------------------------------

16-bit write speed test begin.

Spend time : 0.083000 s.

16-bit write speed: 2526.689209 M/s.

16-bit read speed test begin.

Spend time : 0.229000 s.

16-bit Read speed: 915.786865 M/s.

--------------------------------------

32-bit write speed test begin.

Spend time : 0.051000 s.

32-bit Write speed: 4112.062500 M/s.

32-bit read speed test begin.

Spend time : 0.147000 s.

32-bit Read speed: 1426.634033 M/s.

Memory performance completed.

msh >

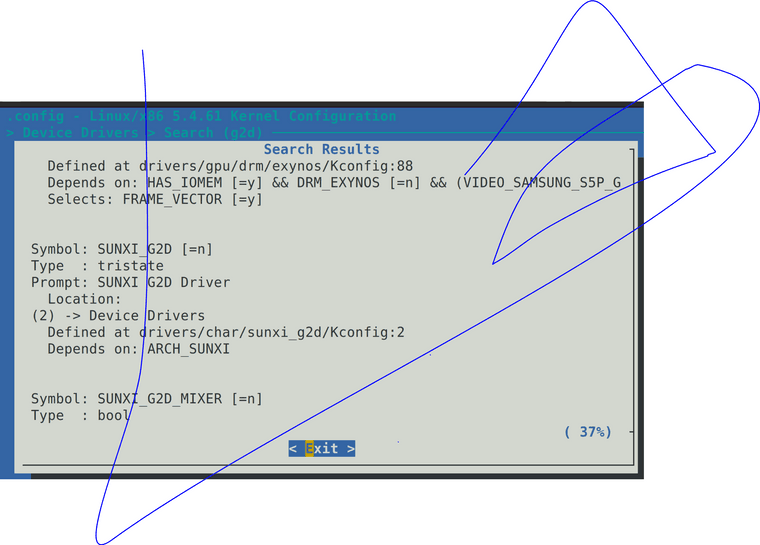

有谁移植过t113或者f133的裸机G2D部分吗,我愿意出400元,有这方面经验的朋友可以私信我,谢谢

@chengwei_peng 哦,cpu读取的话占用cpu比较高,因为我用到的波特率是1.5Mbps,我在研究研究吧,只能曲线救国了

@yuzukitsuru 以前用的smt32之类的单片机都是一个个接收的啊,串口缓冲区有一个数据dma就传输一个,并不是这样128字节一起传输啊,这个你们有没有碰到过,串口比较特殊的,接收到的数据可能是不定长的,并不能事先设置固定的dma长度啊

@yuzukitsuru 我用的是裸机,我测试出来的结果就是用dma接收串口数据的时候,不是串口接收到一个dma就捕获一个,而是需要等到128字节,dma才会从串口获取128字节,当然如果我配置为dma长度为16字节,那么16字节就可以.

请问一下t113的dma是否有bug,我在测试uart3的rxd接收dma,配置为dma1,然后开始接收数据,比如我配置为接收256个字节产生dma完成中断,这个是没有问题的,并且也能正常接收到数据,但是想实现任意长度数据的接收,然后就想到读取dma寄存器的

0x0118 + N*0x0040 DMAC Channel Byte Counter Left Register N (Default Value: 0x0000_0000)这个寄存器,看资料这个寄存器里面读出来的数据就是代表本次dma传输剩余的数据,比如我上位机发送10个数据过去,然后这里应该读取出来的是(256-10)=246个,打是我在读取中发现这里的数据固定为256.....只有当上位机发送128个字节之后,这里的数据变成128 ,然后继续保持128不变,直到上位机发送完256个字节这里才变成0,

也就是说这个寄存器里面的数据是按照128字节跳跃的,并不是接收到多少个,这里减少多少个,是我配置的问题还是这个芯片本身的bug,

如果按照128字节跳跃的话,我该如何实现dma接收不定长数据的功能

https://bbs.aw-ol.com/topic/1543/发现一个t113-spi诡异问题?_=1654672907596

参考之前的帖子,然后现在加了dma测试了一下,读取10MB的时间为181ms,换算下来55MB/s

因为用的120M时钟,所以理论上是60MB每秒,比用cpu读取的快5倍

@smiletiger 唉我自问自答把

刚刚测试发现逻辑分析仪接错了clk线,测试出来是设置没有生效,时钟一直是100M

现在总结如下: t113s3的qspi其实没有想象中那么好,缺少一个qspi io模式,只有qspi in/qspi out模式,在时钟频率比较低的时候,qspi的确比spi快3-4倍,但是在时钟频率在100m以上的时候,qspi反而没有spi快,我测试下来读取15MB资料,在120M下面,qspi花时间1978ms spi花时间1973ms,应该是全志的qspi并不是完整的qspi导致的,所以优化开机启动的时候,用100M spi模式就可以,还可以省2个io口

跑的裸机spi功能,我设置不同的spi_sclk,发现读取16M flash使用的时间居然不变,

用逻辑分析仪抓clk波形,发现clk的波形的确在100M--2.2M之间变化,但是读取完毕16M字节的速度居然都是在1600ms左右不变化,而且用qspi读取时间也几乎是1600ms不变,

现在有疑问如下:

1.用逻辑分析仪抓取的clk波形的确按照设置的频率改变了,所以不用怀疑是不是寄存器没设置进去的问题,

2.qspi和spi模式都用逻辑分析仪抓过,spi模式下面d2没有波形,qspi下面d2有波形,说明也是设置到qspi模式了

3.用printf随机打印出来不同内存地址的数据,数据和原始16M数据对比过数据是对的,

所以也不存在什么是不是数据没有读取完整这样的问题

那么是不是全志有啥黑科技?用3M的spi时钟可以在1.6s内读取完毕16MB的数据????????

@l13819506056 请问可以提供一下裸机g2d部分的全部驱动吗,我愿意给红包,因为自己对linux不太熟,感觉要修改好多才能用在裸机上,可否把g2d部分的代码打包发给我参考下,谢谢

@l13819506056 在 T113-S3 G2D 裸机测试 中说:

终于将G2D裸机环境使用搞定了。 简单测试了一下bitblt 和矩形填充。

extern const unsigned char image_mn_map[800*480*4];/*图片文件*/ void g2d_test(void) { g2d_probe(); g2d_open(); g2d_blt_h blit_para; while(1) { /* bitblt测试 */ memset(&blit_para,0,sizeof(g2d_blt_h)); g2d_image_enh *src = &blit_para.src_image_h; g2d_image_enh *des = &blit_para.dst_image_h; blit_para.flag_h = G2D_ROT_180;//G2D_ROT_V;// G2D_ROT_0; src->laddr[0] = (uint32_t)image_mn_map; src->align[0] = 4; src->clip_rect.w = 800; src->clip_rect.h = 480; src->width = 800; src->height = 480; src->format = G2D_FORMAT_ARGB8888; src->mode = G2D_PIXEL_ALPHA; src->bpremul = 0; des->laddr[0] = r528_de_config.LayerAddr[0] ; des->align[0] = 4; des->clip_rect.w = 800; des->clip_rect.h = 480; des->width = 800; des->height = 480; des->format = G2D_FORMAT_ARGB8888; des->mode = G2D_PIXEL_ALPHA; des->bpremul = 0; long ret = g2d_ioctl( G2D_CMD_BITBLT_H, (unsigned long )&blit_para); /* 矩形填充测试 */ g2d_fillrect_h fill_para; memset(&fill_para,0,sizeof(g2d_fillrect_h)); src = &fill_para.dst_image_h; src->laddr[0] = (uint32_t)r528_de_config.LayerAddr[0] ;; src->align[0] = 4; src->clip_rect.w = 800; src->clip_rect.h = 480; src->width = 800; src->height = 480; src->format = G2D_FORMAT_ARGB8888; src->mode = G2D_PIXEL_ALPHA; src->bpremul = 0; src->gamut = G2D_BT709; src->color = 0xFFFF0000; src->alpha = 0xff; ret = g2d_ioctl( G2D_CMD_FILLRECT_H, (unsigned long )&fill_para); } }

请问可以共享一下更多的细节吗,一直也在研究裸机G2D,一直搞不定看了linux的源代码

void g2d_top_set_base(unsigned long base)

{

g2d_top = (struct g2d_top_reg *)(base);

mixer_glb = (struct g2d_mixer_glb_reg *)(base + 0x0100);

}

void g2d_rot_set_base(unsigned long base)

{

base_addr = base;

}

这里的基址base是多少啊,是不是0x05410000

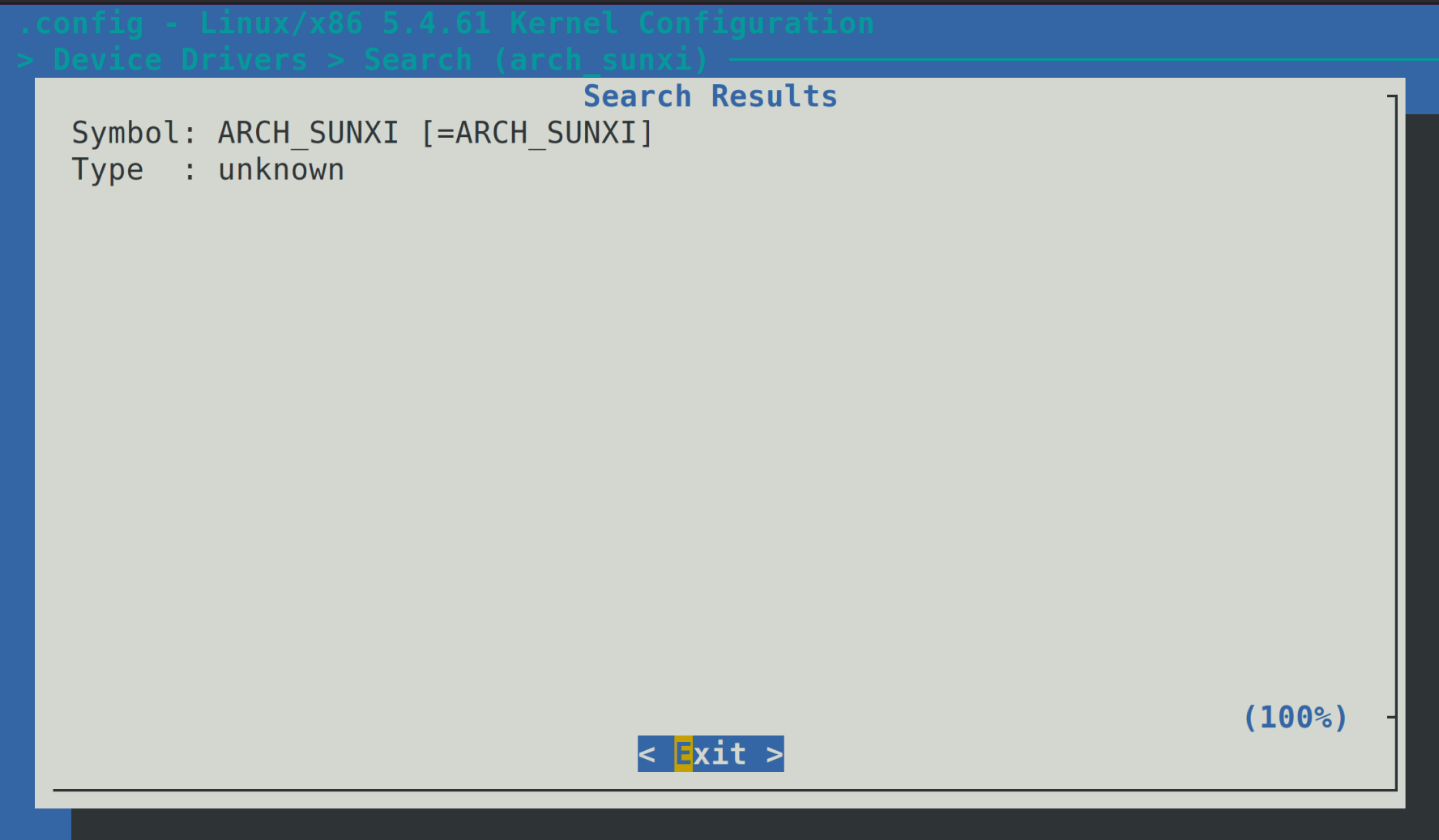

@yuzukitsuru 我下载了2个版本的tina_linux,两个都没有,我可以截图给你看

一个是longgan的,还有一个是普通的,但是打了mq双核的补丁的

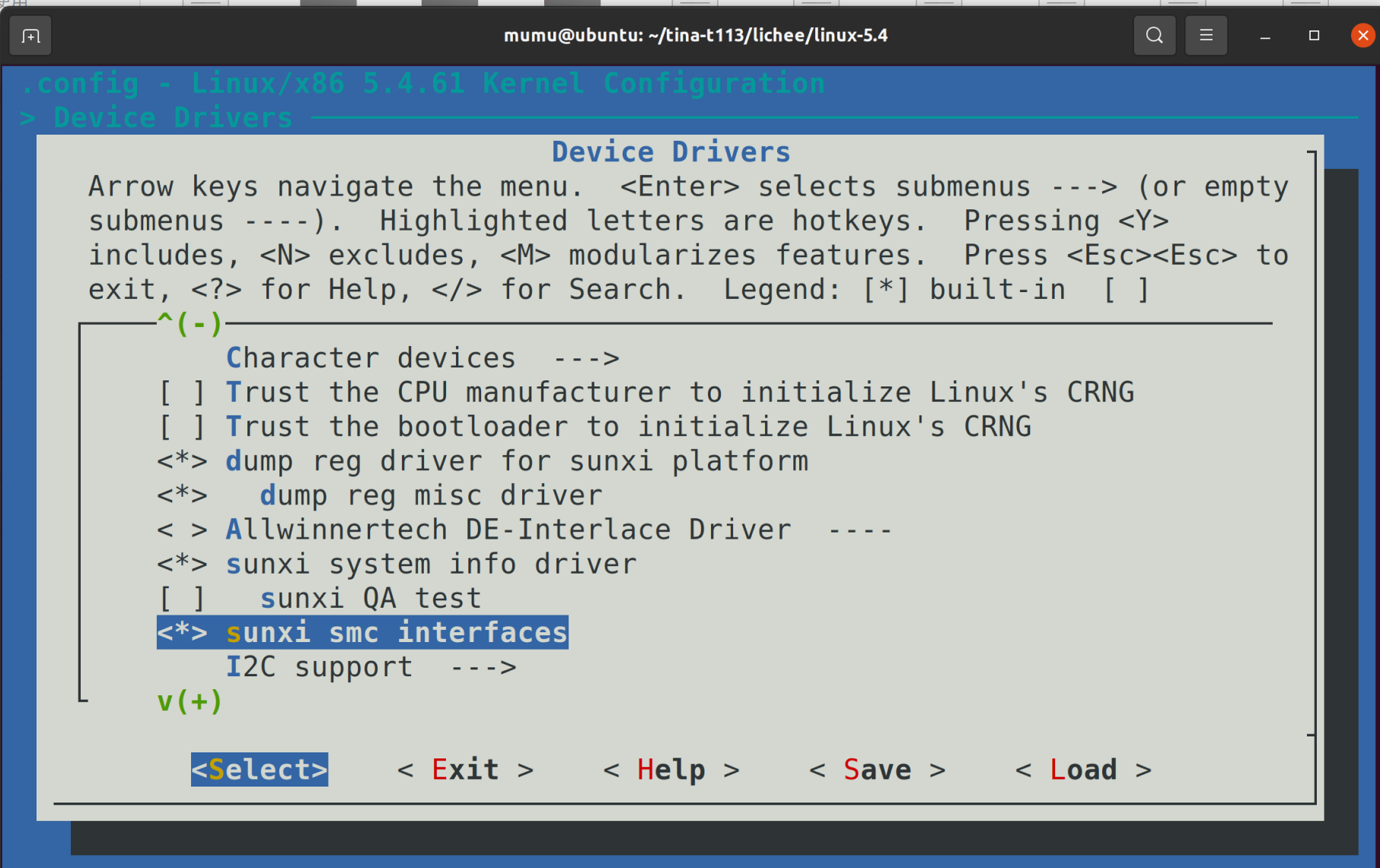

我咨询过fae,说要用make menuconfig ARCH=arm去打开,但是我打开之后报了一堆错误

请问你这个是用哪个defconfig配置出来的

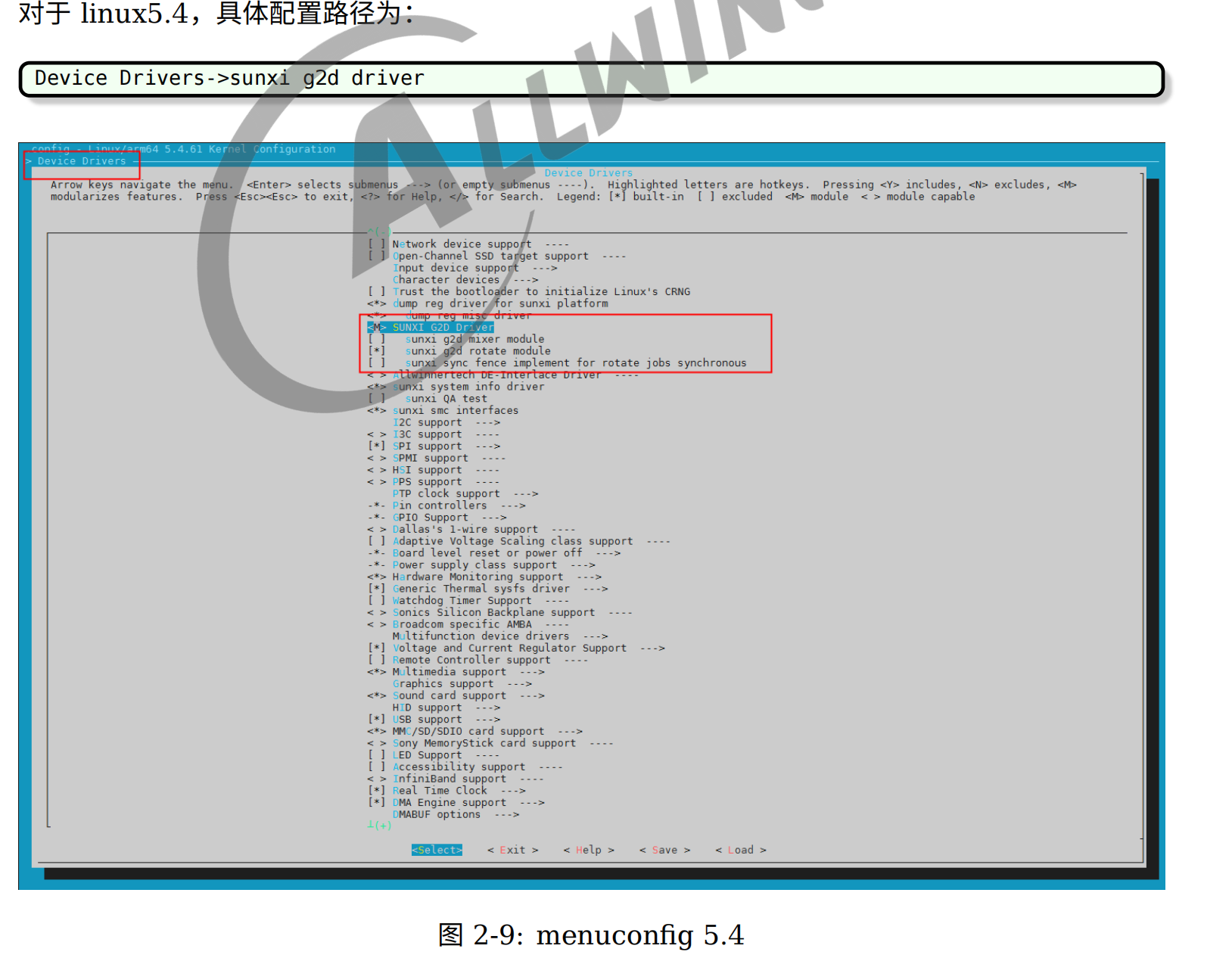

按照说明书操作想打开这个选项开启旋转功能,在make menuconfig之后却发现没有这个选项

到底该怎么样才可以打开?

说明书上写着打开这个就可以,

t113的g2d旋转功能可以在uboot启用吗,因为液晶屏是竖屏,但是ui是横屏,kernel阶段是可以设置g2d硬件旋转的,uboot阶段有这个功能吗

@yuzukitsuru 你这个是不是这个bl没有去操作啊

lcd_bl_en = <&pio PE 12 GPIO_ACTIVE_HIGH>;

我在调试mipi的时候发现这个定义好像是离开uboot进入kernel之后才去操作拉高的,在uboot阶段你跟rst一样,去操作bl口子应该就好了吧

@whycan 谢谢晕哥,我今天测试了下好像是vmware虚拟机的bug,每次copy到win10下面基本上都是上次的老文件,我在linux下面用共享文件夹用cp命令复制到文件夹好像就好了

@whycan 就算生产在其他地方,但是我最后用pack命令生成的tina_t113-mq_uart0.img这个文件也没有变化,所以很烦躁,不知道哪次更改有效,我刚刚为了改一个mipi驱动,muboot,pack指令不知道做了多少次,每次生成的文件都没有任何变化还是修改前的,后来不知道怎么弄了下又成功生成了一次,然后后面又不行了

@whycan 谢谢晕哥回复,比如我打个比方,我修改了uboot下面的de_dsi.c文件,然后我在uboot根目录下make了一下,我发现生成了新的de_dsi.o文件,这个文件的确是会变化的,每次只要我修改文件,然后make就会变,但是最后生成的u-boot.bin确没有任何变化,

同时我查看u-boot.map也是变化了,这个到底为什么会这样

使用的是t113的tina-linux 执行完毕 source./build/envsetup.sh之后有很多编译命令

比如muboot,但是我在uboot源目录修改了代码之后,执行muboot发现生成的u-boot.bin还是没有发生变化,然后我进入到uboot根目录,在根目录下面执行make也是一样没有变化,后来不知道怎么弄了下,又发现更新进去了,测试了好多次,完全没有任何规律,我现在想问的是,这个自己修改了uboot的部分源代码,或者dts文件,应该执行什么命令才可以重新生成新的u-boot.bin文件,然后进一步pack打包成img文件

还有想问一下,在调试过程中,是不是每次都需要生成img,然后用卡刷软件写入sd卡,然后再插入板子才能运行,这样效率太低了,能不能用dd命令把uboot这部分刷进去,如果可以,应该刷到哪个地址?

@yuzukitsuru 有d1s点屏的测试固件吗,能否发我这里测量一下时钟,我手头有d1s的板子

@yuzukitsuru 我下载了一个tina-linux编译 rgb下面显示正常,当然rgb下面还是有那个bug,,然后我还原原来的设置,再把mipi移植进去,发现还是一个鸟样,后面就没时钟了,查看我现在怀疑是不是mipi的中断没开,因为在uboot下面打印disp出来的irq这里一直是0

=> disp

screen 0:

de_rate 300000000 hz, ref_fps:59

mgr0: 720x1280 fmt[rgb] cs[0x204] range[full] eotf[0x4] bits[8bits] err[1] force_sync[0] unblank direct_show[false] iommu[0]

lcd output backlight(100) fps:25.5 720x1280

err:0 skip:0 irq:0 vsync:0 vsync_skip:0

BUF enable ch[1] lyr[0] z[0] prem[N] a[globl 255] fmt[ 0] fb[ 720,1280; 0, 0; 0, 0] crop[ 0, 0, 720,1280] frame[ 0, 0, 720,1280] addr[46acc000, 0, 0] flags[0x 0] trd[0,0]

=>

这里四我用读取mipi的id指令获取的lcd的id返回数据四正确的

/* init code for lcd */

tick_printf("lcd_panel_init dsi_dcs_write=%x\n", 0x29);

sunxi_lcd_dsi_dcs_write_0para(sel, 0x29);

sunxi_lcd_delay_ms(100);

sunxi_lcd_dsi_dcs_write_0para(sel, 0x11);

sunxi_lcd_delay_ms(100);

u8 result[17] = { 0 };

u32 num = 0;

sunxi_lcd_delay_ms(100);

sunxi_lcd_dsi_dcs_read(sel, 0x04, result, &num);

printf("get lcd id0 0x%x get lcd id15 0x%x get lcd id16 0x%x readbytes=%d\n",

result[0], result[15], result[16], num);

打印结果如下

lcd_panel_init dsi_dcs_write=29

get lcd id0 0x41 get lcd id15 0xff get lcd id16 0x0 readbytes=16

为什么没有时钟了呢,崩溃了,研究了好几天了没有任何进展,打印了datasheet里面所有和dsi有关的时钟寄存器,里面都是对的,但是dsi的时钟算出来只有408M/4 这个和理论上的对不上

@yuzukitsuru 你这里有f133测试成功的mipi吗,我手头只有f133和t113 ,没有d1,没办法测试d1

@yuzukitsuru 我问了fae 他们要我把板子寄过去,但是我分析了一下,应该是sdk哪个地方某个时钟有问题,因为rgb驱动的时候用800x480 他们的代码是有bug的,帧率设置到60帧,实际上有82帧,这个地方我改正了,但是mipi没有资料公开,没办法下手

@yuzukitsuru 是全志发我的sdk 应该是longan 主文件夹名字是 auto-t113-linux

用T113S3驱动mipi屏幕,高速video模式下面没有时钟和数据输出

在低速命令阶段,

sunxi_lcd_dsi_dcs_read(sel, 0x04, result, &num);用这个04指令可以读取到lcd的id

说明连线应该都是没问题的,用示波器和逻辑分析仪测量发送接收数据完全正确

但是在这个之后,进入高速video模式之后,mipi的时钟和数据脚就再也没有输出了,这个是哪里有问题啊,全志的sdk是不是哪里有问题啊,在测试rgb的时候也发现了一个bug,自己修正了,现在mipi这里卡住了好几天了,

@yuzukitsuru 我2台电脑和一台手机都打不开,打开就左上角显示一个 EN

我点击EN也没用任何反应,

@yuzukitsuru 我按照你的ruboot,但是生成的uboot.img根本就不会变化还是第一次make之后的,不管我修改什么都不会改变,到底是哪里有问题,完全不懂buildroot,唉,真难啊

@yuzukitsuru 那为什么我修改了board mangopi 下面的dts 然后make之后生成的sdimage还是未修改之前的

@yuzukitsuru 请问如果我需要修改自己的dts文件,应该修改哪个?因为我看到output build目录下面有个uboot2018的目录,这个目录下面也有原来tina sdk的dts,应该修改哪个?哪个覆盖哪个?

用的t113的sdk编译出来的uboot,自己修改了设备树,之前用的800x480的lcd在uboot下面已经用colorbar指令测试成功了,然后想测试手头的mipi屏幕,结果出现了个问题

用disp指令显示,我配置的刷新率应该是59帧,实际只有25.5帧,colorbar测试失败,但是用mipi指令可以获取到屏幕的id值,说明mipi其实已经跑起来了,可能是时钟哪里配置不对,没有修改uboot源码,只是修改了设备树,按照mipi初始化指令增加了屏幕的指令,这个屏幕不需要额外的初始化指令,只需要一个0x29和0x11指令就可以显示的

uboot打印的logo如下

U-Boot 2018.05-g2a24076-dirty (May 13 2022 - 21:35:03 +0800) Allwinner Technology

[03.349].................................set debug mode=8[03.354]CPU: Allwinner Family

[03.357]Model: sun8iw20

[03.359]DRAM: 128 MiB

[03.362]Relocation Offset is: 04f36000

[03.380]secure enable bit: 0

[03.383]CPU=1008 MHz,PLL6=600 Mhz,AHB=200 Mhz, APB1=100Mhz MBus=300Mhz

[03.389]gic: normal mode

[03.391]flash init start0

[03.393]workmode = 0,storage type = 3

spi sunxi_slave->max_hz:120000000

SF: Detected w25q128 with page size 256 Bytes, erase size 64 KiB, total 16 MiB

[03.409]sunxi flash init ok

[03.412]sunxi_flash_probe ok

[03.415]sunxi_flash_probe ok1

[03.417]line:703 init_clocks

[03.420]init_clocks:finish

[03.422]drv_disp_init

[03.430]get flash lcd idx 0

request pwm success, pwm7:pwm7:0x2000c00.

fdt get node offset faill: hdmi

[03.441]HDMI 2.0 driver init start!

[03.444]fdt_path_offset hdmi fail

[03.447]unable to map hdmi registers

[03.450]drv_disp_init finish

[03.453]boot_gui_init:start

[03.456]set disp.dev2_output_type fail. using defval=0

[03.461]lcd_open_flow=0

[03.463]lcd_clk_config--------------------------------

[03.468]-------------disp_al_lcd_get_clk_info

[03.472]DSI_VERSION_40

[03.474]DSI_VERSION_40 lcd_dsi_format=0

[03.477]tcon_div=4 lcd_div=1 dsi_div=6 dsi_rate=150000000

[03.482]lcd_rate=408000000 pll_rate=408000000 tcon_div=4

[03.488]pll_rate_set=408000000

[03.490]2222222222

[03.492]disp 0, clk: pll(408000000),clk(408000000),dclk(68000000) dsi_rate(150000000)

clk real:pll(408000000),clk(408000000),dclk(102000000) dsi_rate(150000000)

[03.507]DSI_VERSION_40

[03.509]DSI_VERSION_40 lcd_dsi_format=0

[03.512]tcon_div=4 lcd_div=1 dsi_div=6 dsi_rate=150000000

[03.518]lcd_open_flow=0

[03.851]switch device: sel=0, type=1, mode=4, format=0, bits=0, eotf=4, cs=260

[03.858]boot_gui_init:finish

GUID P[03.861]lcd_open_flow=0

[03.873]lcd_panel_init dsi_dcs_write=29

get lcd id0 0x41 get lcd id15 0xff get lcd id16 0x0 readbytes=16

artition Table Header signature is wrong: 0xE07060200000000 != 0x5452415020494645

part_get_info_efi: *** ERROR: In[04.192]lcd_open_flow=0

valid GPT ***

ERROR: attempting read past flash size

*** ERROR: Can't read GPT header ***

part_get_info_efi: *** ERROR: Invalid Backup GPT ***

partno erro : can't find partition bootloader

GUID Partition Table Header signature is wrong: 0xE07060200000000 != 0x5452415020494645

part_get_info_efi: *** ERROR: Invalid GPT ***

ERROR: attempting read past flash size

*** ERROR: Can't read GPT header ***

part_get_info_efi: *** ERROR: Invalid Backup GPT ***

partno erro : can't find partition boot-resource

[04.238]Get bootloader and boot-resource partition number fail[04.244]lcd_open_flow=0

[04.247]lcd_open_flow=0

[04.249]lcd_open_flow=0

[04.251]LCD open finish

!

GUID Partition Table Header signature is wrong: 0xE07060200000000 != 0x5452415020494645

part_get_info_efi: *** ERROR: Invalid GPT ***

ERROR: attempting read past flash size

*** ERROR: Can't read GPT header ***

part_get_info_efi: *** ERROR: Invalid Backup GPT ***

[04.277]Loading Environment from SUNXI_FLASH... GUID Partition Table Header signature is wrong: 0xE07060200000000 != 0x5452415020494645

part_get_info_efi: *** ERROR: Invalid GPT ***

ERROR: attempting read past flash size

*** ERROR: Can't read GPT header ***

part_get_info_efi: *** ERROR: Invalid Backup GPT ***

*** Warning - no device, using default environment

Failed (-19)

GUID Partition Table Header signature is wrong: 0xE07060200000000 != 0x5452415020494645

part_get_info_efi: *** ERROR: Invalid GPT ***

ERROR: attempting read past flash size

*** ERROR: Can't read GPT header ***

part_get_info_efi: *** ERROR: Invalid Backup GPT ***

[04.334]update part info

[04.336]key 0

GUID Partition Table Header signature is wrong: 0xE07060200000000 != 0x5452415020494645

part_get_info_efi: *** ERROR: Invalid GPT ***

ERROR: attempting read past flash size

*** ERROR: Can't read GPT header ***

part_get_info_efi: *** ERROR: Invalid Backup GPT ***

[04.361]no misc partition is found

[04.364]update bootcmd

GUID Partition Table Header signature is wrong: 0xE07060200000000 != 0x5452415020494645

part_get_info_efi: *** ERROR: Invalid GPT ***

ERROR: attempting read past flash size

*** ERROR: Can't read GPT header ***

part_get_info_efi: *** ERROR: Invalid Backup GPT ***

GUID Partition Table Header signature is wrong: 0xE07060200000000 != 0x5452415020494645

part_get_info_efi: *** ERROR: Invalid GPT ***

ERROR: attempting read past flash size

*** ERROR: Can't read GPT header ***

part_get_info_efi: *** ERROR: Invalid Backup GPT ***

[04.412]libfdt fdt_check_header(): FDT_ERR_BADMAGIC

[04.417]replace_fdt fail addr:0x43200000

disable nand error: FDT_ERR_NOTFOUND

[04.424](weak)update dtb dram start

[04.428]## error: update_fdt_dram_para : FDT_ERR_NOTFOUND

[04.434]update dts

Hit any key to stop autoboot: 0

## Error: "distro_bootcmd" not defined

=> disp

screen 0:

de_rate 300000000 hz, ref_fps:59

mgr0: 720x1280 fmt[rgb] cs[0x204] range[full] eotf[0x4] bits[8bits] err[1] force_sync[0] unblank direct_show[false] iommu[0]

lcd output backlight(100) fps:25.5 720x1280

err:0 skip:0 irq:0 vsync:0 vsync_skip:0

=>

希望有经验的朋友能不能帮我分析一下,是不是哪里时钟配置出错了

uboot的dts文件如下

/*

* Allwinner Technology CO., Ltd. sun8iw20p1 soc board.

*

* soc board support.

*/

/dts-v1/;

#include "sun8iw20p1-soc-system.dtsi"

&platform {

eraseflag = <1>;

next_work = <3>;

debug_mode = <1>;

};

&target {

boot_clock = <1008>; /*CPU boot frequency, Unit: MHz*/

storage_type = <0xffffffff>; /*boot medium, 0-nand, 1-card0, 2-card2, -1(defualt)auto scan*/

burn_key = <0>; /*1:support burn key; 0:not support burn key*/

dragonboard_test = <0>; /*1:support card boot dragonboard; 0:not support card boot dragonboard*/

};

&charger0 {

pmu_safe_vol = <3500>;

};

&twi6 {

clock-frequency = <200000>;

pinctrl-0 = <&s_twi0_pins_a>;

no_suspend = <1>;

twi_drv_used = <1>;

status = "okay";

};

&pwm7_pin_a {

pins = "PD22";

function = "pwm7";

muxsel = <5>;

drive-strength = <10>;

bias-pull-up;

};

&pwm7_pin_b {

pins = "PD22";

muxsel = <0>;

function = "gpio_out";

};

&pwm7 {

pinctrl-names = "active", "sleep";

pinctrl-0 = <&pwm7_pin_a>;

pinctrl-1 = <&pwm7_pin_b>;

status = "okay";

};

&sdc0_pins_a {

allwinner,pins = "PF0", "PF1", "PF2",

"PF3", "PF4", "PF5";

allwinner,function = "sdc0";

allwinner,muxsel = <2>;

allwinner,drive = <3>;

allwinner,pull = <1>;

pins = "PF0", "PF1", "PF2",

"PF3", "PF4", "PF5";

function = "sdc0";

drive-strength = <30>;

bias-pull-up;

power-source = <3300>;

};

&sdc0_pins_b {

pins = "PF0", "PF1", "PF2",

"PF3", "PF4", "PF5";

function = "sdc0";

drive-strength = <30>;

bias-pull-up;

power-source = <1800>;

};

&sdc0_pins_c {

pins = "PF0", "PF1", "PF2",

"PF3", "PF4", "PF5";

function = "gpio_in";

};

&sdc2_pins_a {

allwinner,pins = "PC2", "PC3", "PC4",

"PC5", "PC6", "PC7";

allwinner,function = "sdc2";

allwinner,muxsel = <3>;

allwinner,drive = <3>;

allwinner,pull = <1>;

pins = "PC2", "PC3", "PC4",

"PC5", "PC6", "PC7";

function = "sdc2";

drive-strength = <30>;

bias-pull-up;

};

&sdc2_pins_b {

pins = "PC2", "PC3", "PC4",

"PC5", "PC6", "PC7";

function = "gpio_in";

};

&nand0_pins_a {

allwinner,pins = "PC0", "PC1", "PC2", "PC5",

"PC8", "PC9", "PC10", "PC11",

"PC12", "PC13", "PC14", "PC15",

"PC16";

allwinner,pname= "nand0_we", "nand0_ale","nand0_cle", "nand0_nre",

"nand0_d0", "nand0_d1", "nand0_d2", "nand0_d3",

"nand0_d4", "nand0_d5", "nand0_d6", "nand0_d7",

"nand0_ndqs";

allwinner,function = "nand0";

allwinner,muxsel = <2>;

allwinner,drive = <1>;

allwinner,pull = <0>;

};

&nand0_pins_b {

allwinner,pins = "PC4", "PC6", "PC03", "PC07";

allwinner,pname= "nand0_ce0", "nand0_rb0", "nand0_ce1", "nand0_rb1";

allwinner,function = "nand0";

allwinner,muxsel = <2>;

allwinner,drive = <1>;

allwinner,pull = <1>; /* only RB&CE should be pulled up */

};

&nand0_pins_c {

allwinner,pins = "PC0", "PC1", "PC2", "PC3",

"PC4", "PC5", "PC6", "PC7",

"PC8", "PC9", "PC10", "PC11",

"PC12", "PC13", "PC14", "PC15",

"PC16";

allwinner,function = "io_disabled";

allwinner,muxsel = <7>;

allwinner,drive = <1>;

allwinner,pull = <0>;

};

&spi0_pins_a {

allwinner,pins = "PC2", "PC4", "PC5";

allwinner,pname = "spi0_sclk", "spi0_mosi", "spi0_miso";

allwinner,function = "spi0";

allwinner,muxsel = <2>;

allwinner,drive = <1>;

allwinner,pull = <0>;

};

&spi0_pins_b {

allwinner,pins = "PC3", "PC7", "PC6";

allwinner,pname = "spi0_cs0", "spi0_hold", "spi0_wp";

allwinner,function = "spi0";

allwinner,muxsel = <2>;

allwinner,drive = <1>;

allwinner,pull = <1>; // only CS should be pulled up

};

&spi0_pins_c {

allwinner,pins = "PC2", "PC3", "PC4", "PC5",

"PC6", "PC7";

allwinner,function = "gpio_in";

allwinner,muxsel = <0>;

allwinner,drive = <1>;

allwinner,pull = <0>;

};

&card0_boot_para { /* Avoid dtc compiling warnings. @TODO: Developer should modify this to the actual value */

/* reg = <0x0 0x2 0x0 0x0>; [> Avoid dtc compiling warnings. @TODO: Developer should modify this to the actual value <] */

device_type = "card0_boot_para";

card_ctrl = <0x0>;

card_high_speed = <0x1>;

card_line = <0x4>;

pinctrl-0 = <&sdc0_pins_a>;

};

&card2_boot_para { /* Avoid dtc compiling warnings. @TODO: Developer should modify this to the actual value */

/* reg = <0x0 0x3 0x0 0x0>; [> Avoid dtc compiling warnings. @TODO: Developer should modify this to the actual value <] */

device_type = "card2_boot_para";

card_ctrl = <0x2>;

card_high_speed = <0x1>;

card_line = <0x4>;

pinctrl-0 = <&sdc2_pins_a>;

sdc_ex_dly_used = <0x2>;

sdc_io_1v8 = <0x1>;

sdc_tm4_win_th = <0x08>;

sdc_tm4_hs200_max_freq = <150>;

sdc_tm4_hs400_max_freq = <100>;

sdc_type = "tm4";

};

&gpio_bias { /* Avoid dtc compiling warnings. @TODO: Developer should modify this to the actual value */

device_type = "gpio_bias";

pc_bias = <1800>;

};

&nand0 {

compatible = "allwinner,sun8iw20-nand";

device_type = "nand0";

//reg = <0x0 0x04011000 0x0 0x1000>;/* nand0 */

pinctrl-names = "default", "sleep";

pinctrl-0 = <&nand0_pins_a &nand0_pins_b>;

pinctrl-1 = <&nand0_pins_c>;

nand0_regulator1 = "vcc-nand";

nand0_regulator2 = "none";

nand0_cache_level = <0x55aaaa55>;

nand0_flush_cache_num = <0x55aaaa55>;

nand0_capacity_level = <0x55aaaa55>;

nand0_id_number_ctl = <0x55aaaa55>;

nand0_print_level = <0x55aaaa55>;

nand0_p0 = <0x55aaaa55>;

nand0_p1 = <0x55aaaa55>;

nand0_p2 = <0x55aaaa55>;

nand0_p3 = <0x55aaaa55>;

chip_code = "sun8iw20";

status = "disabled";

};

&spi0 {

clock-frequency = <100000000>;

pinctrl-0 = <&spi0_pins_a &spi0_pins_b>;

pinctrl-1 = <&spi0_pins_c>;

pinctrl-names = "default", "sleep";

/*spi-supply = <®_dcdc1>;*/

spi_slave_mode = <0>;

spi0_cs_number = <1>;

spi0_cs_bitmap = <1>;

status = "okay";

spi-nand@0 {

compatible = "spi-nand";

spi-max-frequency=<0x5F5E100>;

reg = <0x0>;

spi-rx-bus-width=<0x04>;

spi-tx-bus-width=<0x04>;

status="okay";

};

};

&disp {

disp_init_enable = <1>;

disp_mode = <0>;

screen0_output_type = <1>;

screen0_output_mode = <4>;

screen1_output_type = <3>;

screen1_output_mode = <10>;

screen1_output_format = <0>;

screen1_output_bits = <0>;

screen1_output_eotf = <4>;

screen1_output_cs = <257>;

screen1_output_range = <2>;

screen1_output_scan = <0>;

screen1_output_aspect_ratio = <8>;

dev0_output_type = <1>;

dev0_output_mode = <4>;

dev0_screen_id = <0>;

dev0_do_hpd = <0>;

dev1_output_type = <4>;

dev1_output_mode = <10>;

dev1_screen_id = <1>;

dev1_do_hpd = <1>;

def_output_dev = <0>;

fb0_format = <0>;

fb0_width = <0>;

fb0_height = <0>;

fb1_format = <0>;

fb1_width = <0>;

fb1_height = <0>;

chn_cfg_mode = <1>;

disp_para_zone = <1>;

/*VCC-LCD*/

/* dc1sw-supply = <®_dc1sw>;*/

/*VCC-DSI*/

/* eldo3-supply = <®_eldo3>;*/

/*VCC-PD*/

/* dcdc1-supply = <®_dcdc1>;*/

};

/*800x480 tft*/

/*

&lcd0 {

lcd_used = <1>;

lcd_driver_name = "default_lcd";

lcd_backlight = <100>;

lcd_if = <0>;

lcd_x = <800>;

lcd_y = <480>;

lcd_width = <150>;

lcd_height = <94>;

lcd_dclk_freq = <36>;

lcd_hv_clk_phase = <0>;

lcd_hv_sync_polarity= <3>;

lcd_pwm_used = <1>;

lcd_pwm_ch = <7>;

lcd_pwm_freq = <20000>;

lcd_pwm_pol = <0>;

lcd_hbp = <46>;

lcd_ht = <1055>;

lcd_hspw = <0>;

lcd_vbp = <23>;

lcd_vt = <525>;

lcd_vspw = <0>;

lcd_lvds_if = <0>;

lcd_lvds_colordepth = <1>;

lcd_lvds_mode = <0>;

lcd_frm = <1>;

lcd_io_phase = <0x0000>;

lcd_gamma_en = <0>;

lcd_bright_curve_en = <0>;

lcd_cmap_en = <0>;

pinctrl-0 = <&rgb18_pins_a>;

pinctrl-1 = <&rgb18_pins_b>;

};

&aliases {

nand0 = &nand0;

twi6 = &twi6;

pwm = &pwm;

pwm0 = &pwm0;

pwm1 = &pwm1;

pwm2 = &pwm2;

pwm3 = &pwm3;

pwm4 = &pwm4;

pwm5 = &pwm5;

pwm6 = &pwm6;

pwm7 = &pwm7;

disp = &disp;

lcd0 = &lcd0;

lcd1 = &lcd1;

eink = &eink;

spi0 = &spi0;

};

*/

&lcd0 {

/* part 1 */

lcd_used = <1>;

lcd_driver_name = "lq055k3sx02";

/* part 2 */

lcd_if = <4>;

lcd_dsi_if = <0>;

/* part 3 */

lcd_x = <720>;

lcd_y = <1280>;

lcd_width = <135>;

lcd_height = <216>;

lcd_dclk_freq = <68>;

lcd_hbp = <40>;

lcd_ht = <870>;

lcd_hspw = <10>;

lcd_vbp = <11>;

lcd_vt = <1305>;

lcd_vspw = <1>;

/* part 4 */

lcd_backlight = <100>;

lcd_pwm_used = <1>;

lcd_pwm_ch = <7>;

lcd_pwm_freq = <20000>;

lcd_pwm_pol = <0>;

lcd_pwm_max_limit = <100>;

//lcd_bl_en = <&pio PD 22 1 0 3 1>;//pwm7 pd22

lcd_bright_curve_en = <0>;

/* part 5 */

lcd_dsi_lane = <4>;

lcd_dsi_format = <0>;

lcd_dsi_te = <0>;

/* part 6 */

lcd_frm = <0>;

lcd_gamma_en = <0>;

lcd_cmap_en = <0>;

/* part 7 */

//lcd_pin_power = "dcdc1";

//lcd_pin_power1 = "eldo3";

//lcd_power = "dc1sw";

lcd_gpio_0 = <&pio PG 10 1 0 3 1>;//rst(PG10)

lcd_gpio_1 = <&pio PG 13 1 0 3 1>;// led(PG13)

pinctrl-0 = <&dsi4lane_pins_a>;

pinctrl-1 = <&dsi4lane_pins_b>;

};

&aliases {

nand0 = &nand0;

twi6 = &twi6;

pwm = &pwm;

pwm0 = &pwm0;

pwm1 = &pwm1;

pwm2 = &pwm2;

pwm3 = &pwm3;

pwm4 = &pwm4;

pwm5 = &pwm5;

pwm6 = &pwm6;

pwm7 = &pwm7;

disp = &disp;

lcd0 = &lcd0;

lcd1 = &lcd1;

eink = &eink;

spi0 = &spi0;

};

T113S3的sdk里面执行命令 make sun8iw20p1_nor_defconfig

make sun8iw20p1_nor_defconfig文件里面没有定义CONFIG_CONS_INDEX

为什么make xxdefconfig命令之后.config里面有个CONFIG_CONS_INDEX=1

这个默认值是在哪里定义的

之所以有这个疑问是因为我搜不到有关默认值的赋值在哪个文件,知道的朋友可以提示一下吗

xfel烧录到t113的0x20000sram失败是怎么回事

xfel sid

83007000ac144814010008215cca11cb

MuMu@DESKTOP-EOMBNKD C:\Work\myWork\T113\uboot\tools

xfel read 0x20000 30000 sram.bin

100% [================================================] 29.297 KB, 774.006 KB/s

MuMu@DESKTOP-EOMBNKD C:\Work\myWork\T113\uboot\tools

xfel read 0x20000 30000 sram.bin

100% [================================================] 29.297 KB, 747.179 KB/s

MuMu@DESKTOP-EOMBNKD C:\Work\myWork\T113\uboot\tools

xfel version

AWUSBFEX ID=0x00185900(R528/T113) dflag=0x44 dlength=0x08 scratchpad=0x00045000

MuMu@DESKTOP-EOMBNKD C:\Work\myWork\T113\uboot\tools

xfel sid

83007000ac144814010008215cca11cb

MuMu@DESKTOP-EOMBNKD C:\Work\myWork\T113\uboot\tools

xfel write 0x20000 boot0_sdcard.bin

usb bulk send error

MuMu@DESKTOP-EOMBNKD C:\Work\myWork\T113\uboot\tools

用sunxi-fel也是一样的问题

write 0x20000 boot0_sdcard.bin

Warning: no 'soc_sram_info' data for your SoC (id=1859)

usb_bulk_send() ERROR -7: Operation timed out

@whycan 为什么d1s编译出来的uboot有spl t113编译出来的uboot没有spl,我现在对spl和uboot一片模糊,主要是对全志的一堆工具完全不知道哪里有资料可以查到

全志的打包工具,什么卡刷工具,到底是怎么个打包法,目前只想研究一下uboot里面t113的dsi代码想移植到rtt里面来用,因为dsi部分没有资料,只有uboot里面有相关代码,所有只想跑一下uboot来验证dsi代码, uboot是由spl来启动的,那如果用fxel是不是就可以跳过spl直接来启动uboot,如果是,那么应该加载到ddr哪个地址是ddr的起始地址0x40000000还是其他的,那么spl又是个什么鬼,是不是用了fexl就不需要spl了,这个spl是不是在裸机上电的时候代替xfel完成ddr初始化,并且跳转到ddr跑uboot, 为什么我编译出来的的t113uboot只有没有uboot-spl.bin这样的文件, 为什么spl文件夹下面编译的只有sdboot0和nandboot0 ,没有norboot0

手头有t113的sdk 但是这是想先研究下boot0和uboot,用t113的sdk编译出来的uboot没有带spl,而且都是烧录到nand或者sd卡,现在想用xfel工具烧录到ddr或者nor来测试,到底该怎么操作啊,为什么有的uboot带spl,有的uboot又不带spl,boot0也就是spl不是应该运行在sram里面吗,那么uboot应该运行在ddr,那么是不是可以用xfel把uboot部分加载到ddr然后运行?那么带spl的uboot到底又是啥 如果用xfel烧录带spl的uboot,那么又应该烧录到哪里,完全迷糊了,不知道是不是自己能力有限,开始怀疑自己适不适合linux开发了,连个uboot都搞不定,好烦躁

@whycan bootrom的固化代码是不是会自动读取spi nor 0地址的数据和sd卡8k位置的数据

@whycan 谢谢回复,我捋一下, 是不是把uboot烧录到sd卡的8k位置,brom就会自动读取8k位置的代码,那么这个8k位置的代码需要加入spl+uboot这样的结合还是不需要spl,只要uboot就行

@whycan 请问我如果独立编译出来了uboot,应该烧录到sd卡哪个位置才可以启动

或者能不能烧录到spi nor的某个地址启动

下载了t113的sdk编译,在uboot编译里面有提到boot0 fes sboot这些名词,到底是什么啊

我现在单独编译uboot,要烧录到哪里才可以运行,可以烧录到sd卡吗,sd卡的什么地址,

或者可以烧录到nor flash 0地址吗,uboot必须配合spl吗,我都迷糊了,到底咋弄啊

@aozima 大神能讲解一下smp方面的rtt问题吗,我现在只开启了一个定时器,然后rtconfig里面定义了RT_USING_SMP,然后跑gui发现非常丝滑,

我把RT_USING_SMP这个定义关闭了在跑gui发现非常卡了

然后我想着不是还有一个定时器没有开启吗,我就在void secondary_cpu_c_start(void)

{

int timer_irq_number;

timer_irq_number = 92;

rt_hw_vector_init();

rt_hw_spin_lock(&_cpus_lock);

arm_gic_cpu_init(0, platform_get_gic_cpu_base());

// arm_gic_set_cpu(0, timer_irq_number, 0x2); // timer1

// timer1_init();

//rt_hw_interrupt_install(timer_irq_number, rt_hw_timer1_isr, RT_NULL, "tick1");

//rt_hw_interrupt_umask(timer_irq_number);

rt_system_scheduler_start();

}

这里把定时器2也开启了,现在发现之前开启的那个定时器1中断不进去了,进去的都是定时器2的中断,gui的任务夜跑不起来了,也就是说我在second cpu里面在开启一个定时器就不正常了,找了资料说smp需要开启2个定时器,为什么我这里开启2个定时器之后,前面那个定时器中断进不去了呢,然后我把second cpu的定时器关闭,性能上也达到了双核的提升了呀,因为我如果禁止smp,那么性能比较差的明显的,我现在迷糊了,定时器到底要不要开启2个,能否讲解一下这方面的疑惑,非常感谢

@randolph 谢谢大家提供的数据,我实际测试下来发现t113s3优势非常大,我来跑rtt+awtk t113s3开启smp模式可以丝滑跑120帧,但是f133只能跑60帧,而且60帧还不稳定,不知道是riscv64的开发环境刚出来没优化好还是其他问题,

@yuzukitsuru 又随手跑了一下 Dhrystones

dhrystone_test

Dhrystone Benchmark, Version 2.1 (Language: C)

Program compiled without 'register' attribute

Execution starts, 32000000 runs through Dhrystone

[2022-04-19 11:07:53.418]# RECV ASCII>

Execution ends

Final values of the variables used in the benchmark:

Int_Glob: 5

should be: 5

Bool_Glob: 1

should be: 1

Ch_1_Glob: A

should be: A

Ch_2_Glob: B

should be: B

Arr_1_Glob[8]: 7

should be: 7

Arr_2_Glob[8][7]: 32000010

should be: Number_Of_Runs + 10

Ptr_Glob->

Ptr_Comp: 1073951700

should be: (implementation-dependent)

Discr: 0

should be: 0

Enum_Comp: 2

should be: 2

Int_Comp: 17

should be: 17

Str_Comp: DHRYSTONE PROGRAM, SOME STRING

should be: DHRYSTONE PROGRAM, SOME STRING

Next_Ptr_Glob->

Ptr_Comp: 1073951700

should be: (implementation-dependent), same as above

Discr: 0

should be: 0

Enum_Comp: 1

should be: 1

Int_Comp: 18

should be: 18

Str_Comp: DHRYSTONE

[2022-04-19 11:07:53.538]# RECV ASCII>

PROGRAM, SOME STRING

should be: DHRYSTONE PROGRAM, SOME STRING

Int_1_Loc: 5

should be: 5

Int_2_Loc: 13

should be: 13

Int_3_Loc: 7

should be: 7

Enum_Loc: 1

should be: 1

Str_1_Loc: DHRYSTONE PROGRAM, 1'ST STRING

should be: DHRYSTONE PROGRAM, 1'ST STRING

Str_2_Loc: DHRYSTONE PROGRAM, 2'ND STRING

should be: DHRYSTONE PROGRAM, 2'ND STRING

Microseconds for one run through Dhrystone: 0

Dhrystones per Second: 4484933

VAX MIPS rating: 2552

msh />

因为一直在纠结用f133还是t113,在两者之间徘徊,所以才想测试一下性能,以便决定以后用哪个

@yuzukitsuru 请问你这个是f133的分数吗 或者是d1或者d1s吗,这个core-Mark在linux下和rtthread下面跑分是不是不一样啊,我优化了一下代码下载可以跑到4170了

2K performance run parameters for coremark.

CoreMark Size : 666

Total ticks : 11990

Total time (secs): 11.990000

Iterations/Sec : 4170.141785

Iterations : 50000

Compiler version : GCC6.3.1 20170215 (release) [ARM/embedded-6-branch revision 245512]

Compiler flags :

Memory location : STACK

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0xa14c

Correct operation validated. See README.md for run and reporting rules.

CoreMark 1.0 : 4170.141785 / GCC6.3.1 20170215 (release) [ARM/embedded-6-branch revision 245512] / STACK

msh />

@aozima 我已经开启了cpu1的心跳,

cpu2的心跳不开启的话cpu2不能参与任务调度吗,但是我用rt_thread_control(tid, RT_THREAD_CTRL_BIND_CPU, (void *)1);这个绑定cpu是可以正常调度的呀

@aozima 怎么同时跑两份啊,我用的是你移植的rtt,smp部分不太懂,启动第二个核心的时候那个时钟tick要不要开启啊,你那边的代码里面注释掉了定时器,

2K performance run parameters for coremark.

CoreMark Size : 666

Total ticks : 12751

Total time (secs): 12

Iterations/Sec : 4166

Iterations : 50000

Compiler version : GCC6.3.1 20170215 (release) [ARM/embedded-6-branch revision 245512]

Compiler flags :

Memory location : STACK

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0xa14c

Correct operation validated. See README.md for run and reporting rules.

CoreMark 1.0 : 4166 / GCC6.3.1 20170215 (release) [ARM/embedded-6-branch revision 245512] / STACK

另外我想问一下,我使用smp和不使用,跑分是一样的,这个smp到底是怎么用的啊,是不是没啥用,在rtt里面建立任务的时候会自动分配cpu还是需要人为去指定

或者能不能一个任务两个核一起来用,

另外在附上memory_perf的分数

MemoryPerf version 1.0.0

Copyright (c) 2022 SummerGift (summergift2019@gmail.com)

Licensed under the MIT License version.

Memory performance testing start...

address: 0x40100000, length: 0x100000, iterations: 200

Data length : 209 MB.

--------------------------------------

8-bit write speed test begin.

[2022-04-18 15:41:26.787]# RECV ASCII>

Spend time : 0.223000 s.

8-bit write speed: 940.426880 M/s.

8-bit read speed test begin.

[2022-04-18 15:41:27.346]# RECV ASCII>

Spend time : 0.559000 s.

8-bit Read speed: 375.161346 M/s.

--------------------------------------

16-bit write speed test begin.

[2022-04-18 15:41:27.472]# RECV ASCII>

Spend time : 0.111000 s.

16-bit write speed: 1889.326050 M/s.

16-bit read speed test begin.

[2022-04-18 15:41:27.802]# RECV ASCII>

Spend time : 0.328000 s.

16-bit Read speed: 639.375610 M/s.

--------------------------------------

32-bit write speed test begin.

[2022-04-18 15:41:27.896]# RECV ASCII>

Spend time : 0.091000 s.

32-bit Write speed: 2304.562744 M/s.

32-bit read speed test begin.

[2022-04-18 15:41:28.067]# RECV ASCII>

Spend time : 0.160000 s.

32-bit Read speed: 1310.719971 M/s.

Memory performance completed.

有没有大神拿其他片子来对比一下,这个a7到底什么水平啊

Unhandled Exception 2:Illegal Instruction

mcause:0x0000000000000002,mtval:0x0000000030009073,mepc:0x00000000401685d4

--------------Dump Registers-----------------

Function Registers:

ra(x1) = 0x00000000402ead80()

)

gp(x3) = 0x0000000000000000()

tp(x4) = 0x0000000000000000()

Temporary Registers:

t0(x5) = 0x0000000000000000()

t1(x6) = 0x0000000000000000()

t2(x7) = 0x0000000000000000()

t3(x28) = 0x00000000402eac50()

t4(x29) = 0x00000000402eac50()

t5(x30) = 0x00000000402eac60()

t6(x31) = 0x00000000402eac60()

Saved Registers:

s0/fp(x8) = 0x0000000000000000()

s1(x9) = 0x0000000000000000()

s2(x18) = 0x00000000402eabf8()

s3(x19) = 0x0000000000ff0001()

s4(x20) = 0x0000000000000000()

s5(x21) = 0x0000000000000000()

s6(x22) = 0x00000000402eac20()

s7(x23) = 0x00000000402eac20()

s8(x24) = 0x00000000402eac30()

s9(x25) = 0x00000000402eac30()

s10(x26) = 0x00000000402eac40()

s11(x27) = 0x00000000402eac40()

Function Argu

[2022-03-25 20:08:13.327]# RECV ASCII>

ments Registers:

a0(x10) = 0x0000000000000000()

a1(x11) = 0x00000000402f6ec8()

a2(x12) = 0x0000000070616568()

a3(x13) = 0x0000000000000000()

a4(x14) = 0x0000018300000000()

a5(x15) = 0x00000000402a8380()

a6(x16) = 0x00000000402e62e8()

a7(x17) = 0x00000000402eabf8()

sstatus = 0x0000000a00000000

Supervisor Interrupt Disabled

Last Time Supervisor Interrupt Disabled

Last Privilege is User Mode

Not Permit to Access User Page

Not Permit to Read Executable-only Page

satp = 0x0000000000000000

Mode = No Address Translation/Protection Mode

-----------------Dump OK---------------------

定位到代码是下面这条语句

401685c2: 3002b073 csrc mstatus,t0

401685c6: 6291 lui t0,0x4

401685c8: 3002a073 csrs mstatus,t0

401685cc: 6082 ld ra,0(sp)

401685ce: 34109073 csrw mepc,ra

401685d2: 60c2 ld ra,16(sp)

401685d4: 30009073 csrw mstatus,ra

定位到源代码是这里的

.macro SAVE_ALL

#ifdef ENABLE_FPU

/* save float registers /

addi sp, sp, -CTX_FPU_REG_NR * REGBYTES

#endif / ENABLE_FPU */

/* save general registers */

addi sp, sp, -CTX_GENERAL_REG_NR * REGBYTES //save 33 reg

STORE x1, 1 * REGBYTES(sp) //x1 ra

csrr x1, mstatus

STORE x1, 2 * REGBYTES(sp)

csrr x1, mepc

STORE x1, 0 * REGBYTES(sp)

@randolph

谢谢,内核没有开源的话的确不太方便用,烧录程序,开机启动时间都不好控制,那么好的d1s不拿来跑rtos真的好浪费啊

@yuzukitsuru 请问有rtthread或者freertos吗 因为想跑awtk这个gui 没有研究过melis不知道支不支持awtk

哪位兄弟有用f133使用rtos的,我找了两个兄弟移植的rtos都会运行一段时间宕机

https://github.com/bigmagic123/d1-nezha-rtthread这个是有个兄弟提供的rtthread 我测试的时候发现经常性的宕机,一直找不到问题,

还找到一个freertos也是运行几分钟就宕机的,有没有能正常用的rtos啊,f133用rtos非常合适啊...难道大家都跑linux?

https://bbs.aw-ol.com/topic/231/freertos-10-4-3在riscv-t-head-c906-平台上移植过程?_=1635232850765

有没有可以用的rtos移植啊