@awwwwa 您说的bsp驱动是指全志官方提供的裸机bsp驱动还是说从uboot里找啊?

Z

ZM960406 发布的帖子

-

t113-s3 SMHC模块的校准延时链是个什么技术啊?怎么使用呢?发布在 T Series

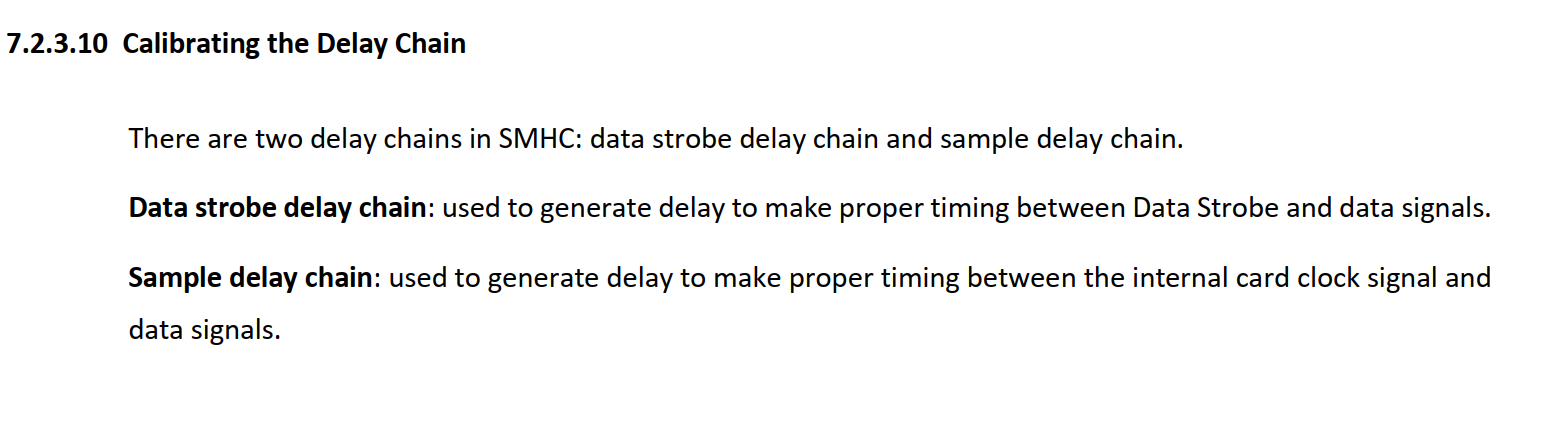

移植好了t113s3 freertos,最近想逐步完善外设驱动,目前正在开发SMHC的驱动,读芯片手册时发现了下面这个内容

,看描述这个延时链技术似乎是用来校准选通信号和数据信号之间的延时,以及时钟信号和数据信号之间的延时的,根据编程指导,我写了一段代码

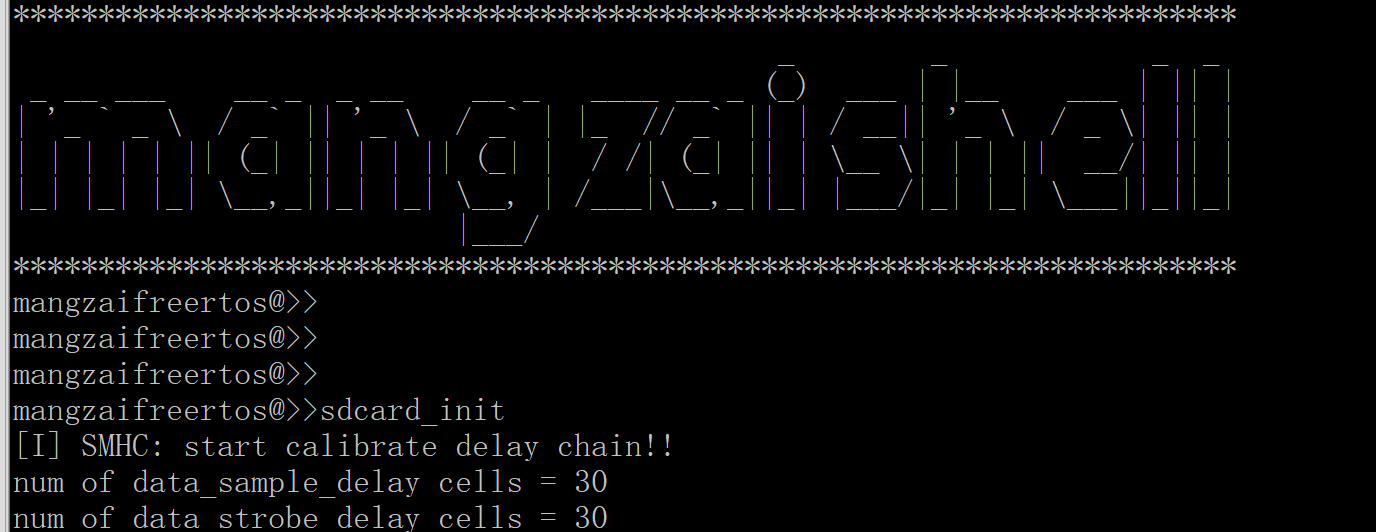

,看描述这个延时链技术似乎是用来校准选通信号和数据信号之间的延时,以及时钟信号和数据信号之间的延时的,根据编程指导,我写了一段代码//校准延时链 info("SMHC: start calibrate delay chain!!\r\n"); init_environment_calibrate_delay(); calibrate_data_sample_delay(&sdhci0); calibrate_data_strobe_delay(&sdhci0); deinit_environment_calibrate_delay();

获取到了两种延时链的delay cells num,分别都是30,SMHC clk = 200MHZ,那得到这些数据之后,如何使用它们呢,非常好奇,有大佬能解释下吗? -

回复: T113 DMA 测试在开启mmu后,测试失败发布在 其它全志芯片讨论区

解决了,awboot中对dma设备寄存器的操作很多情况下都是先在内存中创建一个全局变量,给全局变量赋值后,再将赋值内容传给设备寄存器的地址处,虽然设备地址都被设为no cache了,但全局变量是cacheable的,而未初始化或初始化为0的全局变量都是放在.bss段的,所以.bss段需要设为no cache

base = ((uint32_t)__bss_start__ ) & (~0xFFFFF); end = ((uint32_t)__bss_end__ ); n = (end - base) >> 20; for (i = 0; i < n; i++) //dev { MMU_ConfigSection((uint32_t *)__mmu_start, (const void *)(base + (i << 20)), (base + (i << 20)), &s_mmudmaAttr); }完美解决,测试成功,开了mmu后,基本达到了400Mbit/s的DMA传输速度

[I] ------BootLoader Jump Successed----------- [D] welcome to T113s3 [D] CLK: CPU PLL=PLL_CPU FREQ=1200MHz [D] CLK: PLL_peri (2X)=1200MHz, (1X)=600MHz, (800M)=800MHz [D] CLK: PLL_ddr=1584MHz [D] DMA: init [T] DMA: test 0x42000000 ====> 0x42800000, len 512KB [T] DMA: provide channel 0 [D] DMA: test OK in 20ms [D] timer0 irq is enable [D] i am task0 [D] i am task2