PLIC在写入complete寄存器后立马会触发下一次中断

-

如题所示

按照文档说明,PLIC的处理过程应该是在CPU收到外中断后读取claim/complete 寄存器,取出中断号,随后处理中断,再向claim/complete 寄存器写入完成处理的中断号。

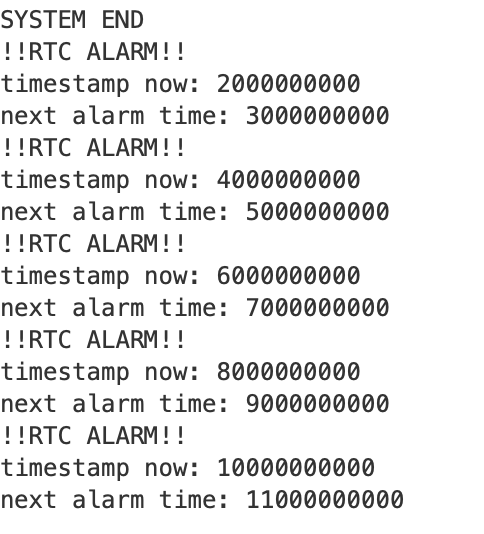

现在我发现在从claim/complete 寄存器读出中断号后对应的pending位已经为0(正常),但将处理完成的中断号写入claim/complete 寄存器后对应中断的pending位会立刻变为1,随后PLIC发出外中断,进入了下一轮中断处理程序,虽然在这之中,外中断源并未真正发出中断信号。我主要测试了UART与RTC,在QEMU中一切正常,使用D1所对应的驱动在D1上跑则会出如上问题。另:此系统为裸机程序,没有使用任何其他内核

代码链接如下:

plic.c

plic.h

sunxi-rtc.c

rtc.h

trap.c另:我发现D1的user manual中关于PLIC的部分寄存器位描述有许多错误,且和C906的文档不一致,倒是和F133的一致,不知是不是全志的小编抄错了

-

@ytf4425 还有哪些写错了?求大佬指出

(这个问题我们先看下) -

@ytf4425 我就知道 硬件肯定没有问题

-

@xiaowenge 还有224页底部链接的问题。其他的部分我也只看了RTC,那里没有问题

-

破案了,alarm0_irq_sta_reg=0不行,要用alarm0_irq_sta_reg=1,alarm0_irq_sta_reg寄存器是W1C,一开始不知道这是啥意思,以为是可写,去查了一下才知道是写1来清零。

问题解决了一个,但是又有一个来了,alarm不按设定的时间发生中断,总是要晚一秒

-

@ytf4425 这个问题也解决了,看起来是因为rtc是在从x秒跳到x+1秒的那一刹那才会触发设置在x秒的闹钟

-

@xiaowenge

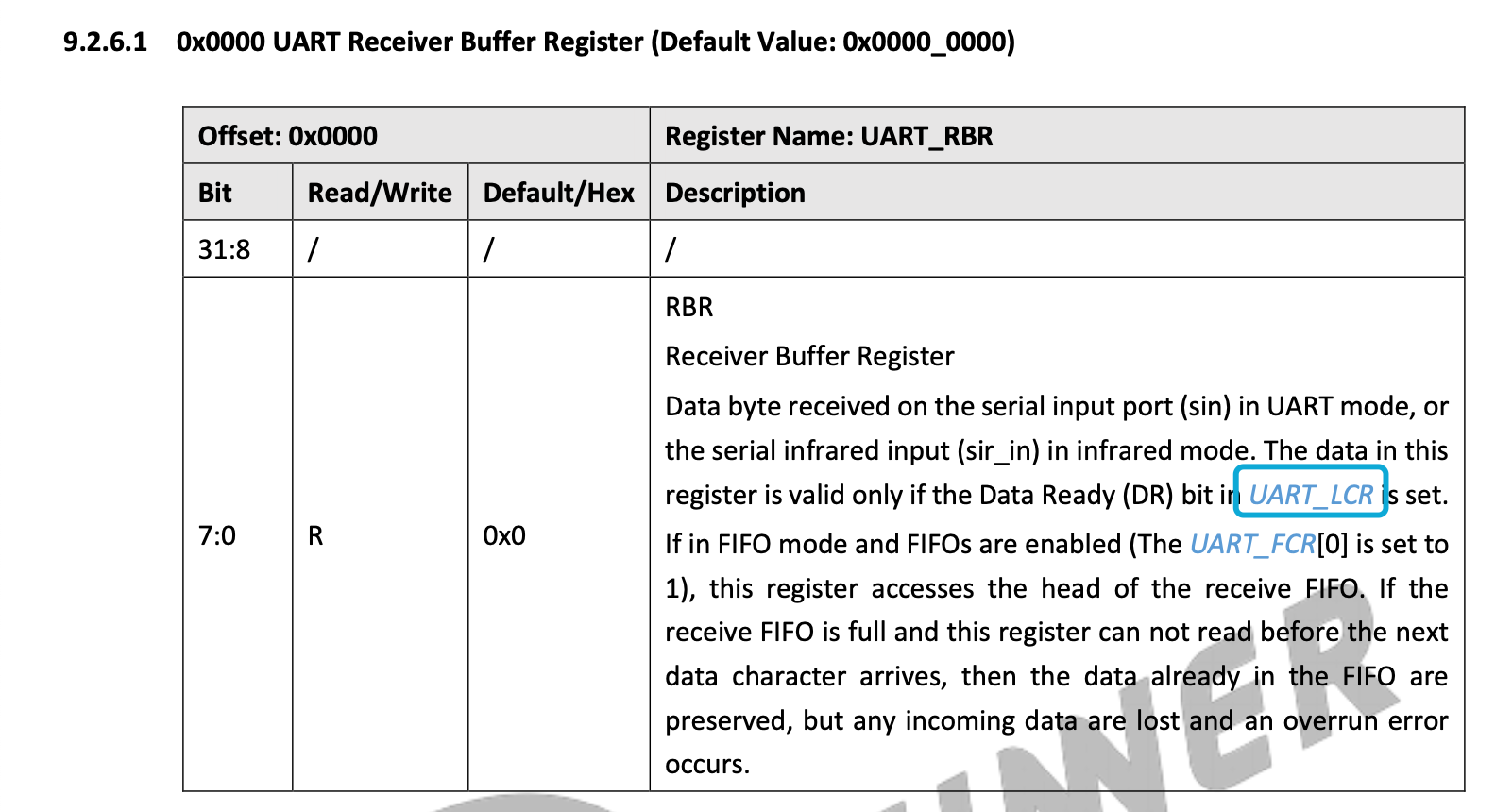

P899 此处应为LSR

Copyright © 2024 深圳全志在线有限公司 粤ICP备2021084185号 粤公网安备44030502007680号