求证:riscv的计算与访存无法并行吗?

-

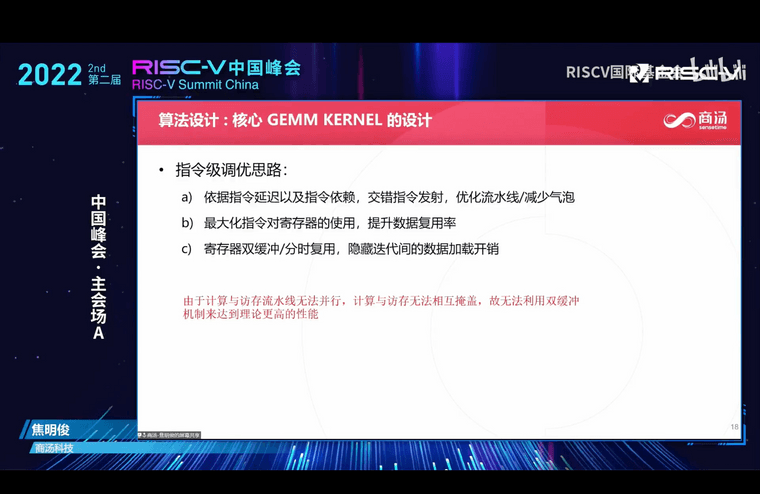

如图,D1上的riscv的计算与访存流水线无法并存?这个结论是怎么得到的呢?

-

访存有专门的Load/Store指令,这样计算的指令都是直接基于寄存器的,更加简单些。

-

@aozima 那计算和访存流水线是串行的对吗?

-

@zhaodongyu 逻辑上看起来是的,实际上有预取,write buffer等特性存在,所以在计算时,访存已提前进行,或上条还未完成,不会等的。

-

@aozima 多谢解答,另外想再问一下,计算和访存不能并行,这个意思是计算和访存不能双发射,但是他们有各自的流水线对吧?

-

@zhaodongyu

感觉它这里针对的是GEMM KERNEL加速核的设计而言的,PPT标题已经给出来了。对经典的CPU流水线来讲,计算阶段和访问阶段已经流水化了,由不同的硬件(ALU/BIU)完成,本身是可以做到并行的。而用计算来掩盖访存延迟一般是HPC计算加速器的做法,因为这种KERNEL 加速器不像CPU有丰富的L1/L2/L3缓存可以用,CPU访存延迟低。计算加速器只能通过大量计算掩盖访存延迟。所以我感觉它这里讲的可能不是RISC-V的特性,而是GEMM阵列的特性。

Copyright © 2024 深圳全志在线有限公司 粤ICP备2021084185号 粤公网安备44030502007680号