LT527X-E 米尔 T527 开发板折腾记录

-

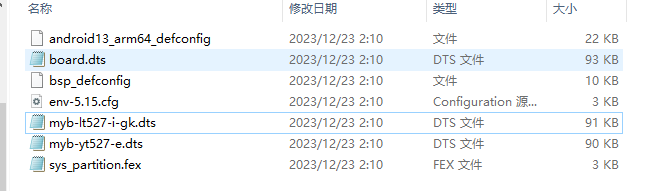

下载SDK之后能看到三份设备树