t113-s3 RMII 网卡IP101GR不识别

-

问题现象:

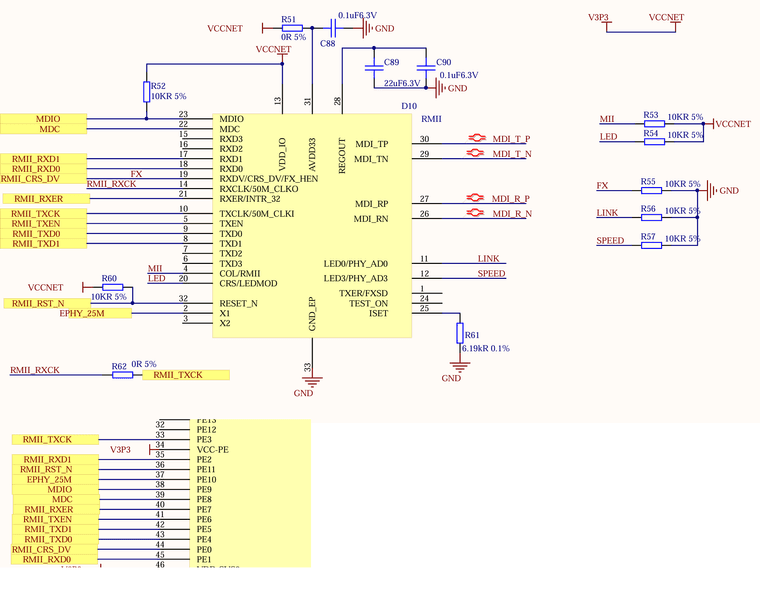

PHY芯片用的IP101GR,kernel已经根据手册把phy 驱动icplus等都添加了。不知道是不是硬件有问题,量了PE10(ephy_25M)没有时钟信号。gmac_pins_a: gmac@0 { pins = "PE0", "PE1", "PE2", "PE3", "PE4", "PE5", "PE6", "PE7", "PE8", "PE9"; function = "gmac0"; drive-strength = <10>; }; gmac_pins_b: gmac@1 { pins = "PE0", "PE1", "PE2", "PE3", "PE4", "PE5", "PE6", "PE7", "PE8", "PE9"; function = "gpio_in"; }; &gmac0 { phy-mode = "rmii"; use_ephy25m = <1>; pinctrl-0 = <&gmac_pins_a>; pinctrl-1 = <&gmac_pins_b>; pinctrl-names = "default", "sleep"; phy-rst = <&pio PE 11 GPIO_ACTIVE_LOW>; /*tx-delay = <3>; /*2~4*/ /*rx-delay = <0>;*/ status = "okay"; };打印输出和网卡相关的只有这些:

[ 0.858513] libphy: Fixed MDIO Bus: probed [ 0.863954] sun8iw20-pinctrl 2000000.pinctrl: 2000000.pinctrl supply vcc-pe not found, using dummy regulator [ 0.875201] sunxi gmac driver's version: 1.0.0 [ 0.880315] gmac-power0: NULL [ 0.883664] gmac-power1: NULL [ 0.886967] gmac-power2: NULL [ 0.891018] ehci_hcd: USB 2.0 'Enhaifconfig -a是有 eth0的

ifconfig eth0 up

[ 34.543389] libphy: 4500000.eth: probed [ 34.547686] sunxi-gmac 4500000.eth eth0: No PHY found! [ 34.703390] libphy: 4500000.eth: probed [ 34.707685] sunxi-gmac 4500000.eth eth0: No PHY found! [ 34.716027] sunxi-gmac 4500000.eth eth0: phy init failed原理图(与V853一致)

https://v853.docs.aw-ol.com/hard/hard_3boardsch/ -

这个是PHY没有找到,PHY的供电、地址是配置正确吗,确保RMII几个时钟要有的,用是的哪个SDK,是否需要在驱动里配置PHY ID ?

-

可以调一下drive-strength看看,之前RMII遇到过能识别phy没法通信

-

@fanhuacloud 好的,试试

-

@radxiaohe 供电没有问题,phy_id 配置的0, LED3/PHY_AD3..都是低电平

-

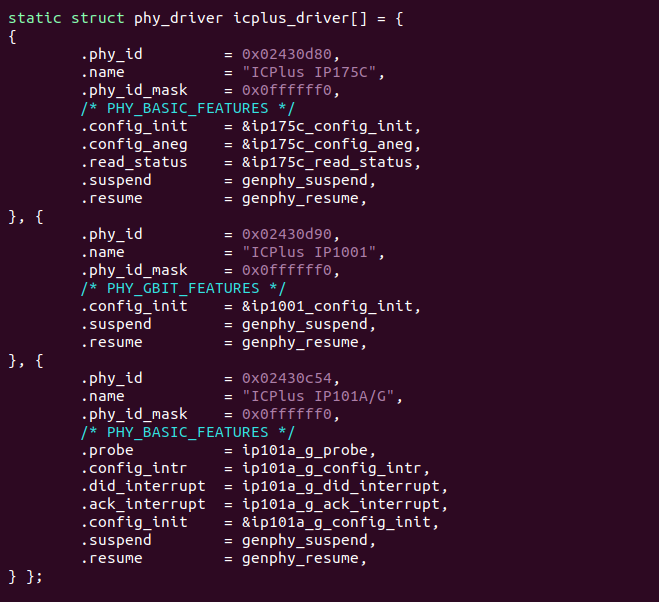

这个是原理图,kernel phy驱动icplus已经配置了,/drivers/net/phy/icplus.c中有phy identify了,跟ip101gr手册上对了一致的

,该从哪个地方开始查呢

,该从哪个地方开始查呢 -

@radxiaohe sdk用的tina和 论坛“T113 Tina SDK、Longan SDK、开发资料下载”里面的都试过了

-

@yubeer 在 t113-s3 RMII 网卡IP101GR不识别 中说:

这个是原理图,kernel phy驱动icplus已经配置了,/drivers/net/phy/icplus.c中有phy identify了,跟ip101gr手册上对了一致的

,该从哪个地方开始查呢

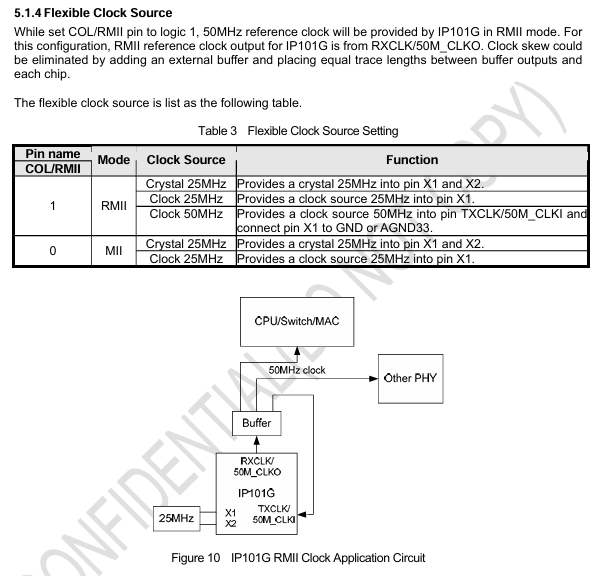

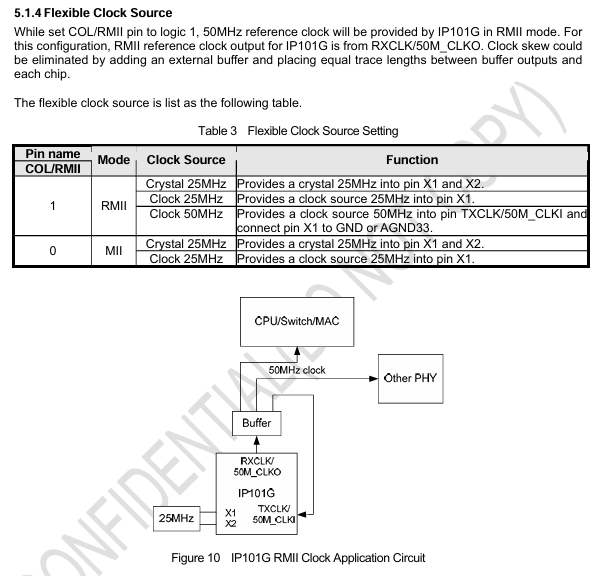

,该从哪个地方开始查呢我记得RMII对于百兆网而言应该是使用50MHz(由PHY输出,以太网MAC控制器输入),一般主芯片不输出时钟,由PHY输出时钟。IP101GR的X1、X2应该是接25M晶振的(如果只接一个脚应该是有源晶振),PHY的50MHz时钟(RXCLK/50M_CLKO)可能应该接在主芯片的某一个引脚上(极有可能是PE10,因为按标准应该PHY与主芯片之间应该是50MHz的频率)。

-

@heyahong 没错,X1-X2是需要提供25MH在时钟源的,看了IP101GR的手册,25MHz时钟可以有外部晶振提供,也可以由外部时钟源提供连接X1,另外PHY50MHz时钟在RMII模式,可以由IP101内部提供。图应该没问题啊~

datasheet page-44

Reduced Media Independent Interface (RMII) is defined to provide a fewer pins data transmission

condition. The management interface, MDC and MDIO, are identical to the MII defined in IEEE 802.3.

RMII supports 10/100Mb data rates and the clock source are provided by a single 50MHz clock from

either external or within IP101G.

-

@yubeer 在 t113-s3 RMII 网卡IP101GR不识别 中说:

@heyahong 没错,X1-X2是需要提供25MH在时钟源的,看了IP101GR的手册,25MHz时钟可以有外部晶振提供,也可以由外部时钟源提供连接X1,另外PHY50MHz时钟在RMII模式,可以由IP101内部提供。图应该没问题啊~

datasheet page-44

Reduced Media Independent Interface (RMII) is defined to provide a fewer pins data transmission

condition. The management interface, MDC and MDIO, are identical to the MII defined in IEEE 802.3.

RMII supports 10/100Mb data rates and the clock source are provided by a single 50MHz clock from

either external or within IP101G.

看图中的箭头方向,图中不正好说明CPU不产生时钟(接受时钟输入),X1-X2应该装无源晶振,只用X1应该装有源晶振而不是连在CPU上。

-

@heyahong 是的,打算飞一个晶振试试

-

@yubeer

1 测一下TXCK的波形,硬件正常时这里有正常波形

2 确保硬件连接无误后,在驱动代码中,将RMII_RST_N对应的GIO先拉高,等200ms以上,再拉低试试,T517上就是这么调通的。 -

把这个寄存器dump出来看下配置对不对 -

@yubeer 请问解决了吗?

-

@yubeer 我用tina时能驱动IP101GR,是由T113PG11口提供的时钟。但是在主线6.6.x下就没法动态获取IP

-

这个配置咋配置呀我现在也是这样的现象,博主解决了没求解答

-

Moved from MR Series by

xiaowenge

xiaowenge

-

@admin5 这个解决了吗?我现在也卡住了

-

@yubeer 楼主解决了这个网口的问题吗?我现在也卡住这个地方了,不知道咋设置,

Copyright © 2024 深圳全志在线有限公司 粤ICP备2021084185号 粤公网安备44030502007680号