为什么不能解决制造问题的人?

aozima 发布的帖子

-

回复: t113-s3 tplayerdemo循环播放视频中,突然断电后,视频文件损坏发布在 T Series

播放是只读操作,检查是否哪里有误,在进行写操作。

如果确实没有写也会坏,那就是EMMC的问题了,可以尝试换个型号对比。 -

回复: 双核t8100笔记本4G真机UBUNTU18.4编译内核error: Illegal instruction发布在 MR Series

CPU要支持avx指令,是时候奖励自己1台新电脑了。

$ cat /proc/cpuinfo | grep avx -

回复: 求证:riscv的计算与访存无法并行吗?发布在 MR Series

@zhaodongyu 逻辑上看起来是的,实际上有预取,write buffer等特性存在,所以在计算时,访存已提前进行,或上条还未完成,不会等的。

-

回复: 100s 的tina 定时器精度只能到10ms,现在需要用gpio来模拟nec协议的红外发送,大家有什么好的建议吗?发布在 Linux

只需要模拟那个毫秒级的信号就行了吧,38K载波应该用PWM来实现。

-

回复: D1s-RTT2022纪念版应用分享发布在 MR Series

每个独立的elf文件体积都很大,你看只有一句话的hello.elf,体积有34K,还不如20年前的VC6.0

应该strip一下就小了

-

回复: 选型需求有款设备,需要音频,1000m以太网,usb,要linux操作系统。 现在全志满足这些要求的,哪款芯片最便宜?发布在 MR Series

好奇问下 要传递啥数据?必须要1000m以太网?

-

回复: 请教大佬,有没有开源支持D1s SPINor RTOS系统的boot引导程序,可以直接跑RTOS系统那种!!!发布在 MR Series

难不成D1s和F133的ddr参数不同?

有空找2个对比下看看

-

回复: T113-S3 RT-Thread SMP适配笔记发布在 其它全志芯片讨论区

@lijinfeng xfel把JTAG打开,应该就可以连接得上了吧,你试试。

最近在研究一个核心跑 RT-Thread,另外一个核跑 linux 。

AMP通信配合工作 -

回复: 哪吒开发板如何使用向量指令发布在 MR Series

https://whycan.com/t_7592.html

探索麻雀D1s上的RVV

关键点在于设置VS标志位

VS位于MSTATUS寄存器的23到24位。但是需要注意的是,当使用RVV时,需要开启浮点寄存器(FS),不然会报错。 -

回复: 调MIPI屏,同样的二进制程序,D1-H可以,D1S就不出信号,麻烦帮看下。发布在 MR Series

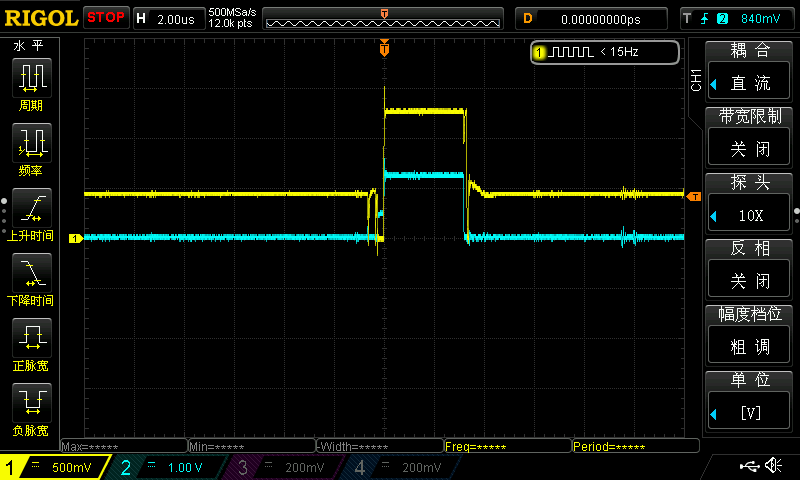

问题最后定位出来:

lcd_dclk_freq用30就可以,用31 32 33都不行。不明觉厉!

-

回复: 调MIPI屏,同样的二进制程序,D1-H可以,D1S就不出信号,麻烦帮看下。发布在 MR Series

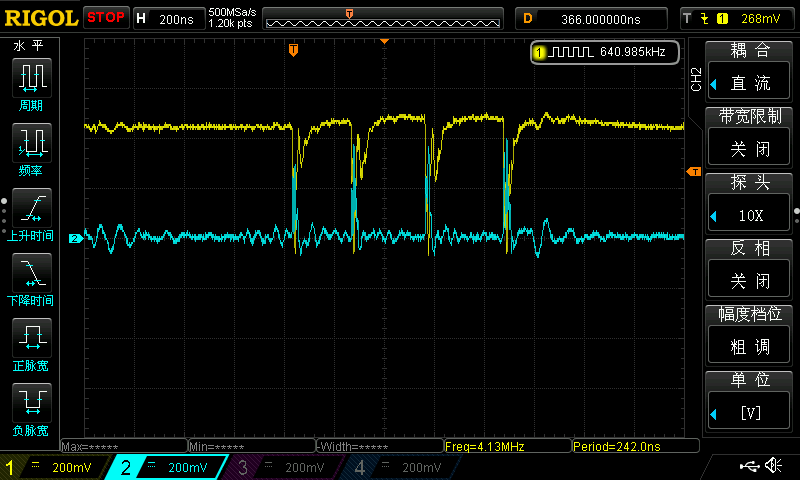

问题更新

经交叉对比发现,时钟信号不正常的原因,并不是因为D1-H和D1S的原因。

而是因为配置的MIPI屏参的问题。现在D1S上面,使用D1-H的TFT08006的参数,也可以正常出波形。

但D1S目前使用的参数,是从 https://bbs.aw-ol.com/topic/808 这里来的,这参数本身看起来也是没问题的。 -

调MIPI屏,同样的二进制程序,D1-H可以,D1S就不出信号,麻烦帮看下。发布在 MR Series

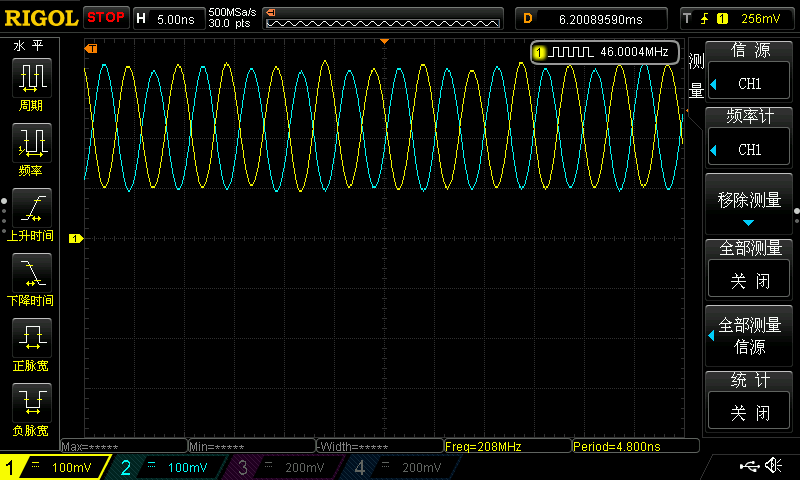

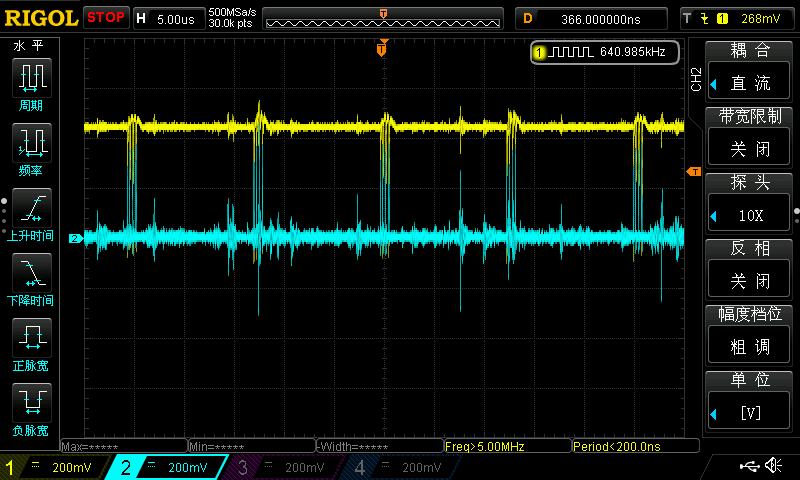

我们基于melis代码,在移植柿饼UI,RGB屏之前调通了,这次准备点MIPI屏,结果D1S配好参数好,没有点亮,用示波器测量MIPI-DSI的差分时钟输出,发现是乱的。为了对比找问题,我们把同样的二进制程序下载到D1-H上面跑,差分时钟输出就很完美。

此时2个芯片的程序,在二进制上已是相同的,他们的所用的LCD输出IO也是相同的,所以实在想不到还有不同,请大佬们帮分析下可能会是哪里的差异造成?

D1-H正常时钟信号

D1S异常时钟信号

-

回复: T113-S3 ARM 及 DSP Benchmark发布在 其它全志芯片讨论区

目前hifi dsp采用的自编译的gcc编译器

这个赞!

dsp的gcc可以拿来玩吗?只有基本指令还是有部分DSP指令?

-

回复: 谁跑过D1a的core_mark分数吗,我这里有T113的跑分,想来对比下发布在 MR Series

@smiletiger 没心跳只是与时间相关的不正常,主动让出不受影响。

建议把cpu1的心跳也开起来吧,期待! -

回复: 谁跑过D1a的core_mark分数吗,我这里有T113的跑分,想来对比下发布在 MR Series

@smiletiger 注意下,那个移植里面,不光第2核的心跳没启动,0核的心跳也没启动呢。

-

回复: 谁跑过D1a的core_mark分数吗,我这里有T113的跑分,想来对比下发布在 MR Series

@smiletiger 你要测性能的话要开启的,我那个代码是从qemu那边复制过来的,要重新适配T113才行,你可以试试加上心跳。

-

回复: 谁跑过D1a的core_mark分数吗,我这里有T113的跑分,想来对比下发布在 MR Series

rtt里面建立任务的时候会自动分配cpu还是需要人为去指定

或者能不能一个任务两个核一起来用,默认会自动分配吧,也可以绑定。你这跑分,可以改下代码,同时跑2份core_mark看看部分。

-

回复: T113-S3 RT-Thread SMP适配笔记发布在 其它全志芯片讨论区

@a937983423 那就不清楚了,看提示,应该和代码本身无关的。

你换个目录看看,是否本地目录权限什么的。或linux编译下。 -

回复: 请教T113-S3调试IP101GRI,不能发送的问题。发布在 其它全志芯片讨论区

@suitjune 我过阵子也需要在F133上面使用百兆以太网,手上没有参考原理图。

想问下你的RMII 50M时钟是谁提供的?F133/T113有50M输出吗?

你用的是哪组IO?我打算使用PGx这组。

PG11 EPHY-25M 这个IO作用是啥? -

回复: 请教T113-S3调试IP101GRI,不能发送的问题。发布在 其它全志芯片讨论区

@suitjune 自动协商也可以不走MDIO的,因为大部分PHY上电默认就是自动协商模式。

你的loopback要分清是emac内部的,还是PHY里面的。

emac里面的,不接PHY都能回环的。

要用PHY里面的才行。收发都有计数器都不是0

PHY里面的收发都不是0了?再尝试通信下是否会涨?如果会,那你就要怀疑你的PC这边了。你是直边PC还是用了交换机?

-

回复: 请教T113-S3调试IP101GRI,不能发送的问题。发布在 其它全志芯片讨论区

网线那边有协商的,应该收发都通的。

那么,RMII这边的TX也许有焊接问题?看看PHY里面有没有收发包计数器?或在PHY里面开一下loopback模式测试确认下。 -

T113-S3 RT-Thread SMP适配笔记发布在 其它全志芯片讨论区

T113-S3 SMP适配笔记

目标

给T113-S3适配RT-Thread,并支持SMP。

资料

没有太详细的资料和示例,只有一些零星的信息。

- F133封装基本兼容

- Cortex-A7双核

一些参考资料

计划

- 最好能直接使用xfel在SRAM,或是DDR中运行,避免从SD卡启动还需要SPL。

- 先用xfel payload跑通, 最好能有串口打印。

- 再尝试直接load到ddr运行。

- 尝试在DDR中运行rt-thread

- 尝试响应中断

- 尝试支持SPL

过程

环境准备

- 开发板 芒果派

- 下载工具 xfel

先连接好开发板,默认没卡也没有FLASH,会自动进入USB FEL。

通过xfel可以探测并读取芯片信息。$ xfel version AWUSBFEX ID=0x00185900(R528/T113) dflag=0x44 dlength=0x08 scratchpad=0x00045000 $ xfel sid d3402000ec1408140140082114cb5bcb $ xfel ddr t113-s3 Initial ddr controller succeededxfel payload

磨刀不误砍柴工,调芯片最好有JTAG,没有的情况下,串口打印是必须的。

xfel工程里面有默认有t113-s3的ddr和spi的payload工程了。

我们先从里面剥离出最简单的串口操作代码,让其至少有输出功能,方便后面打印日志。使用新编译出的payload,重新编译生成xfel,再随便执行下spi flash命令,串口有打印就行了。

留着这代码备用。ddr中运行代码

继续基于上面的代码,把具体的功能可以先屏蔽。然后把修改链接地址为ddr。

然后使用xfel把这代码加载到DDR中,运行下看没有输出。xfel ddr t113-s3 xfel write 0x40000000 spi.bin xfel exec 0x40000000果然看到了打印,说明可以使用xfel直接加载程序到DDR中运行,这样为后面的开发带来了极大的便利。

DDR中运行rt-thread

有了基本开发条件后,就可以开始移植软件部分了。

因为是cortex-a的内核,这块都比较通用,我打算基于

bsp/qemu-vexpress-a9来修改。先是使用menuconfig重新配置一下,把所有用不到的组件全关了,只留最基本的kernal和串口驱动部分。

再把链接脚本中的地址修改为目标芯片的地址 0x40000000。

然后把board.c中的中断和时钟心跳这些与硬件有关的代码先屏蔽。

串口驱动

因为没有JTAG,那么串口驱动是必须的了, 把之前从xfel payload中提取出来的串口驱动复制过来。

替换到原来的串口驱动的初始化部分,并把原来的所有硬件相关的代码暂时屏蔽。

只保留putc功能。编译通过后,使用xfel加载到ddr中运行。观察串口。

果然没有任何打印 !!!!汇编中的debug

遇事不要慌,问题肯定不大。没有任何打印说明程序没能正常运行,或是打印本身有问题。

首先没被运行的可能性可以排除,因为之前加载payload改的小代码可以运行的。然后就是有可能程序还没运行到程序中串口初始化的地方,此时最好能有JTAG单步,或是能知道启动代码中的汇编程序都运行到哪了。

如果是C,每行加个打印就好了。嗯,汇编也能加。因为驱动中的接口都是一堆参数,带句柄,还是static的,显然不方便汇编里面调用。

于是我们单独改造下,让串口初始化不需要参数,输出函数只要一个输出数据参数即可。void sys_uart_init(void) { virtual_addr_t addr; uint32_t val; /* Config GPIOE2 and GPIOE3 to txd0 and rxd0 */ addr = 0x020000c0 + 0x0; val = readl(addr); val &= ~(0xf << ((2 & 0x7) << 2)); val |= ((0x6 & 0xf) << ((2 & 0x7) << 2)); write32(addr, val); ............ } void sys_uart_putc(char c) { virtual_addr_t addr = 0x02500000; while((readl(addr + 0x7c) & (0x1 << 1)) == 0); write32(addr + 0x00, c); }这样汇编中就可以比较方便调用了,先放在启动入口看看有没打印。

.globl _reset _reset: ldr r1, [r1] bl sys_uart_init mov r0, ='R' bl sys_uart_putc mov r0, ='T' bl sys_uart_putc mov r0, ='T' bl sys_uart_putc新程序加载到DDR中,果然看到了我们想要的RTT这3个字的打印。说明程序运行到了这里。

通过这种办法,继续在汇编中不同位置添加不同的字符,最后定位到是进MMU初始化就再没打印了。哦!!! 想起来还没更新MMU配置呢。

MMU配置可以先简单些,32位的全4G空间全部当成外设,把DDR区域设置为常规(带cache,可运行)修改board.c中的platform_mem_desc表就好了

struct mem_desc platform_mem_desc[] = { {0x00000000, 0xFFFFFFFF, 0x00000000, DEVICE_MEM}, {0x40000000, 0x47FFFFFF, 0x40000000, NORMAL_MEM}, };更新mmu配置后,果然看到了 RT-Thread 启动LOGO,还打印了

msh>。

当然,此时命令行不能输入。因为我们串口驱动的输入还没写。因为全志的串口驱动基本兼容的,知道串口外设的基地址,直接抄原来其它芯片的代码,直接读寄存器,把getc实现就好了。

但还是不能输入,应该是要支持中断才行。中断

cortex-A芯片一般都使用GIC,但有好几个版本,通过有限的资料查到,T113-S3是使用GICv2。

这块代码都是通用的,关键是要知道其在芯片中的地址,这个PDF中也有查到GIC地址是在0x03020000。RT-Thread中,GICv2的基本适配已做好,新芯片适配需要知道2个地址,但PDF中没写。

这块根据全志同类型芯片的偏移来看,猜测是一样的/* the basic constants and interfaces needed by gic */ rt_inline rt_uint32_t platform_get_gic_dist_base(void) { return 0x03021000; } rt_inline rt_uint32_t platform_get_gic_cpu_base(void) { return 0x03022000; }再通过PDF上面查到的UART0中断号是34,改好后,加载运行,果然收到中断了。

SMP

接下来就是适配SMP了,因为只是2核,所以也不用管分簇这些了。

最主要是要知道第2个核是怎么启动,启动后会运行哪个地址的程序。其它这里还有个坑点要注意,就是有些芯片多核是自动启动的,但此时一般软件环境还没准备好,可能会乱飞,需要把非0核先暂停下来。

如果是这类芯片,就需要把RT_SMP_AUTO_BOOT打开,这样非0核会自动挂起,直到被0核唤醒,再去指定地址运行。

因为我们之前都能正常运行了,所以肯定不是这种类型的。通过 https://whycan.com/t_7808.html 这个贴子里面 shaoxi2010 大佬的说明,知道了第2个核的启动方法。

此时更新menuconfig把SMP打开,然后更新下SMP需要的几个接口/* The Soft Entry Address Register of CPU0 is 0x070005C4. The Soft Entry Address Register of CPU1 is 0x070005C8. */ void rt_hw_secondary_cpu_up(void) { uint32_t cpuboot_membase = 0x070005c4; uint32_t cpuxcfg_membase = 0x09010000; uint32_t cpu, reg; cpu = 1; /* Set CPU boot address */ writel((uint32_t)(secondary_cpu_start), cpuboot_membase + 4 * cpu); /* Deassert the CPU core in reset */ reg = readl(cpuxcfg_membase); writel(reg | (1 << cpu), cpuxcfg_membase); __asm__ volatile ("isb":::"memory"); }一些和芯片外设相关的先禁用掉,不要心跳也是能运行的。

void secondary_cpu_c_start(void) { // int timer_irq_number; // timer_irq_number = aw_get_irq_num("TIMER1"); rt_hw_vector_init(); rt_hw_spin_lock(&_cpus_lock); arm_gic_cpu_init(0, platform_get_gic_cpu_base()); // arm_gic_set_cpu(0, timer_irq_number, 0x2); //timer1 // timer1_init(); // rt_hw_interrupt_install(timer_irq_number, rt_hw_timer1_isr, RT_NULL, "tick1"); // rt_hw_interrupt_umask(timer_irq_number); rt_system_scheduler_start(); }编译通过后,使用xfel加载到ddr中运行。SMP果然愉快地运行起来了。

\ | / - RT - Thread Operating System / | \ 4.1.0 build Apr 9 2022 21:17:55 2006 - 2022 Copyright by RT-Thread team [I/sal.skt] Socket Abstraction Layer initialize success. cpuxcfg_membase = 0x13FF0101 // 启动之前的值 cpuxcfg_membase = 0x13FF0103 // 启动之后的值 Hello T113 RT-Thread SMP! msh />ps thread cpu bind pri status sp stack size max used left tick error -------- --- ---- --- ------- ---------- ---------- ------ ---------- --- tshell 0 2 20 running 0x00000140 0x00001000 15% 0x0000000a 000 aio N/A 2 16 suspend 0x00000080 0x00000800 07% 0x0000000a 000 sys work N/A 2 23 suspend 0x00000084 0x00000800 06% 0x0000000a 000 tsystem N/A 2 30 suspend 0x00000098 0x00000400 22% 0x00000020 000 tidle1 1 1 31 running 0x0000005c 0x00000400 19% 0x00000020 000 tidle0 N/A 0 31 ready 0x0000005c 0x00000400 19% 0x00000020 000 timer N/A 2 4 suspend 0x0000007c 0x00000400 12% 0x0000000a 000后续

整理代码上gitee

-

回复: USB Gadget 模拟摄像头 g_webcam: musb-hdrc.4.auto: failed to start g_webcam: -22发布在 Linux

有复合设备吗?把不必要的复合设备关掉,看能不能减少端点占用。

-

回复: D1-H内存访问速度差异测试发布在 MR Series

抱歉,我理解成写入操作了。

只读取的话,清cache后确实真实地从DRAM中读取。

但此时CPU实际可能会从DRAM读取64字节的数据吧,因为cache line是64字节。 -

回复: D1-H内存访问速度差异测试发布在 MR Series

虽然你访问完就刷cache,但实际CPU操作的还是cache中的,结果有参考意义,但不准确。除非你裸机映射成非cache的,但这样没什么实际意义。

实际使用中,数据结构和地址多留意尽量对齐,大数据量尽量cache line对齐就行了。

-

回复: 因为喜欢用ADB,因为不喜欢插拔TF卡,所以D1直接用PhoenixSuit烧录TF(SDNAND)发布在 MR Series

D1S好改不?烧录速度多少?

我现在烧录D1S的SDNAND,是改写了xfel来实现的

https://whycan.com/t_7730.html -

请教D1/D1S的LDO输入端串的二极管作用?发布在 MR Series

看到原理图上面都有串一个二极管,请问此二极管的作用是什么?

- 降压替LDO分担压差?用低压差的肖特基二极还是标准压差的好?

- 掉电时防止电流倒灌?

-

回复: 请教:按照配网开发指南在哪吒板采用smartconfig方式配网,收不到xconfig发出的广播包发布在 MR Series

尽量BLE配网啊,实在不行AP也可以接受。

smartconfig的坑别跳了!