baiwen 发布的帖子

-

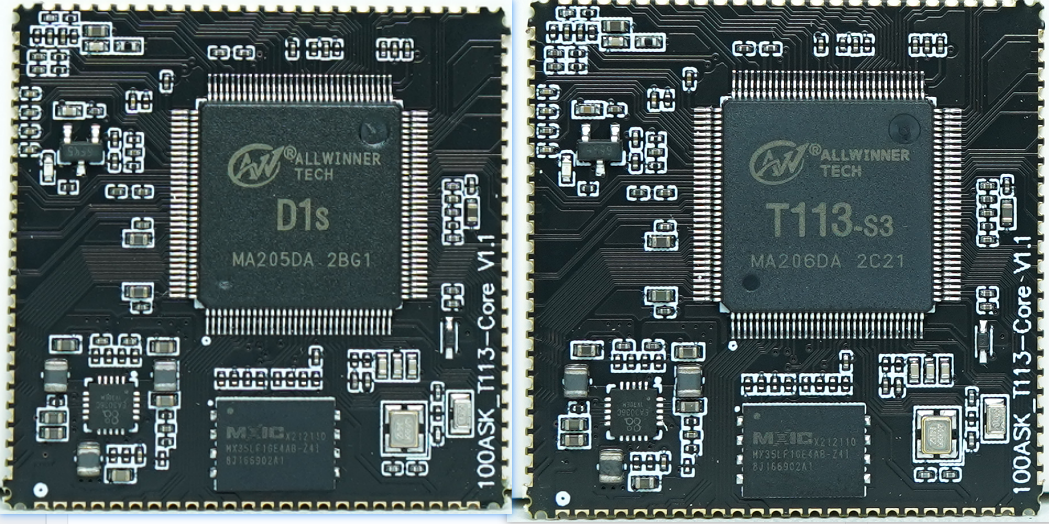

韦东山 全志T113s3 PRO V1.3来啦!发布在 其它全志芯片讨论区

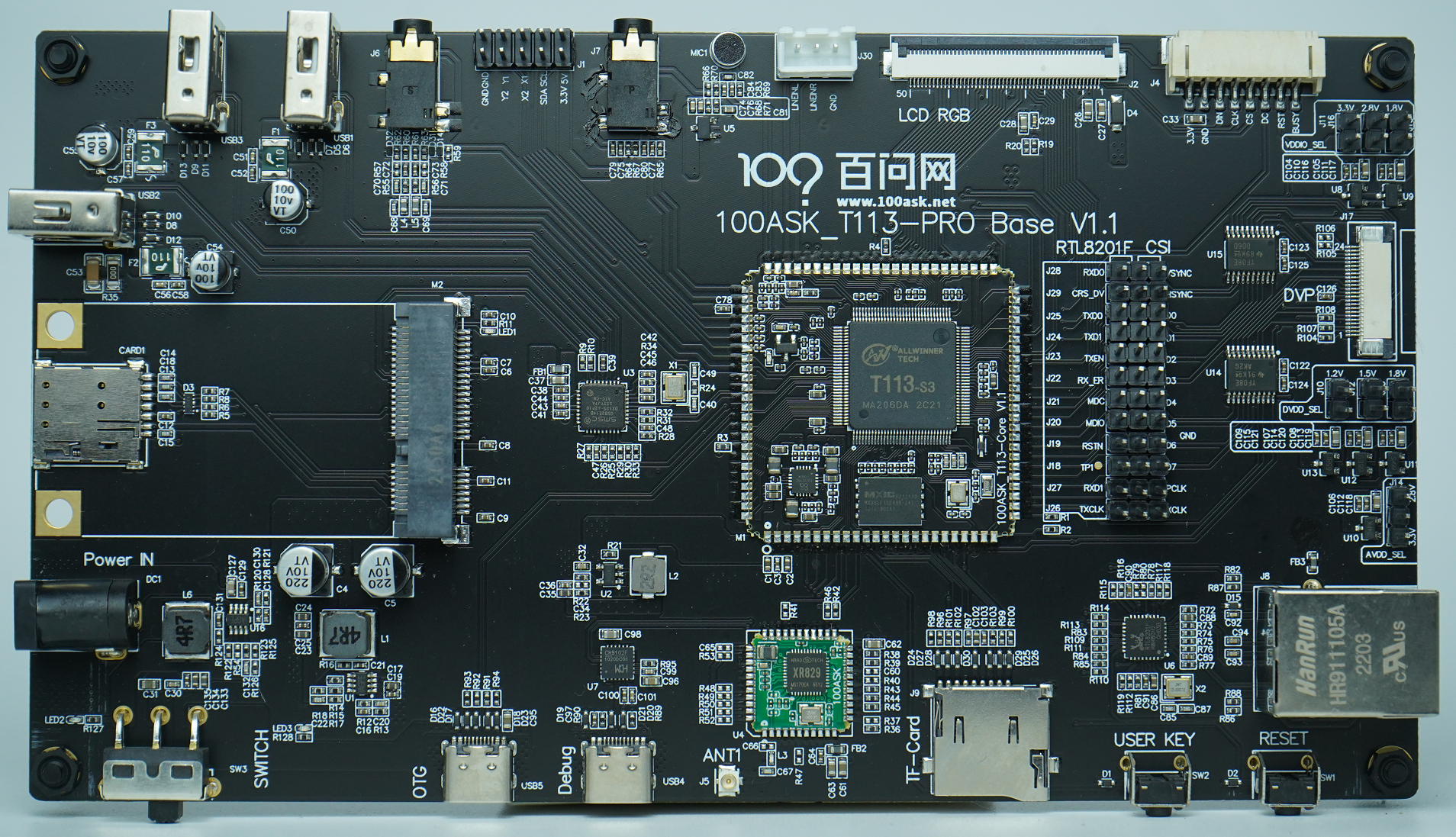

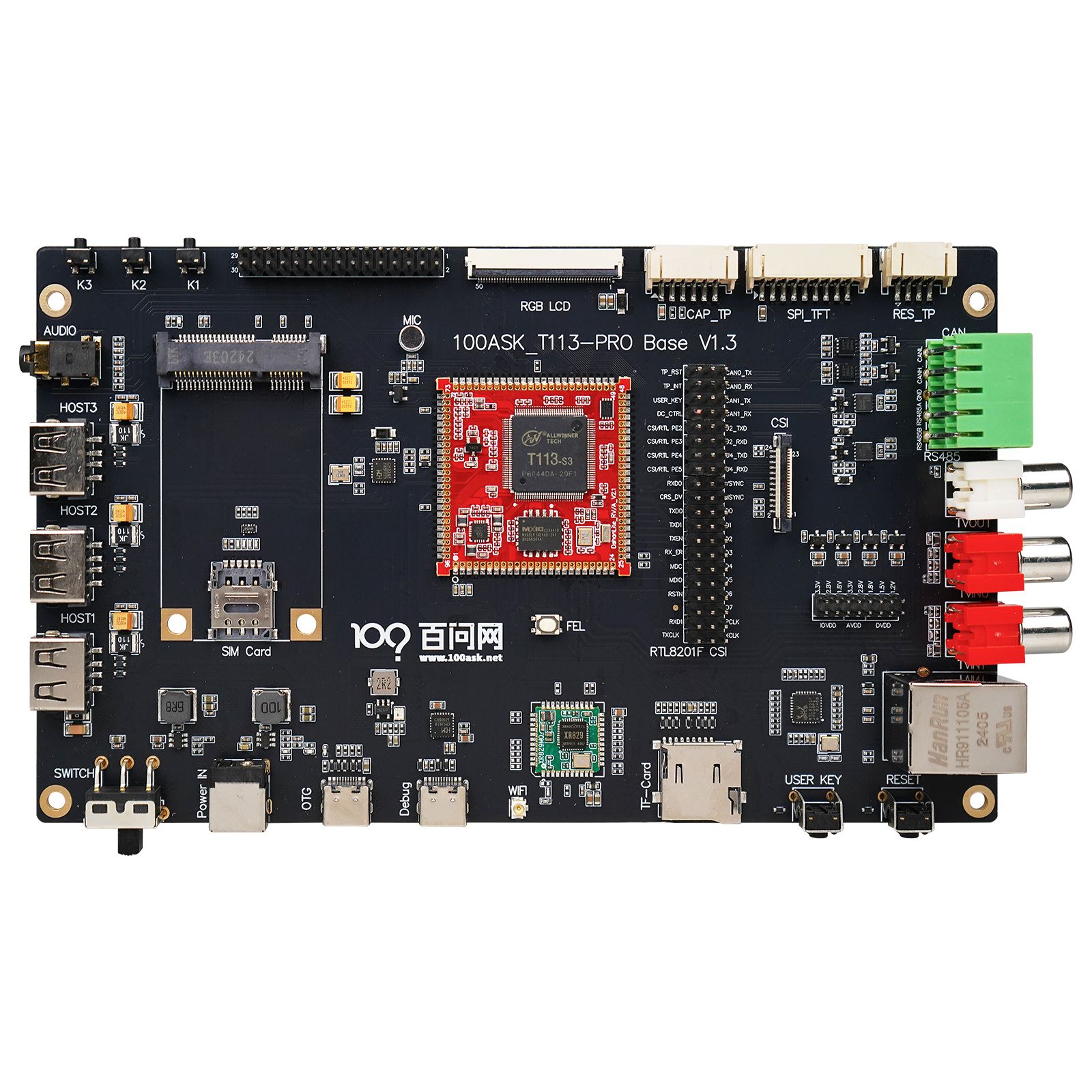

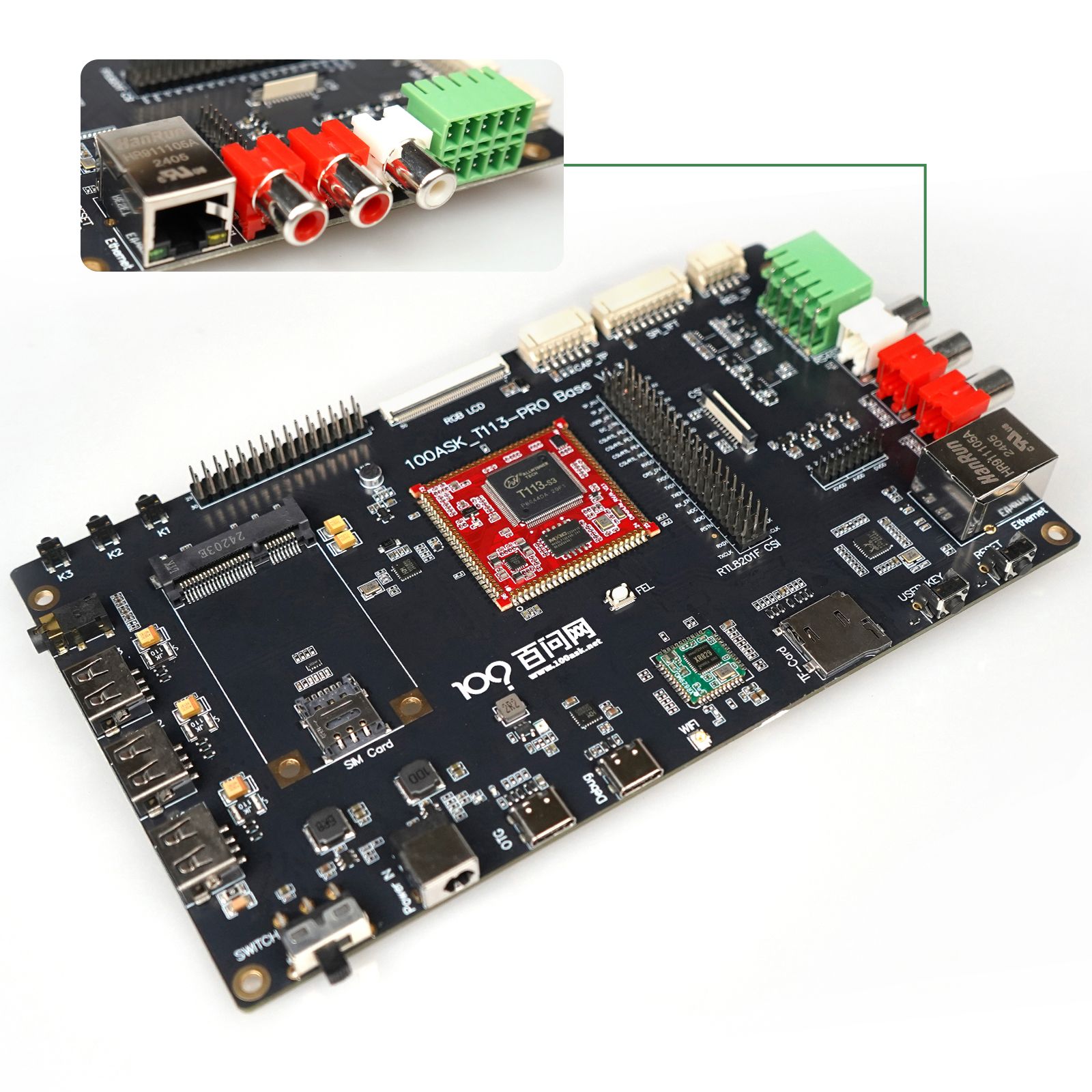

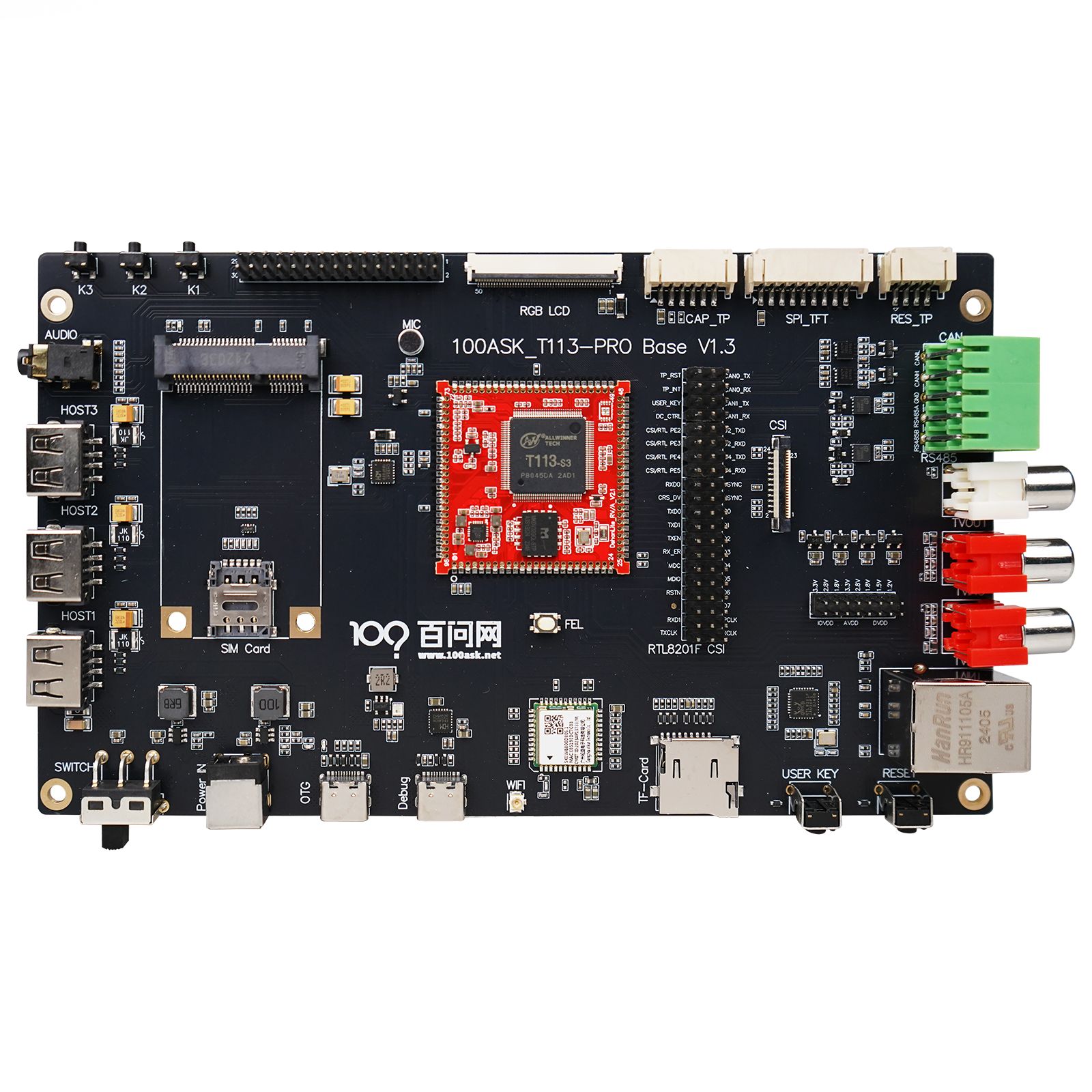

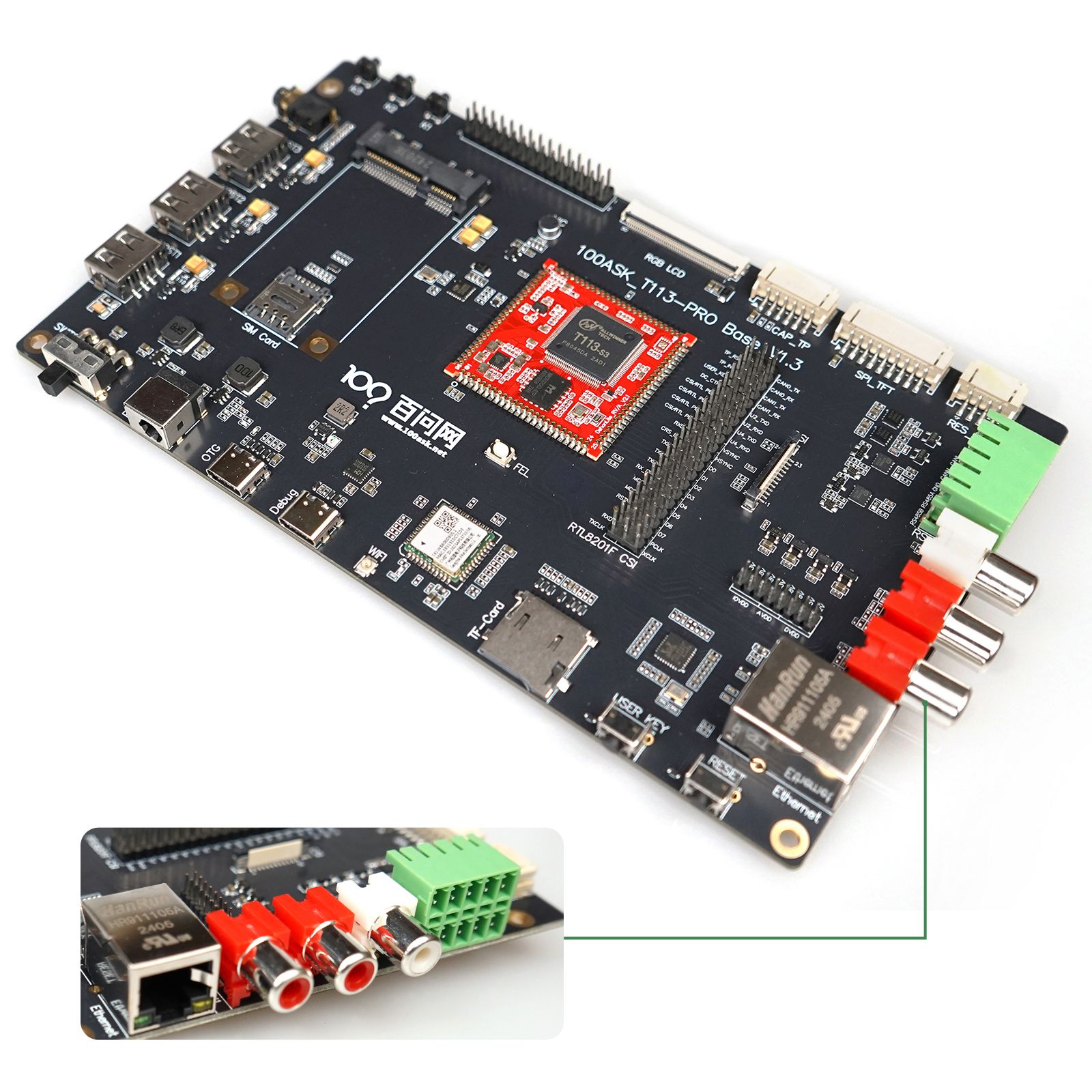

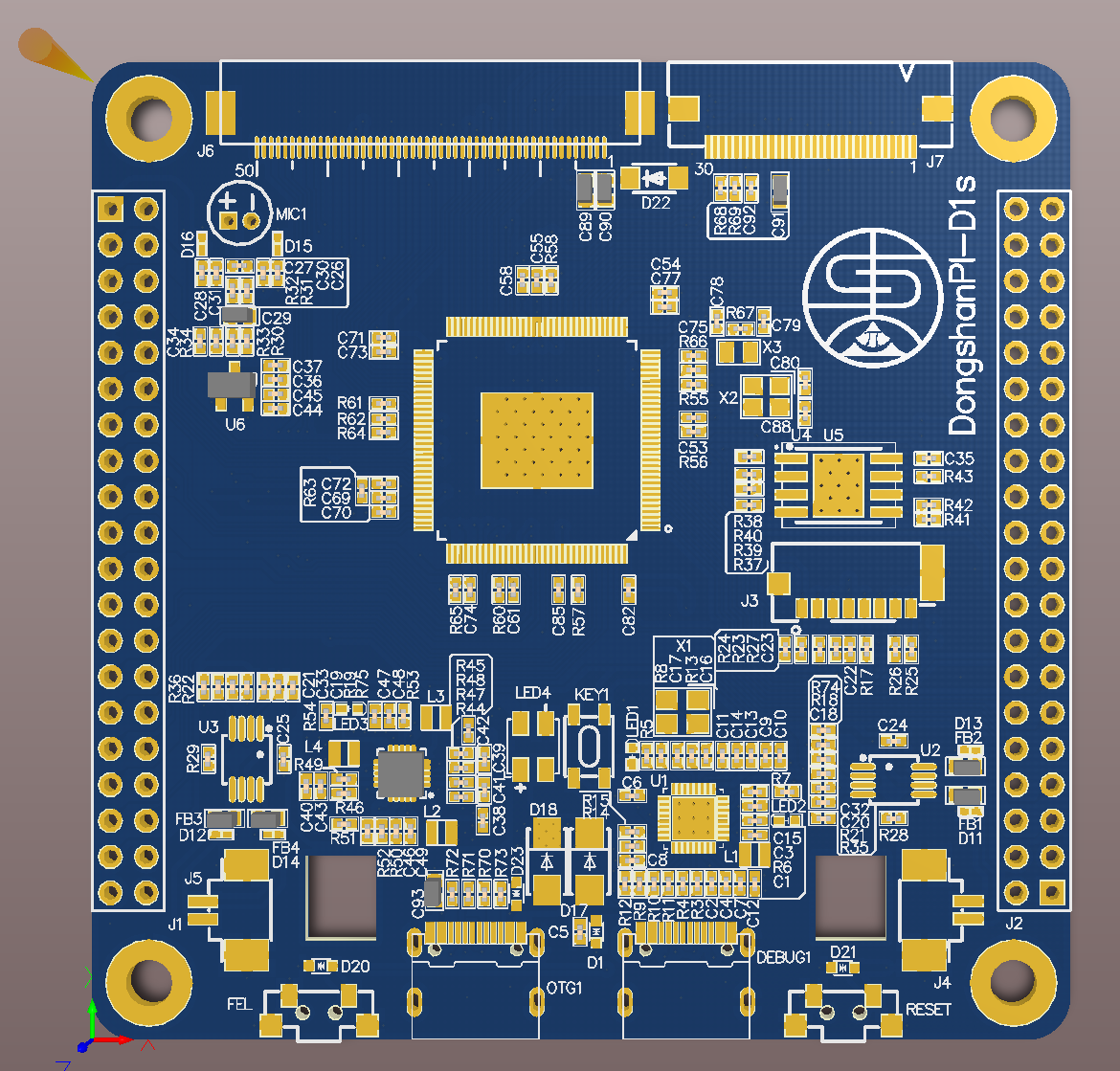

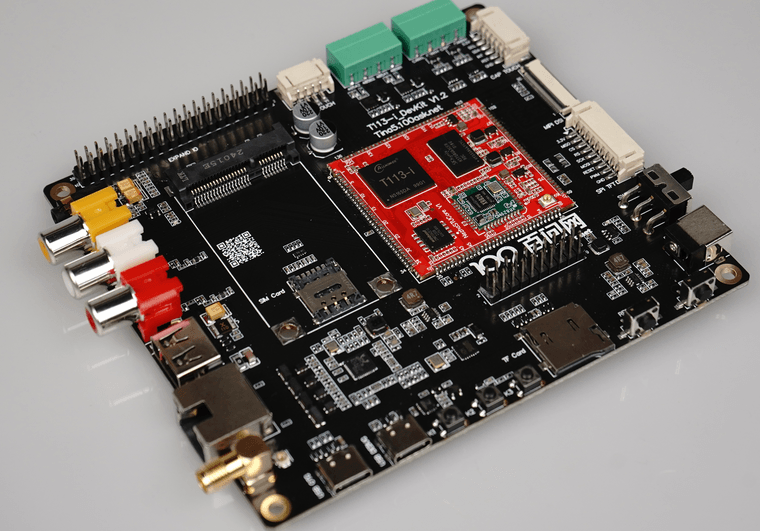

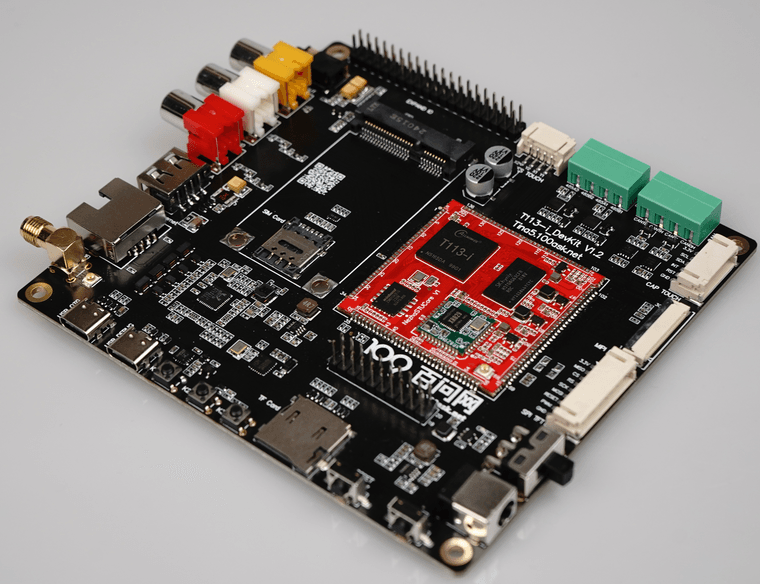

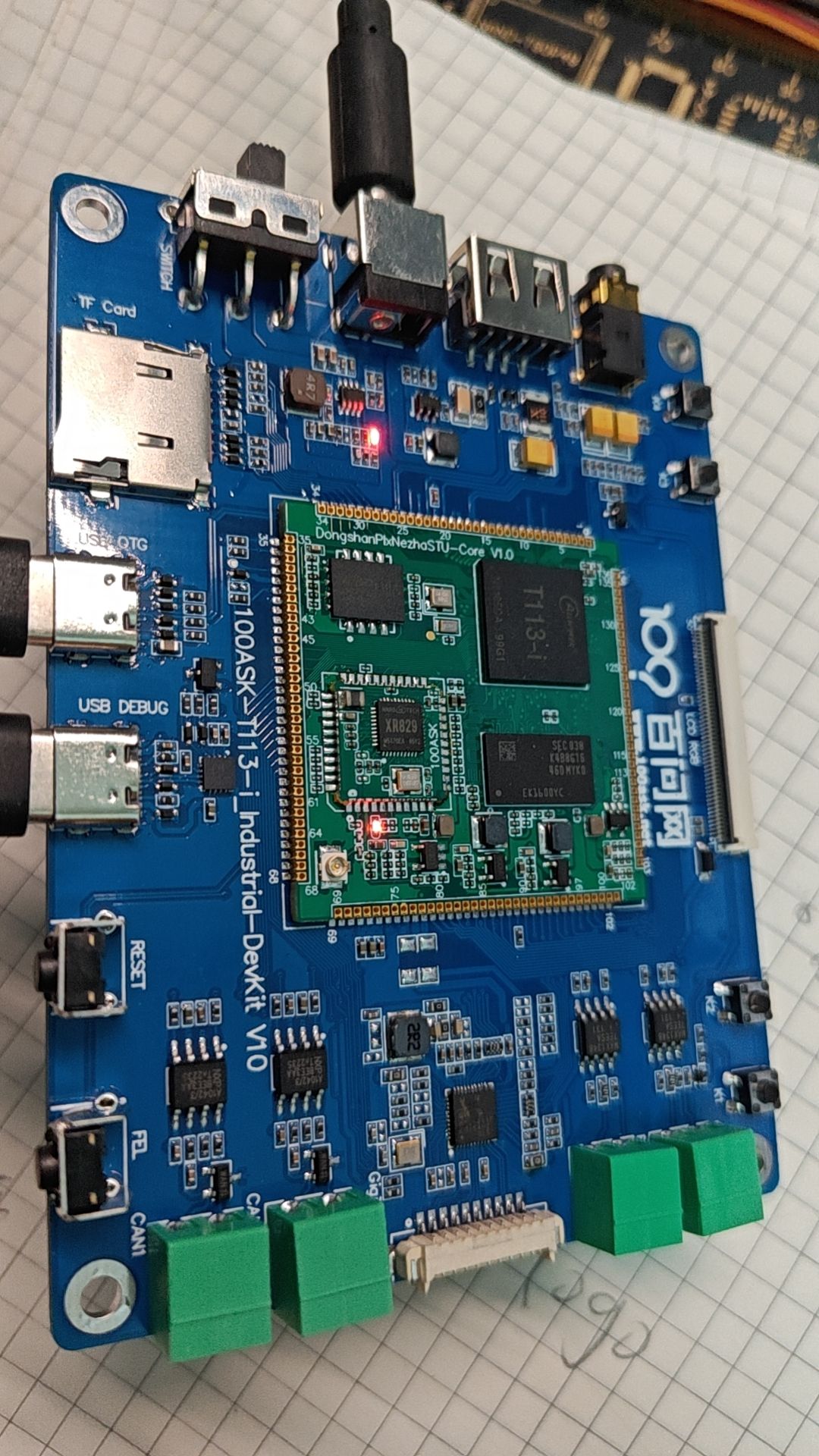

完全兼容V1.2版本软硬件+文档 视频教程,另外在此基础上,新增了 RS485 CAN2.0 TVIN 输入 TVOUT输出等接口,同时我们提供了 SD-NAND 4GB 大容量类EMMC版本 + WIFI6 + BT5无线 模块支持!

-

回复: t113(tina)加入paha.mqtt.c库,编译成固件烧录到板子上后报错找不到动态库发布在 MR Series

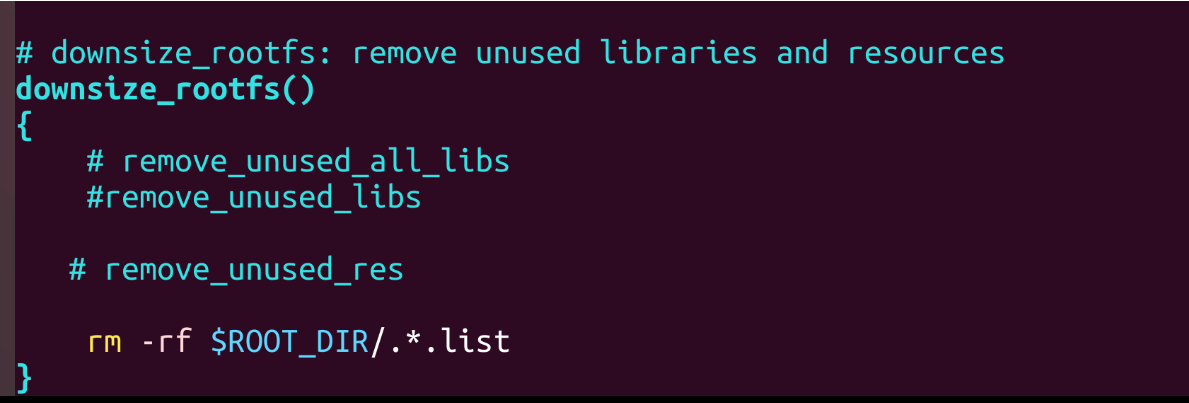

我也遇到了编译QT5 无法打包所有qt so库的情况。

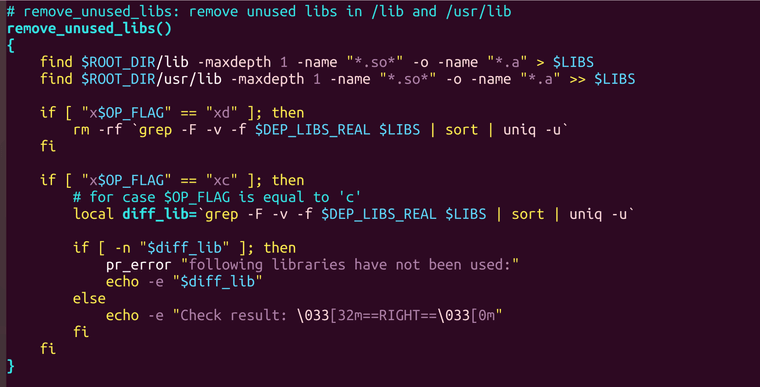

经过调试发现

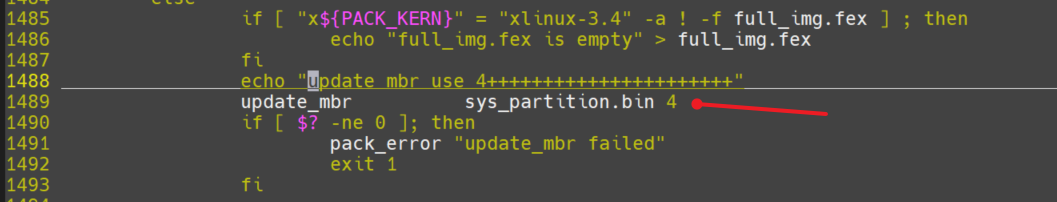

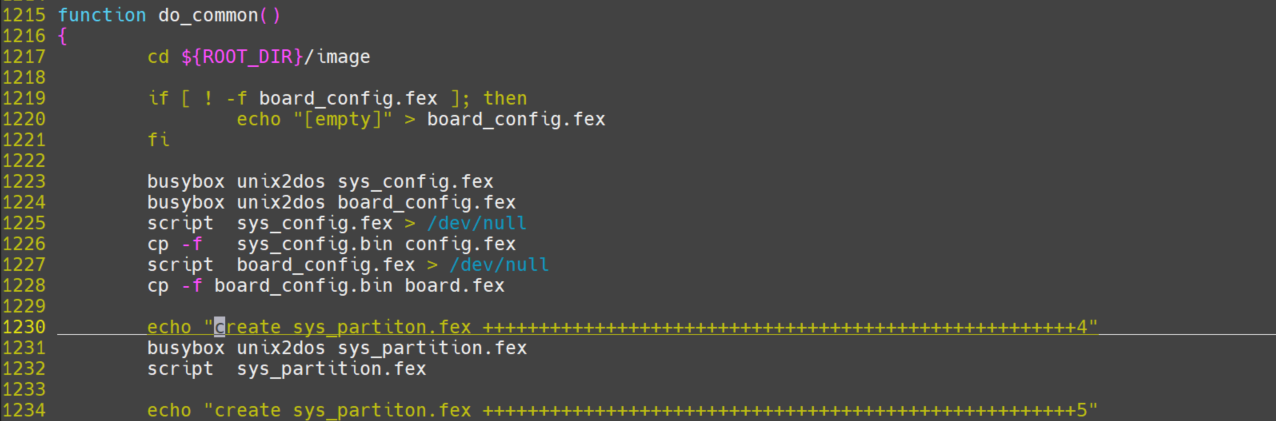

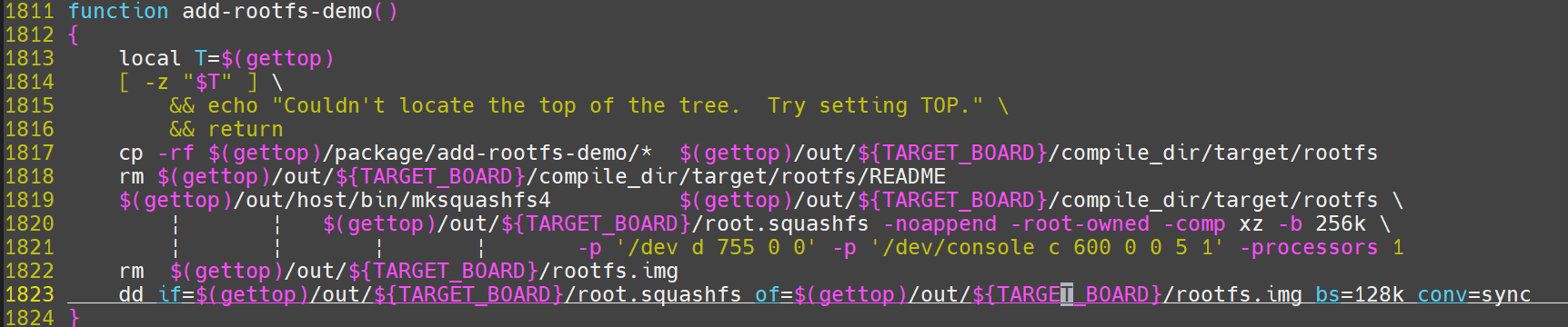

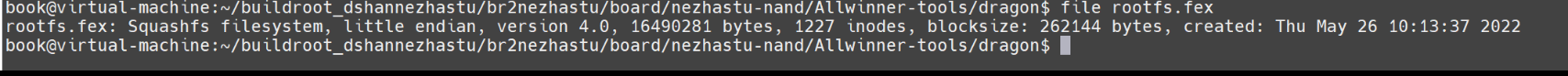

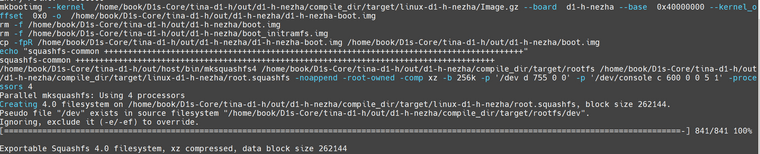

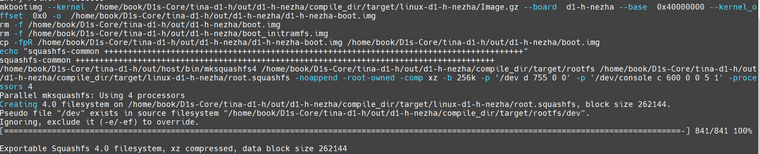

是最后打包制作 rootfs.img 时 自动将 脚本认为无用的 文件资源 库 给移除掉了。所以导致最终目标系统没有包含进去。

源码 build 目录 找到 reduce-rootfs-size.sh 脚本

找到 downsize_rootfs 函数,注释掉里面的几个 remove函数

具体打包无效原因在。

-

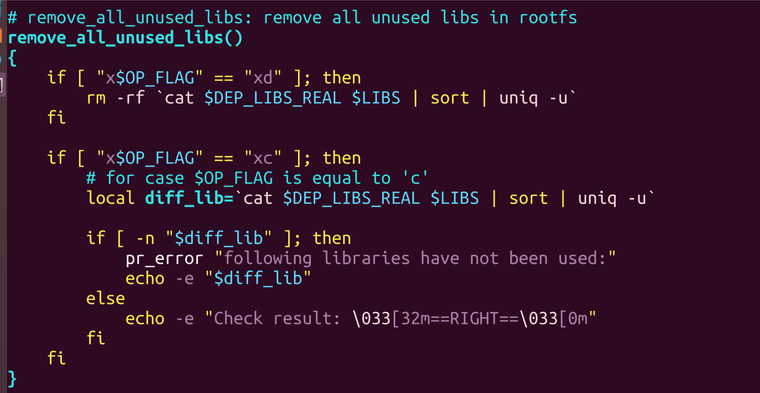

请问如何在D1-h上同时驱动MIPIDSI + HDMI实现双屏异显!发布在 MR Series

参考大佬 https://bbs.aw-ol.com/topic/362/diy教程-d1的双屏异显第一弹来啦-d1同时支持两个屏幕-一共做ui交互-一边个播放视频?_=1713492912563

帖子,

尝试去做实验,

发现修改 libuapi 库,videoOutPort.c 文件 SCREEN_0 为1 ,

通过 tplayerdemo播放视频,HDMI无任何输出,

但是通过 colorbar 调试,两边是可以显示不同的画面。

如果不修改 videoOutPort.c 文件 SCREEN_0 为1 ,则MIPI DSI可以正常播放视频。

cd /sys/kernel/debug/dispdbg echo disp0 > name; echo switch1 > command; echo 1 4 0 0 0x4 0x101 0 0 0 8 > param; echo 1 > start; echo 1 > /sys/class/disp/disp/attr/colorbar cd /sys/kernel/debug/dispdbg echo disp1 > name; echo switch1 > command; echo 4 10 0 0 0x4 0x101 0 0 0 8 > param; echo 1 > start; cat /sys/devices/virtual/disp/disp/attr/sys 考官方文档截屏,导出的图像是正常的 echo 0 > /sys/class/disp/disp/attr/disp echo /data/filename.bmp > /sys/class/disp/disp/attr/capture_dump 使用colorbar,显示不正常 echo 0 > /sys/class/disp/disp/attr/disp echo 1 > /sys/class/disp/disp/attr/colorbar echo 1 > /sys/class/disp/disp/attr/disp echo 3 > /sys/class/disp/disp/attr/colorbar 重新对LCD初始化就正常了。 mount -t debugfs none /sys/kernel/debug; cd /sys/kernel/debug/dispdbg; echo suspend > command; echo disp0 > name; echo 1 > start echo resume > command; echo disp0 > name; echo 1 > start目前认为是是 硬件部分 没问题,两个图层已经创建,单独 MIPI DSI 运行LVGL示例没问题,但是Tplayerdemo在调取disp图层 播放视频时无法从 hdmi 输出,有没有比较了解的大佬指点一二?

不胜感激! -

回复: 求教使用百问网v851s的sdk打包问题!发布在 V Series

@awwwwa

可以参考 编译步骤

https://dongshanpi.com/YuzukiHD-Lizard/07-TinaSDK_DevelopmentGuide/

重新 拉取 SDK Lizard 扩展补丁包

覆盖

-

回复: V851S上的ISP真的坏了吗?发布在 V Series

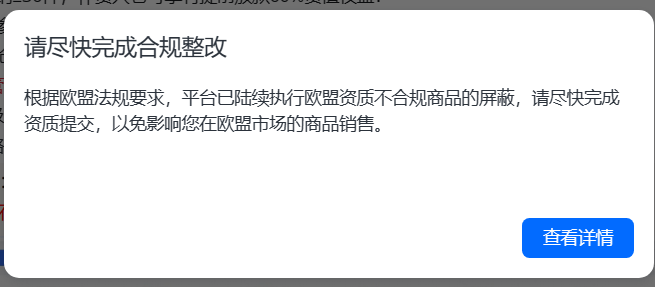

@kanken6174 非常抱歉,给您带来了 不好的体验, V851S商品没有下架,平台最近对认证有着非常严格的要求,导致我们的商品无法在 欧盟地区 售卖。

有相关问题,可以 发 邮件到 support@100ask.net

我们会单独处理。

-

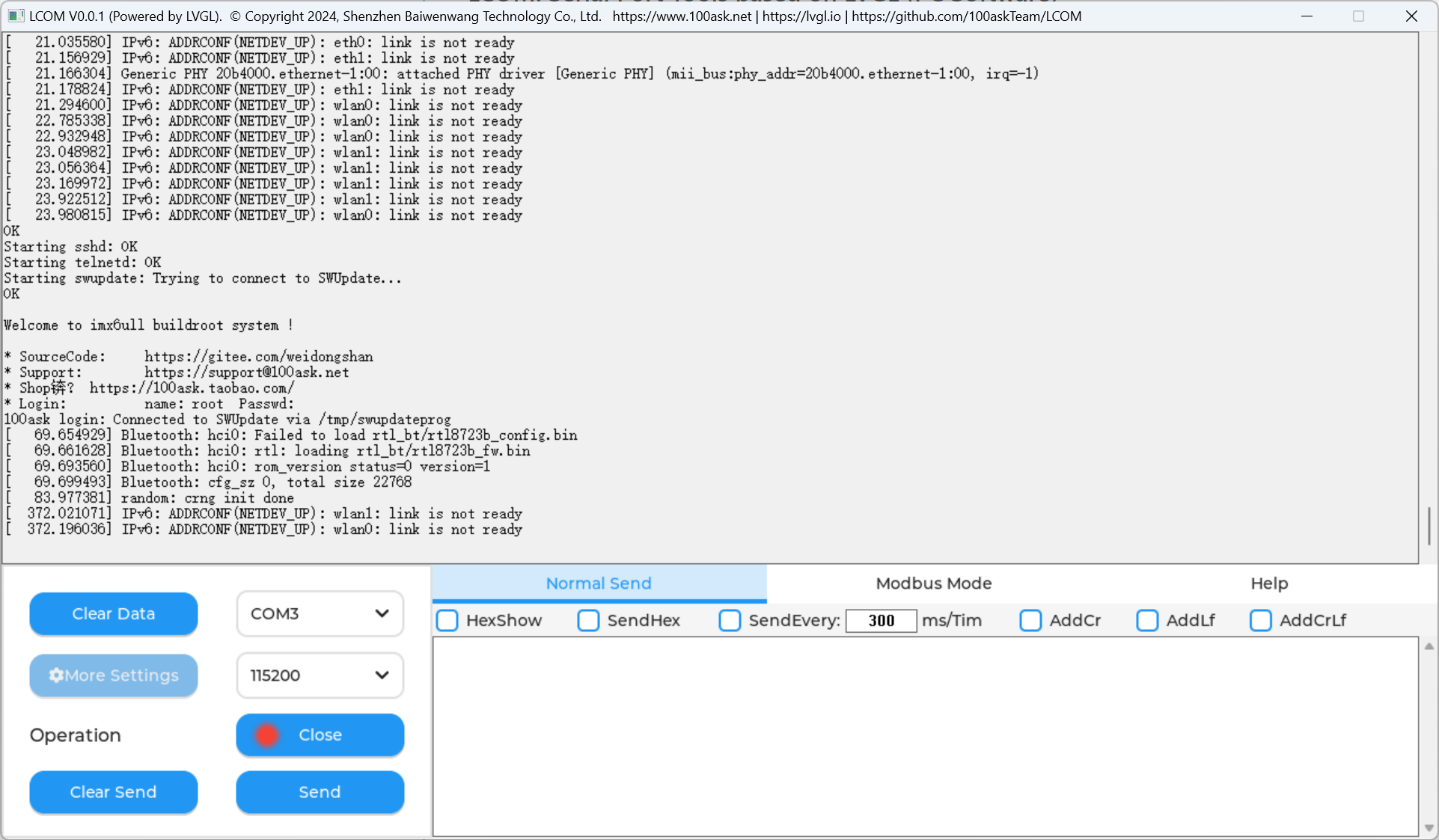

基于LVGL编写的windows串口工具: LCOM发布在 GUI

LCOM: Serial Port Tools based on LVGL (PC Software)

一直以来我都想用LVGL做一个真正意义上的PC软件,来验证或者表达LVGL出色的特性,现在我用LCOM做到了!

LCOM 是一个基于LVGL编写的串口工具,界面简洁,功能出色,并且上手简单。

LCOM的一些功能包括:

- 以HEX或ASCII格式发送和接收数据。

- 实时刷新COM端口列表。可设置COM端口的连接参数包括波特率、奇偶校验、数据位、停止位和流控。

- 支持定时发送

- 支持换行发送(CR、LR、CRLF)

- 多种字符编码格式支持,比如 ASII,GBK(Chinese),UTF-8,UTF-16 等

- Modbus模式支持(为百问网STM32H5 modbus解决方案准备(学习教程))

- 界面多语言支持

- 多条字符串发送

- 自动保存设置(退出保存)

- 串口自动检测,支持记住上次使用的串口号

- 串口断线自动重连

- TCP/UDP 支持,包括客户端和服务端模式支持

- 自定义主题

- More todo

演示视频:https://www.bilibili.com/video/BV1bK4y1z7se

Get LCOM

- GitHub: https://github.com/100askTeam/LCOM/releases

- Gitee:https://gitee.com/weidongshan/LCOM/releases

Source code

Not yet open source (soon)

Issues

-

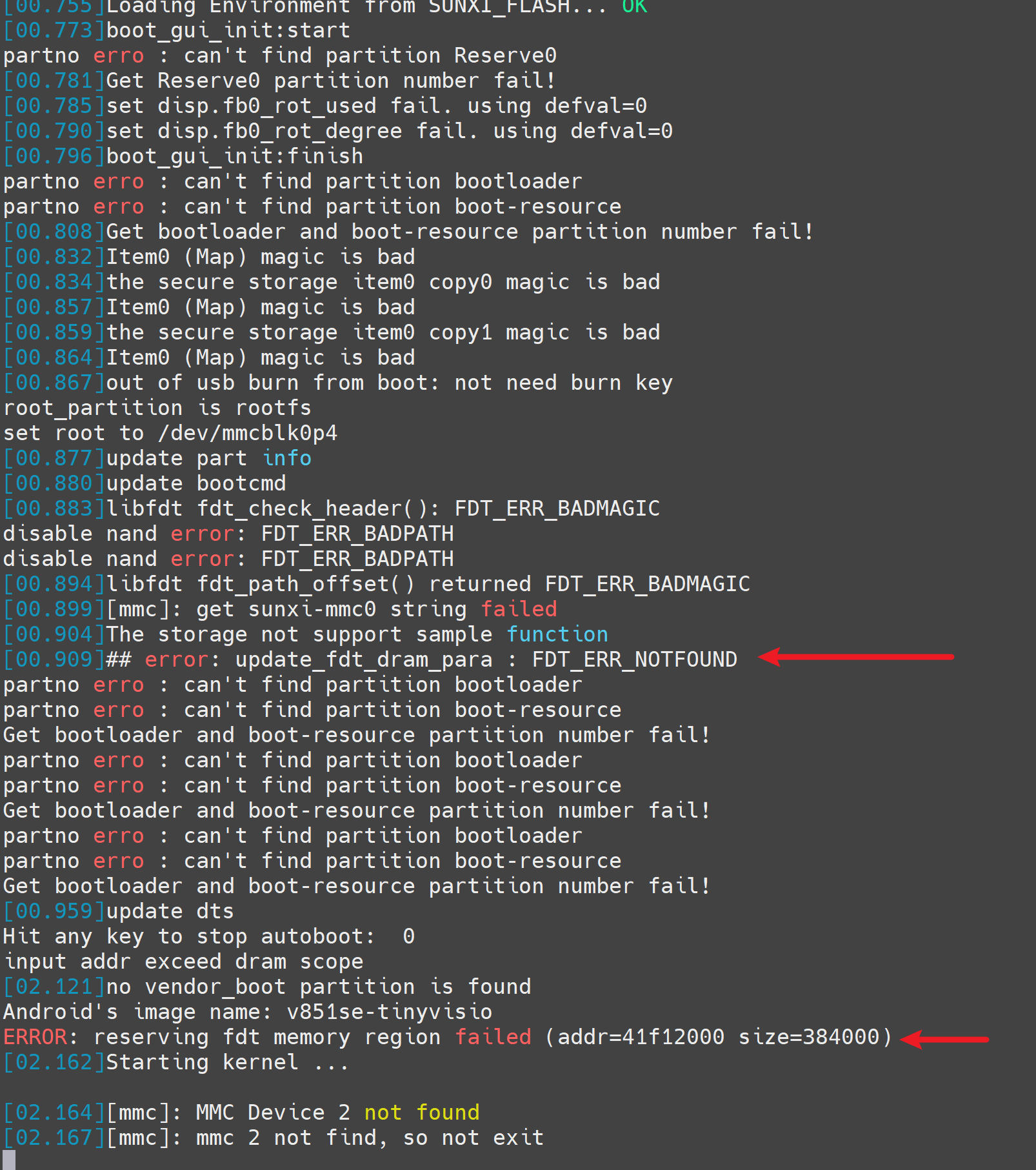

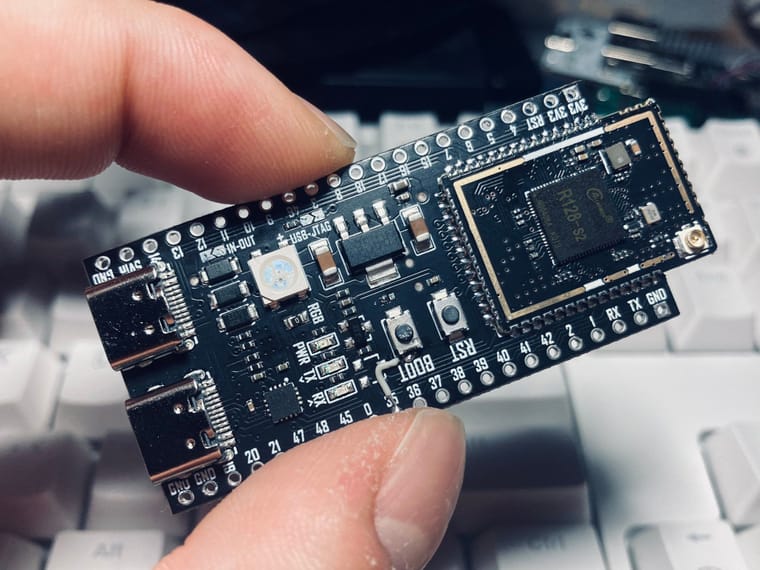

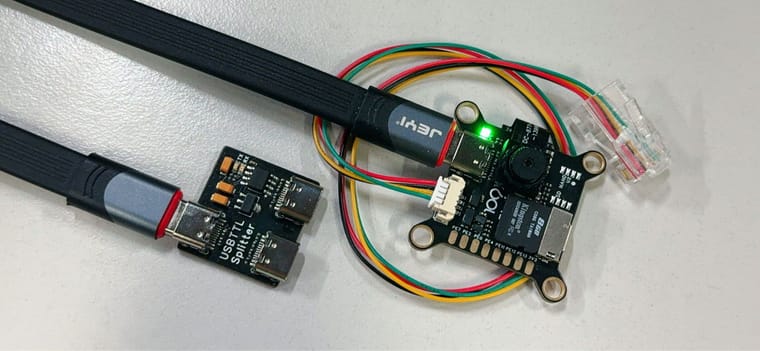

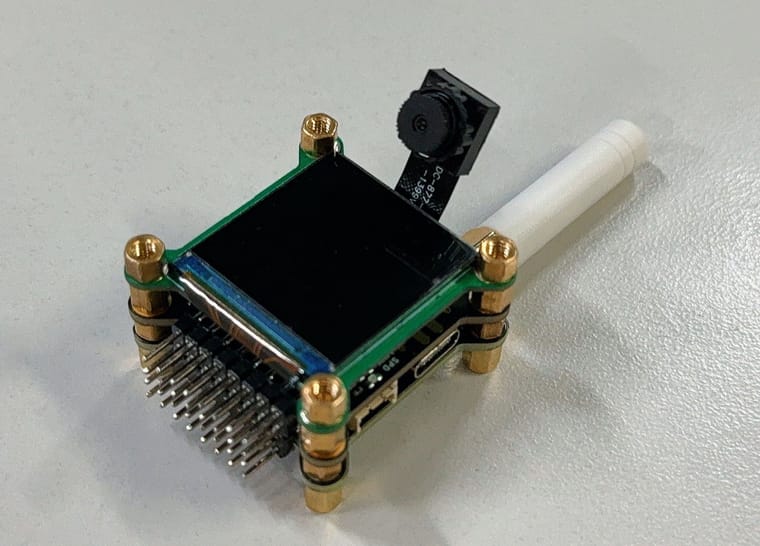

回复: V851SE TinyVision地表最帅AI开发板来了! @yuzukihd发布在 V Series

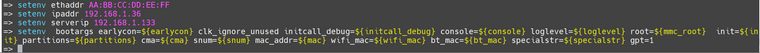

@baiwen 使用tina-sdk 4.0 启动 提示 ERROR: reserving fdt memory region failed (addr=41f12000 size=384000)

有问题固件

tina_v851se-tinyvision_uart0_kernel-error.zipsd线刷

330db410-2984-48f5-8b60-ad3b94fe6689-sd-tina_v851se-tinyvision_uart0.zipenv.cfg

ubuntu@ubuntu1804:~/Downloads/tina-v851/device/config/chips/v851se/configs/default$ cat env.cfg #kernel command arguments earlyprintk=sunxi-uart,0x02500000 initcall_debug=0 console=ttyS0,115200 nand_root=ubi0_4 mmc_root=/dev/mmcblk0p4 nor_root=/dev/mtdblock1 init=/init loglevel=8 coherent_pool=16K #reserve_list=30M@64M,78M@128M,200M@512M mac= wifi_mac= bt_mac= specialstr= root_partition=rootfs mtd_name=sys rootfstype=ubifs, rw #set kernel cmdline if boot.img or recovery.img has no cmdline we will use this setargs_nor=setenv bootargs earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${nor_root} rootwait init=${init} rdinit=${rdinit} partitions=${partitions} cma=${cma} coherent_pool=${coherent_pool} ion_carveout_list=${reserve_list} setargs_nand=setenv bootargs earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} ubi.mtd=${mtd_name} root=${nand_root} rootfstype=${rootfstype} rootwait init=${init} rdinit=${rdinit} partitions=${partitions} cma=${cma} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} selinux=${selinux} specialstr=${specialstr} coherent_pool=${coherent_pool} ion_carveout_list=${reserve_list} setargs_nand_ubi=setenv bootargs ubi.mtd=${mtd_name} earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${nand_root} rootfstype=${rootfstype} init=${init} partitions=${partitions} cma=${cma} snum=${snum} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} specialstr=${specialstr} gpt=1 setargs_mmc=setenv bootargs earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${mmc_root} rootwait init=${init} partitions=${partitions} cma=${cma} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} selinux=${selinux} specialstr=${specialstr} coherent_pool=${coherent_pool} ion_carveout_list=${reserve_list} #nand command syntax: sunxi_flash read address partition_name read_bytes #0x4007f800 = 0x40080000(kernel entry) - 0x800(boot.img header 2k) boot_partition=boot boot_normal=sunxi_flash read 44800000 ${boot_partition};bootm 44800000 boot_recovery=sunxi_flash read 44800000 extend;bootm 44800000 boot_fastboot=fastboot #recovery key recovery_key_value_max=0x13 recovery_key_value_min=0x10 #fastboot key fastboot_key_value_max=0x8 fastboot_key_value_min=0x2 #uboot system env config bootdelay=1 #default bootcmd, will change at runtime according to key press bootcmd=run setargs_nand boot_normal#default nand boot #verify the kernel verify=N -

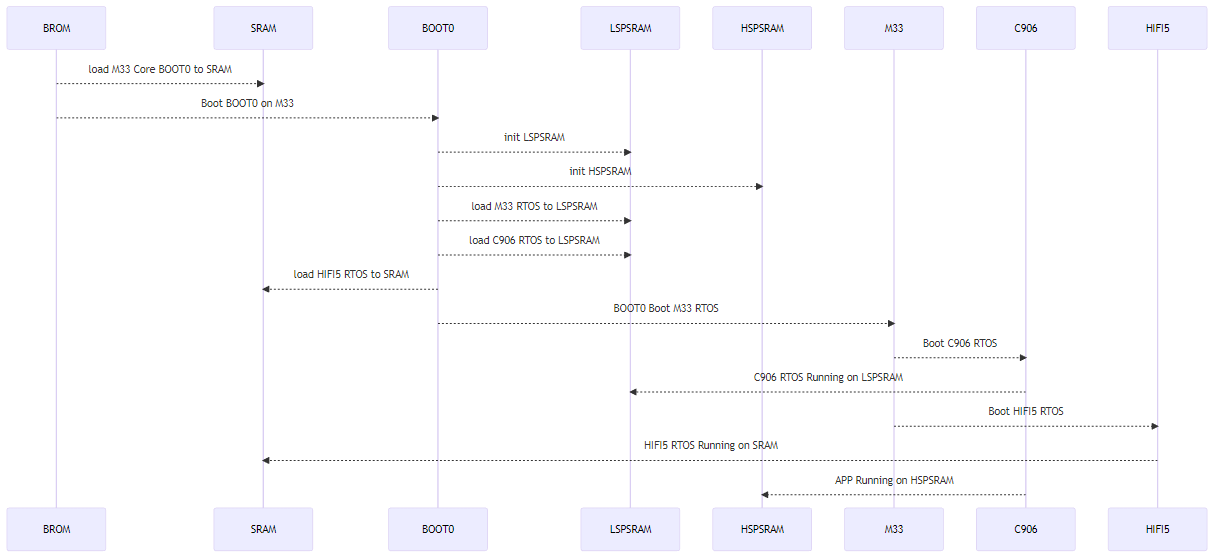

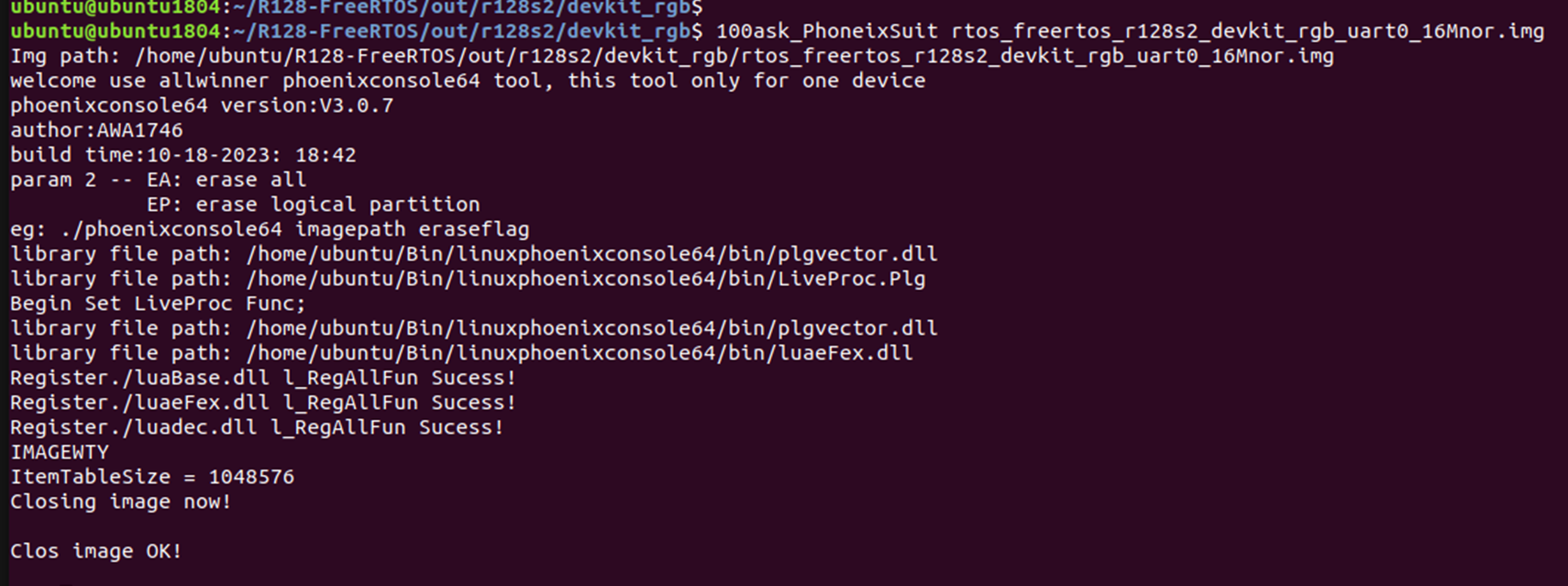

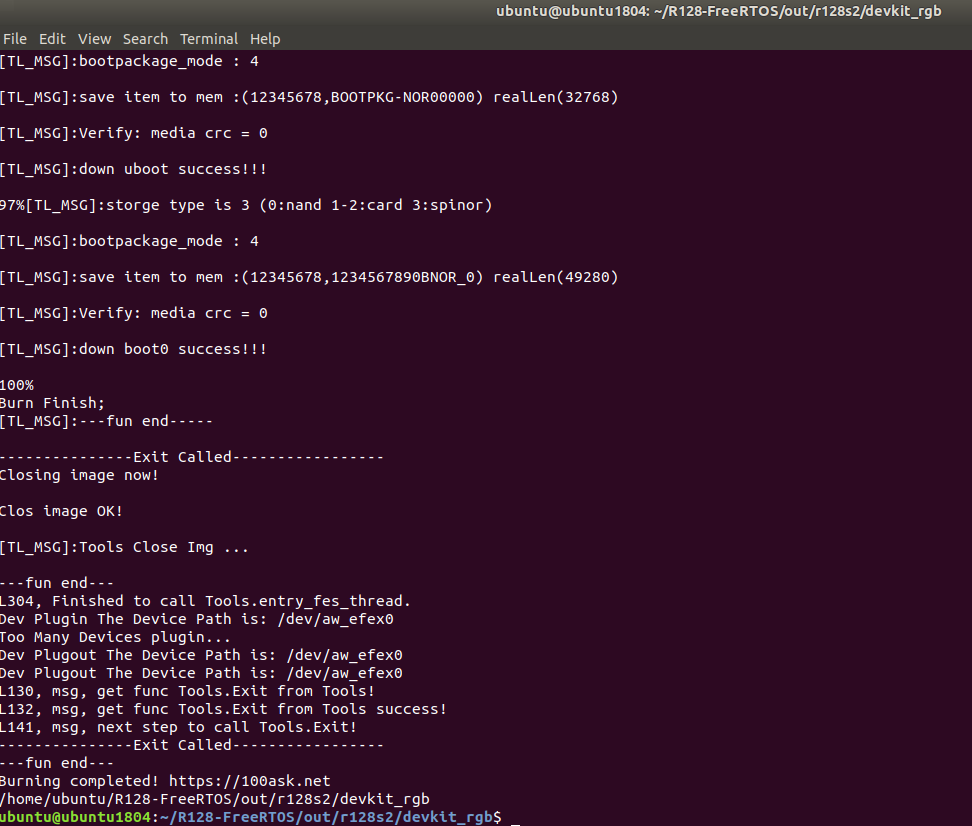

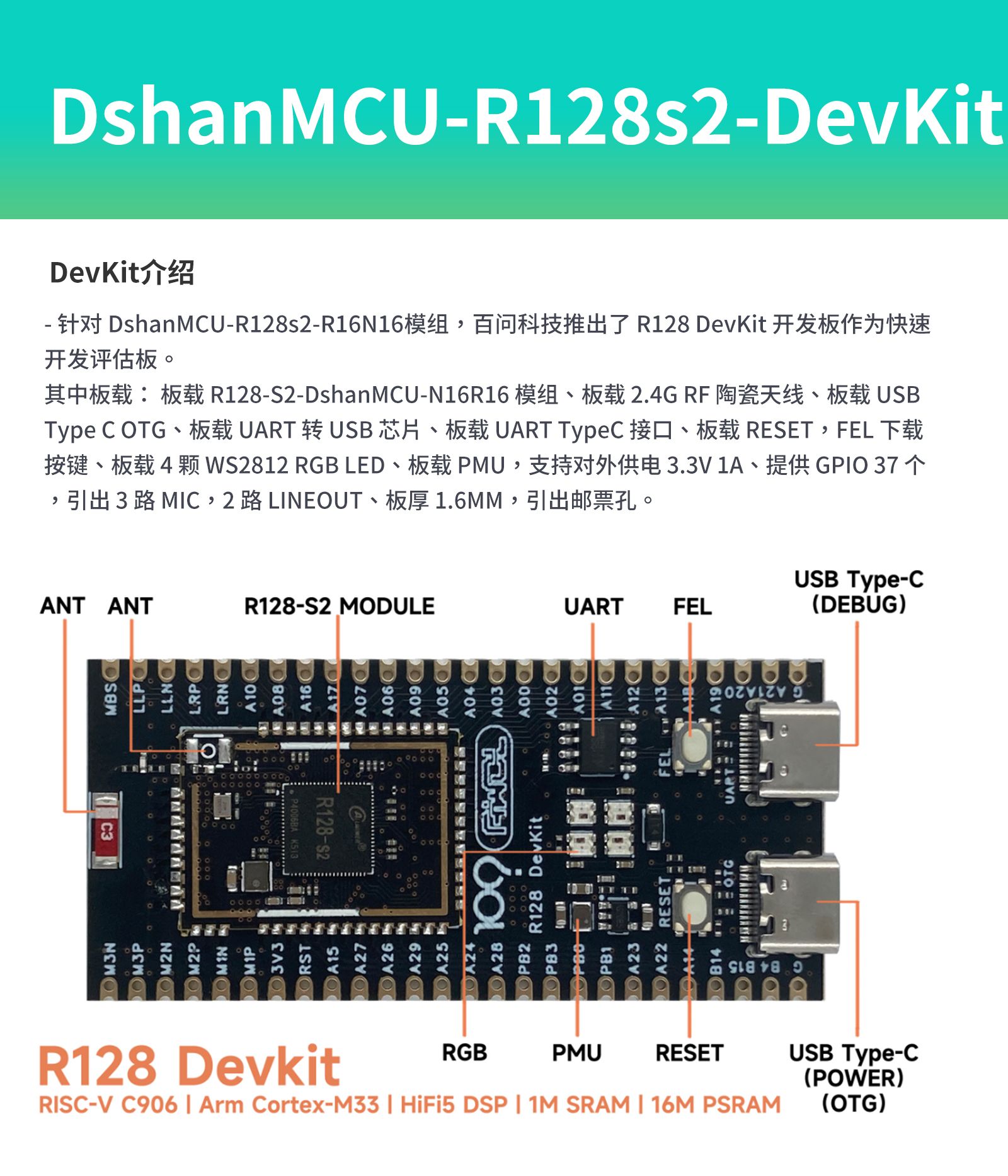

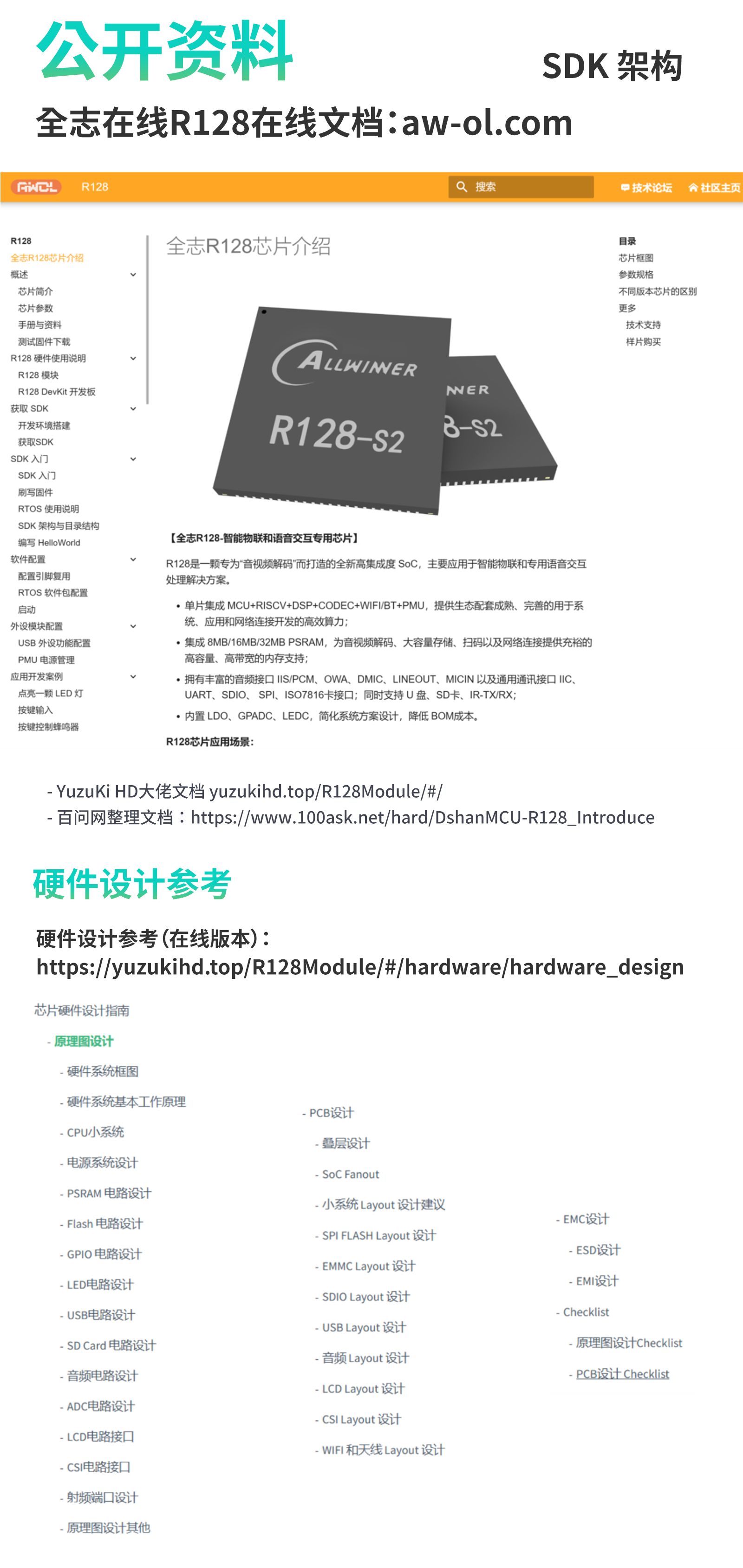

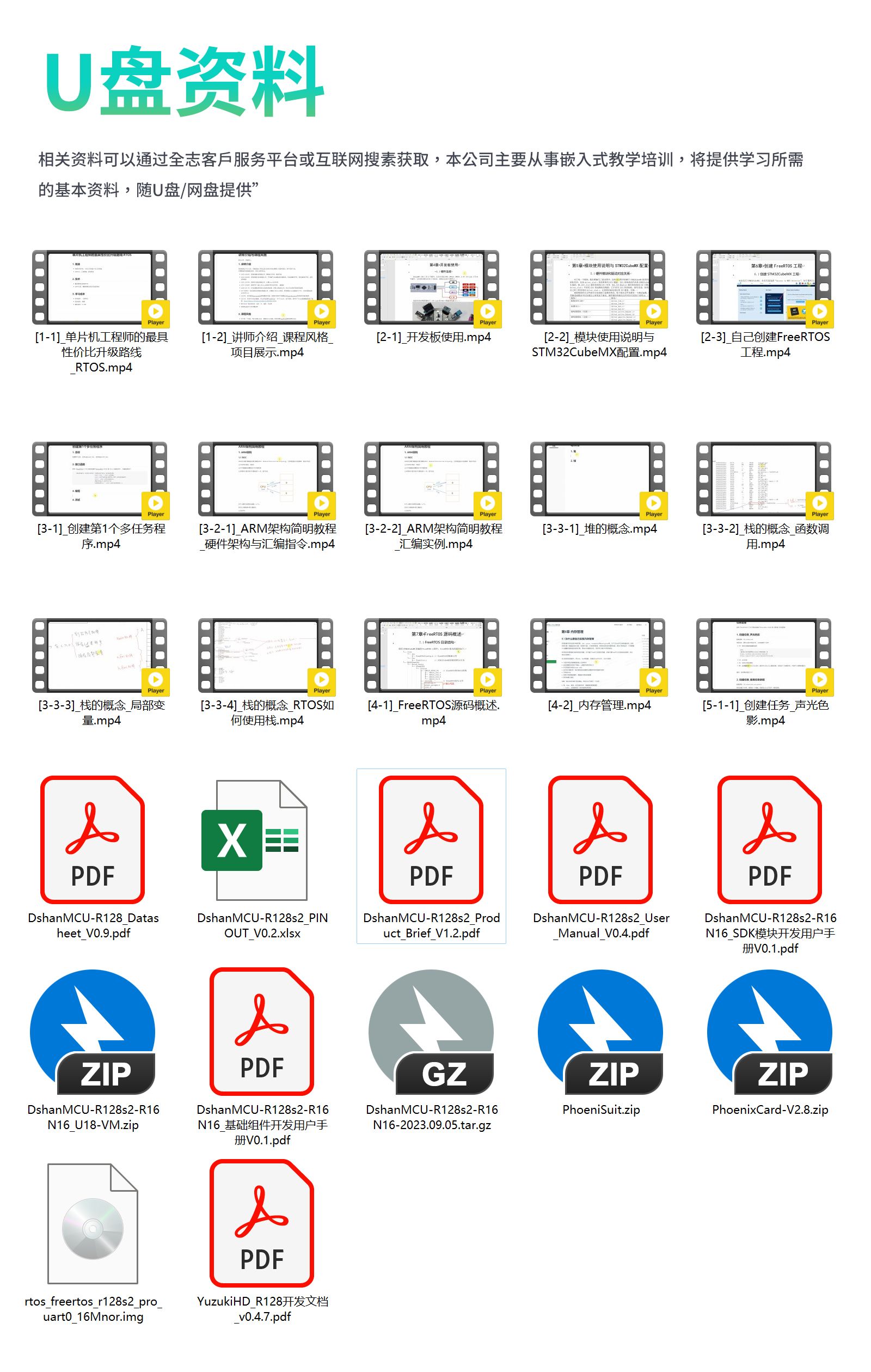

R128入门视频教程来啦!发布在 A Series

视频观看地址:https://www.bilibili.com/video/BV1oC4y1w7AH

获取全志R128开发板:https://item.taobao.com/item.htm?id=736154682975

学习QQ群:318160957 -

回复: 【R128学习案例】R128平衡小车发布在 A Series

@wj8331585 在 【R128学习案例】R128平衡小车 中说:

我这咋什么都没显示出来。

那应该是你的网络问题,我用手机也能预览,如果一直无法查看视频,可以去b站观看:https://www.bilibili.com/video/BV1Fg4y197Vh

-

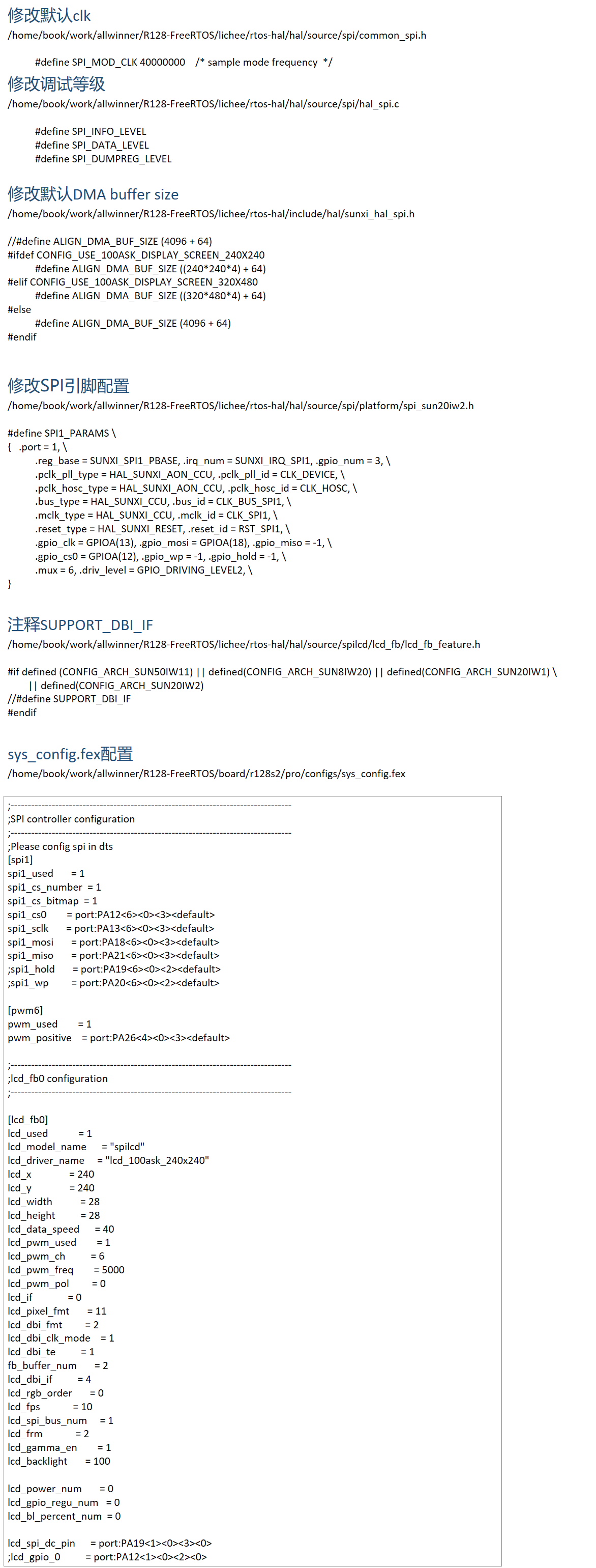

回复: R128适配SPI LCD+LVGL发布在 A Series

这是我的一些笔记:

所使用的补丁:spilcd2.0.zip

修改默认clk /home/book/work/allwinner/R128-FreeRTOS/lichee/rtos-hal/hal/source/spi/common_spi.h #define SPI_MOD_CLK 40000000 /* sample mode frequency */修改调试等级

/home/book/work/allwinner/R128-FreeRTOS/lichee/rtos-hal/hal/source/spi/hal_spi.c #define SPI_INFO_LEVEL #define SPI_DATA_LEVEL #define SPI_DUMPREG_LEVEL修改默认DMA buffer size

/home/book/work/allwinner/R128-FreeRTOS/lichee/rtos-hal/include/hal/sunxi_hal_spi.h //#define ALIGN_DMA_BUF_SIZE (4096 + 64) #ifdef CONFIG_USE_100ASK_DISPLAY_SCREEN_240X240 #define ALIGN_DMA_BUF_SIZE ((240*240*4) + 64) #elif CONFIG_USE_100ASK_DISPLAY_SCREEN_320X480 #define ALIGN_DMA_BUF_SIZE ((320*480*4) + 64) #else #define ALIGN_DMA_BUF_SIZE (4096 + 64) #endif修改SPI引脚配置

/home/book/work/allwinner/R128-FreeRTOS/lichee/rtos-hal/hal/source/spi/platform/spi_sun20iw2.h #define SPI1_PARAMS \ { .port = 1, \ .reg_base = SUNXI_SPI1_PBASE, .irq_num = SUNXI_IRQ_SPI1, .gpio_num = 3, \ .pclk_pll_type = HAL_SUNXI_AON_CCU, .pclk_pll_id = CLK_DEVICE, \ .pclk_hosc_type = HAL_SUNXI_AON_CCU, .pclk_hosc_id = CLK_HOSC, \ .bus_type = HAL_SUNXI_CCU, .bus_id = CLK_BUS_SPI1, \ .mclk_type = HAL_SUNXI_CCU, .mclk_id = CLK_SPI1, \ .reset_type = HAL_SUNXI_RESET, .reset_id = RST_SPI1, \ .gpio_clk = GPIOA(13), .gpio_mosi = GPIOA(18), .gpio_miso = -1, \ .gpio_cs0 = GPIOA(12), .gpio_wp = -1, .gpio_hold = -1, \ .mux = 6, .driv_level = GPIO_DRIVING_LEVEL2, \ }注释SUPPORT_DBI_IF

/home/book/work/allwinner/R128-FreeRTOS/lichee/rtos-hal/hal/source/spilcd/lcd_fb/lcd_fb_feature.h #if defined (CONFIG_ARCH_SUN50IW11) || defined(CONFIG_ARCH_SUN8IW20) || defined(CONFIG_ARCH_SUN20IW1) \ || defined(CONFIG_ARCH_SUN20IW2) //#define SUPPORT_DBI_IF #endifsys_config.fex配置

/home/book/work/allwinner/R128-FreeRTOS/board/r128s2/pro/configs/sys_config.fex ;---------------------------------------------------------------------------------- ;SPI controller configuration ;---------------------------------------------------------------------------------- ;Please config spi in dts [spi1] spi1_used = 1 spi1_cs_number = 1 spi1_cs_bitmap = 1 spi1_cs0 = port:PA12<6><0><3><default> spi1_sclk = port:PA13<6><0><3><default> spi1_mosi = port:PA18<6><0><3><default> spi1_miso = port:PA21<6><0><3><default> ;spi1_hold = port:PA19<6><0><2><default> ;spi1_wp = port:PA20<6><0><2><default> [pwm6] pwm_used = 1 pwm_positive = port:PA26<4><0><3><default> ;---------------------------------------------------------------------------------- ;lcd_fb0 configuration ;---------------------------------------------------------------------------------- [lcd_fb0] lcd_used = 1 lcd_model_name = "spilcd" lcd_driver_name = "lcd_100ask_240x240" lcd_x = 240 lcd_y = 240 lcd_width = 28 lcd_height = 28 lcd_data_speed = 40 lcd_pwm_used = 1 lcd_pwm_ch = 6 lcd_pwm_freq = 5000 lcd_pwm_pol = 0 lcd_if = 0 lcd_pixel_fmt = 11 lcd_dbi_fmt = 2 lcd_dbi_clk_mode = 1 lcd_dbi_te = 1 fb_buffer_num = 2 lcd_dbi_if = 4 lcd_rgb_order = 0 lcd_fps = 10 lcd_spi_bus_num = 1 lcd_frm = 2 lcd_gamma_en = 1 lcd_backlight = 100 lcd_power_num = 0 lcd_gpio_regu_num = 0 lcd_bl_percent_num = 0 lcd_spi_dc_pin = port:PA19<1><0><3><0> ;lcd_gpio_0 = port:PA12<1><0><2><0> -

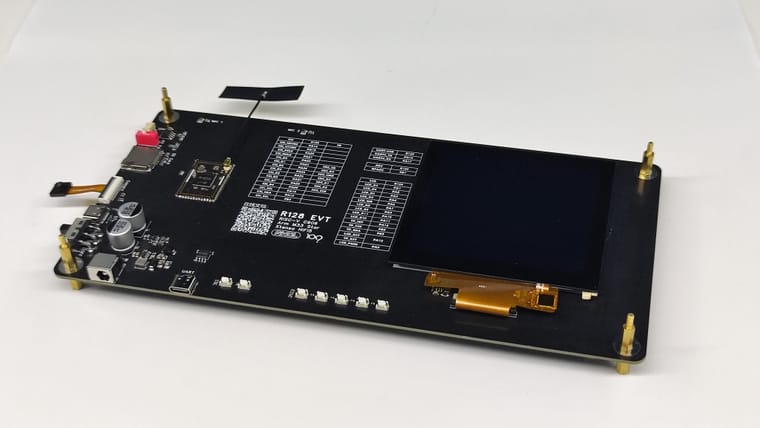

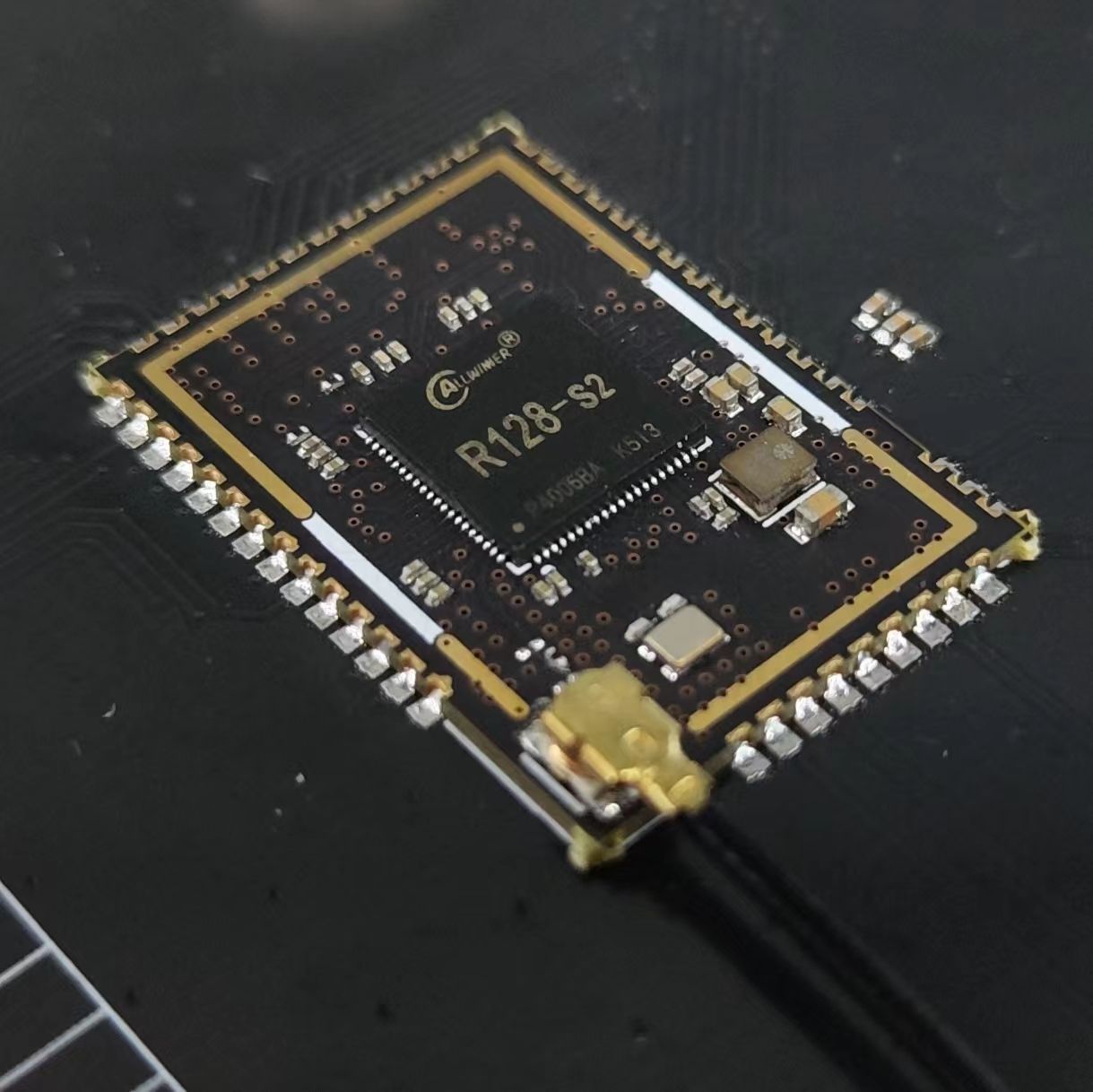

【R128学习案例】R128平衡小车发布在 A Series

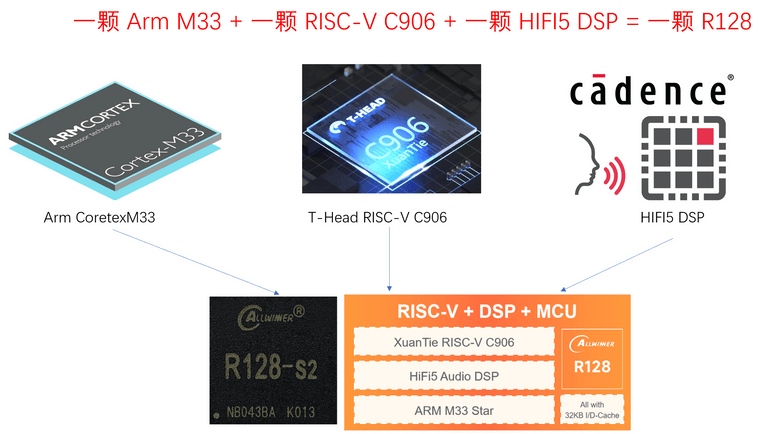

R128是一颗专为“音视频解码”而打造的全新高集成度 SoC,主要应用于智能物联和专用语音交互处理解决方案。

如果做一台能通过发挥R128的wifi&蓝牙特性的平衡小车,从而能通过wifi或蓝牙连接的方式进行控制,那将会是非常有趣的项目!

但是我们还有一个计划,那就是发挥R128的音频处理单元功能,从而能通过语音识别进行控制。试想一下,我们可以动动嘴就能操控小车,这样项目将会更有趣!我们将这个项目命名为: B_ROBOT_100ASK

项目代码及模型文件将会上传到git仓库:- Gitee: https://gitee.com/weidongshan/100ask_r128_demos

- GitHub: https://github.com/100askTeam/100ask_r128_demos

使用的R128硬件(淘宝购买链接):

文档教程阅读地址:

功能特性:

自平衡功能

WiFI控制功能(微信小程序或手机APP)

蓝牙控制功能(微信小程序或手机APP)

语音控制功能最后,希望大家喜欢这个项目,在边玩边学习的同时收获到有用的知识!

-

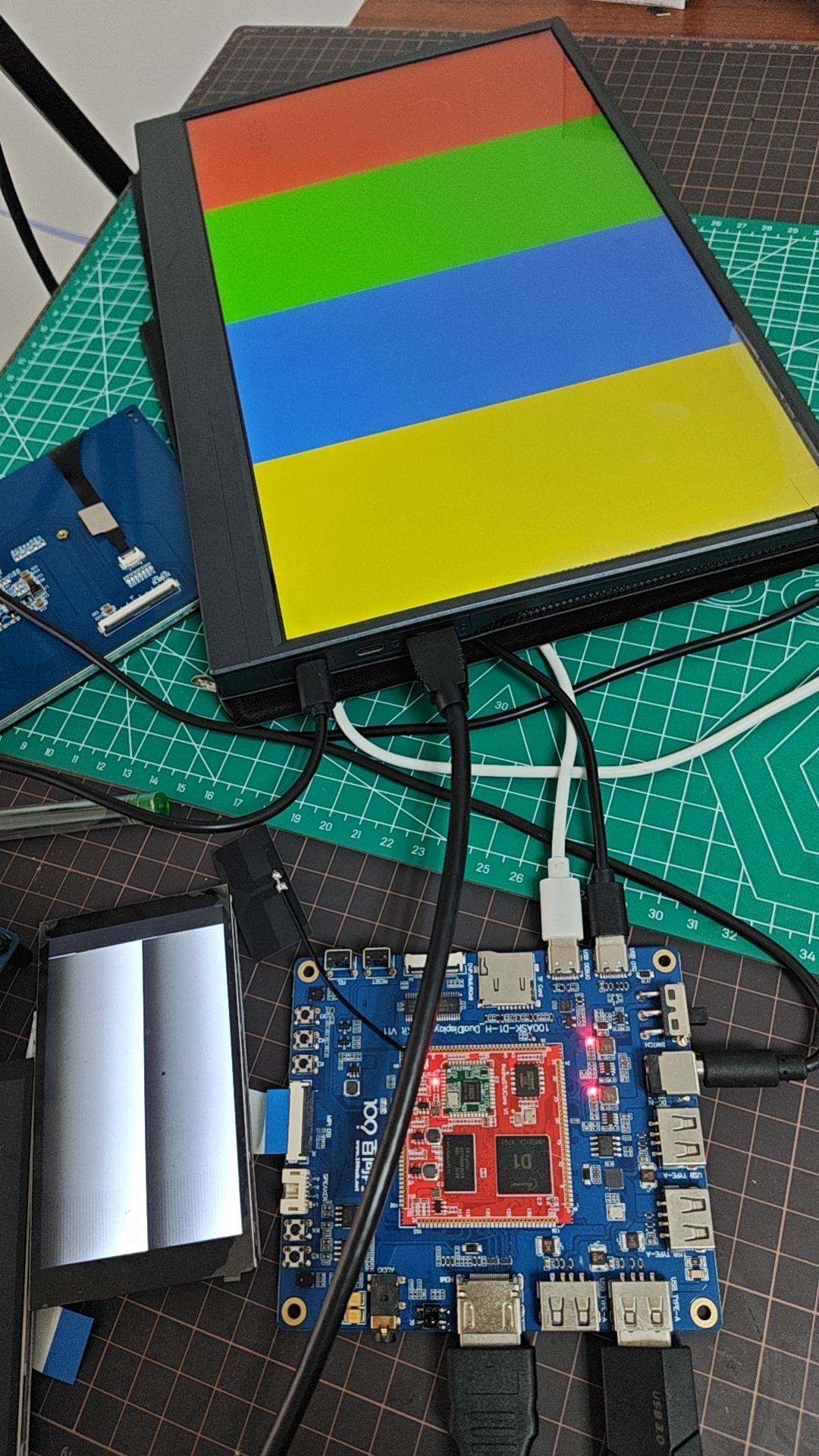

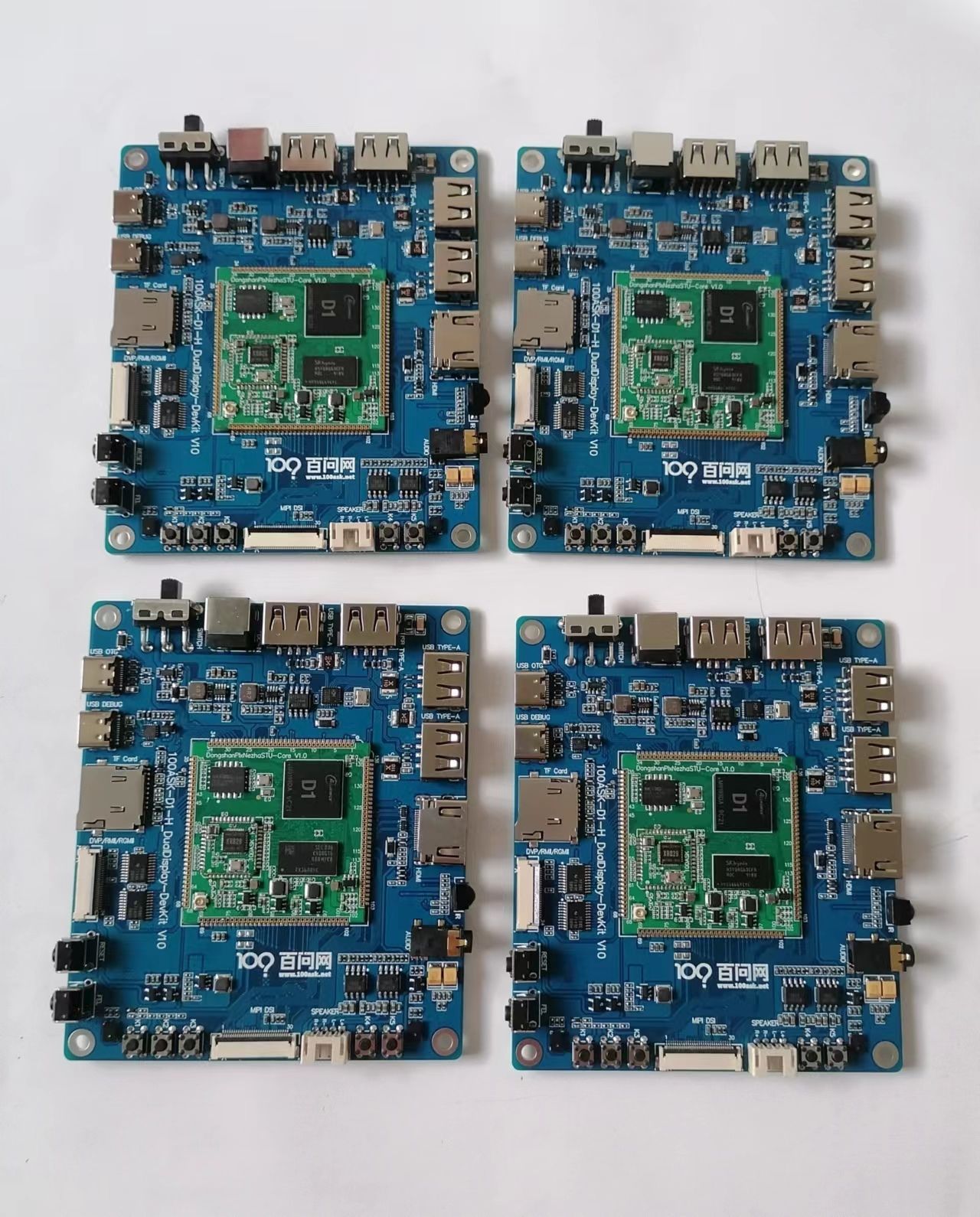

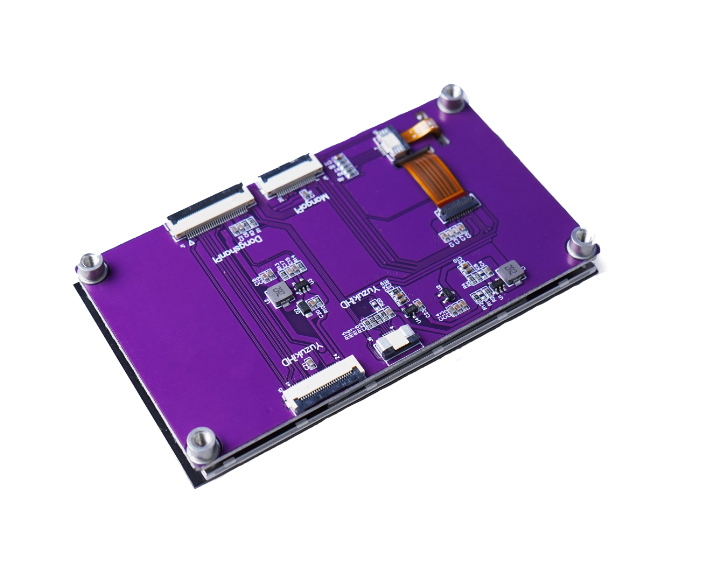

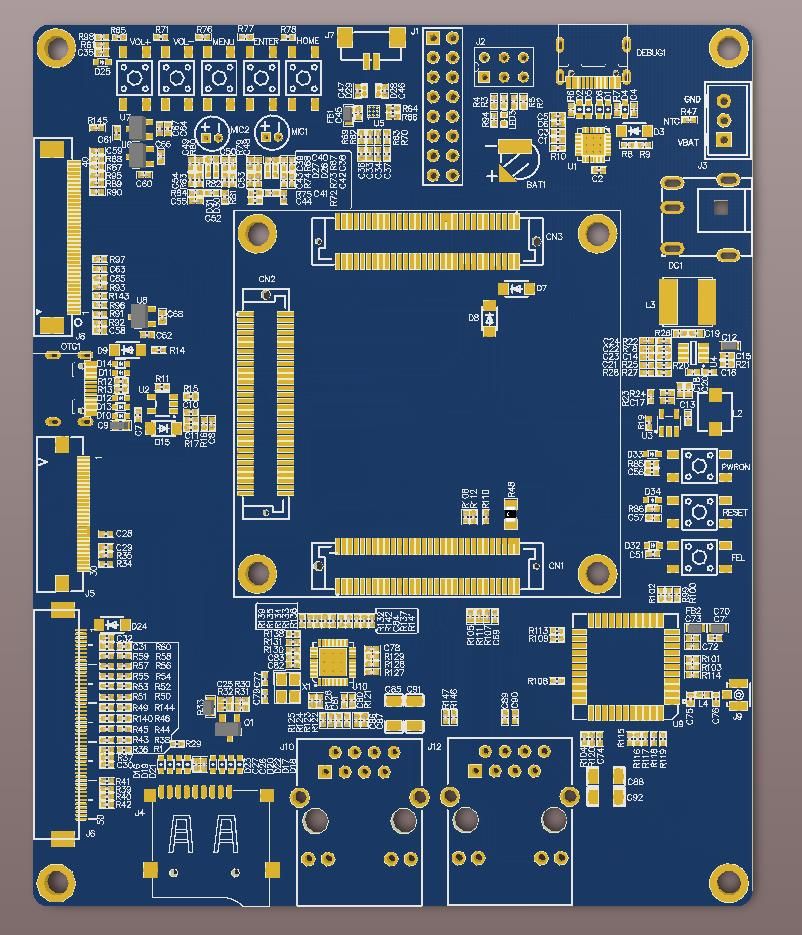

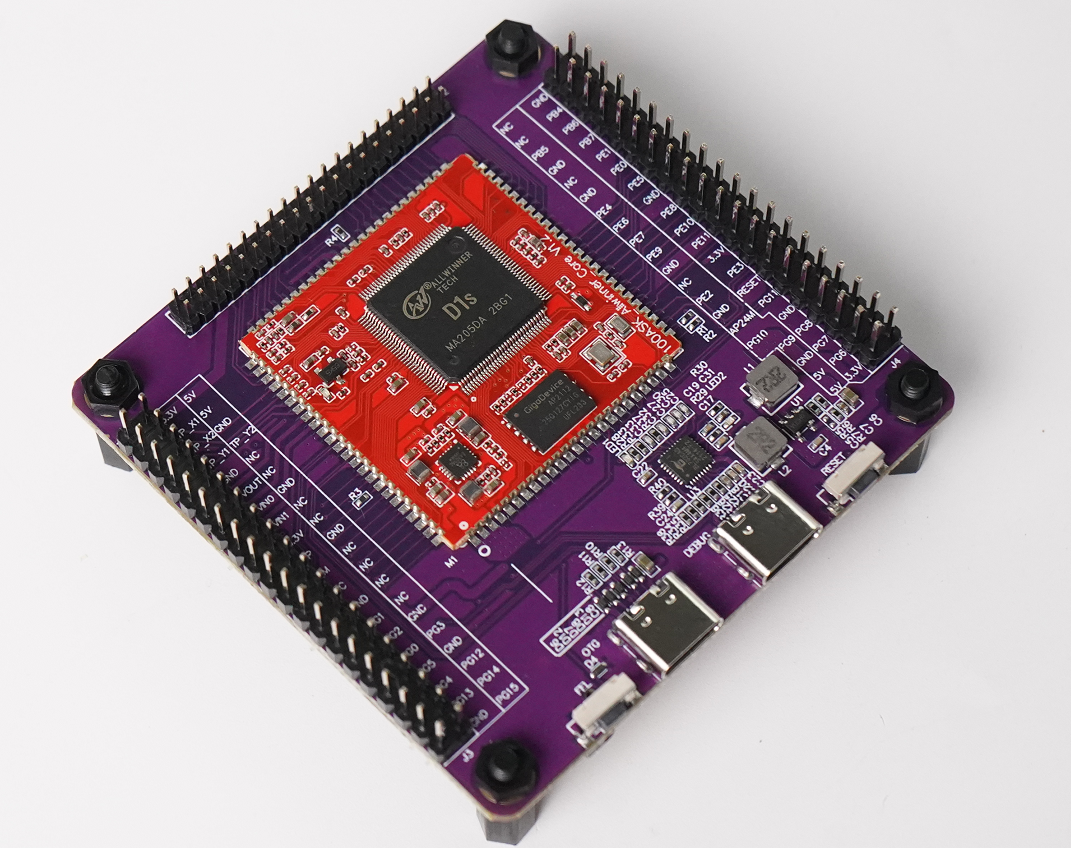

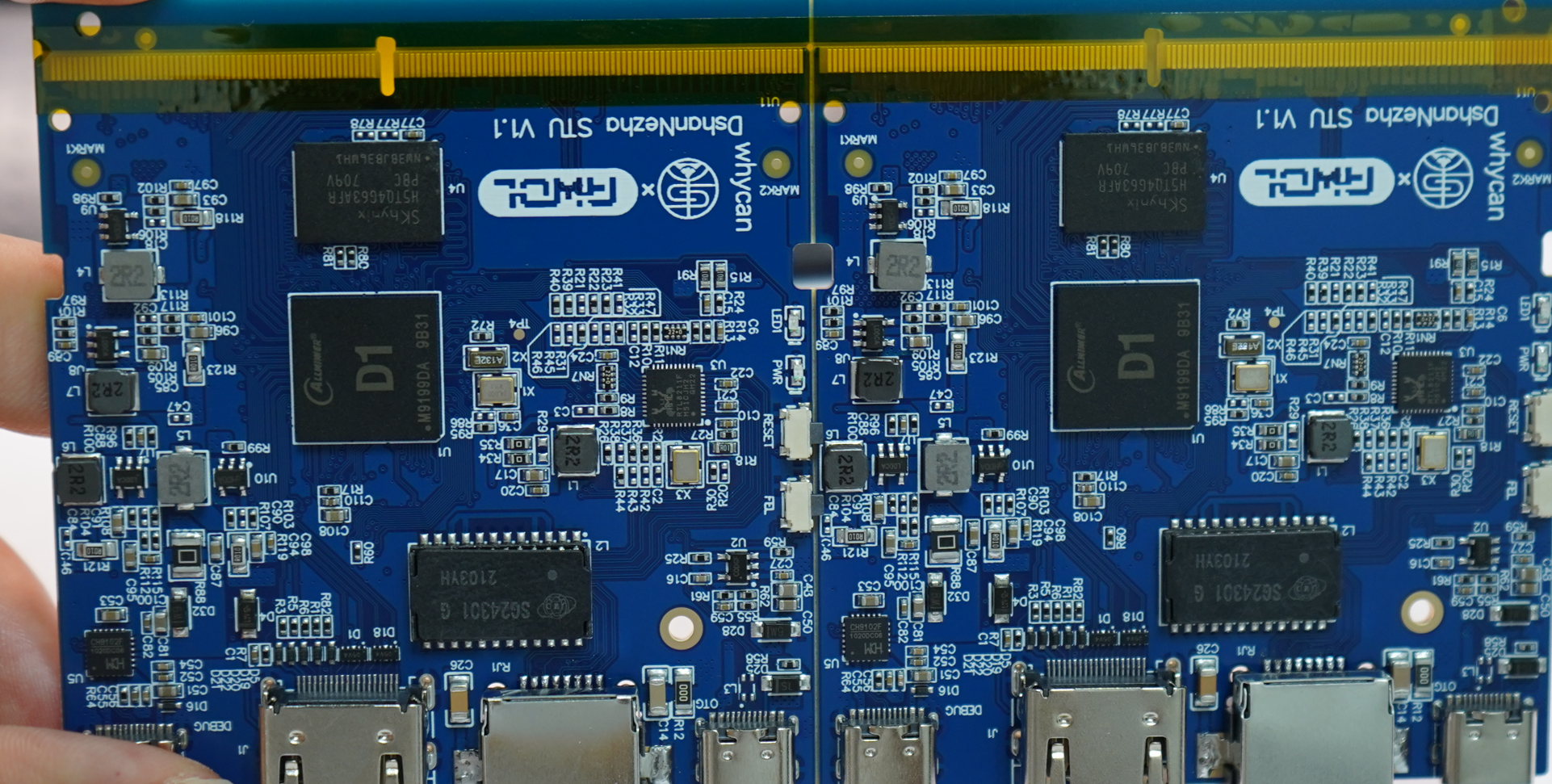

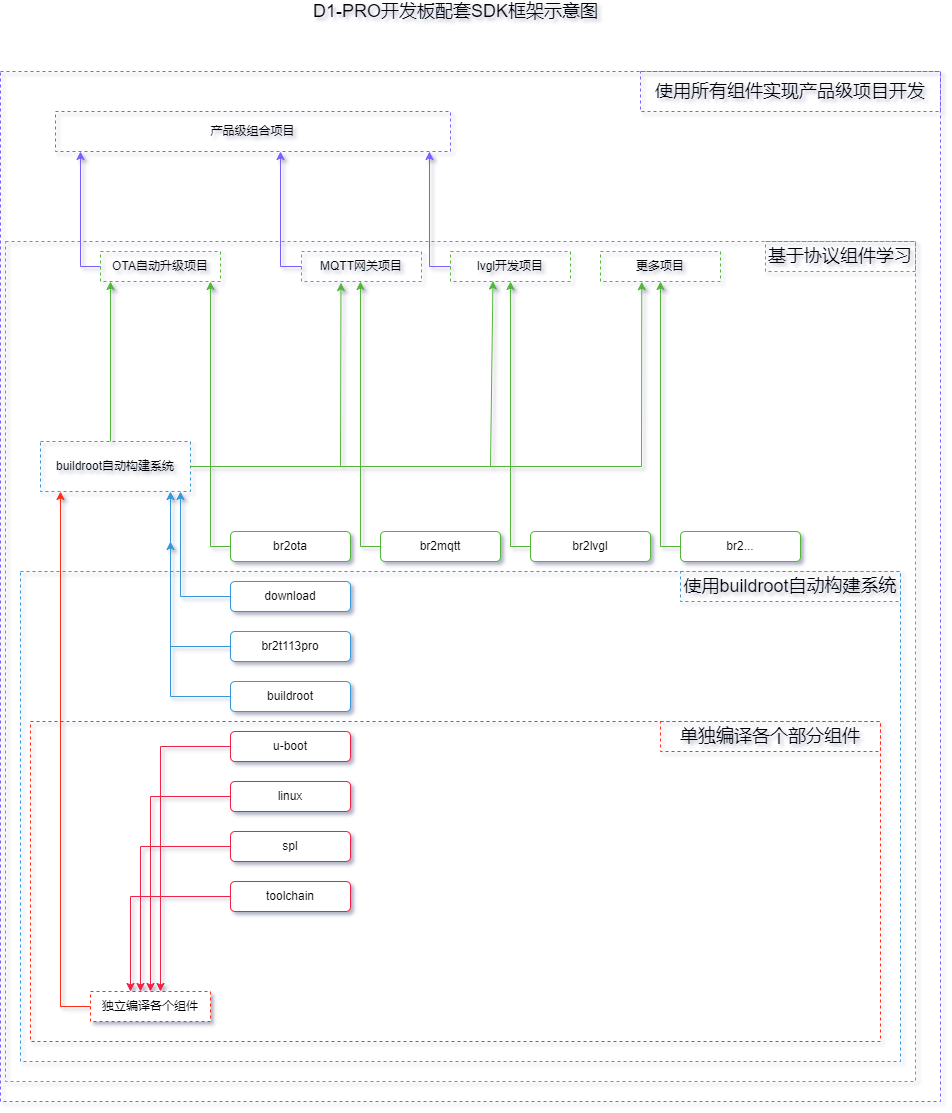

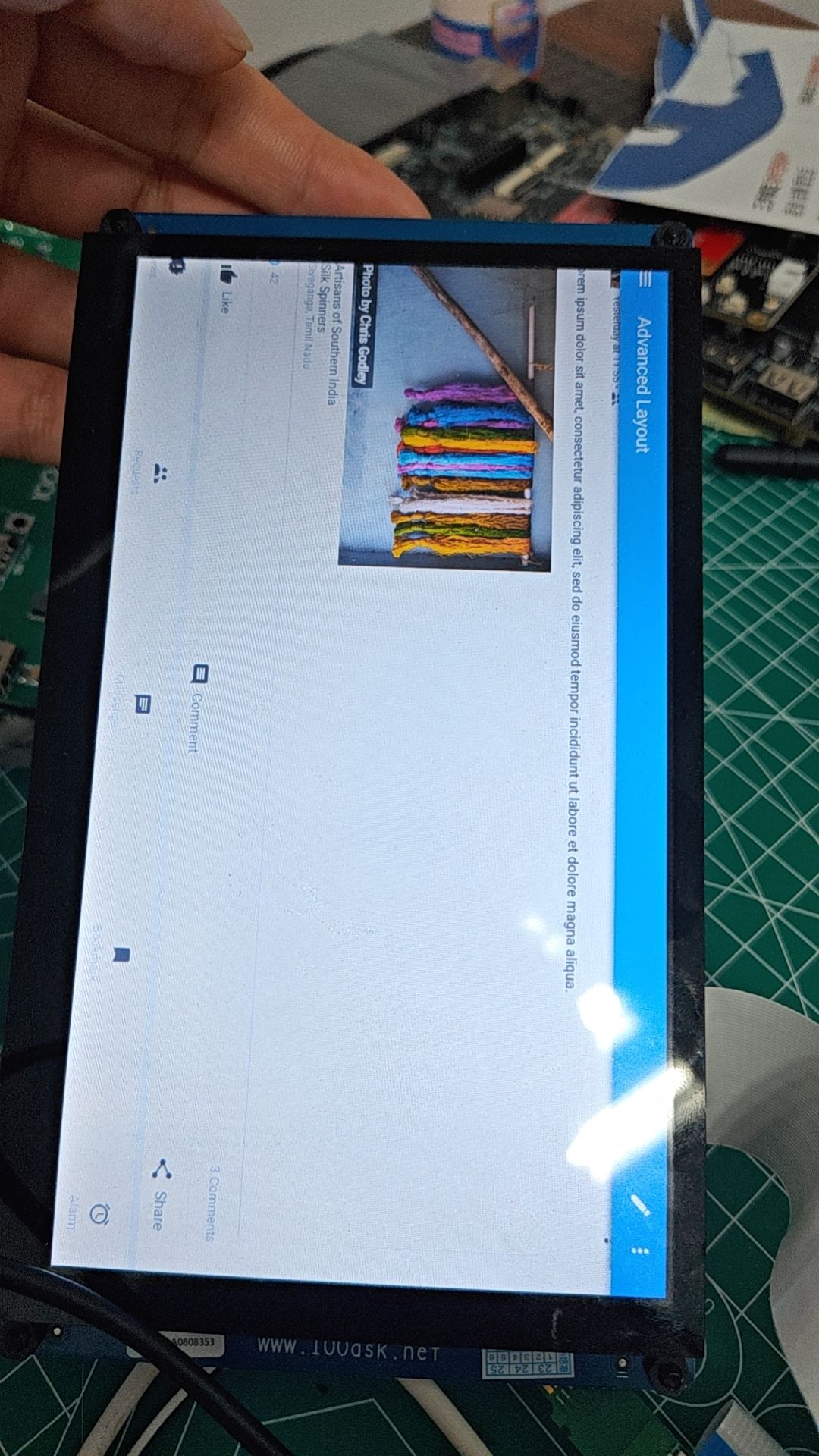

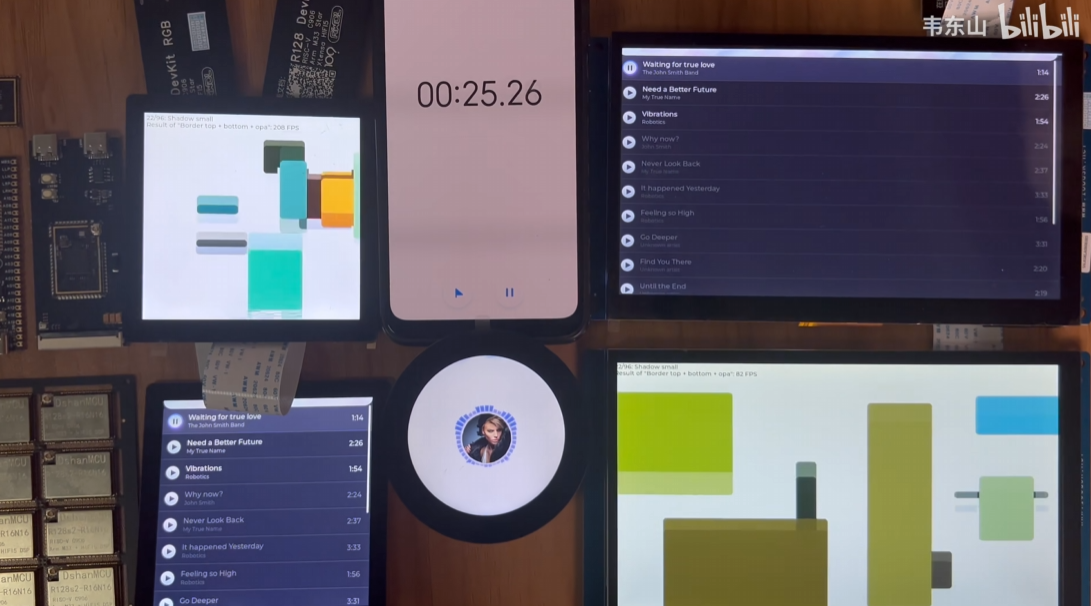

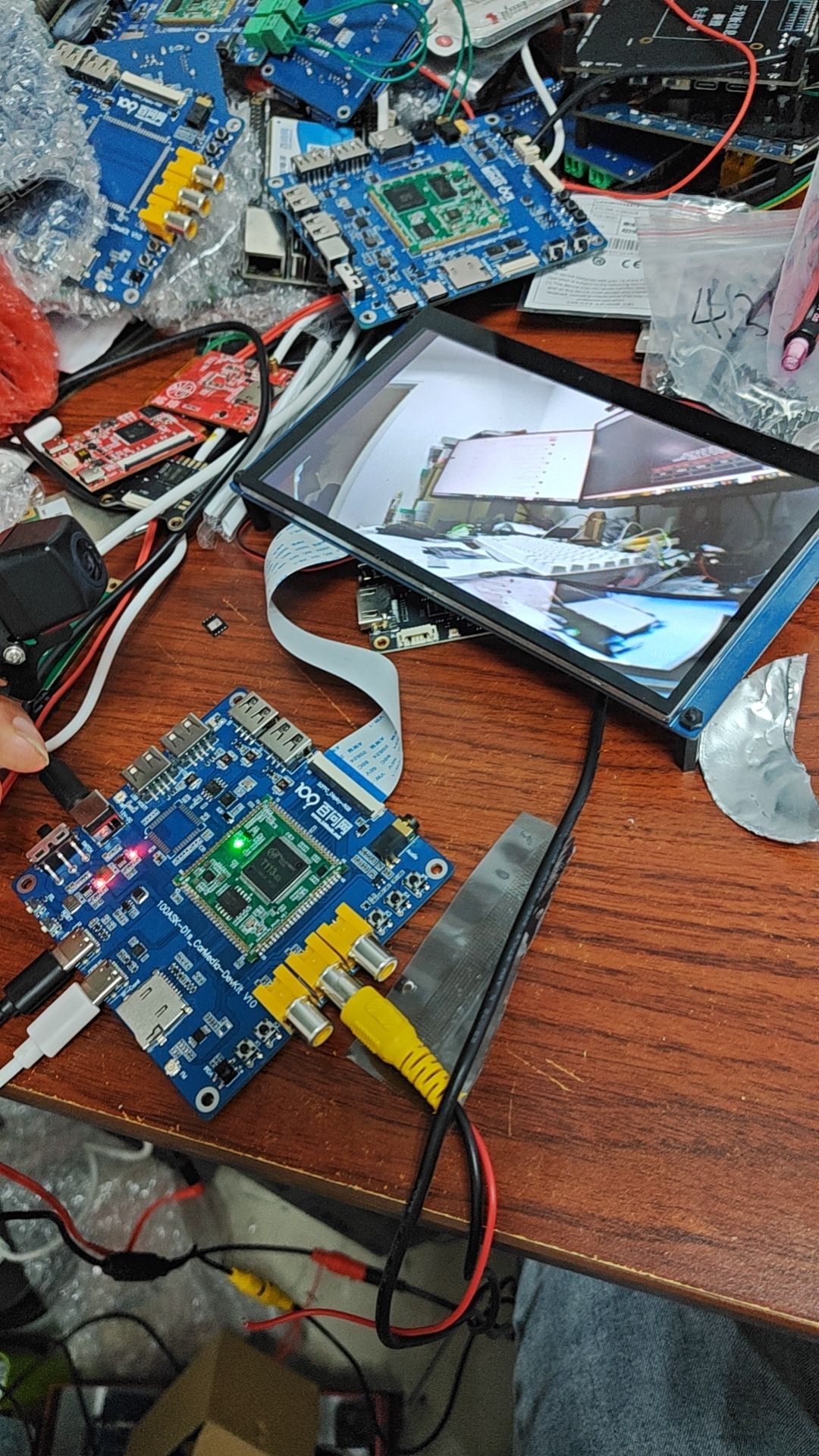

百问网 哪吒D1-H 双屏异显项目板来啦!!!发布在 MR Series

您还在为拿到D1-H不知道可以做什么而苦恼么?

您还在为拿到D1-H不知道学什么而苦恼么?

您的D1-H板还在吃灰么?

这次我们专门针对于D1-H的显示特性,推出了首款D1-H项目板,专门用来学习 双屏异显项目,提供深入的MPP开发教程,显示接口开发教程等,欢迎大家了解! -

回复: 万能的群友,如何才能表达出R128三核异构的独特之处,能做出形象的图我们赠送 R128 DevKit板+U盘资料!发布在 A Series

@baiwen

某位不知名大佬 YuzukiHD 推荐参考这种风格

某位不知名大佬 YuzukiHD 推荐参考这种风格 -

万能的群友,如何才能表达出R128三核异构的独特之处,能做出形象的图我们赠送 R128 DevKit板+U盘资料!发布在 A Series

万能的群友,如何才能表达出R128三核异构的独特之处,能做出形象的表达图 我们将赠送 R128 DevKit板+U盘资料(价值至少300RMB)!

-

回复: 编译buildroot,编译出来的程序没法放到T113上运行。发布在 其它全志芯片讨论区

@shz18877605430 先确认一下T113上使用的 工具链类型是什么,是否有硬浮点支持,还是使用musl C库,如果一致,确认一下 你编译的这个程序是否有相应的 .so 动态库/依赖需要配合着 才能运行!

-

回复: SDK 如何下载发布在 MR Series

参考阿志的SDK教程 ttps://d1.docs.aw-ol.com/study/study_3getsdktoc/

另外建议您放一下出错的截图信息,方便分析 解决问题! -

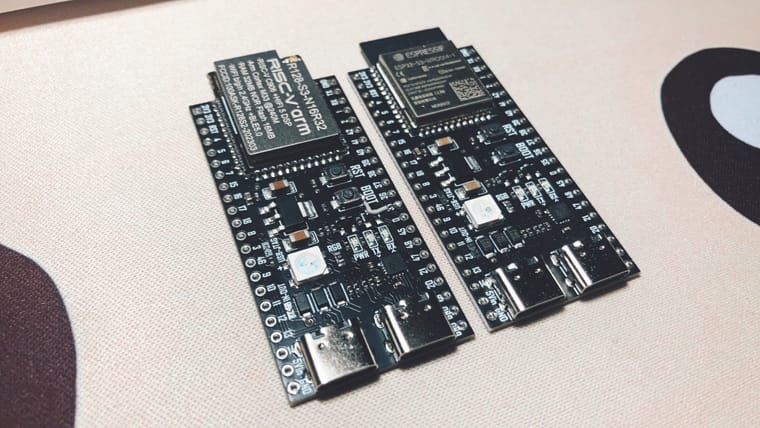

回复: 全志R128开发板来啦!RISC-V C906 + Arm M33有机结合,支持 Wi-Fi/BT发布在 A Series

千呼万唤始出来,前前后后多次改版,多次测验,终于可以上架了,感兴趣的小伙伴 可以优先体验,凭 aw-ol.com账号截图,可以减免 8 元 运费哦! 限量100pcs.

https://item.taobao.com/item.htm?&id=736154682975 -

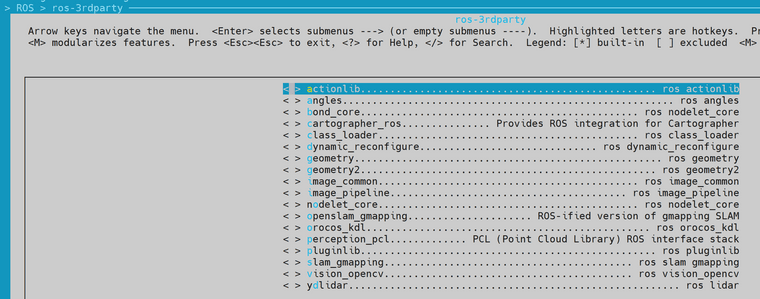

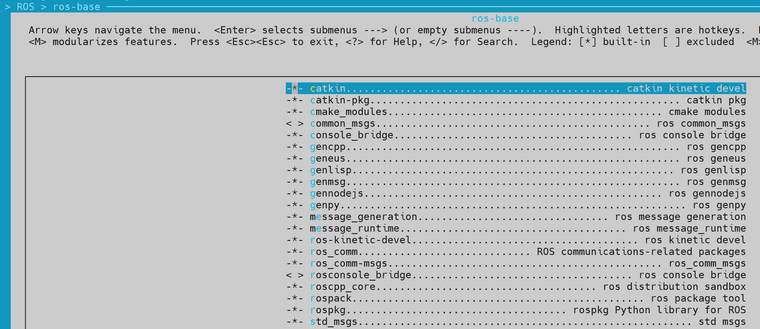

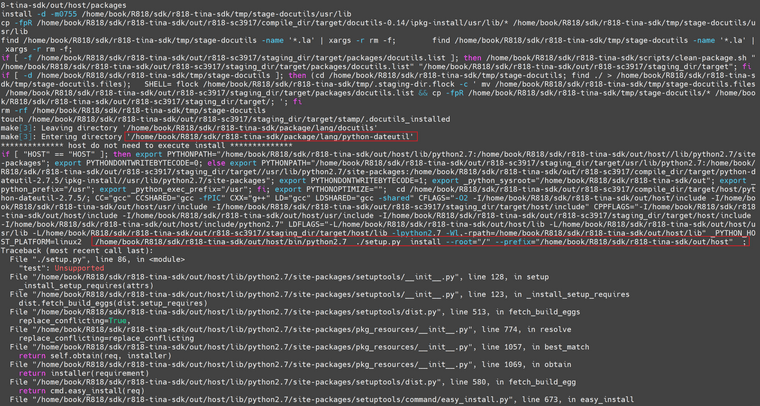

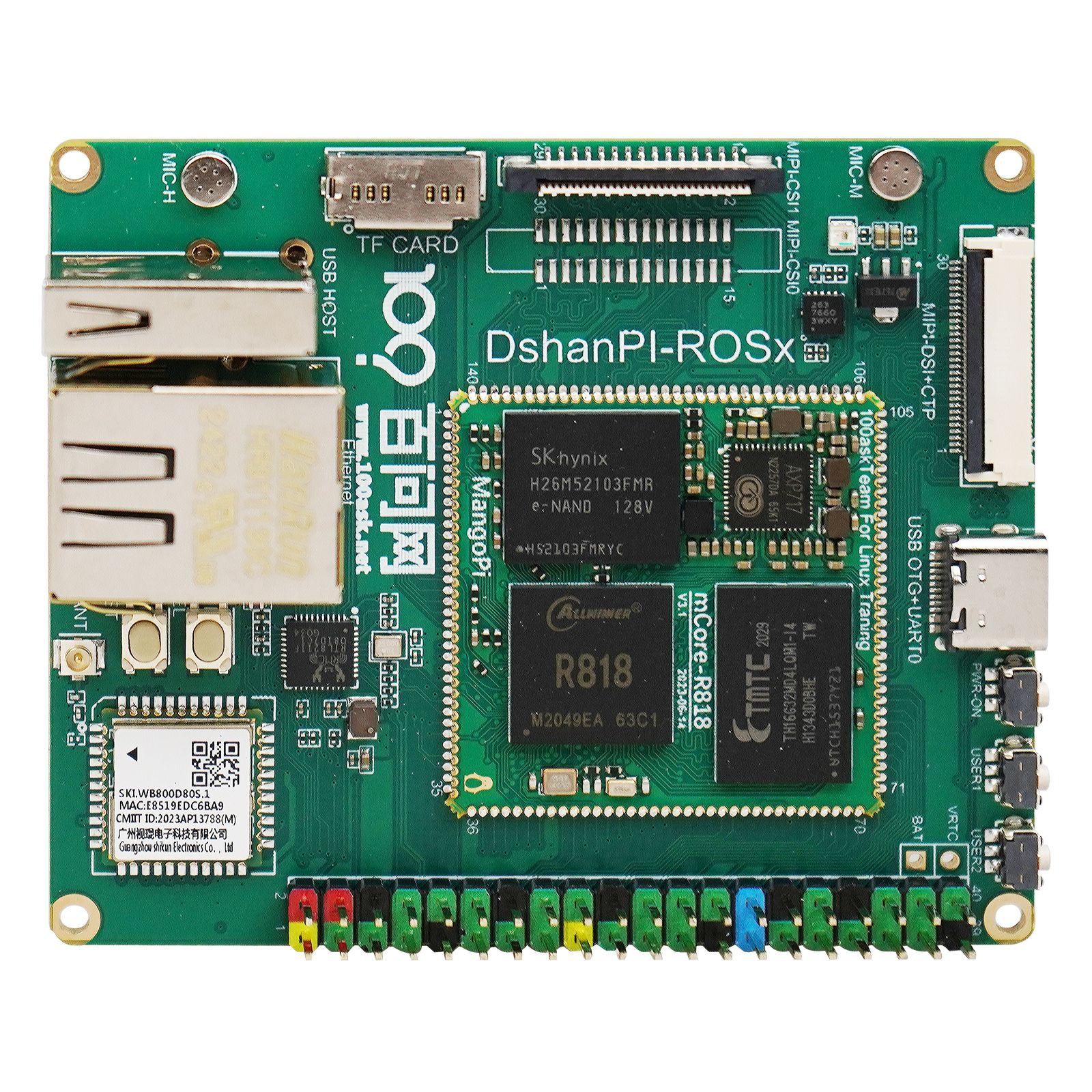

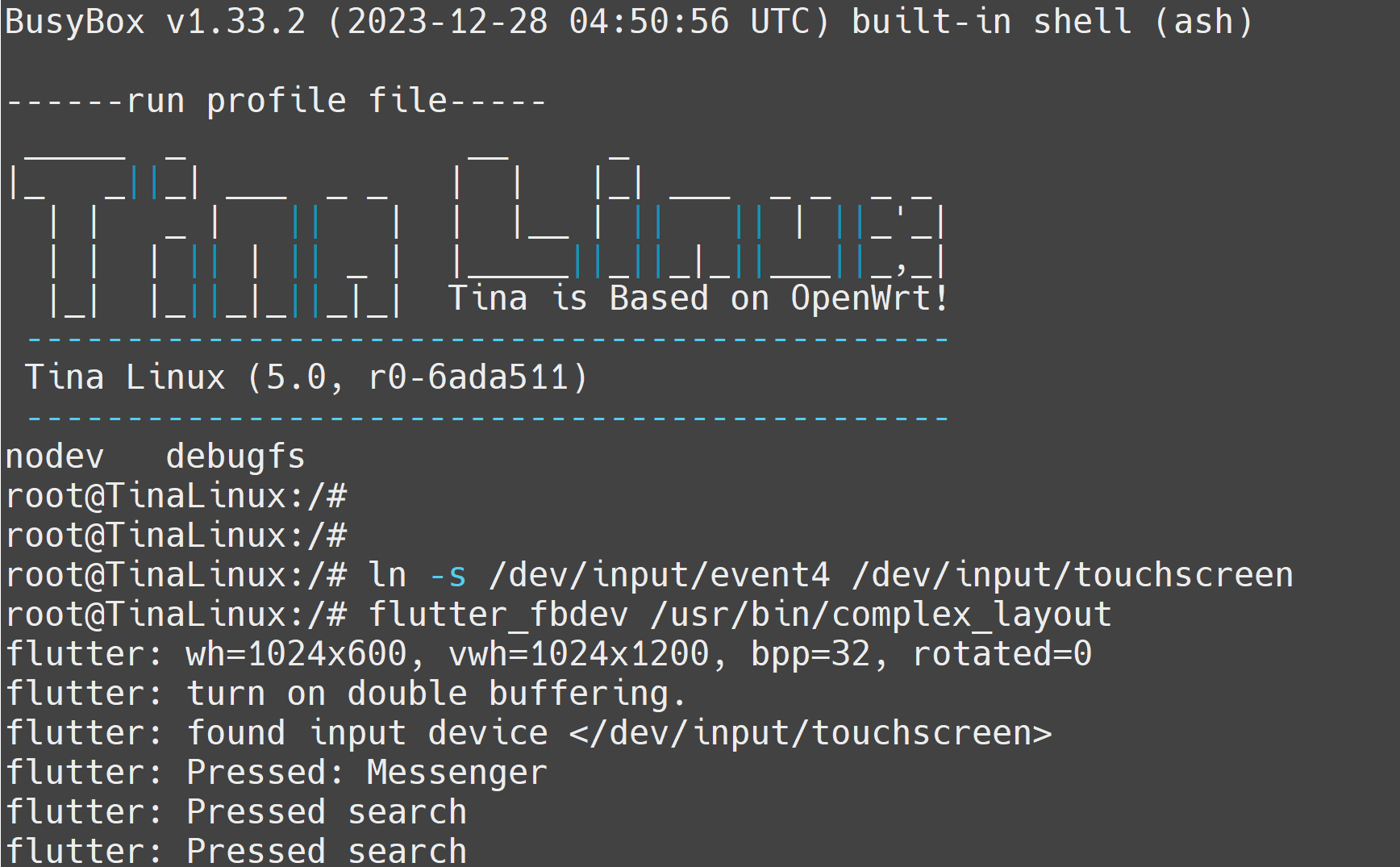

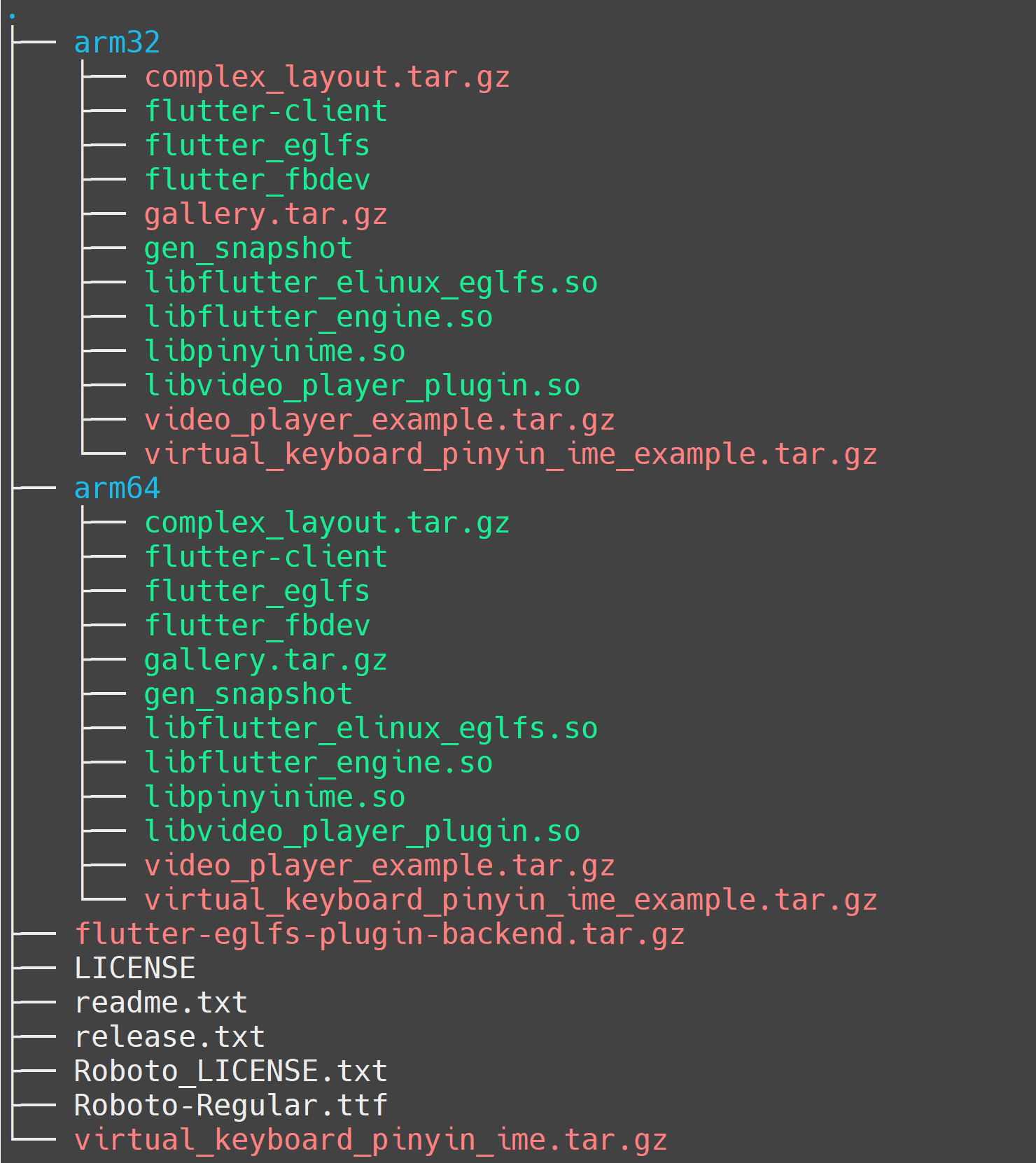

ubuntu 18编译 R818 TinaSDK 2.0 ROS包,提示 host python 错误,有遇到过的同学么?发布在 其它全志芯片讨论区

参考下图配置,使用ubuntu 18环境,尝试 安装了 python pip对应包,解决,发现问题依旧存在,

目前认为是 host端 python存在不兼容问题导致,现尝试更换到Ubuntu 20看是否可以解决

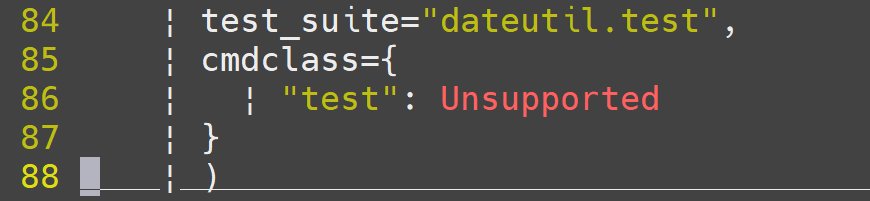

make[3]: Entering directory '/home/book/R818/sdk/r818-tina-sdk/package/lang/python-dateutil' ************** host do not need to execute install ************** if [ "HOST" == "HOST" ]; then export PYTHONPATH="/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7:/home/book/R818/sdk/r818-tina-sdk/out/host//lib/python2.7/site-packages"; export PYTHONDONTWRITEBYTECODE=0; else export PYTHONPATH="/home/book/R818/sdk/r818-tina-sdk/out/r818-sc3917/staging_dir/target/usr/lib/python2.7:/home/book/R818/sdk/r818-tina-sdk/out/r818-sc3917/staging_dir/target//usr/lib/python2.7/site-packages:/home/book/R818/sdk/r818-tina-sdk/out/r818-sc3917/compile_dir/target/python-dateutil-2.7.5/ipkg-install//usr/lib/python2.7/site-packages"; export PYTHONDONTWRITEBYTECODE=1; export _python_sysroot="/home/book/R818/sdk/r818-tina-sdk/out"; export _python_prefix="/usr"; export _python_exec_prefix="/usr"; fi; export PYTHONOPTIMIZE=""; cd /home/book/R818/sdk/r818-tina-sdk/out/r818-sc3917/compile_dir/target/host/python-dateutil-2.7.5/; CC="gcc" CCSHARED="gcc -fPIC" CXX="g++" LD="gcc" LDSHARED="gcc -shared" CFLAGS="-O2 -I/home/book/R818/sdk/r818-tina-sdk/out/host/include -I/home/book/R818/sdk/r818-tina-sdk/out/host/usr/include -I/home/book/R818/sdk/r818-tina-sdk/out/r818-sc3917/staging_dir/target/host/include" CPPFLAGS="-I/home/book/R818/sdk/r818-tina-sdk/out/host/include -I/home/book/R818/sdk/r818-tina-sdk/out/host/usr/include -I/home/book/R818/sdk/r818-tina-sdk/out/r818-sc3917/staging_dir/target/host/include -I/home/book/R818/sdk/r818-tina-sdk/out/host/include/python2.7" LDFLAGS="-L/home/book/R818/sdk/r818-tina-sdk/out/host/lib -L/home/book/R818/sdk/r818-tina-sdk/out/host/usr/lib -L/home/book/R818/sdk/r818-tina-sdk/out/r818-sc3917/staging_dir/target/host/lib -lpython2.7 -Wl,-rpath=/home/book/R818/sdk/r818-tina-sdk/out/host/lib" _PYTHON_HOST_PLATFORM=linux2 /home/book/R818/sdk/r818-tina-sdk/out/host/bin/python2.7 ./setup.py install --root="/" --prefix="/home/book/R818/sdk/r818-tina-sdk/out/host" ; Traceback (most recent call last): File "./setup.py", line 86, in <module> "test": Unsupported File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/__init__.py", line 128, in setup _install_setup_requires(attrs) File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/__init__.py", line 123, in _install_setup_requires dist.fetch_build_eggs(dist.setup_requires) File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/dist.py", line 513, in fetch_build_eggs replace_conflicting=True, File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/pkg_resources/__init__.py", line 774, in resolve replace_conflicting=replace_conflicting File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/pkg_resources/__init__.py", line 1057, in best_match return self.obtain(req, installer) File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/pkg_resources/__init__.py", line 1069, in obtain return installer(requirement) File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/dist.py", line 580, in fetch_build_egg return cmd.easy_install(req) File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/command/easy_install.py", line 673, in easy_install return self.install_item(spec, dist.location, tmpdir, deps) File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/command/easy_install.py", line 699, in install_item dists = self.install_eggs(spec, download, tmpdir) File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/command/easy_install.py", line 884, in install_eggs return self.build_and_install(setup_script, setup_base) File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/command/easy_install.py", line 1152, in build_and_install self.run_setup(setup_script, setup_base, args) File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/command/easy_install.py", line 1138, in run_setup run_setup(setup_script, args) File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/sandbox.py", line 253, in run_setup raise File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/contextlib.py", line 35, in __exit__ self.gen.throw(type, value, traceback) File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/sandbox.py", line 195, in setup_context yield File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/contextlib.py", line 35, in __exit__ self.gen.throw(type, value, traceback) File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/sandbox.py", line 166, in save_modules saved_exc.resume() File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/sandbox.py", line 141, in resume six.reraise(type, exc, self._tb) File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/sandbox.py", line 154, in save_modules yield saved File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/sandbox.py", line 195, in setup_context yield File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/sandbox.py", line 250, in run_setup _execfile(setup_script, ns) File "/home/book/R818/sdk/r818-tina-sdk/out/host/lib/python2.7/site-packages/setuptools/sandbox.py", line 44, in _execfile code = compile(script, filename, 'exec') File "/tmp/easy_install-6NxiQu/setuptools_scm-7.1.0/setup.py", line 20 def scm_version() -> str: ^ SyntaxError: invalid syntax Makefile:65: recipe for target '/home/book/R818/sdk/r818-tina-sdk/out/r818-sc3917/compile_dir/target/host/python-dateutil-2.7.5/.built' failed make[3]: *** [/home/book/R818/sdk/r818-tina-sdk/out/r818-sc3917/compile_dir/target/host/python-dateutil-2.7.5/.built] Error 1 make[3]: Leaving directory '/home/book/R818/sdk/r818-tina-sdk/package/lang/python-dateutil' package/Makefile:192: recipe for target 'package/lang/python-dateutil/host/compile' failed make[2]: *** [package/lang/python-dateutil/host/compile] Error 2 make[2]: Leaving directory '/home/book/R818/sdk/r818-tina-sdk'

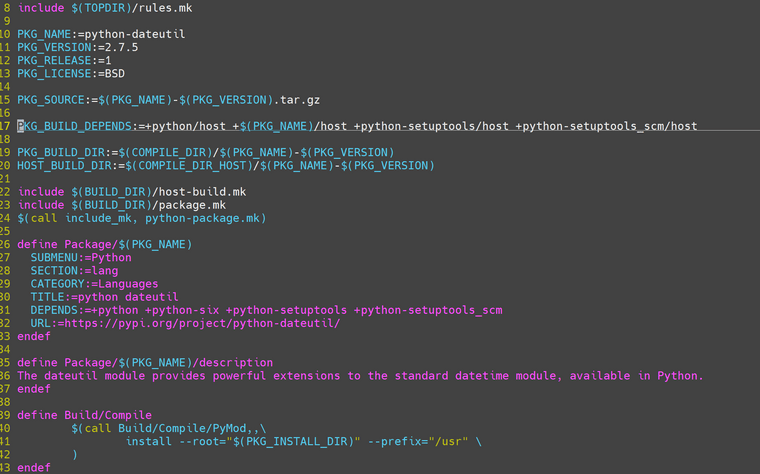

查看了包的Makefile规则

找到软件包源码报错位置 out/r818-sc3917/compile_dir/target/host/python-dateutil-2.7.5/setup.py

我的主机环境这里 python 2.7 python3 都有

-

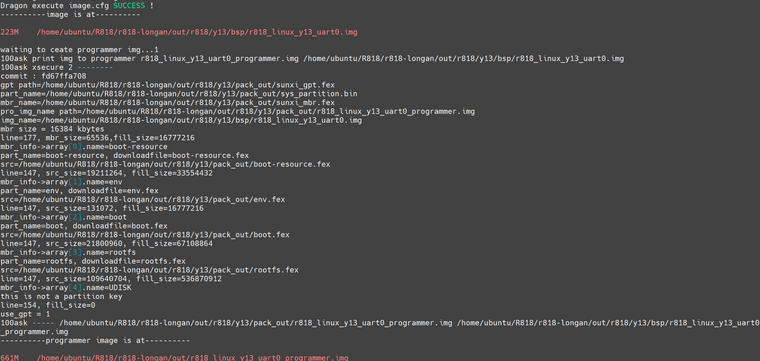

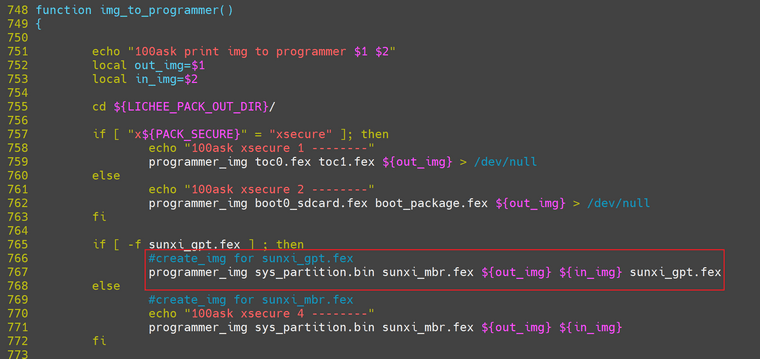

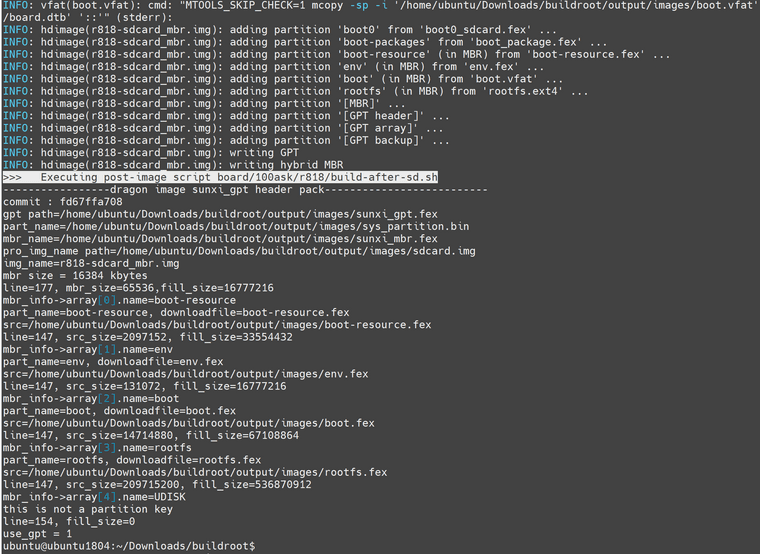

回复: mCore R818使用genimage 打包镜像通过dd if烧录 提示如下错误!发布在 其它全志芯片讨论区

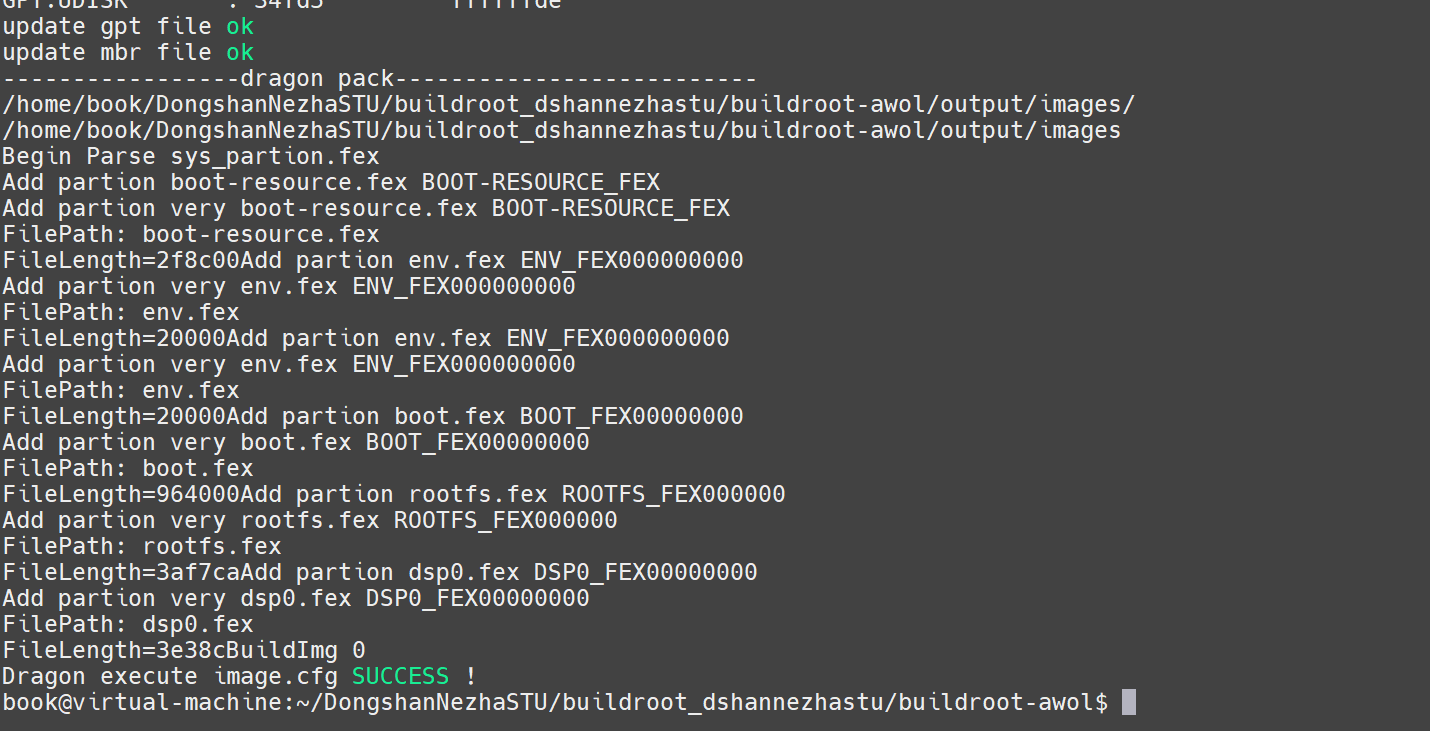

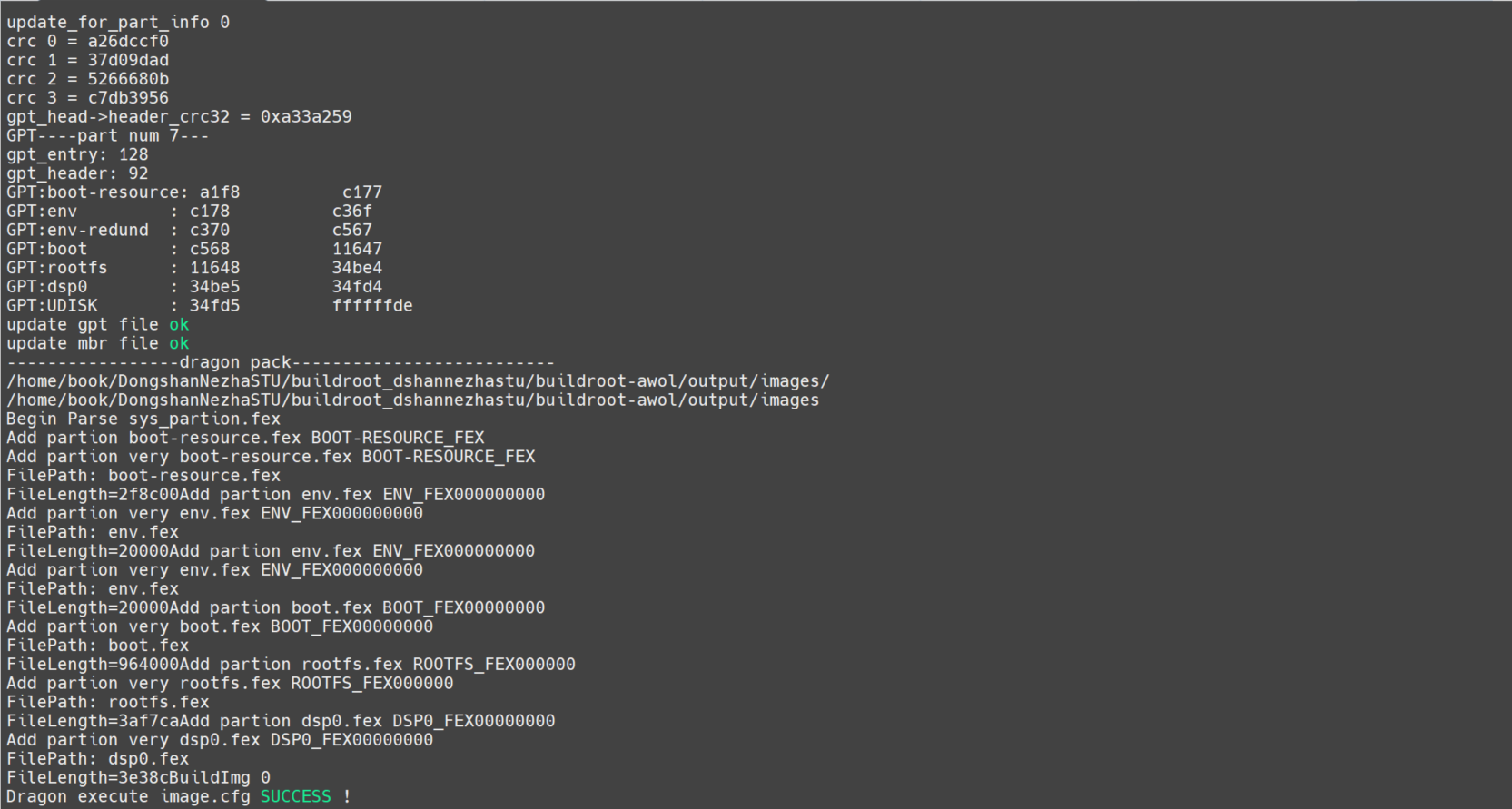

@awwwwa 感谢大佬的回复,我通过分析 build/pack 使用 ./build.sh packraw

找到了下面那个最终生成的命令

然后把 programmer_img 丢进 buildroot 打包目录,直接编译打包,生成的镜像就可以直接用啦!

sunxi_gpt这个我学习一下 怎么融进去 让他自己转换打包。

不得不说,这个 programmer_img 很强大,但是里面怎么实现的我很好奇,当时修改了各种 genimage.cfg的分区类型和头部都不行。

-

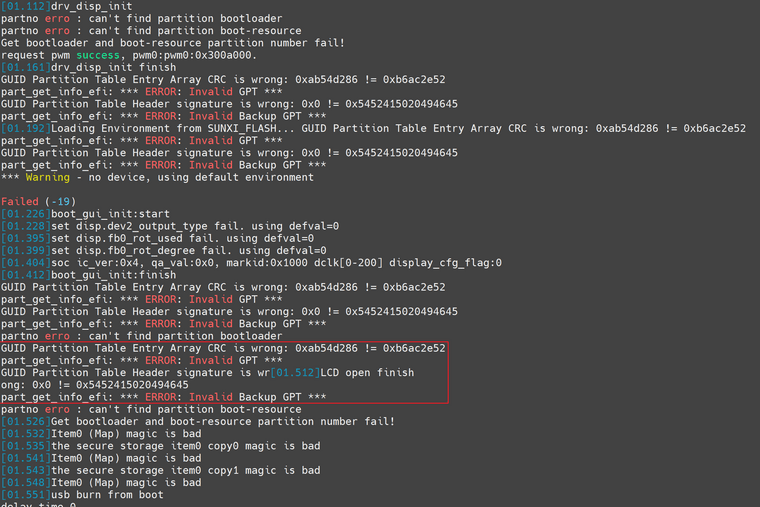

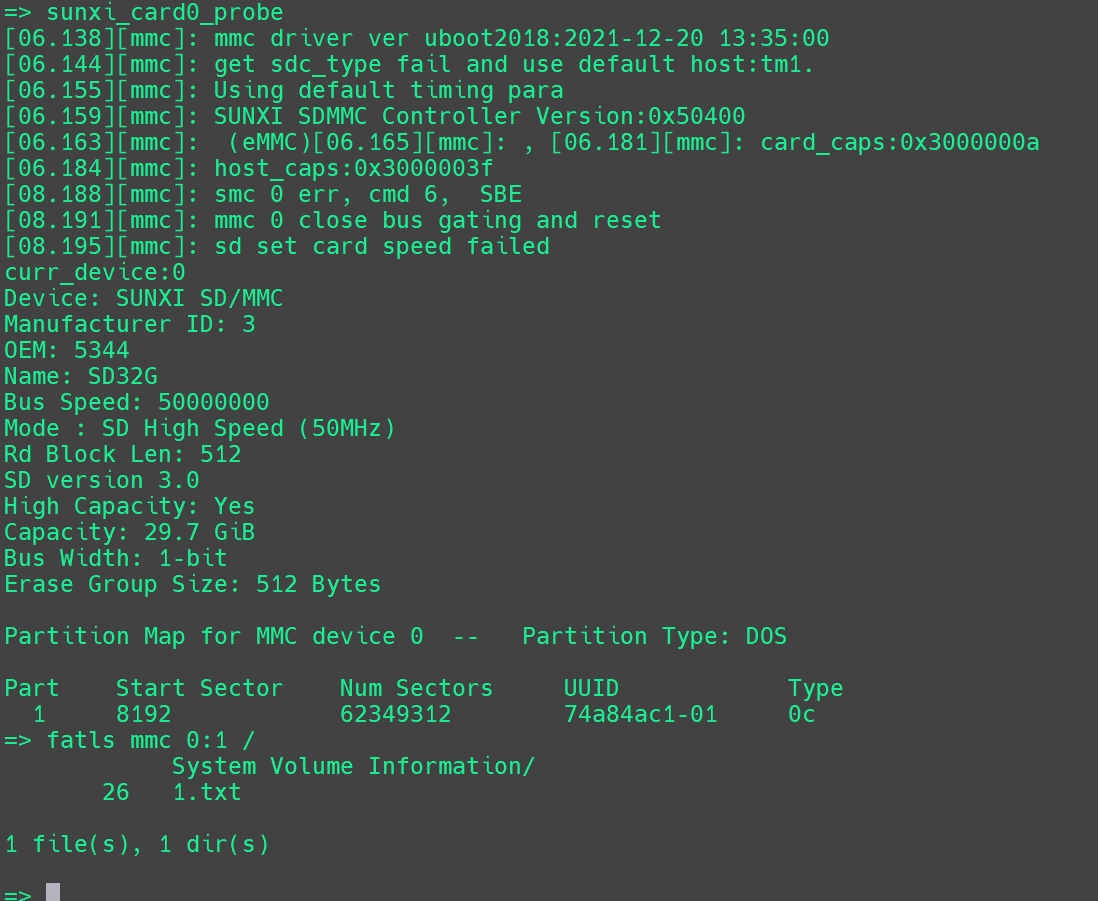

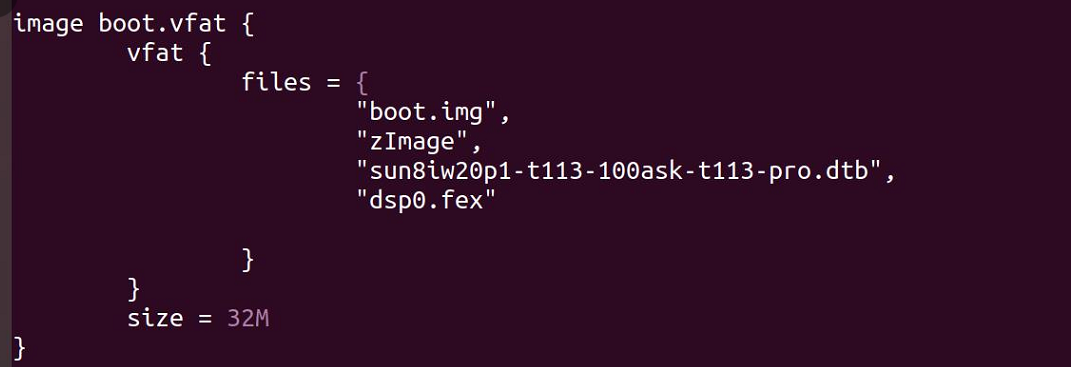

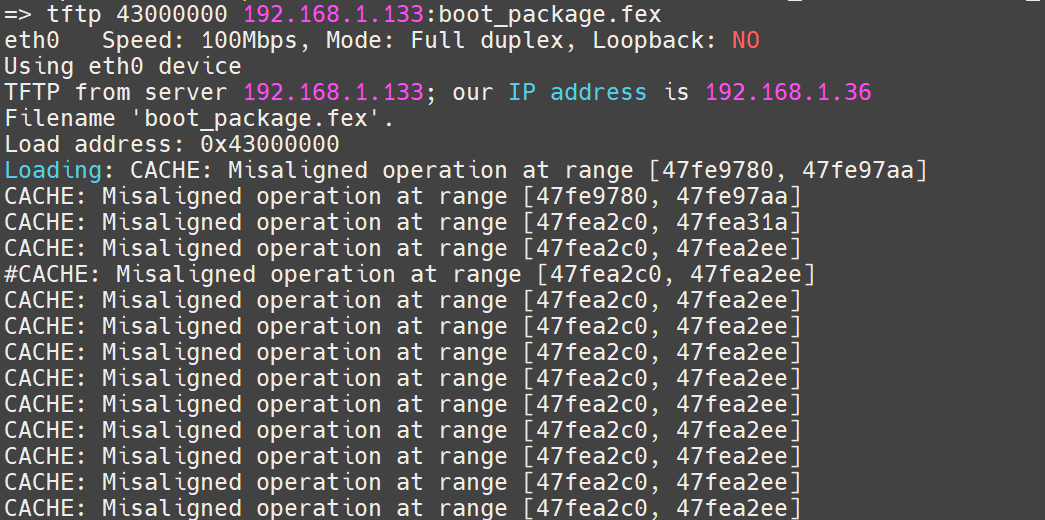

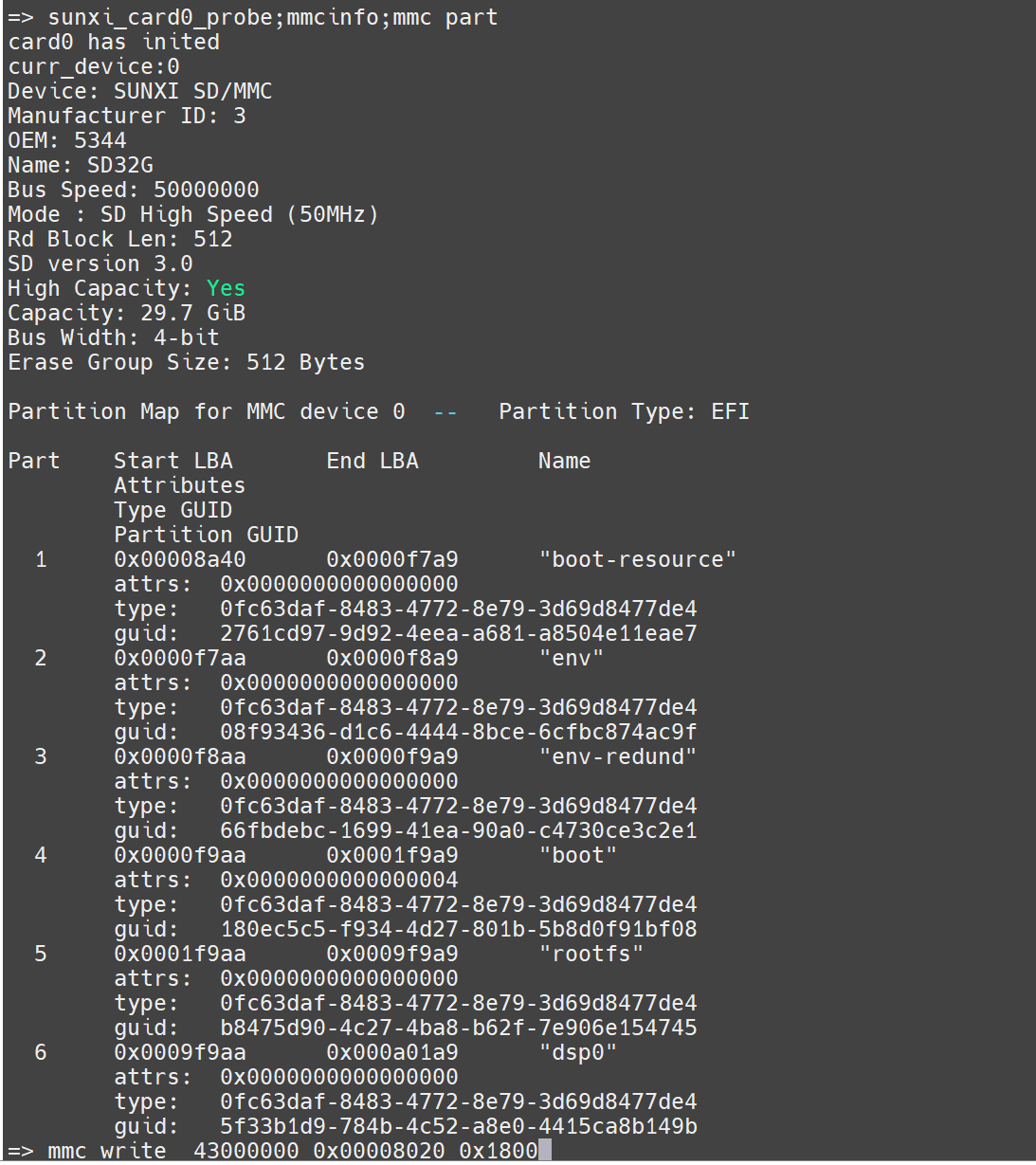

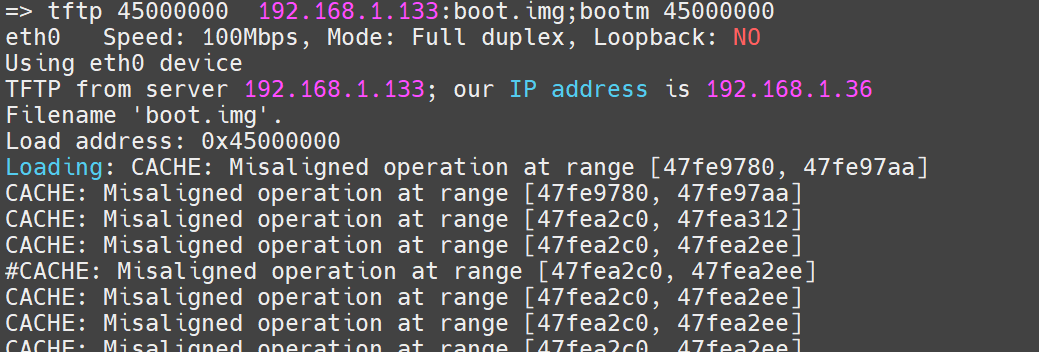

mCore R818使用genimage 打包镜像通过dd if烧录 提示如下错误!发布在 其它全志芯片讨论区

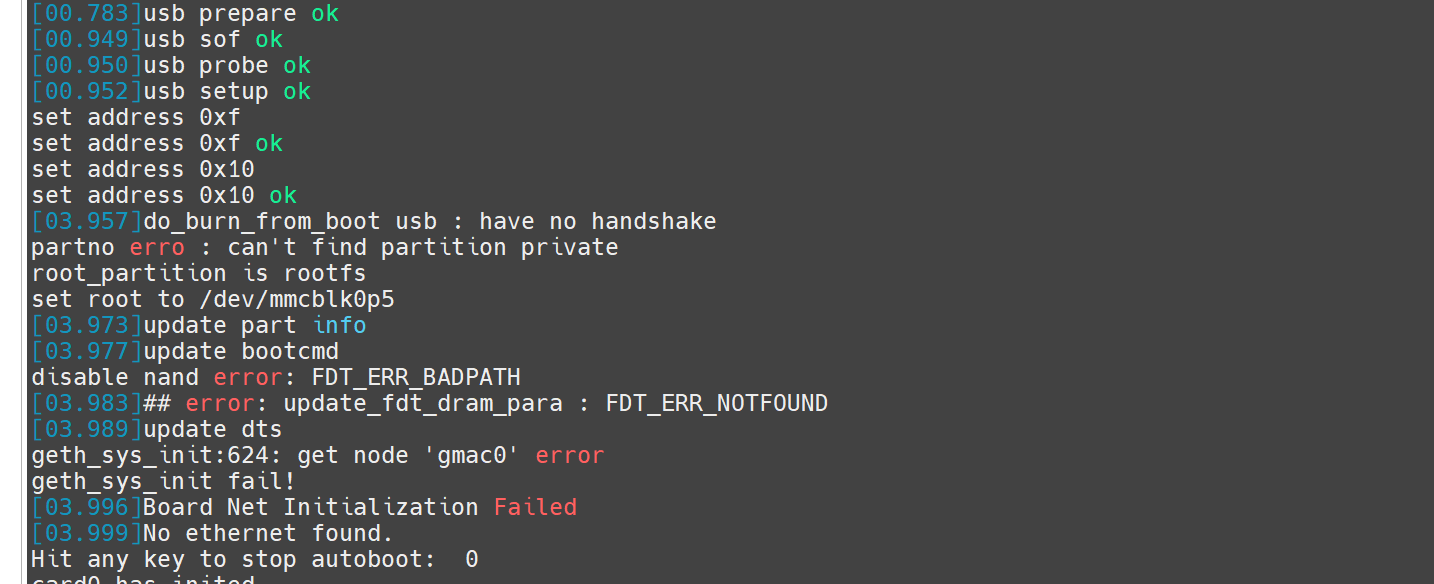

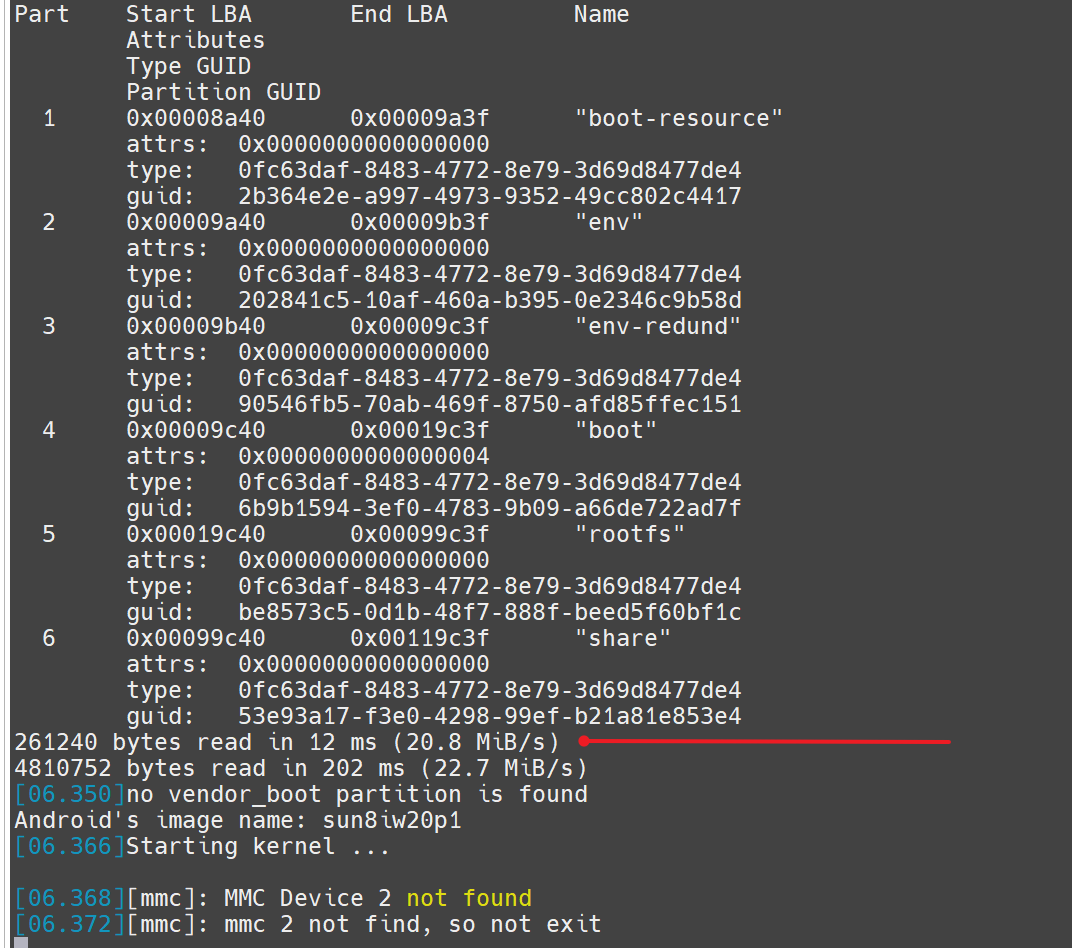

如果镜像只包含 boot0_sdcard.fex boot_package.fex 两个分区,就可以正常启动到uboot,如果增加了任意某一个 如 env boot.vfat rootfs就会出现 如下提示 GPT分区无效,目前怀疑是 R818的 uboot 启动后会对分区做动态修改,导致不能手动指定分区类型/格式。

目前尝试多种方式,都会出现类似情况,有知道问题/方向的大佬指点一下?GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** partno erro : can't find partition bootloader GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wr[01.512]LCD open finish ong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** partno erro : can't find partition boot-resource

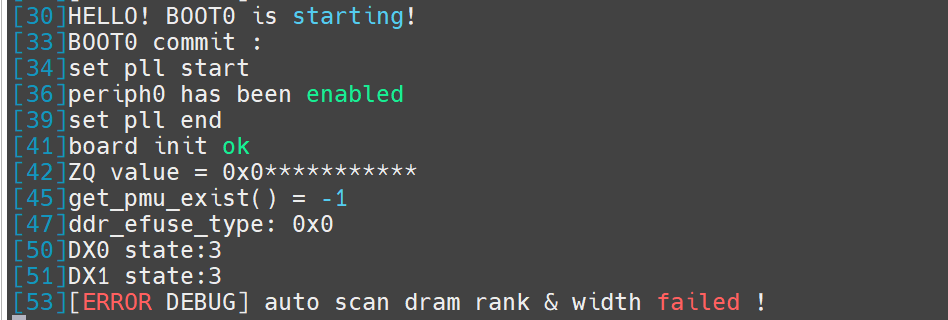

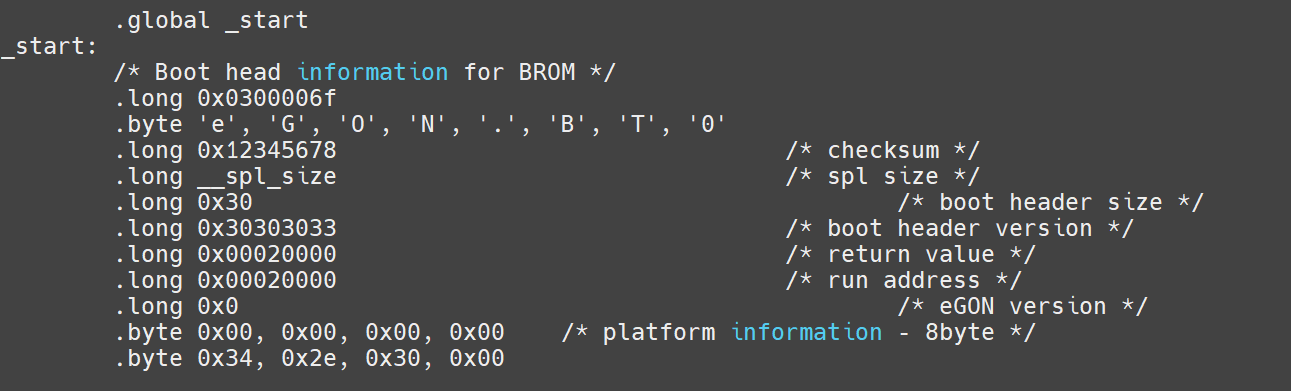

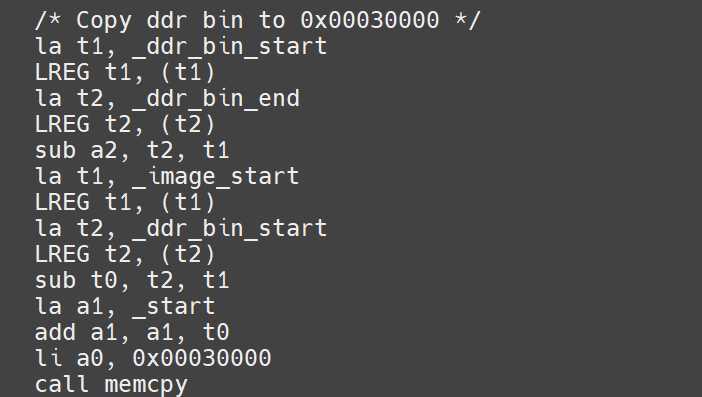

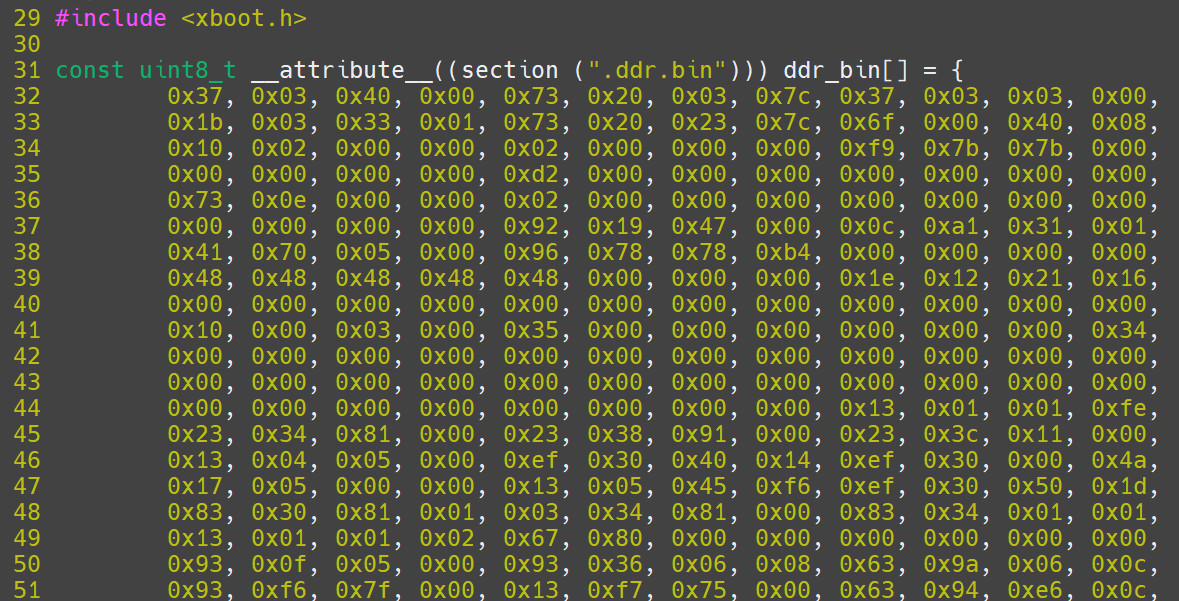

完整启动log[28]HELLO! BOOT0 is starting! [31]BOOT0 commit : e7dab2b212 [34]set pll start [36]periph0 has been enabled [39]set pll end [41]PL gpio voltage : 1.8V [45][pmu]: bus read error [47]unknow PMU [49][pmu]: bus read error [52]PMU: AXP2202 [54][pmu]: bus read error [58]vaild para:1 select dram para0 [61]board init ok, set sys_vol to 950mv! [65]rtc[3] value = 0xb00f [88]enable_jtag [90]DRAM BOOT DRIVE INFO: V0.697 [93]the chip id is 0x1000 [95]the chip id is 0x1000 [98]the chip id is 0x1000 [101]the chip id is 0x1000 [103]the chip id is 0x1000 [106]chip id check OK [109]DRAM_VCC set to 1100 mv [122][AUTO DEBUG]32bit,2 ranks training success! [250][AUTO DEBUG]default config,dram_clk=792 ,mtest pass [600][AUTO DEBUG]26-45,19,0x23 18-36,18,0x1b 23-44,21,0x21 26-48,22,0x25 [AUTO DEBUG]10-26,16,0x12 11-29,18,0x14 11-28,17,0x13 7-28,21,0x11 [708][AUTO DEBUG]after escan,dram_tpr11 = 25211b23,dram_tpr12 = 11131412 [715]DRAM CLK =792 MHZ [717]DRAM Type =8 (3:DDR3,4:DDR4,6:LPDDR2,7:LPDDR3,8:LPDDR4) [729]phy_dfs_clk1 = 632M [731]phy_dfs_clk2 = 352M [734]phy_dfs_clk3 = 98M [737]phy_dfs_clk0 = 792M [739]DRAM SIZE =4096 MBytes, para1 = 310a, para2 = 10001000, tpr13 = 7525 [751]DRAM simple test OK. [754]dram size =4096 [757]chipid = 53801000 [759]nsi init ok 2021-10-14 [762]card no is 0 [764]sdcard 0 line count 4 [766][mmc]: mmc driver ver 2021-10-12 13:56 [771][mmc]: b mmc 0 bias 4 [779][mmc]: Wrong media type 0x0 [782][mmc]: ***Try SD card 0*** [793][mmc]: HSSDR52/SDR25 4 bit [796][mmc]: 50000000 Hz [798][mmc]: 30448 MB [800][mmc]: ***SD/MMC 0 init OK!!!*** [877]Loading boot-pkg Succeed(index=0). [881][mmc]: b mmc 0 bias 4 [884]Entry_name = u-boot [892]Entry_name = dtb [895]mmc not para ▒897]Jump to second Boot. U-Boot 2018.07-gdb54bdb-dirty (Aug 08 2023 - 02:23:48 +0000) Allwinner Technology [00.908]CPU: Allwinner Family [00.911]Model: sun50iw10 I2C: ready [00.927]DRAM: 4 GiB [00.931]Relocation Offset is: 75eee000 [00.965]secure enable bit: 0 [00.968]PMU: AXP2202 [00.970]BMU: AXP2202 AXP2202_IIN_LIM:38 AXP2202_IIN_LIM:38 [00.977][axp][err]: b12_mode: 0 AXP2202_IIN_LIM:38 FDT ERROR:fdt_get_all_pin:get property handle pinctrl-1 error:FDT_ERR_INTERNAL bias_name:pl_bias bias_vol:1800 bias_name:pc_bias bias_vol:1800 [01.024]battery_check pass:radio:100, vol:4345 [01.029]EXT: EXT_probe [01.031]pmu_sy8827g_probe pmic_bus_read fail [01.035]TCS: TCS_probe [01.037]pmu_tcs4838_probe pmic_bus_read fail [01.042]CPU=1416 MHz,PLL6=600 Mhz,AHB=200 Mhz, APB1=100Mhz MBus=400Mhz [01.048]gic: normal mode sunxi flash map init [01.052]flash init start [01.054]workmode = 0,storage type = 1 get value error [01.059][mmc]: mmc driver ver uboot2018:2022-11-04 08:58:00 [01.064][mmc]: get sdc_type fail and use default host:tm1. [01.070][mmc]: can't find node "mmc0",will add new node [01.075][mmc]: fdt err returned <no error> [01.079][mmc]: Using default timing para [01.082][mmc]: SUNXI SDMMC Controller Version:0x50300 [01.101][mmc]: card_caps:0x3000000a [01.104][mmc]: host_caps:0x3000003f [01.109]sunxi flash init ok [01.112]drv_disp_init partno erro : can't find partition bootloader partno erro : can't find partition boot-resource Get bootloader and boot-resource partition number fail! request pwm success, pwm0:pwm0:0x300a000. [01.161]drv_disp_init finish GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** [01.192]Loading Environment from SUNXI_FLASH... GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** *** Warning - no device, using default environment Failed (-19) [01.226]boot_gui_init:start [01.228]set disp.dev2_output_type fail. using defval=0 [01.395]set disp.fb0_rot_used fail. using defval=0 [01.399]set disp.fb0_rot_degree fail. using defval=0 [01.404]soc ic_ver:0x4, qa_val:0x0, markid:0x1000 dclk[0-200] display_cfg_flag:0 [01.412]boot_gui_init:finish GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** partno erro : can't find partition bootloader GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wr[01.512]LCD open finish ong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** partno erro : can't find partition boot-resource [01.526]Get bootloader and boot-resource partition number fail! [01.532]Item0 (Map) magic is bad [01.535]the secure storage item0 copy0 magic is bad [01.541]Item0 (Map) magic is bad [01.543]the secure storage item0 copy1 magic is bad [01.548]Item0 (Map) magic is bad [01.551]usb burn from boot delay time 0 weak:otg_phy_config [01.562]usb prepare ok [01.827]usb sof ok [01.829]usb probe ok [01.831]usb setup ok set address 0x35 set address 0x35 ok [02.238]do_burn_from_boot usb : have no handshake cann't get the boot_base from the env GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** [02.272]update part info [02.275]battery temp is 194 GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** [02.326]update bootcmd GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** [02.376]change working_fdt 0xbbe9de50 to 0xbbe6de50 disable nand error: FDT_ERR_BADPATH get value error GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** partno erro : can't find partition bootloader GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** partno erro : can't find partition boot-resource Get bootloader and boot-resource partition number fail! GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** partno erro : can't find partition bootloader GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** partno erro : can't find partition boot-resource Get bootloader and boot-resource partition number fail! GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** partno erro : can't find partition bootloader GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_get_info_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid Backup GPT *** partno erro : can't find partition boot-resource Get bootloader and boot-resource partition number fail! [02.594]libfdt fdt_path_offset() for lcd [02.598]Could not find pmu_ext type: update_pmu_ext_info_to_kernel: L63 [02.604]update dts Hit any key to stop autoboot: 0 ## Error: "distro_bootcmd" not defined => mmc <INTERRUPT> => part list mmc 0 Partition Map for MMC device 0 -- Partition Type: EFI GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_print_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_print_efi: *** ERROR: Invalid Backup GPT *** => part list mmc 0 Partition Map for MMC device 0 -- Partition Type: EFI GUID Partition Table Entry Array CRC is wrong: 0xab54d286 != 0xb6ac2e52 part_print_efi: *** ERROR: Invalid GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_print_efi: *** ERROR: Invalid Backup GPT *** -

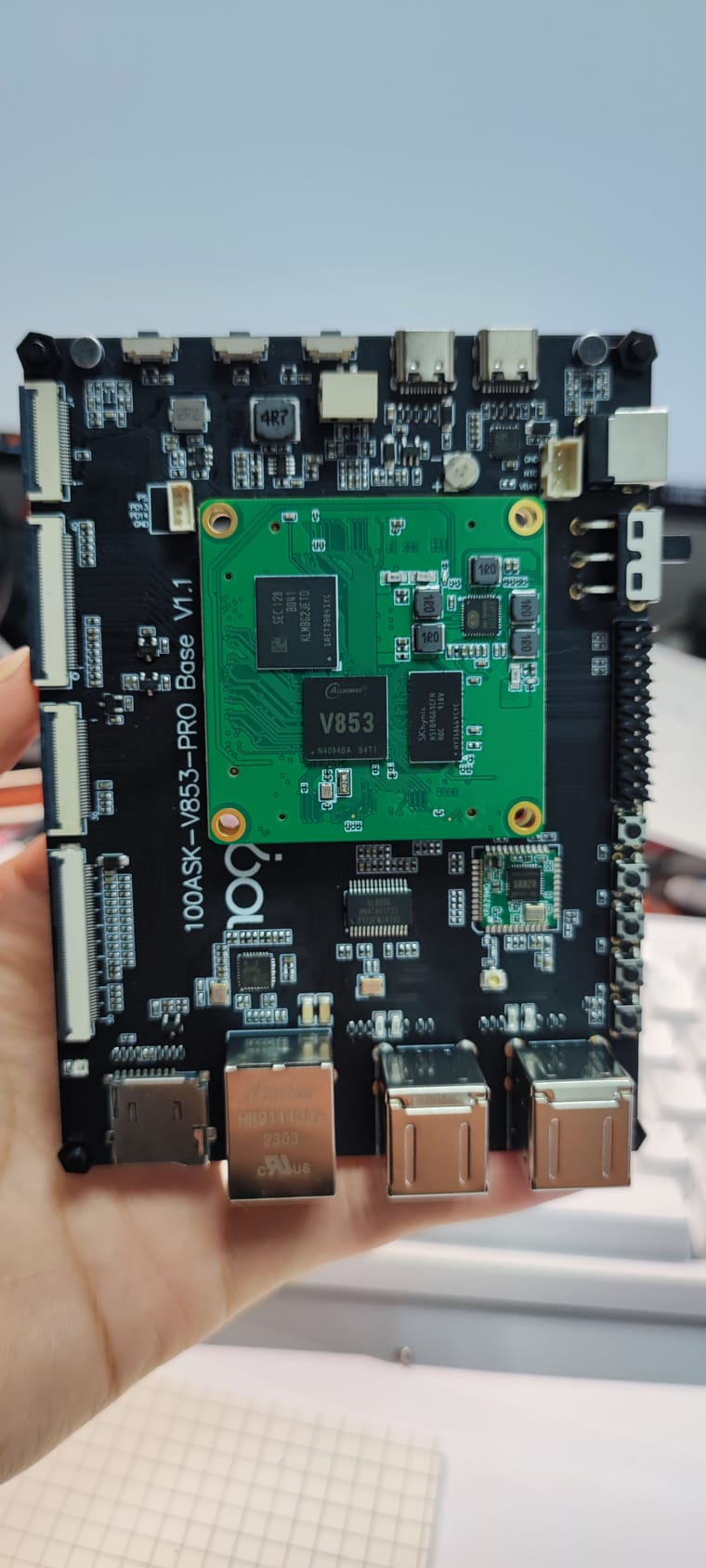

100ASK-V853-PRO开发板支持yolov5模型部署发布在 V Series

100ASK_V853-PRO开发板支持yolov5模型部署

0.前言

本章节主要讲述如何获取yolov5单阶段目标检测算法,并将yolov5原始模型转换为ONNX格式。使用模型转换工具进行模型的转换,并将转换后的模型部署到开发板上。

本章使用的软件列表:

- anaconda(Windows)

- Git(Windows)

- Tina SDK(Linux)

- 全志NPU扩展包(Linux)

- OpenCV库(Linux)

硬件列表:

百问网100ASK_V853-PRO开发板:https://www.aw-ol.com/boards/16这里提供Source资源包:source (包含conda配置yolov5环境依赖包文件,端侧部署代码)

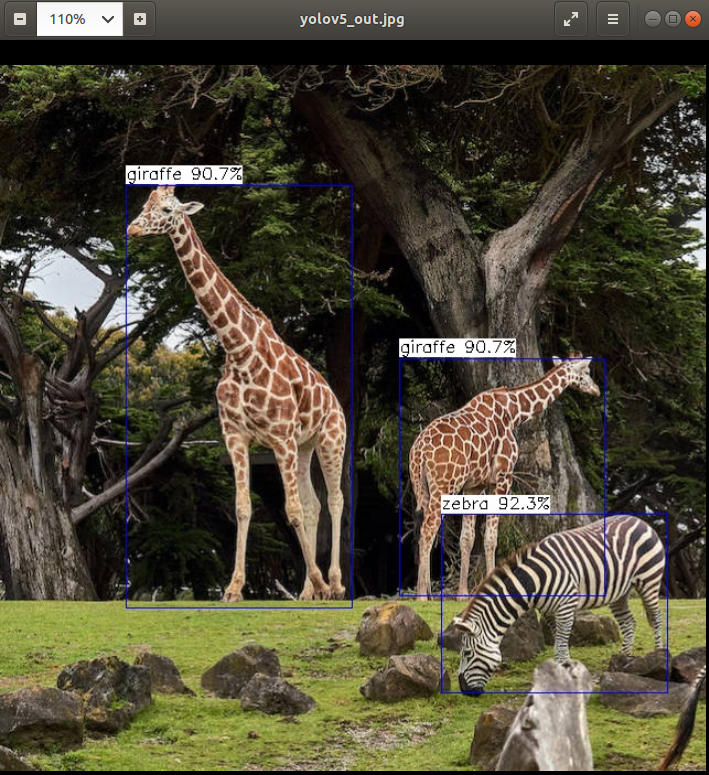

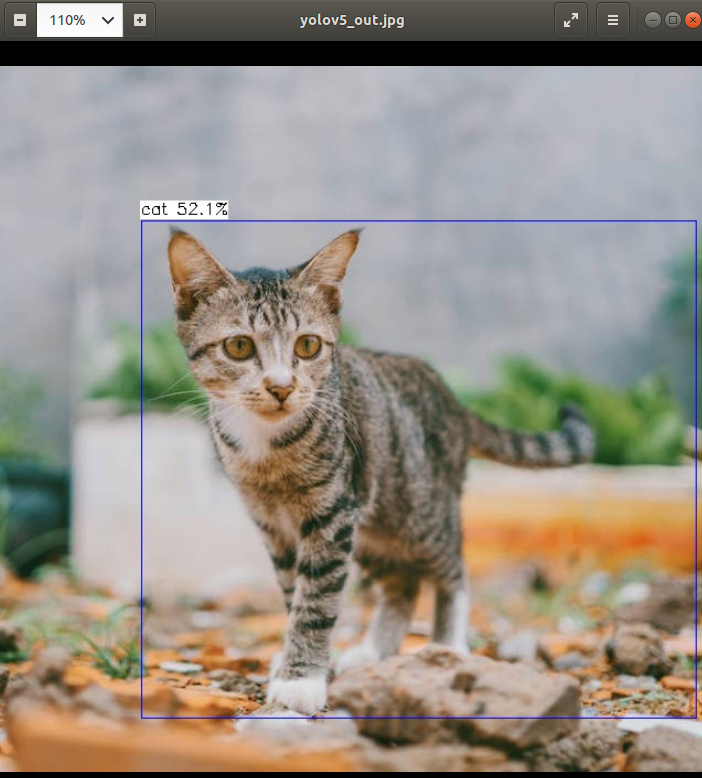

yolov5体验镜像:v853_linux_100ask_uart0.img (测试方法:yolov5 /etc/models/yolov5_model.nb <测试图像>)

YOLOV5官方提供的V6.0版本的资源:

yolov5s ONNX模型文件:https://github.com/ultralytics/yolov5/releases/download/v6.0/yolov5s.onnx

yolov5s PT模型文件:https://github.com/ultralytics/yolov5/releases/download/v6.0/yolov5s.pt

yolov5-v6.0代码:https://github.com/ultralytics/yolov5/archive/refs/tags/v6.0.zip

1.配置yolov5环境

yolov5官方网址为:https://github.com/ultralytics/yolov5

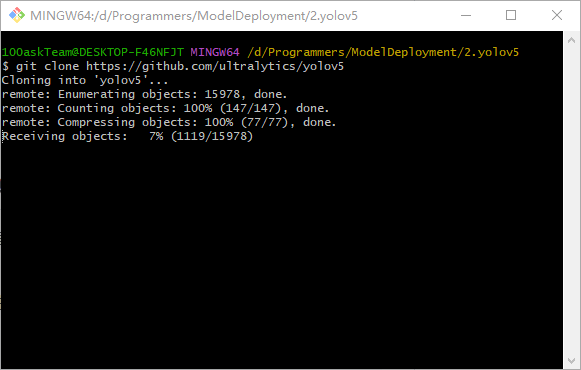

使用Git工具在任意目录下获取源码V6.0版本,输入

git clone -b v6.0 https://github.com/ultralytics/yolov5

如果您使用Git下载出现问题,也可以直接点击下面网址直接下载源码压缩包,下载完成解压即可正常使用。

https://github.com/ultralytics/yolov5/archive/refs/tags/v6.0.zip

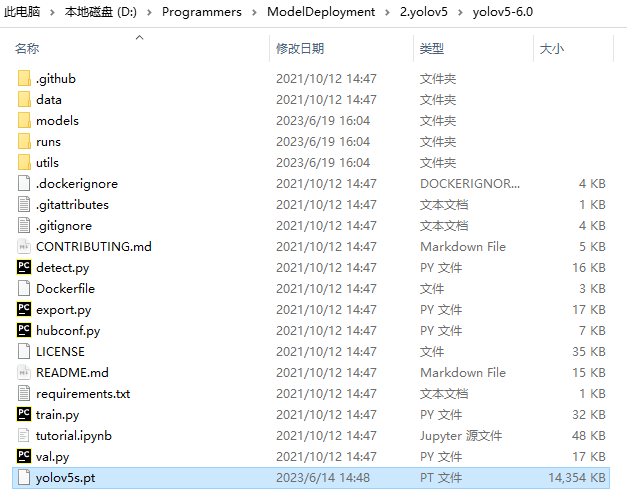

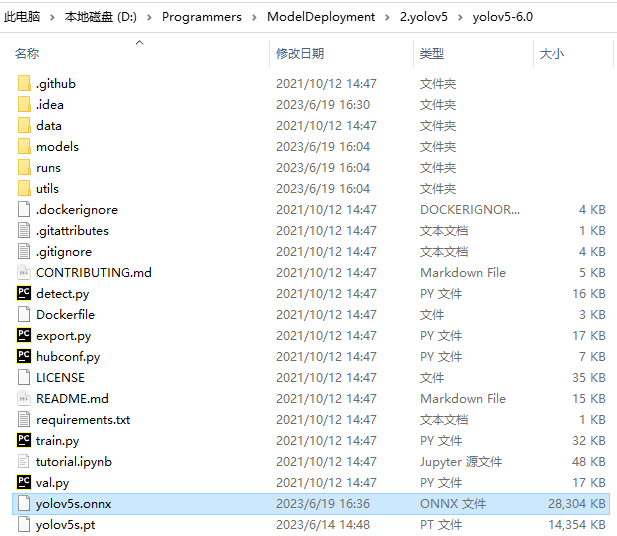

等待下载完成,下载完成后会在当前目录下,查看到yolov5项目文件夹

100askTeam@DESKTOP-F46NFJT MINGW64 /d/Programmers/ModelDeployment/2.yolov5 $ ls yolov5/ 100askTeam@DESKTOP-F46NFJT MINGW64 /d/Programmers/ModelDeployment/2.yolov5 $ cd yolov5/ 100askTeam@DESKTOP-F46NFJT MINGW64 /d/Programmers/ModelDeployment/2.yolov5/yolov5 (master) $ ls CITATION.cff README.zh-CN.md detect.py requirements.txt tutorial.ipynb CONTRIBUTING.md benchmarks.py export.py segment/ utils/ LICENSE classify/ hubconf.py setup.cfg val.py README.md data/ models/ train.py打开Anaconda Prompt (Anaconda3)软件,进入yolov5项目目录中,输入以下命令

(base) C:\Users\100askTeam>D: (base) D:\>cd D:\Programmers\ModelDeployment\2.yolov5\yolov5 (base) D:\Programmers\ModelDeployment\2.yolov5\yolov5>使用conda创建yolov项目环境,输入

conda create -n my-yolov5-env python=3.7激活yolov5环境

conda activate my-yolov5-env安装依赖

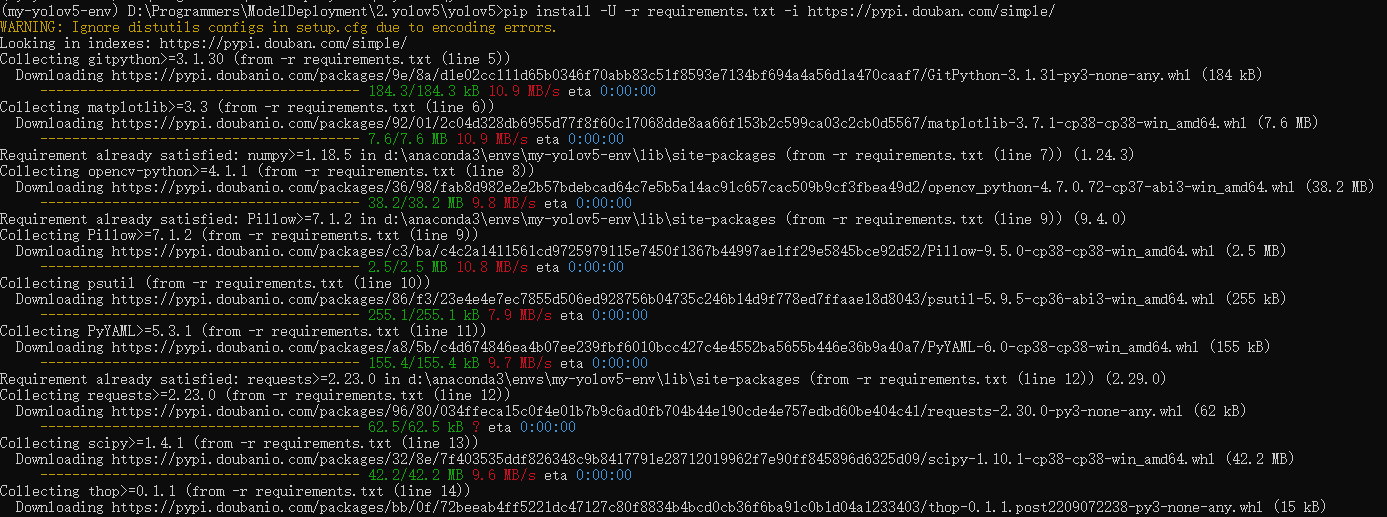

pip install -U -r requirements.txt -i https://pypi.doubanio.com/simple/

FAQ:

搭建环境时由于版本的不同会遇各种问题,下面我会提供我配置好的环境所需的包文件版本,文件位于压缩包的requirements文件夹中的conda-yolov5_6-env.yaml。在Conda终端中创建新环境,执行

conda env create -f conda-yolov5_6-env.yaml执行

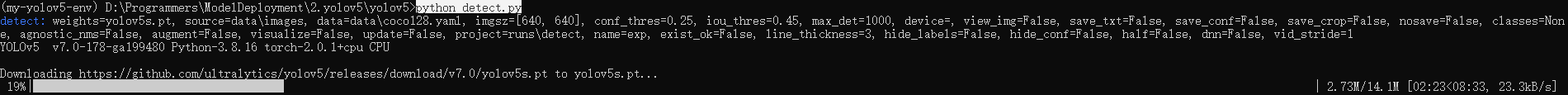

python detect.py,测试环境是否搭建成功,执行后会自动下载模型权重文件

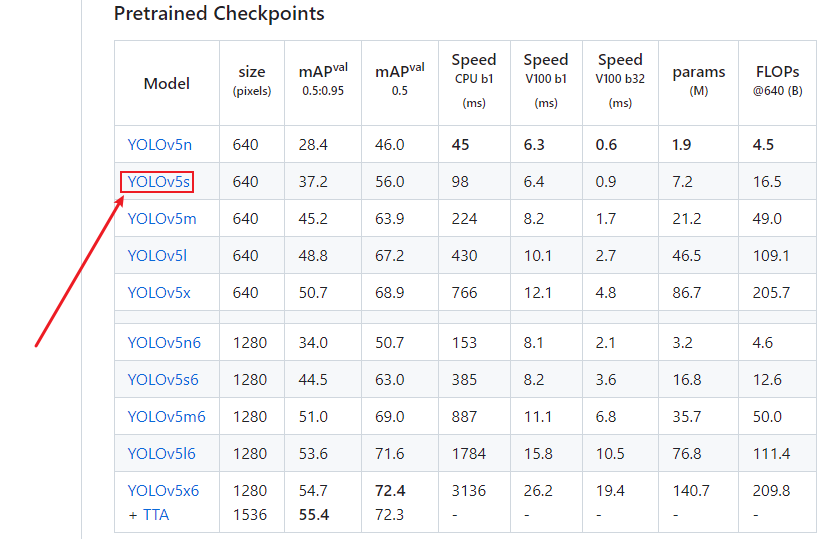

这里下载速度可能会很慢,建议直接访问官网下载https://github.com/ultralytics/yolov5/tree/v6.0,点击下图红框处的YOLOV5s。这里我下载 v6.0 版本的 yolov5s.onnx 模型作为示例。

下载地址:https://github.com/ultralytics/yolov5/releases/download/v6.0/yolov5s.pt

点进入后会进去yolov5资源中心,往下找到V6.0版本的资源下载界面,找到您所需的资源即可。

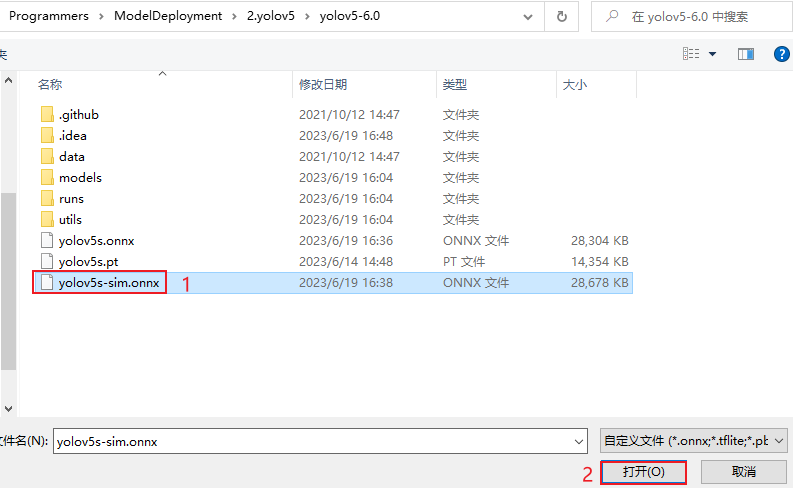

将该模型文件放在yolov5项目文件夹下,如下图所示:

在conda终端中输入

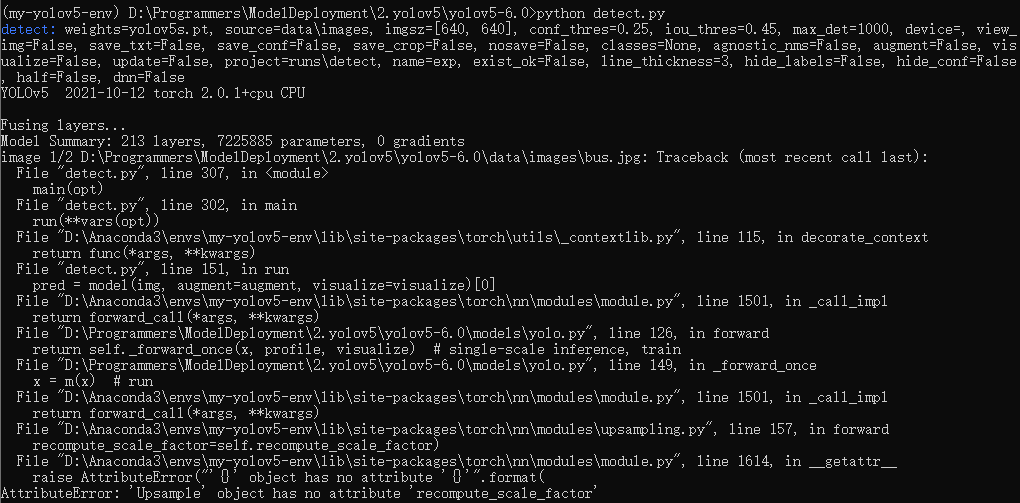

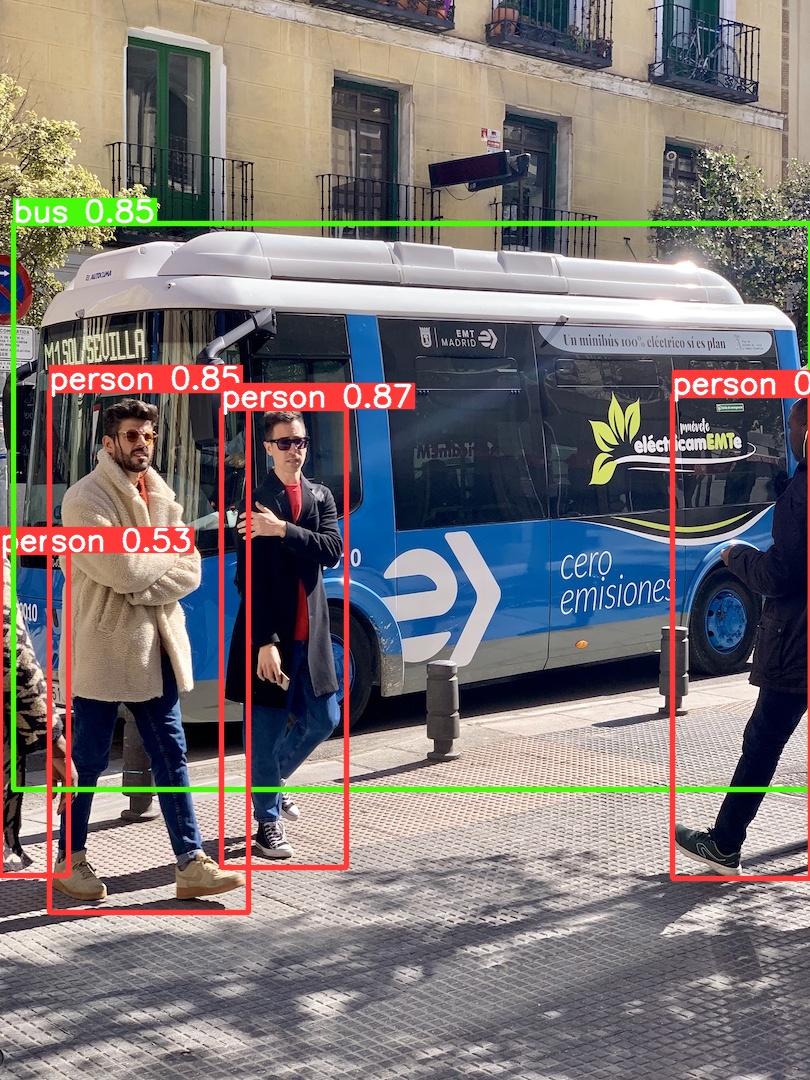

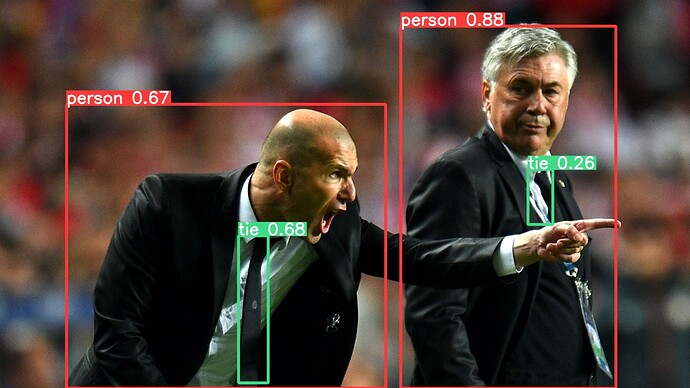

python detect.py,可得到如下执行结果(my-yolov5-env) D:\Programmers\ModelDeployment\2.yolov5\yolov5-6.0>python detect.py detect: weights=yolov5s.pt, source=data\images, imgsz=[640, 640], conf_thres=0.25, iou_thres=0.45, max_det=1000, device=, view_img=False, save_txt=False, save_conf=False, save_crop=False, nosave=False, classes=None, agnostic_nms=False, augment=False, visualize=False, update=False, project=runs\detect, name=exp, exist_ok=False, line_thickness=3, hide_labels=False, hide_conf=False, half=False, dnn=False YOLOv5 2021-10-12 torch 2.0.1+cpu CPU Fusing layers... D:\Anaconda3\envs\my-yolov5-env\lib\site-packages\torch\functional.py:504: UserWarning: torch.meshgrid: in an upcoming release, it will be required to pass the indexing argument. (Triggered internally at C:\actions-runner\_work\pytorch\pytorch\builder\windows\pytorch\aten\src\ATen\native\TensorShape.cpp:3484.) return _VF.meshgrid(tensors, **kwargs) # type: ignore[attr-defined] Model Summary: 213 layers, 7225885 parameters, 0 gradients image 1/2 D:\Programmers\ModelDeployment\2.yolov5\yolov5-6.0\data\images\bus.jpg: 640x480 4 persons, 1 bus, Done. (0.274s) image 2/2 D:\Programmers\ModelDeployment\2.yolov5\yolov5-6.0\data\images\zidane.jpg: 384x640 2 persons, 1 tie, Done. (0.189s) Speed: 4.5ms pre-process, 231.3ms inference, 2.8ms NMS per image at shape (1, 3, 640, 640) Results saved to runs\detect\exp1FAQ:

如果您执行此命令时,遇到如下报错:

原因:torch版本过高,可以通过修改代码或者降低版本。

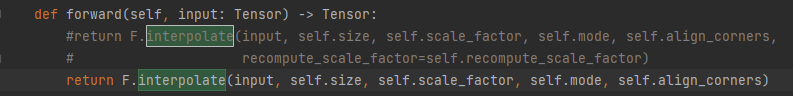

下面我使用修改代码的方式解决:

修改

D:\Anaconda3\envs\my-yolov5-env\lib\site-packages\torch\nn\modules\upsampling.py文件中的Upsample类中forward函数的返回值。原本:

def forward(self, input: Tensor) -> Tensor: return F.interpolate(input, self.size, self.scale_factor, self.mode, self.align_corners, recompute_scale_factor=self.recompute_scale_factor)修改后:

def forward(self, input: Tensor) -> Tensor: return F.interpolate(input, self.size, self.scale_factor, self.mode, self.align_corners)修改结果如下图所示:

执行

python detect.py完成后,可以在yolov5项目文件夹下的runs\detect\exp1目录下找到执行后的输出结果,如下所示。

2.导出yolov5 ONNX模型

2.1 export程序导出模型

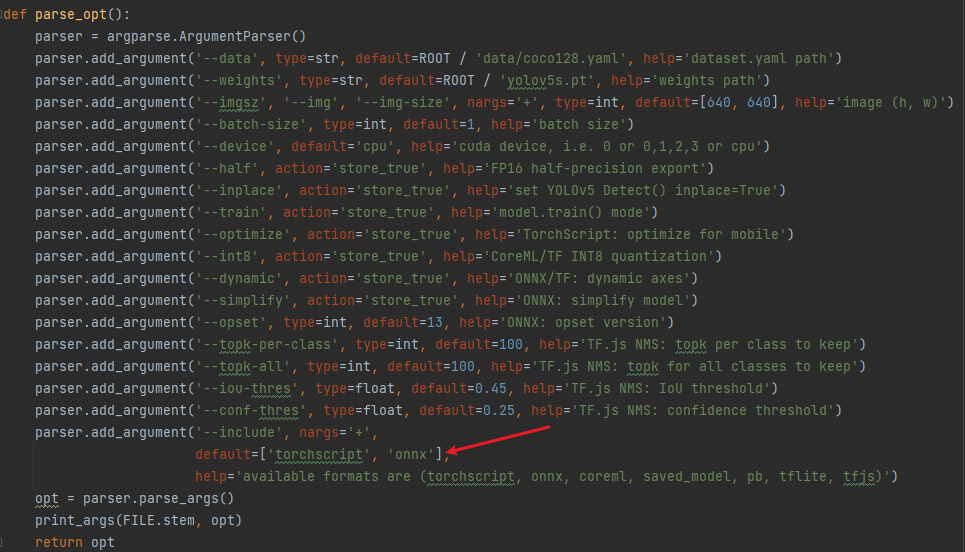

在export.py程序找到parse_opt函数,查看默认输出的模型格式。如果默认支持有onnx格式,就无需修改,如果默认没有填写onnx,修改默认格式为onnx格式。

执行export.py函数前需要需要确保已经安装了onnx包,可手动安装,如下所示

pip install onnx==1.13.0 -i https://pypi.doubanio.com/simple/执行export.py函数导出yolov5的onnx格式动态模型,在conda终端输入

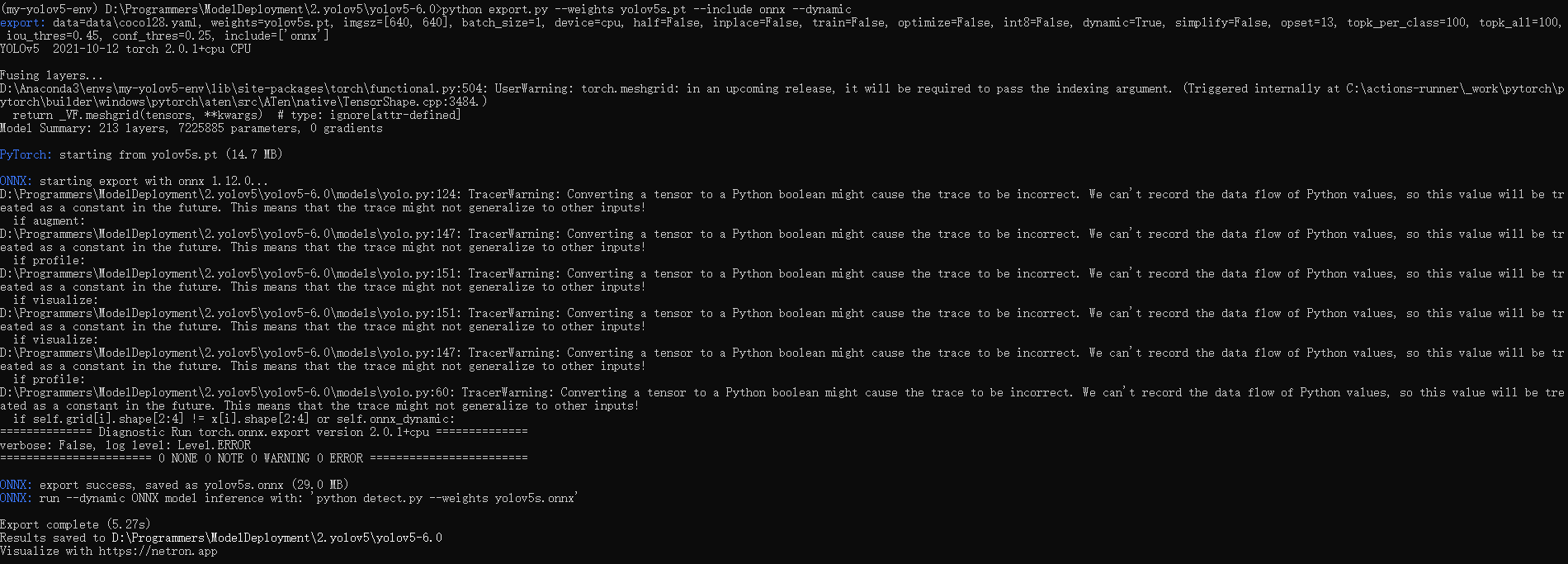

python export.py --weights yolov5s.pt --include onnx --dynamic

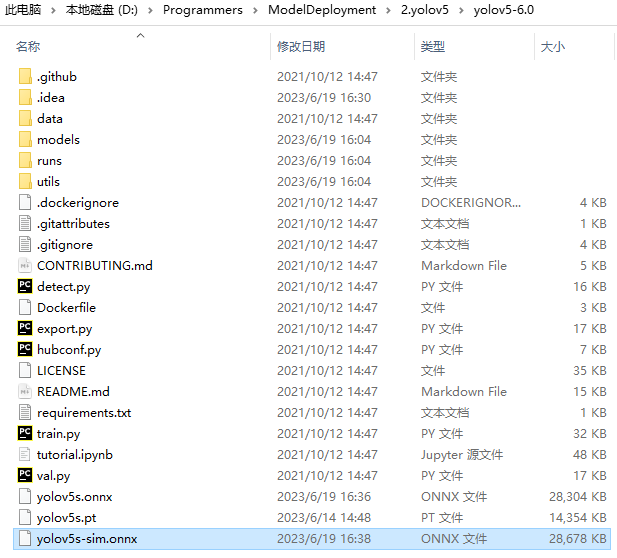

执行完成后会在yolov5项目目录中生成一个名称为

yolov5s.onnx的文件,如下图所示:

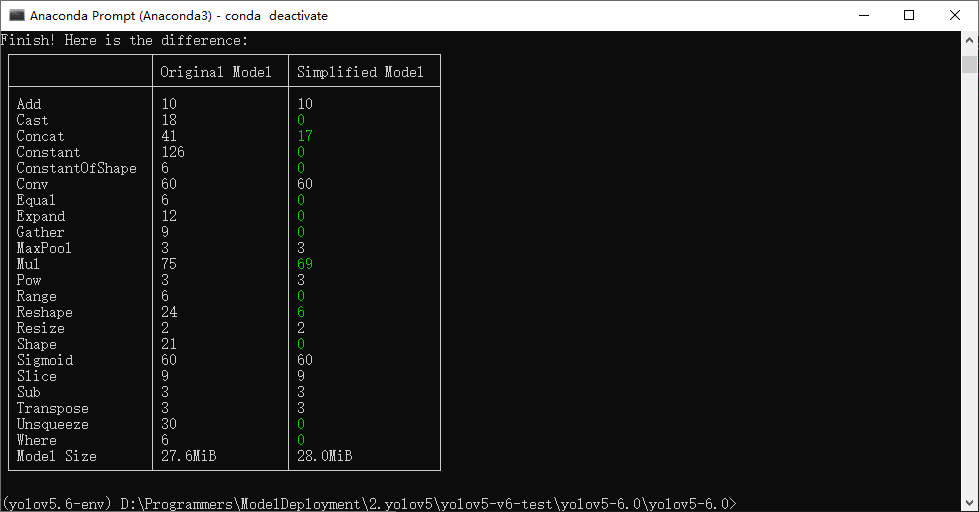

2.2 简化模型

由于转换的模型是动态 Shape 的,不限制输入图片的大小,对于 NPU 来说会增加处理工序,所以这里我们需要转换为静态 Shape 的模型。

需要安装

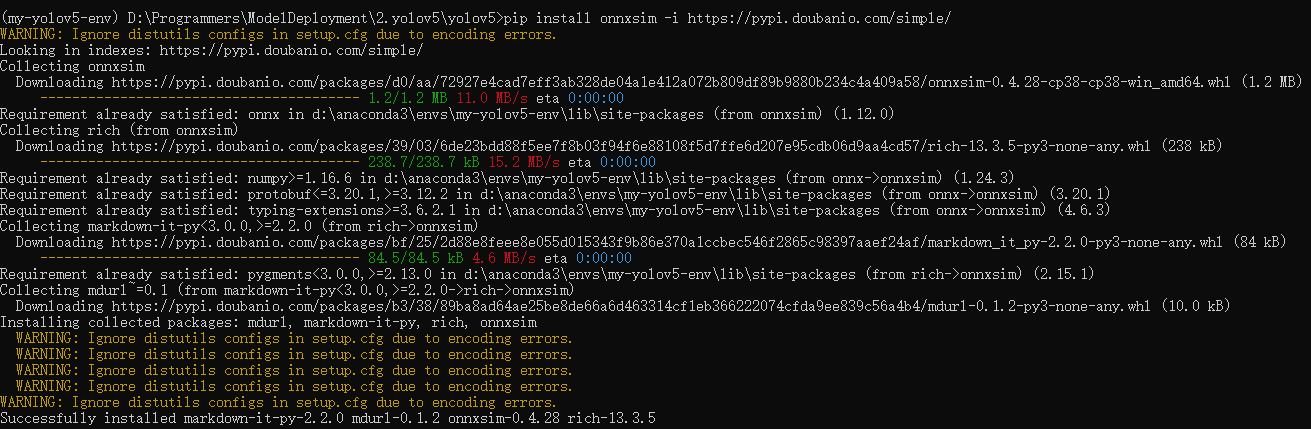

onnxsim工具,在conda终端输入pip install onnxsim -i https://pypi.doubanio.com/simple/

然后使用这条命令转换:

python -m onnxsim yolov5s.onnx yolov5s-sim.onnx --input-shape 1,3,640,640

执行完成后会导出名为

yolov5s-sim.onnx文件,文件位于yolov5项目文件夹下,如下图所示:

2.3 查看模型

使用开源网站Netron网站

访问上面网址查看模型结构。

选择

yolov5s-sim.onnx文件,点击打开。

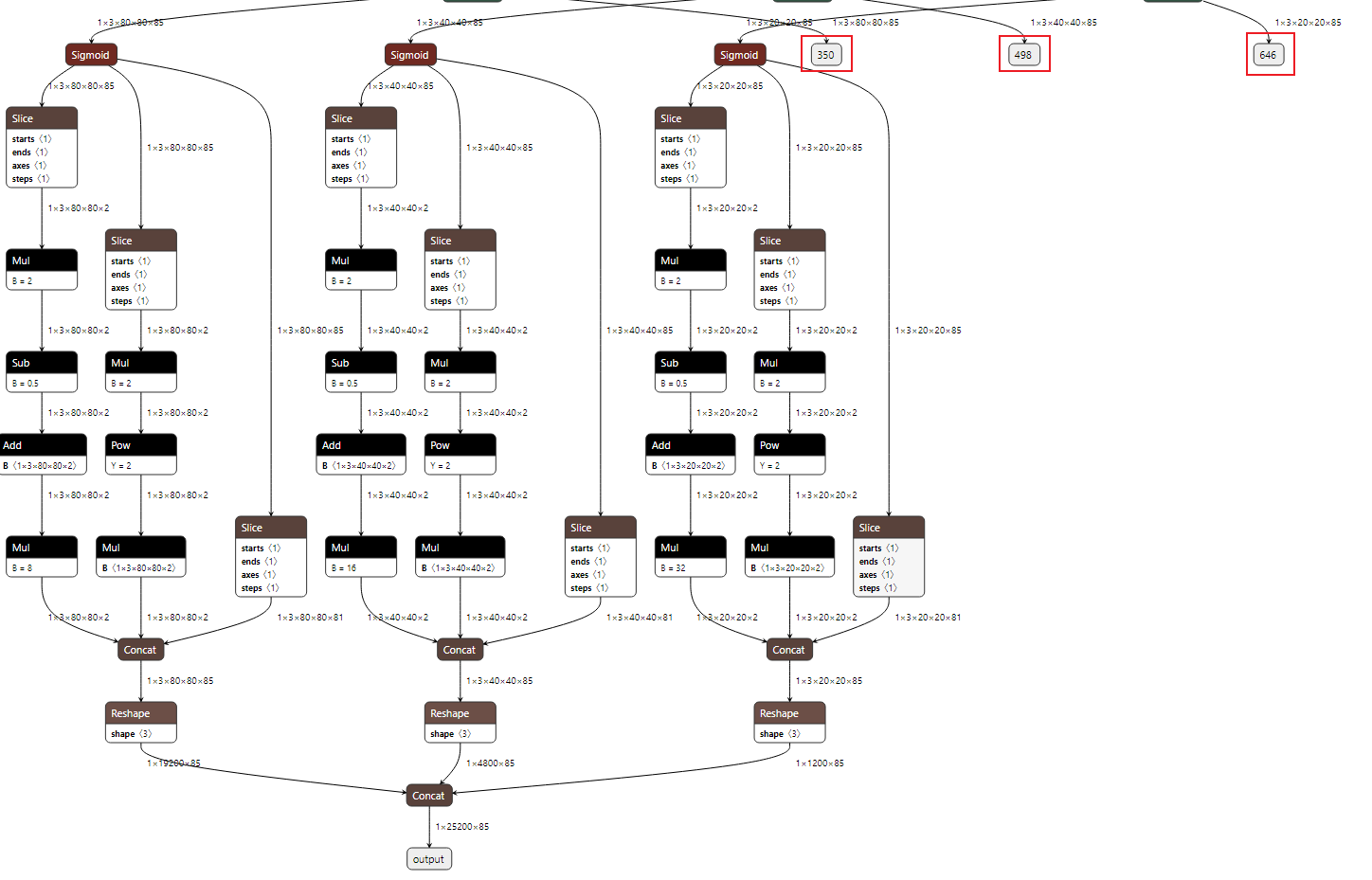

查看如下图所示输出节点

可看到模型有 4 个输出节点,其中 ouput 节点为后处理解析后的节点;在实际测试的过程中,发现 NPU 量化操作后对后处理的运算非常不友好,输出数据偏差较大,所以我们可以将后处理部分放在 CPU 运行;因此保留

350,498,646三个后处理解析前的输出节点即可,后文在导入模型时修改输出节点。3.转换NPU模型

3.1 创建转换目录

打开NPU工具包的虚拟机Ubuntu20.04,创建yolov5-6.0文件夹,存放模型和量化图像等。

ubuntu@ubuntu2004:~$ mkdir yolov5-6.0进入yolov5模型转换目录。

ubuntu@ubuntu2004:~$ cd yolov5-6.0/创建data目录存放量化图像

mkdir data将量化图像传入data文件夹下,例如,传入

test01.jpg图像到dataubuntu@ubuntu2004:~/yolov5-test$ ls data test01.jpg在yolov5模型转换目录中创建

dataset.txtubuntu@ubuntu2004:~/yolov5-6.0$ touch dataset.txt修改

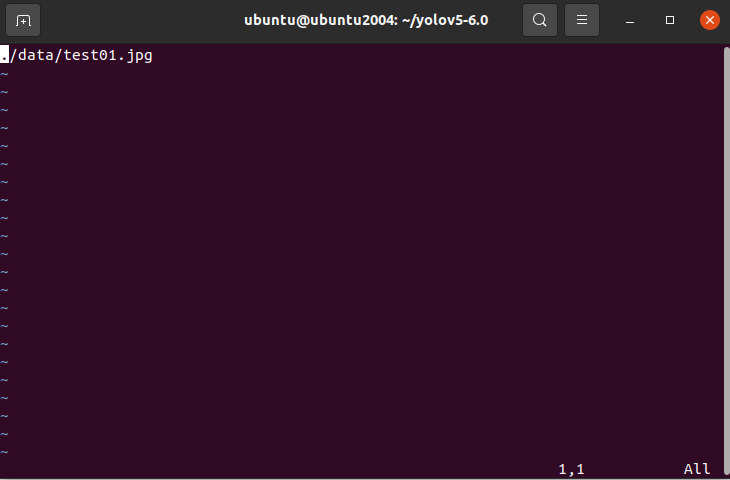

dataset.txt文件ubuntu@ubuntu2004:~/yolov5-6.0$ vi dataset.txt在

dataset.txt文件中增加量化图片的路径../data/test01.jpg

将

yolov5s-sim.onnx模型传入yolov5模型转换文件夹下。例如:ubuntu@ubuntu2004:~/yolov5-6.0$ ls data dataset.txt yolov5s-sim.onnx工作目录的文件如下所示:

ubuntu@ubuntu2004:~/yolov5-6.0$ tree . ├── data │ └── test01.jpg ├── dataset.txt └── yolov5s-sim.onnx 1 directory, 3 files3.2 导入模型

导入模型前需要知道我们要保留的输出节点,由之前查看到我们输出的三个后处理节点为:

350,498,646。pegasus import onnx --model yolov5s-sim.onnx --output-data yolov5s-sim.data --output-model yolov5s-sim.json --outputs 350 498 646导入生成两个文件,分别是是

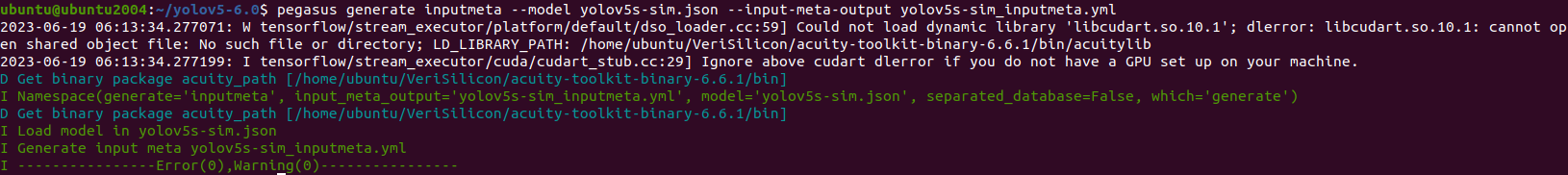

yolov5s-sim.data和yolov5s-sim.json文件,两个文件是 YOLO V5 网络对应的芯原内部格式表示文件,data文件储存权重,cfg文件储存模型。3.3生成 YML 文件

YML 文件对网络的输入和输出的超参数进行描述以及配置,这些参数包括,输入输出 tensor 的形状,归一化系数 (均值,零点),图像格式,tensor 的输出格式,后处理方式等等

pegasus generate inputmeta --model yolov5s-sim.json --input-meta-output yolov5s-sim_inputmeta.yml

pegasus generate postprocess-file --model yolov5s-sim.json --postprocess-file-output yolov5s-sim_postprocess_file.yml修改

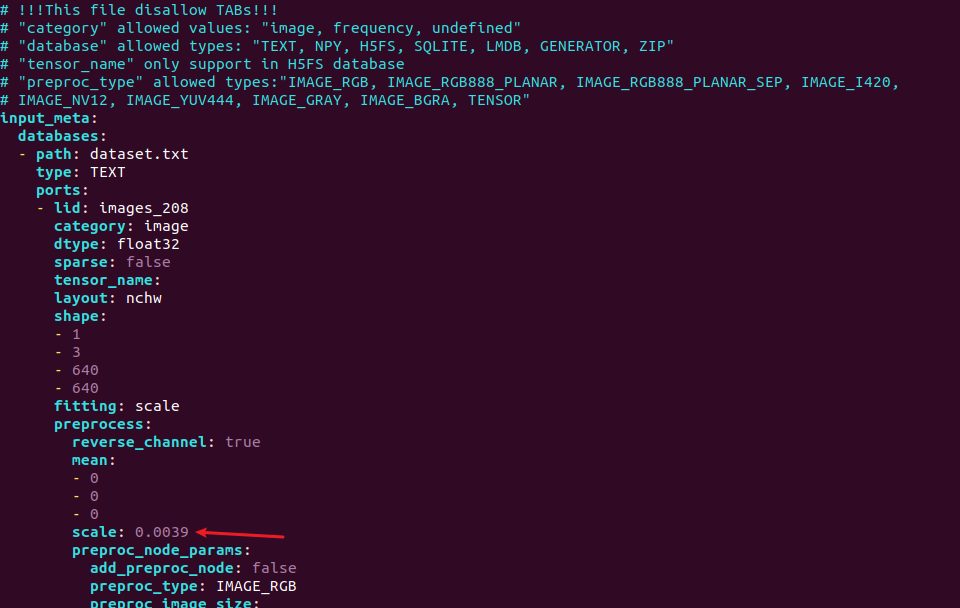

yolov5s-sim_inputmeta.yml文件中的的scale参数为0.0039216(1/255),目的是对输入tensor进行归一化,和网络进行训练的时候是对应的。vi yolov5s-sim_inputmeta.yml

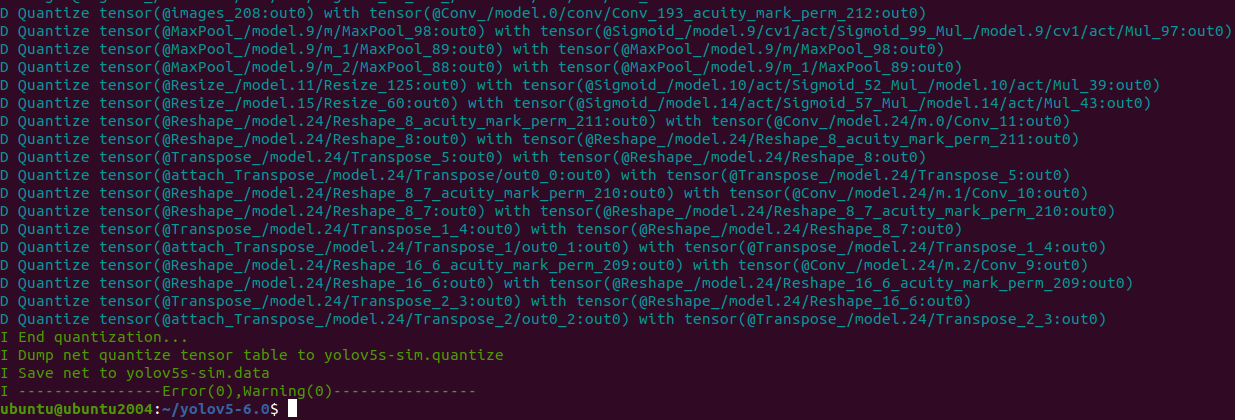

3.4 量化

生成量化表文件,使用非对称量化,uint8,修改

--batch-size参数为你的dataset.txt里提供的图片数量。pegasus quantize --model yolov5s-sim.json --model-data yolov5s-sim.data --batch-size 1 --device CPU --with-input-meta yolov5s-sim_inputmeta.yml --rebuild --model-quantize yolov5s-sim.quantize --quantizer asymmetric_affine --qtype uint8

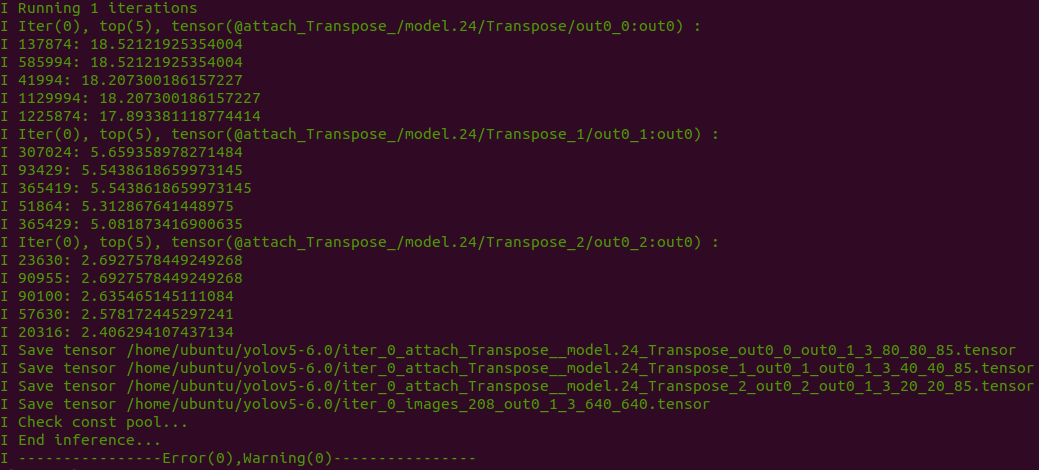

3.5 预推理

利用前文的量化表执行预推理,得到推理

tensorpegasus inference --model yolov5s-sim.json --model-data yolov5s-sim.data --batch-size 1 --dtype quantized --model-quantize yolov5s-sim.quantize --device CPU --with-input-meta yolov5s-sim_inputmeta.yml --postprocess-file yolov5s-sim_postprocess_file.yml

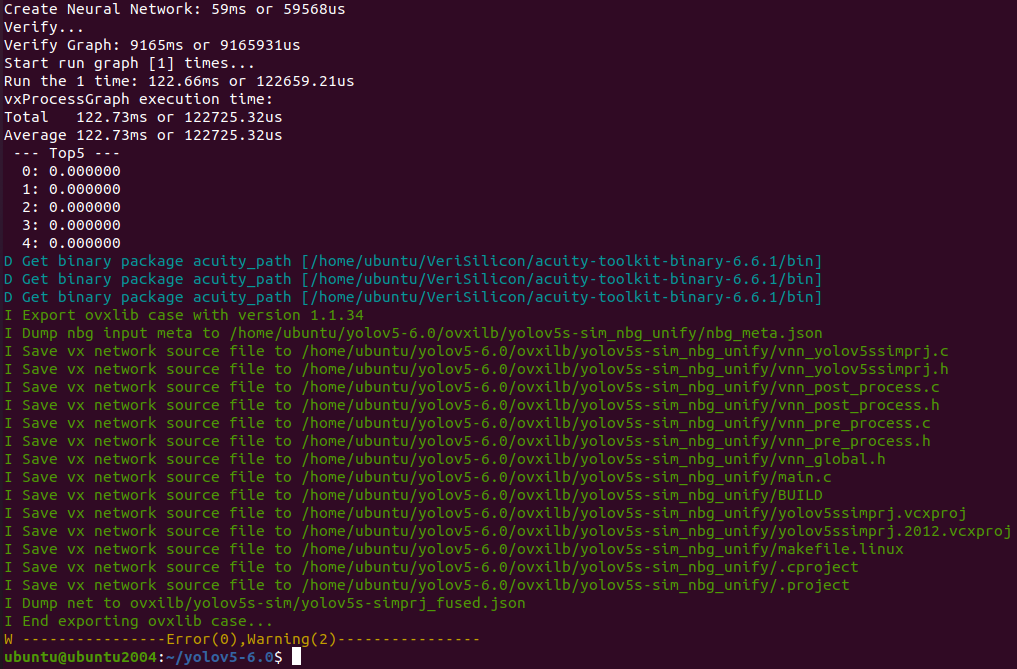

3.6 导出模板代码与模型

输出的模型可以在

ovxilb/yolov5s-sim_nbg_unify文件夹中找到network_binary.nb文件。pegasus export ovxlib --model yolov5s-sim.json --model-data yolov5s-sim.data --dtype quantized --model-quantize yolov5s-sim.quantize --batch-size 1 --save-fused-graph --target-ide-project 'linux64' --with-input-meta yolov5s-sim_inputmeta.yml --output-path ovxilb/yolov5s-sim/yolov5s-simprj --pack-nbg-unify --postprocess-file yolov5s-sim_postprocessmeta.yml --optimize "VIP9000PICO_PID0XEE" --viv-sdk ${VIV_SDK}

将生成的

network_binary.nb文件拷贝出来备用。4.YOLOV5端侧部署

4.1 配置yolov5端侧部署环境

在进行端侧部署前,由于后处理需要使用OpenCV库,所以请先按照如下步骤

-

配置OpenCV库:https://forums.100ask.net/t/topic/3349

配置完成后才能编译端侧部署程序。

下载

source压缩包中的yolov5.tar.gz,将该压缩包拷贝到虚拟机中,解压压缩包tar -xzvf yolov5.tar.gz将解压出来的文件夹拷贝到

tina-v853-open/openwrt/package/npu/目录下cp yolov5/ ~/workspaces/tina-v853-open/openwrt/package/npu/ -rf注意:上面的

~/workspaces/tina-v853-open/openwrt/package/npu/目录需要更换为您自己的SDK实际的目录。拷贝完成后,如下所示:

book@100ask:~/workspaces/tina-v853-open/openwrt/package/npu$ ls lenet viplite-driver vpm_run yolov3 yolov54.2 编译端侧部署代码

配置编译环境

book@100ask:~/workspaces/tina-v853-open$ source build/envsetup.sh ... book@100ask:~/workspaces/tina-v853-open$ lunch You're building on Linux Lunch menu... pick a combo: 1 v853-100ask-tina 2 v853-vision-tina Which would you like? [Default v853-100ask]: 1 ...进入Tina配置界面

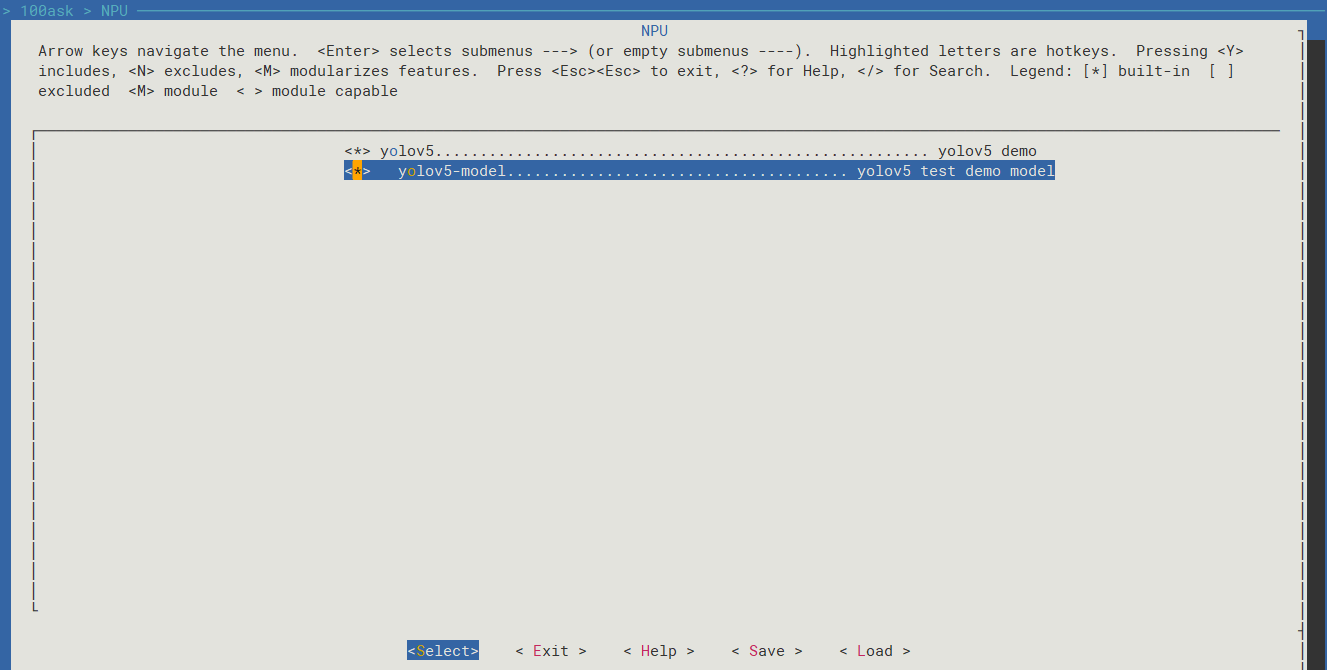

book@100ask:~/workspaces/tina-v853-open$ make menuconfig进入如下目录,选中yolov5后即可编译端侧部署程序

> 100ask > NPU <*> yolov5....................................................... yolov5 demo <*> yolov5-model...................................... yolov5 test demo model注意:yolov5-model该选择后会将yolov5_model.nb打包进镜像中,该模型文件会在/etc/models/目录下。

保存并退出Tina配置界面。

编译Tina SDK镜像,编译完成后打包生成镜像

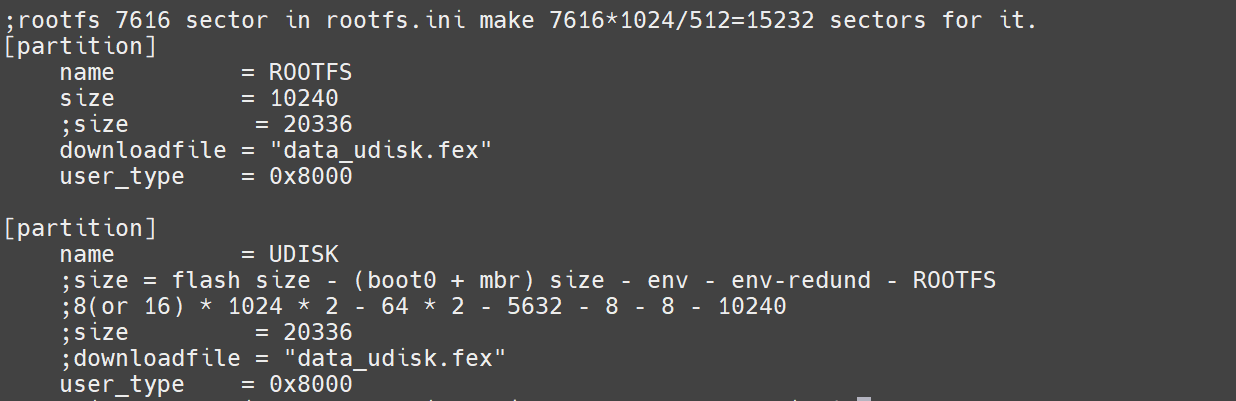

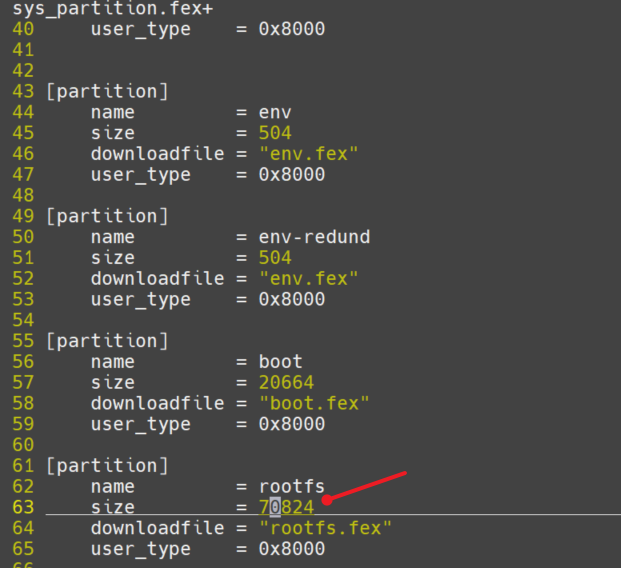

book@100ask:~/workspaces/tina-v853-open$ make ... book@100ask:~/workspaces/tina-v853-open$ pack注意:如果您将模型打包进镜像中,可能会出现文件系统大小设置值太小的问题们可以参考https://forums.100ask.net/t/topic/3158解决。

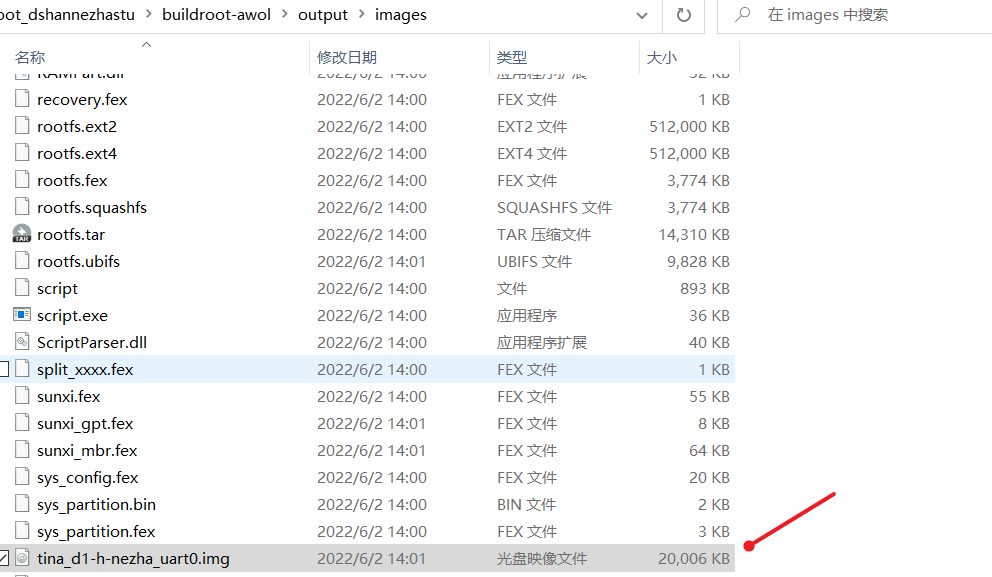

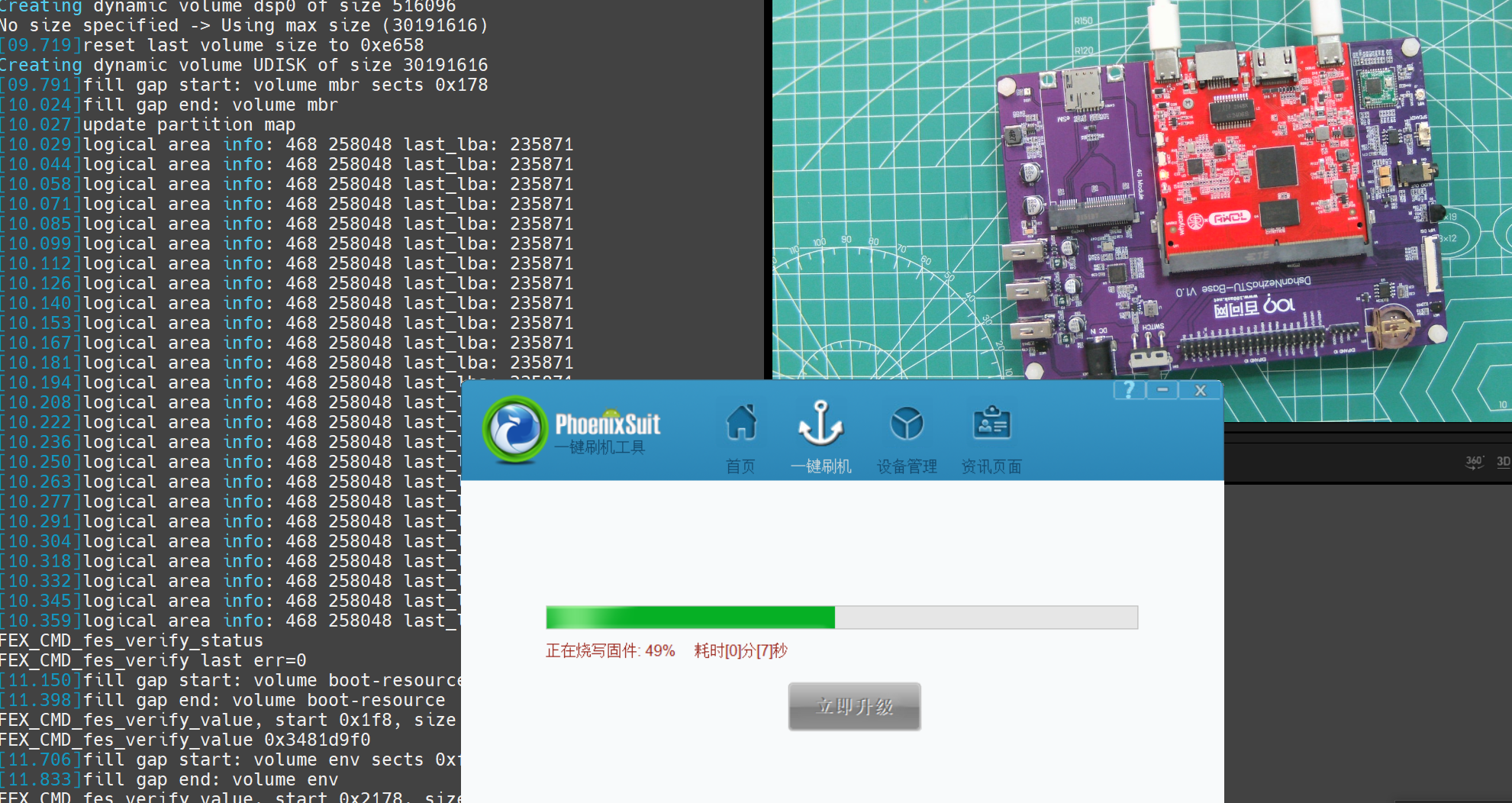

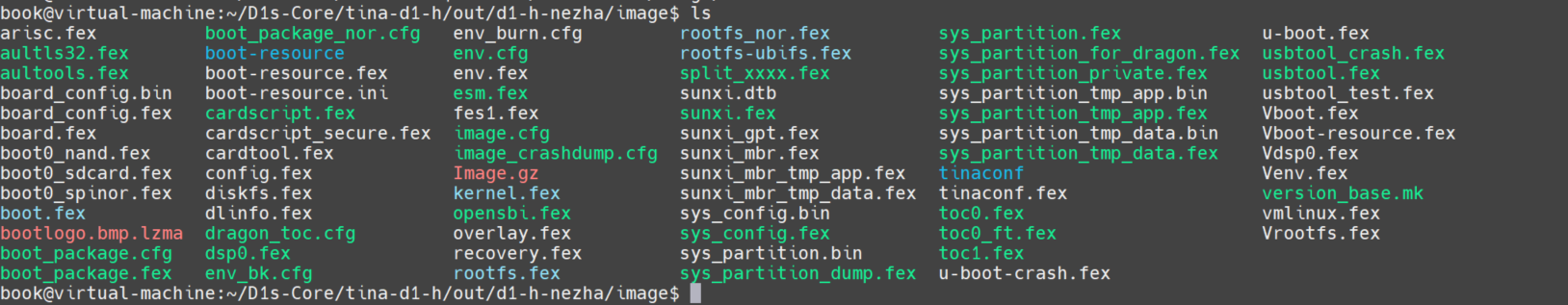

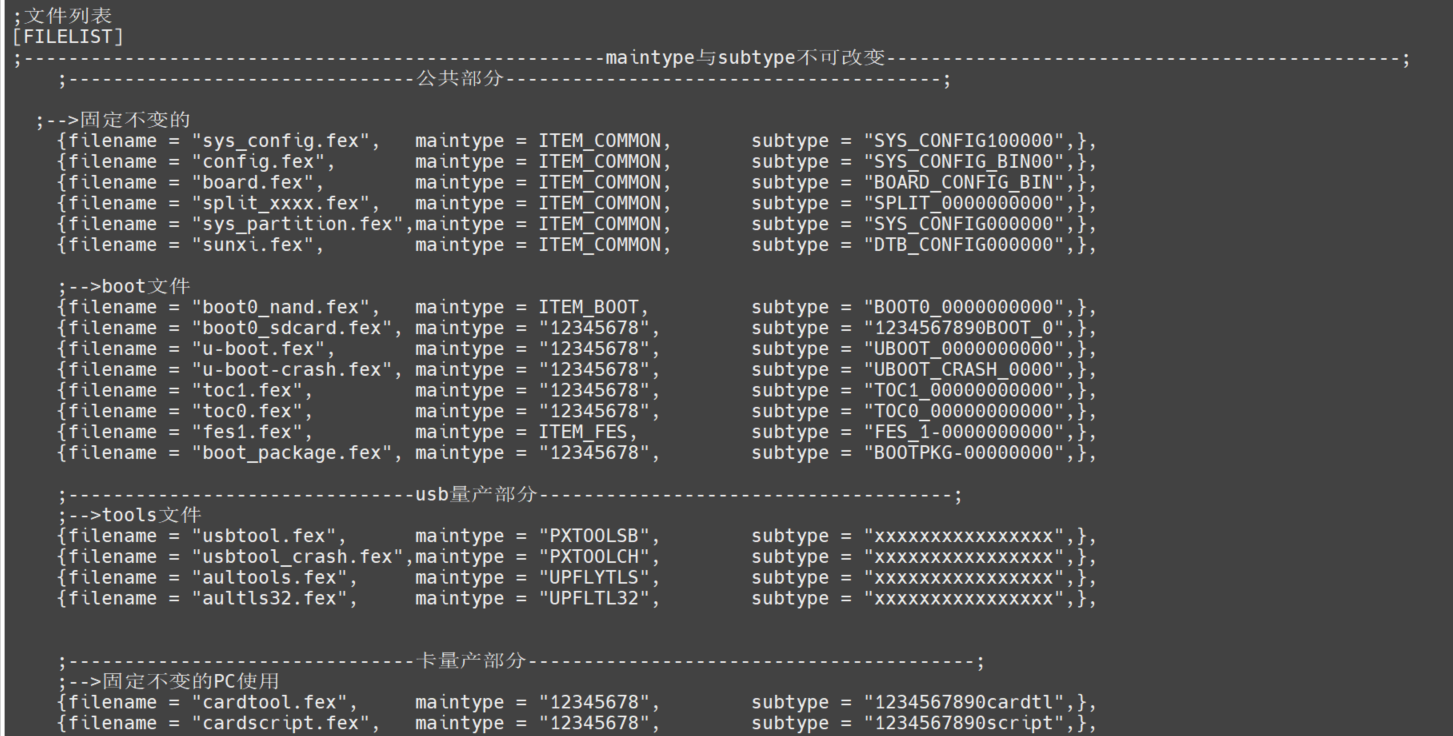

打包完成后,使用全志烧写工具进行烧写新镜像,如果您还不会烧写系统,请参考:https://forums.100ask.net/t/topic/3403

4.3 测试yolov5端侧部署

测试图像文件要求:

- 图片

- 尺寸:640*640

开发板端:

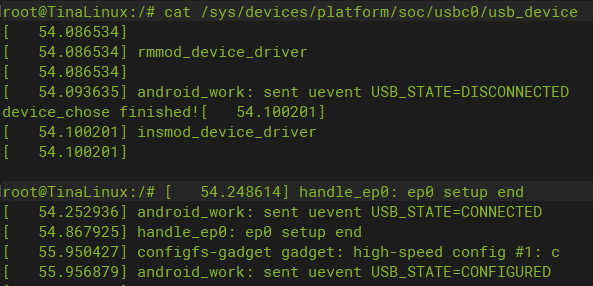

使用ADB将测试图片传输到开发板上,将USB0的模式切换到 Device 模式

cat /sys/devices/platform/soc/usbc0/usb_device

主机端:

将ADB设备连接上虚拟机,并将虚拟机中的测试图片传输到开发板中,查看ADB设备

book@100ask:~/workspaces/testImg$ adb devices List of devices attached 20080411 device查看需要传输的文件

book@100ask:~/workspaces/testImg$ ls bus_640-640.jpg bus_640-640.jpg传输文件到开发板中

book@100ask:~/workspaces/testImg$ adb push bus_640-640.jpg /mnt/UDISK bus_640-640.jpg: 1 file pushed. 0.7 MB/s (97293 bytes in 0.128s)开发板端:

进入测试图像目录

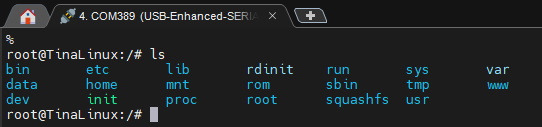

root@TinaLinux:/# cd /mnt/UDISK/ root@TinaLinux:/mnt/UDISK# ls bus_640-640.jpg lost+found overlayyolov5程序参数要求:yolov5 <模型文件路径> <测试图像路径>

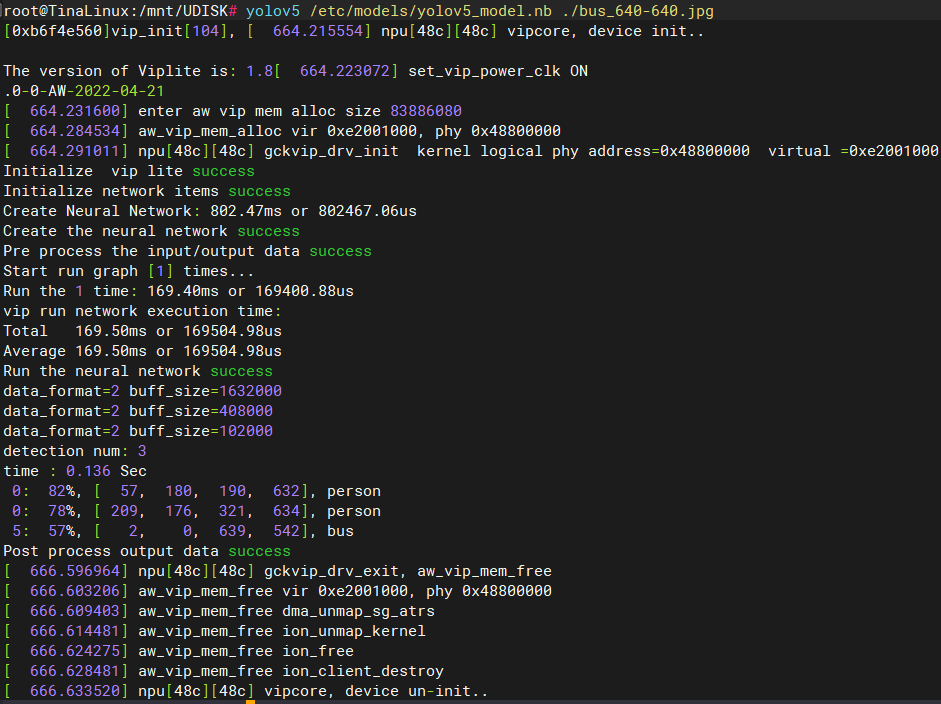

如果您打包了默认的yolov5模型文件,可以输入

yolov5 /etc/models/yolov5_model.nb ./bus_640-640.jpg如果您需要选择自己的模型文件进行测试,可以将上面的

/etc/models/yolov5_model.nb更换为自己的模型路径,下面我以默认的模型文件进行测试。

查看输出图像文件

yolov5_out.jpgroot@TinaLinux:/mnt/UDISK# ls bus_640-640.jpg lost+found overlay yolov5_out.jpg主机端:

拉取输出文件

yolov5_out.jpg到当前文件夹下book@100ask:~/workspaces/testImg$ adb pull /mnt/UDISK/yolov5_out.jpg ./ /mnt/UDISK/yolov5_out.jpg: 1 file pulled. 0.9 MB/s (184894 bytes in 0.202s) image-20230625172512521.png)

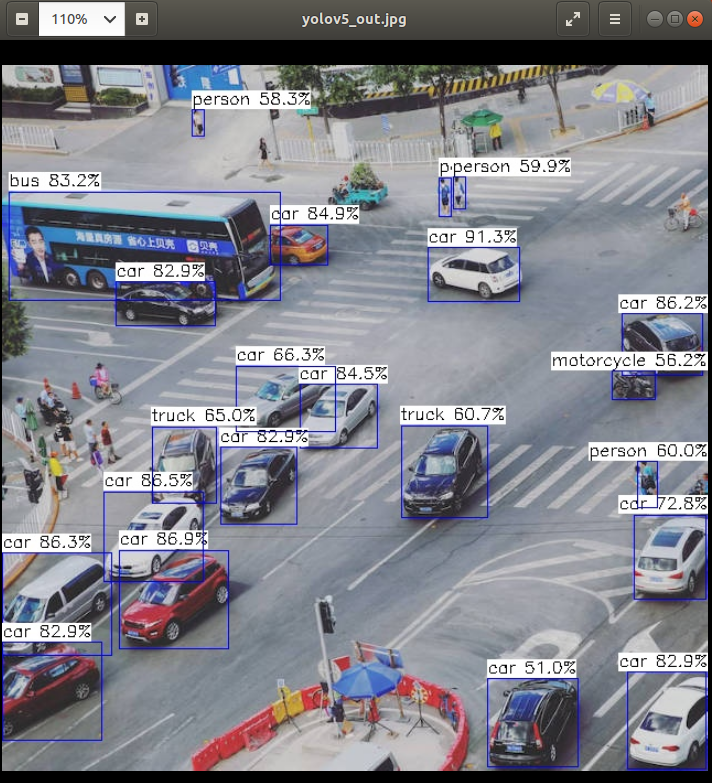

image-20230625172512521.png)4.4 测试其他图像

对于人形的识别,该模型还是比较准确的

对于交通道路这种复杂的情况,对于行人丢失些许目标,但对于车辆效果很好,丢失情况较少。

测试动物,对于动物的检测该模型是十分准确的,检测效果即预测精度都较高。

-

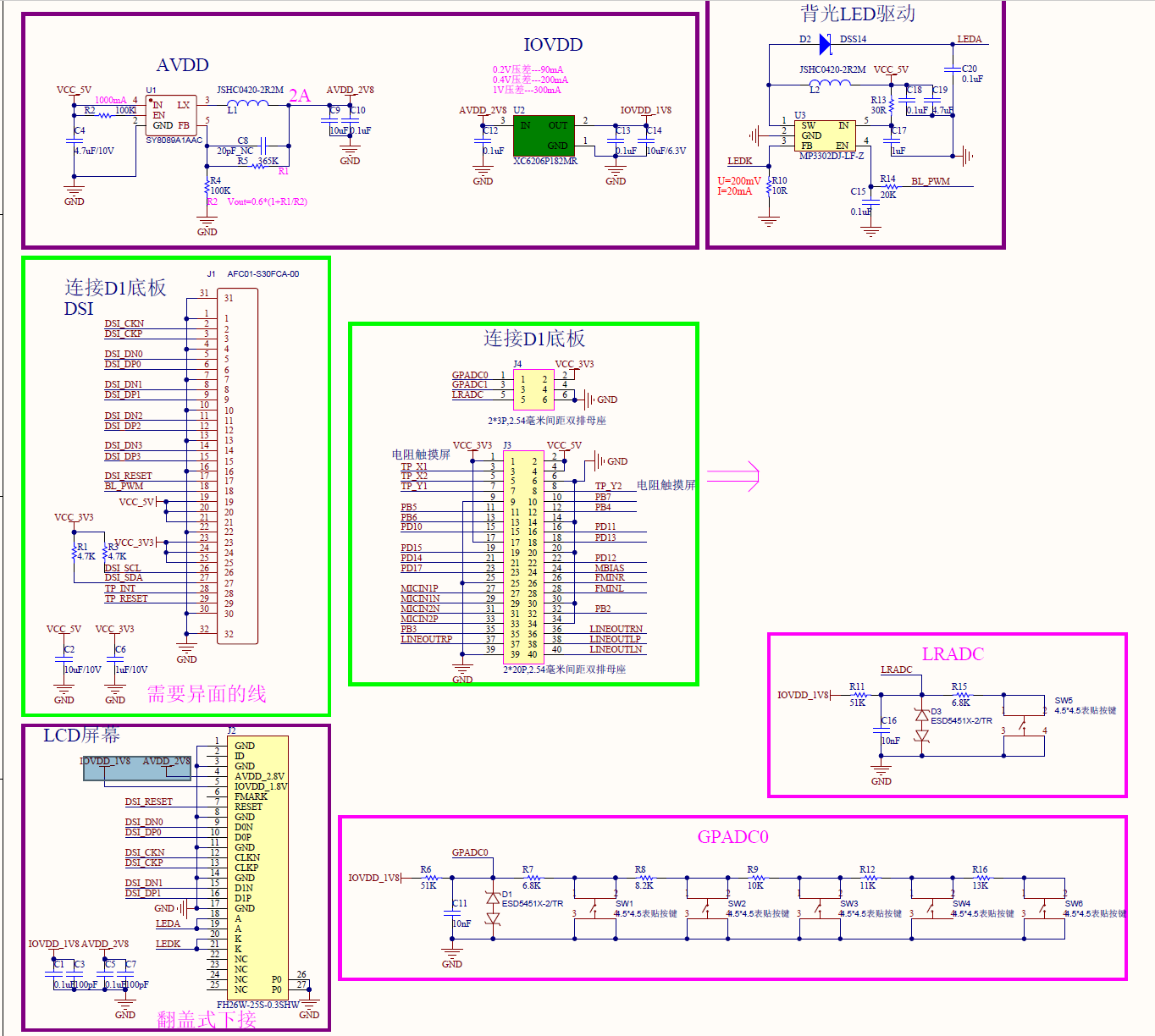

100ASK_V853-PRO开发板支持按键输入发布在 V Series

100ASK_V853-PRO开发板支持按键输入

0.前言

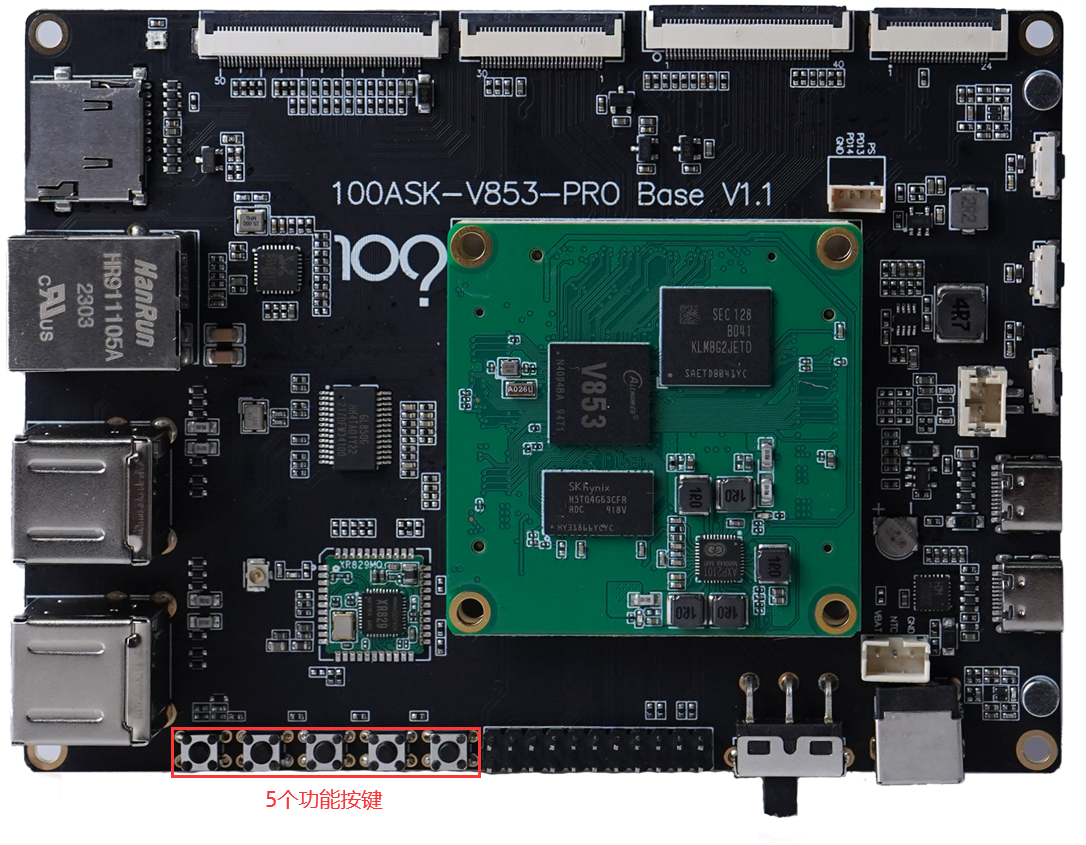

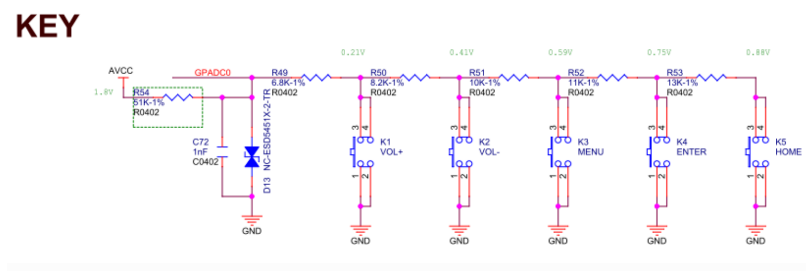

100ASK_V853-PRO开发板上共有5个功能按键,本章节跟大家讨论如何使能这五个按键。

1.V853功能按键原理

100ASK_V853-PRO开发板上提供的5个按键是通过GPADC高精度数模转换模块模拟出5个功能按键。GPADC 是 12bit

分辨率,8 位采集精度的模数转换模块,具体通道数可以查看对应的 spec 说明⽂档,模拟输⼊范 围 0〜1.8V,最⾼采样率

1MHz,并且⽀持数据⽐较,⾃校验功能,同时⼯作于可配置⼀下⼯作模式:

- Single mode:在指定的通道完成⼀次转换并将数据放在对应数据寄存器中;

- Single-cycle mode:在指定的通道完成⼀个周期转换并将数据放在响应数据寄存器中;

- Continuous mode:在指定的通道持续转换并将数据放在响应数据寄存器中;

- Burst mode:边采样边转换并将数据放⼊ 32 字节的 FIFO,⽀持中断控制。

部分 GPADC 接⼝也开始慢慢⽤于 KEY 模块按键的读取,⼀般包括 VOL+、VOL-、HOME、MENU、ENTER 等等, GPADC0 ⽤于 KEY 的电路如上图。 AVCC-AP 为 1.8V 的供电,不同的按键按下,GPADC0 ⼝的电压不同,CPU 通过对这个电压的采样来确定具体是那 ⼀个按键按下。如上图,VOL+、VOL-、MENU、ENTER、HOME/UBOOT 对应的电压分别为 0.21V、0.41V、 0.59V、0.75V、0.88V。具体可以查看《100ASK-V853_Pro系统开发手册.pdf》中第五篇驱动开发的第⼗三章 Linux GPADC 开发指南。

2.GPADC驱动

GPADC驱动存放的位置为

tina-v853-open/kernel/linux-4.9/drivers/input/sensor/sunxi_gpadc.c tina-v853-open/kernel/linux-4.9/drivers/input/sensor/sunxi_gpadc.h3.GPADC内核配置

在Tina的根目录下输入

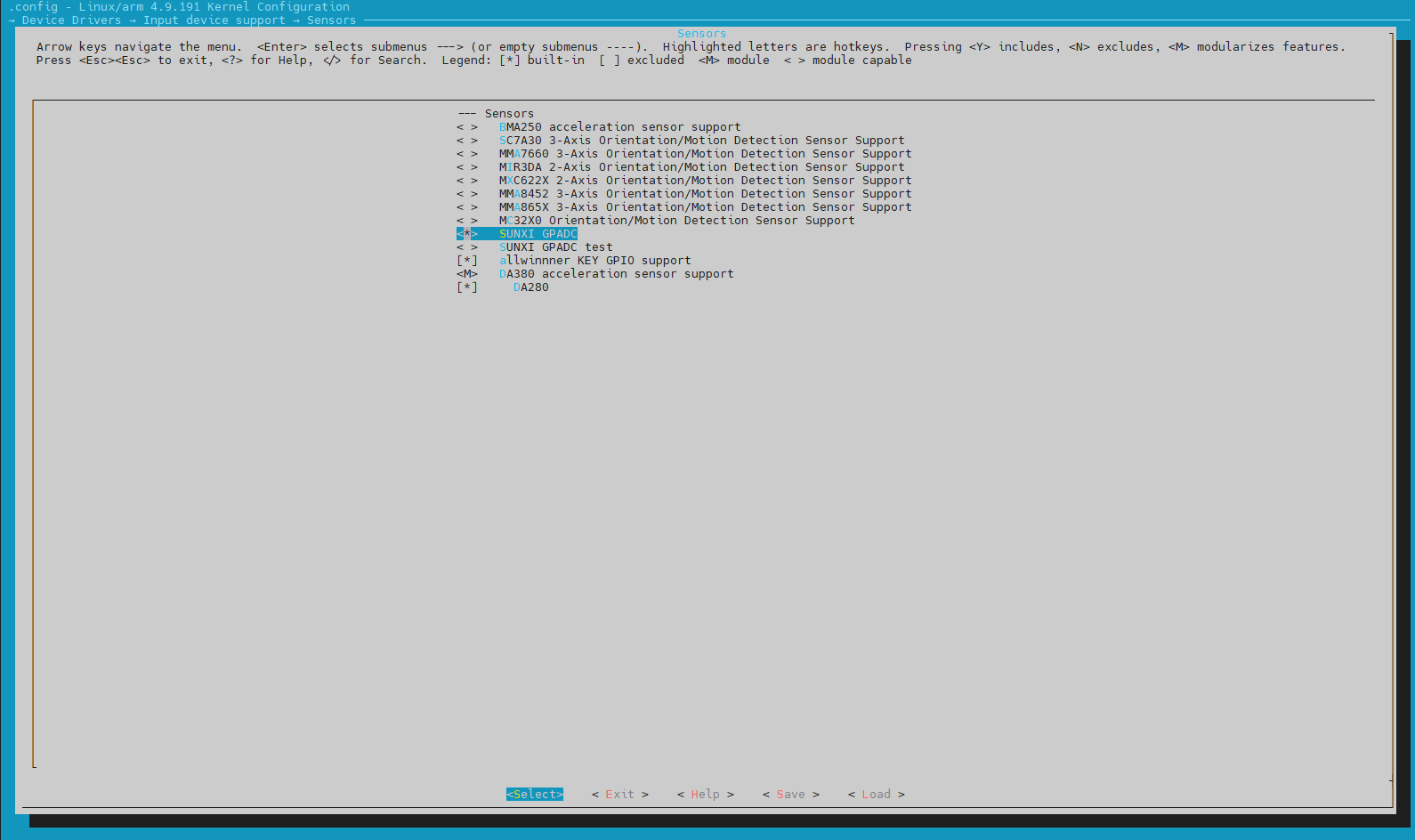

make kernel_menuconfigbook@100ask:~/workspaces/tina-v853-open$ make kernel_menuconfig进入如下目录中,输入Y使能SUNXI GPADC驱动。

→ Device Drivers → Input device support → Sensors <*> SUNXI GPADC配置完成后如下图所示。

保存并退出内核配置界面。

4.GPADC设备树配置

内核设备树存放位置:

tina-v853-open/device/config/chips/v853/configs/100ask/board.dts进入该目录后输入

vi board.dtsbook@100ask:~/workspaces/tina-v853-open$ cd device/config/chips/v853/configs/100ask/ book@100ask:~/workspaces/tina-v853-open/device/config/chips/v853/configs/100ask$ ls BoardConfig.mk board.dts buildroot env.cfg linux-4.9 sys_config.fex uboot-board.dts book@100ask:~/workspaces/tina-v853-open/device/config/chips/v853/configs/100ask$ vi board.dts找到&gpadc节点,这个节点保存有采样相关的配置,键值,电压数据等。

&gpadc { channel_num = <1>; // 使用1通道 channel_select = <0x01>; // 选择 0x01 通道 channel_data_select = <0>; // 启用数据通道 channel_compare_select = <0x01>; // 启用通道比较功能 channel_cld_select = <0x01>; // 启用数据小于比较功能 channel_chd_select = <0>; // 启用数据大于比较功能 channel0_compare_lowdata = <1700000>; // 小于这个值触发中断 channel0_compare_higdata = <1200000>; // 大于这个值触发中断 channel1_compare_lowdata = <460000>; // 小于这个值触发中断 channel1_compare_higdata = <1200000>; // 大于这个值触发中断 key_cnt = <5>; // 按键数量 key0_vol = <210>; // 按键电压,单位mv key0_val = <115>; // 按下按键的键值 key1_vol = <410>; // 按键电压,单位mv key1_val = <114>; // 按下按键的键值 key2_vol = <590>; // 按键电压,单位mv key2_val = <139>; // 按下按键的键值 key3_vol = <750>; // 按键电压,单位mv key3_val = <28>; // 按下按键的键值 key4_vol = <880>; // 按键电压,单位mv key4_val = <102>; // 按下按键的键值 status = "okay"; // 启用GPADC };我们还能通过board.dts文件中知道还有一部分不经常需要修改的配置保存在sun8iw21p1.dtsi文件中,进入该目录,并打开该文件。

book@100ask:~/workspaces/tina-v853-open$ cd kernel/linux-4.9/arch/arm/boot/dts/ book@100ask:~/workspaces/tina-v853-open/kernel/linux-4.9/arch/arm/boot/dts$ vi sun8iw21p1.dtsi查看gpadc节点,可以发现这里的配置保存有中断和时钟等信息,但默认不使能。注意:这里可以不修改,因为这里的所设置的status配置会被board.dts中的status覆盖,只要在board.dts设置为使能,最终生成打包进镜像的设备树都为使能状态。

gpadc:gpadc@2009000 { compatible = "allwinner,sunxi-gpadc"; // 用于驱动和设备的绑定 reg = <0x0 0x02009000 0x0 0x400>; // 设备使用的寄存器地址 interrupts = <GIC_SPI 57 IRQ_TYPE_NONE>; // 设备使用的中断 clocks = <&clk_gpadc>; // 设备使用的时钟 status = "disabled"; // 配置默认不启用GPADC };5.增加getevent测试包

在Tina根目录下执行

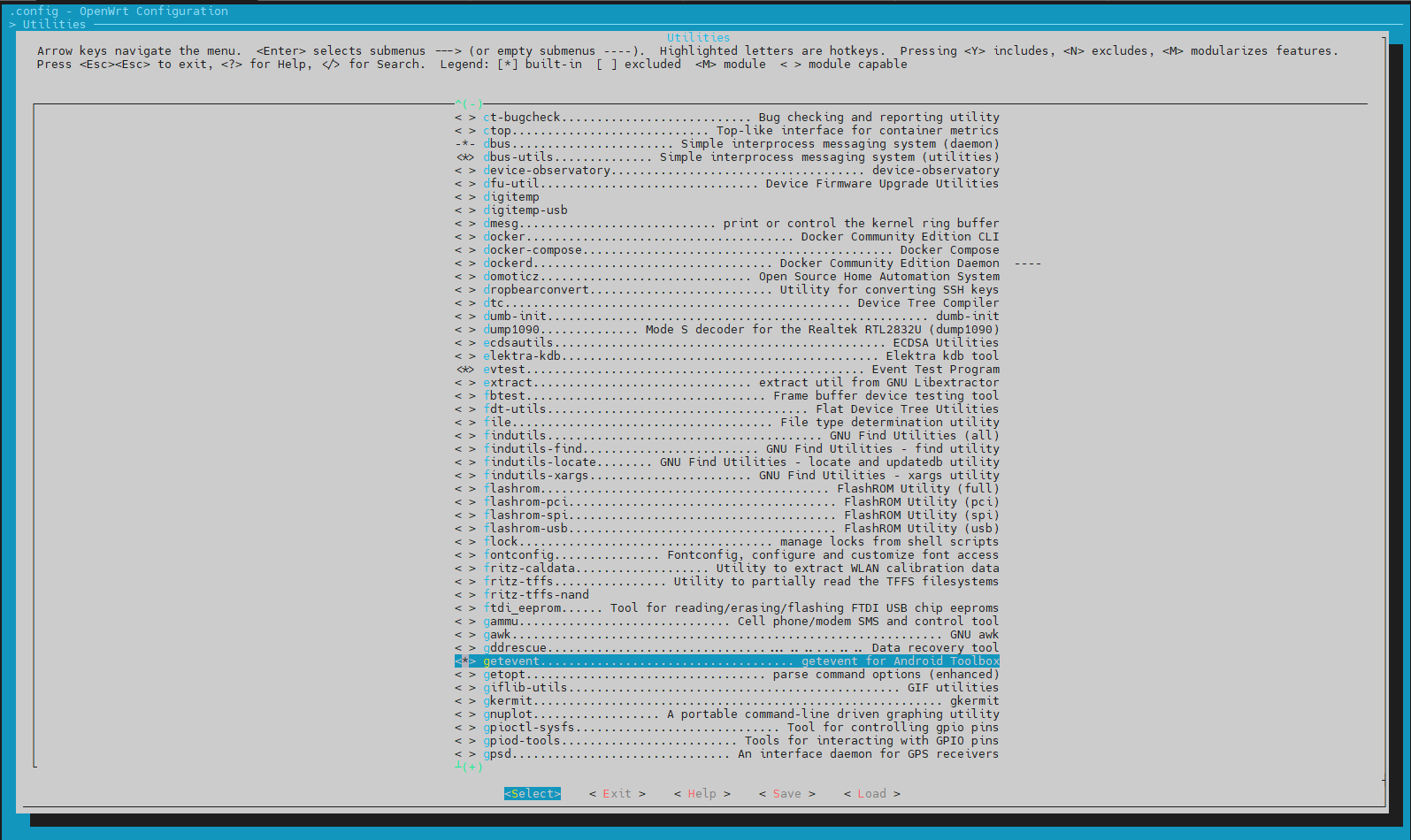

make menuconfigbook@100ask:~/workspaces/tina-v853-open$ make menuconfig进入Utilities目录下,输入Y选中getevent

> Utilities <*> getevent.................................... getevent for Android Toolbox选中完成后如下图所示。

保存并退出Tina配置界面。6.编译、打包和烧写

在Tina的根目录下,输入

make -j32book@100ask:~/workspaces/tina-v853-open$ make -j32 ... book@100ask:~/workspaces/tina-v853-open$ pack ... 生成镜像后,将tina-v853-open/out/v853/100ask/openwrt/目录下的v853_linux_100ask_uart0.img镜像拷贝到Windows电脑主机中,使用全志PhoenixSuit烧写工具烧写到开发板上。

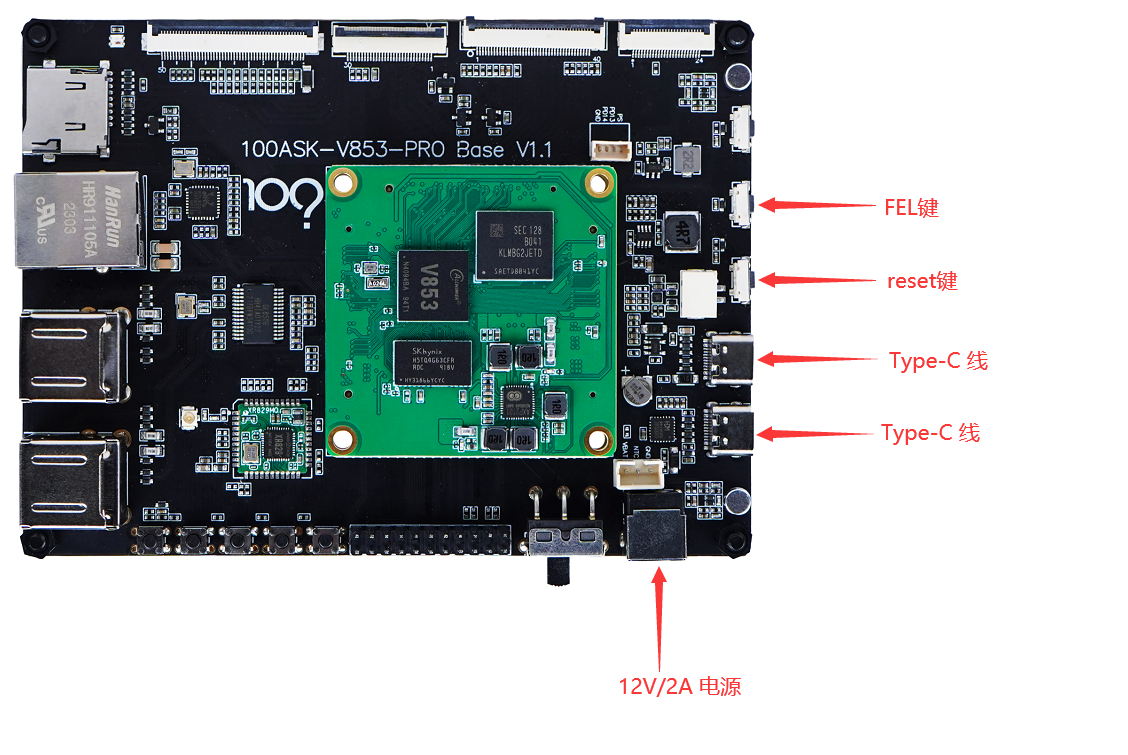

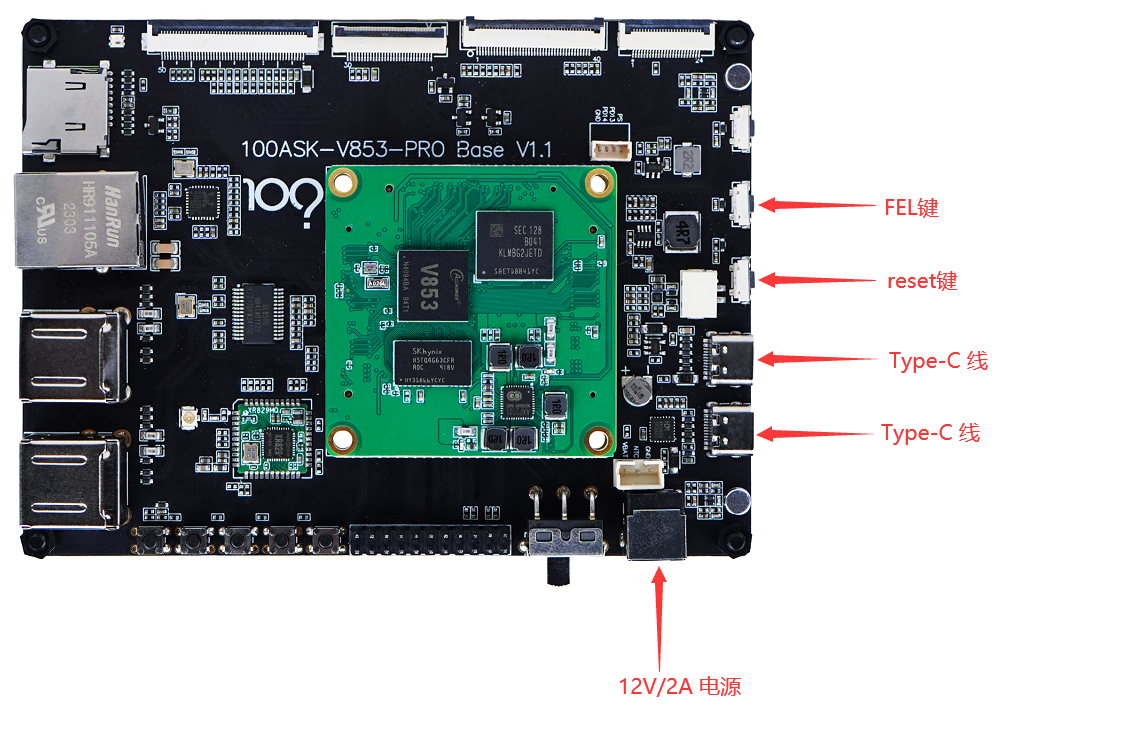

插上12V的电源线,和两条Type-C,把开关拨向电源接口方向上电,烧写新镜像后等待启动系统,在命令行中输入

getevent可以进入测试程序,通过输出的打印信息我们知道,我们的gpadc驱动上报的信息使用的是

/dev/input/event1,此时按下按键,会读取按键的键值。root@TinaLinux:~# getevent add device 1: /dev/input/event2 name: "ft6336" add device 2: /dev/input/event1 name: "sunxi-gpadc0" add device 3: /dev/input/event0 name: "axp2101-pek" poll 4, returned 1 /dev/input/event1: 0001 0073 00000001 poll 4, returned 1 /dev/input/event1: 0000 0000 00000000 poll 4, returned 1 /dev/input/event1: 0001 0073 00000000 poll 4, returned 1 /dev/input/event1: 0000 0000 00000000按下Crtl+C结束测试。

7.编写一个测试应用程序

通过上一章节的测试,我们知道gpadc使用的

/dev/input/event1上报按键数据,则我们编写的应用程序中获取数据的节点应该为/dev/input/event1,应用程序如下所示。#include <stdio.h> #include <linux/input.h> #include <stdlib.h> #include <sys/types.h> #include <sys/stat.h> #include <fcntl.h> #include <sys/time.h> #include <limits.h> #include <unistd.h> #include <signal.h> #define DEV_PATH "/dev/input/event1" //Modified to gpadc drive reporting node static int gpadc_fd = 0; unsigned int test_gpadc(const char * event_file) { int code = 0, i; struct input_event data; gpadc_fd = open(DEV_PATH, O_RDONLY); if(gpadc_fd <= 0) { printf("open %s error!\n", DEV_PATH); return -1; } for(i = 0; i < 10; i++) //read 10 times { read(gpadc_fd, &data, sizeof(data)); if(data.value == 1) { printf("key %d pressed\n", data.code); } else if(data.value == 0) { printf("key %d releaseed\n", data.code); } } close(gpadc_fd); return 0; } int main(int argc,const char *argv[]) { int rang_low = 0, rang_high = 0; return test_gpadc(DEV_PATH);8.编译应用程序并进行测试

新建一个gpadc目录,存放应用程序和可执行程序。

book@100ask:~/workspaces$ mkdir gpadc_test book@100ask:~/workspaces$ cd gpadc_test/ book@100ask:~/workspaces/gpadc_test$ vi gpadc_test.c将上一小节编写的应用程序复制到gpadc_test.c中保存。

编写完成后,我们需要提供编译环境给gpadc_test应用程序,输入

book@100ask:~/workspaces/gpadc_test$ export STAGING_DIR=~/workspaces/tina-v853-open/prebuilt/rootfsbuilt/arm/toolchainsunxi-musl-gcc-830/toolchain/arm-openwrt-linux-muslgnueabi使用交叉编译工具链编译二进制文件,注意:需要Tina SDK包目录需要更换为自己的目录。

book@100ask:~/workspaces/gpadc_test$ ~/workspaces/tina-v853-open/prebuilt/rootfsbuilt/arm/toolchain-sunxi-musl-gcc-830/toolchain/bin/arm-openwrt-linux-gcc -o gpadc_test gpadc_test.c编译完成后会再当前目录下生成一个gpadc_test可执行程序,将其拷贝到开发板上运行即可。下面使用TF卡的方式将文件拷贝到开发板上,此时假设你已经将文件拷贝到TF卡中,插入开发板后,在命令行中输入以下命令挂在SD卡到

/mnt/目录下,并将gpadc_test应用程序拷贝到、root目录下。root@TinaLinux:/# mount /dev/mmcblk1p1 /mnt/ [ 26.744697] FAT-fs (mmcblk1p1): Volume was not properly unmounted. Some data may be corrupt. Please run fsck. root@TinaLinux:/# cd /mnt/ root@TinaLinux:/mnt# ls System Volume Information gpadc_test root@TinaLinux:/mnt# cp gpadc_test /root/进入/root目录下执行测试程序,该程序读取10次值会自动结束才测试

root@TinaLinux:/mnt# cd /root/ root@TinaLinux:~# ./gpadc_test key 115 pressed key 0 releaseed key 115 releaseed key 0 releaseed key 114 pressed key 0 releaseed key 114 releaseed key 0 releaseed key 139 pressed key 0 releaseed -

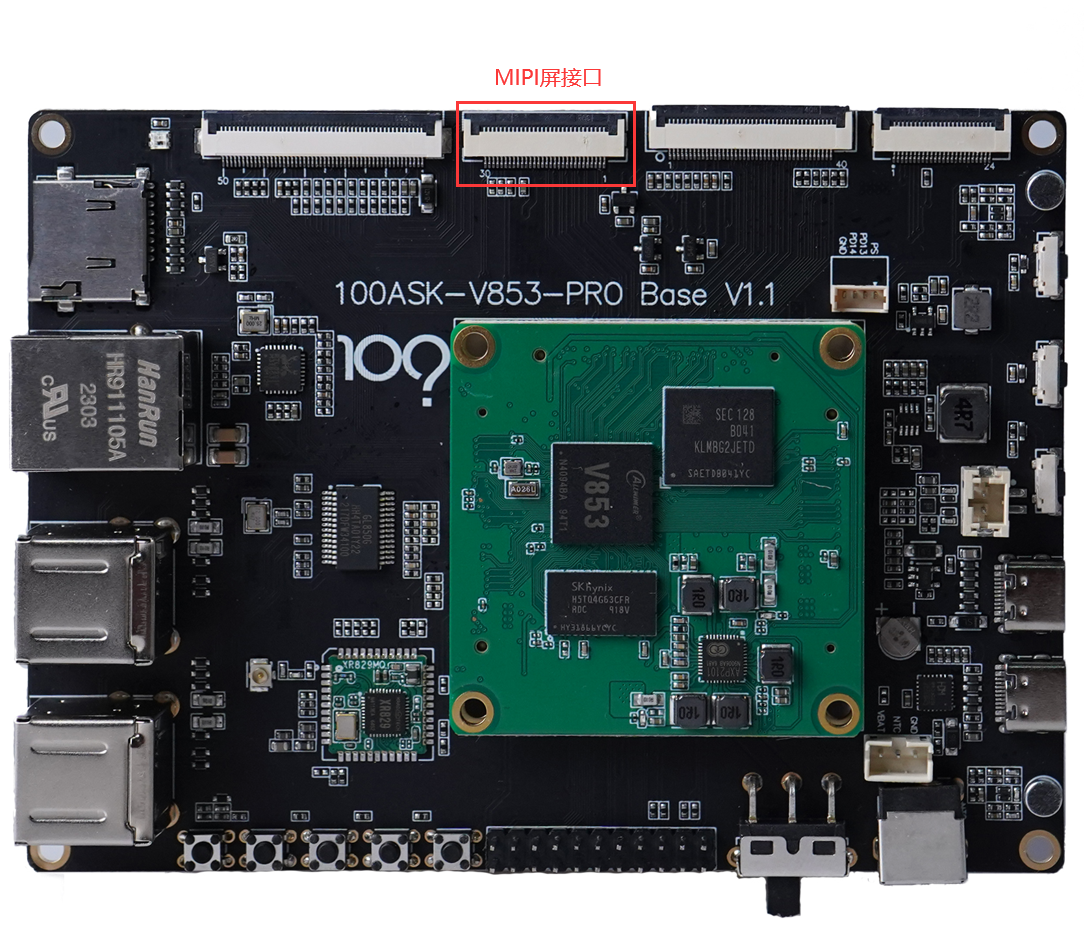

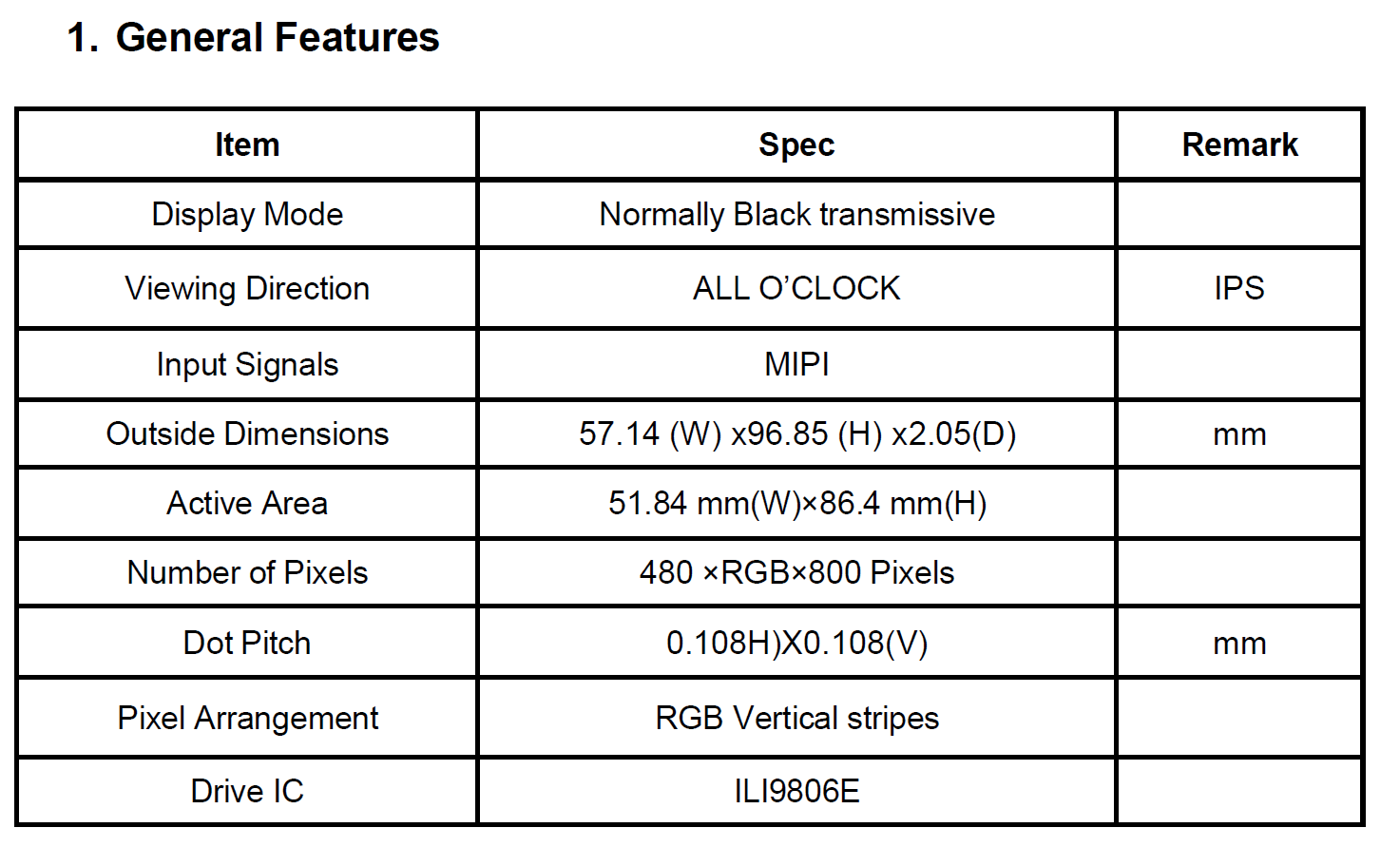

100ASK_V853-PRO开发板支持4寸MIPI屏发布在 V Series

100ASK_V853-PRO开发板支持4寸MIPI屏

0.前言

由于之前我们已经适配过RGB屏,如果我们去适配了4寸MIPI屏,那么RGB屏就不能使用了。对于4寸屏购买链接为:

LCD_调试指南:https://tina.100ask.net/SdkModule/Linux_LCD_DevelopmentGuide-01/

Display_开发指南:https://tina.100ask.net/SdkModule/Linux_Display_DevelopmentGuide-01/

4寸屏适配资源包:V853支持4寸MIPI屏source.zip 。该资源包里面包含了适配修改后的所有文件(包括驱动程序、设备树和配置文件等)

1.添加新驱动

将驱动程序添加到

内核的lcd驱动目录下:

tina-v853-open/kernel/linux-4.9/drivers/video/fbdev/sunxi/disp2/disp/lcduboot的lcd驱动目录下:

tina-v853-open/brandy/brandy-2.0/u-boot-2018/drivers/video/sunxi/disp2/disp/lcd/由于uboot和内核中的屏驱动会存在一些差别,下面分别展示出uboot和内核中不同的屏驱动。具体源文件可以在4寸屏适配资源包中查看。

1.1 uboot驱动程序

驱动程序头文件tft08006.h

#ifndef _TFT08006_H #define _TFT08006_H #include "panels.h" extern __lcd_panel_t tft08006_panel; extern s32 bsp_disp_get_panel_info(u32 screen_id, disp_panel_para *info); #endif /*End of file*/驱动程序的C文件tft08006.c

这里只展示与内核不同的部分

__lcd_panel_t tft08006_panel = { /* panel driver name, must mach the name of * lcd_drv_name in sys_config.fex */ .name = "tft08006", .func = { .cfg_panel_info = lcd_cfg_panel_info, .cfg_open_flow = lcd_open_flow, .cfg_close_flow = lcd_close_flow, .lcd_user_defined_func = lcd_user_defined_func, }, };1.2 内核驱动程序

驱动程序头文件tft08006.h

#ifndef _TFT08006_H #define _TFT08006_H #include "panels.h" extern struct __lcd_panel tft08006_panel; extern s32 bsp_disp_get_panel_info(u32 screen_id, struct disp_panel_para *info); #endif /*End of file*/驱动程序的C文件"tft08006.c,这里只展示与uboot不同的部分。

struct __lcd_panel tft08006_panel = { /* panel driver name, must mach the name of * lcd_drv_name in sys_config.fex */ .name = "tft08006", .func = { .cfg_panel_info = lcd_cfg_panel_info, .cfg_open_flow = lcd_open_flow, .cfg_close_flow = lcd_close_flow, .lcd_user_defined_func = lcd_user_defined_func, }, };2.修改内核中panels.h和panels.c

由于内核中没有对tft08006屏驱动有相关的配置,所以我们还需要在panels全志显示驱动中增加定义。

2.1 修改内核中panels.h

在屏驱动目录下修改panels.h

book@100ask:~/workspaces/tina-v853-open/kernel/linux-4.9/drivers/video/fbdev/sunxi/disp2/disp/lcd$ vi panels.h在icn6202屏驱动定义的后面增加tft08006屏驱动定义

#ifdef CONFIG_LCD_SUPPORT_ICN6202 extern struct __lcd_panel icn6202_panel; #endif #ifdef CONFIG_LCD_SUPPORT_ICN6202 extern struct __lcd_panel icn6202_panel; #endif #ifdef CONFIG_LCD_SUPPORT_NT35510_MIPI extern struct __lcd_panel nt35510_panel; #endif按下ESC,输入

:wq,保存刚才的修改并退出2.2 修改内核中panels.c

在屏驱动目录下修改panels.c

book@100ask:~/workspaces/tina-v853-open/kernel/linux-4.9/drivers/video/fbdev/sunxi/disp2/disp/lcd$ vi panels.c在icn6202屏驱动定义的后面增加tft08006屏驱动定义

#ifdef CONFIG_LCD_SUPPORT_ICN6202 &icn6202_panel, #endif #ifdef CONFIG_LCD_SUPPORT_TFT08006 &tft08006_panel, #endif #ifdef CONFIG_LCD_SUPPORT_NT35510_MIPI &nt35510_panel, #endif按下ESC,输入

:wq,保存刚才的修改并退出3.修改内核中Kconfig和Makefile

3.1 修改内核中的Kconfig

修改屏驱动目录下的Kconfig,使内核配置中增加tft08006屏驱动的,以便后续选择编译该屏驱动

在屏驱动目录下输入

vi Kconfigtina-v853-open/kernel/linux-4.9/drivers/video/fbdev/sunxi/disp2/disp/lcd$ vi Kconfig在icn6202屏驱动配置的后面增加tft08006屏驱动配置

config LCD_SUPPORT_ICN6202 bool "LCD support icn6202 panel" default n ---help--- If you want to support icn6202 panel for display driver, select it. config LCD_SUPPORT_TFT08006 bool "LCD support tft08006 panel" default n ---help--- If you want to support tft08006 panel for display driver, select it. config LCD_SUPPORT_NT35510_MIPI bool "LCD support nt35510_mipi panel" default n help If you want to support nt35510_mipi panel for display driver, select it.按下ESC,输入

:wq,保存刚才的修改并退出3.2 修改内核中的Makefile

返回屏驱动的上一级目录,修改Makefile文件

book@100ask:~/workspaces/tina-v853-open/kernel/linux-4.9/drivers/video/fbdev/sunxi/disp2/disp$ vi Makefile在icn6202屏驱动编译规则的后面增加tft08006屏驱动编译规则

disp-$(CONFIG_LCD_SUPPORT_ICN6202) += lcd/icn6202.o disp-$(CONFIG_LCD_SUPPORT_TFT08006) += lcd/tft08006.o disp-$(CONFIG_LCD_SUPPORT_NT35510_MIPI) += lcd/nt35510.o按下ESC,输入

:wq,保存刚才的修改并退出4.修改内核配置

在Tina的根目录下输入

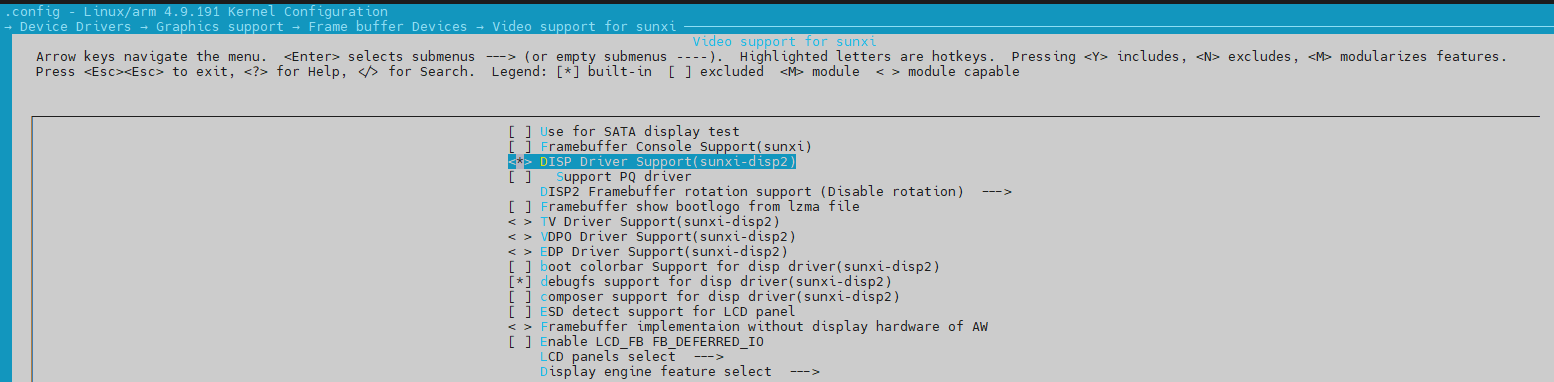

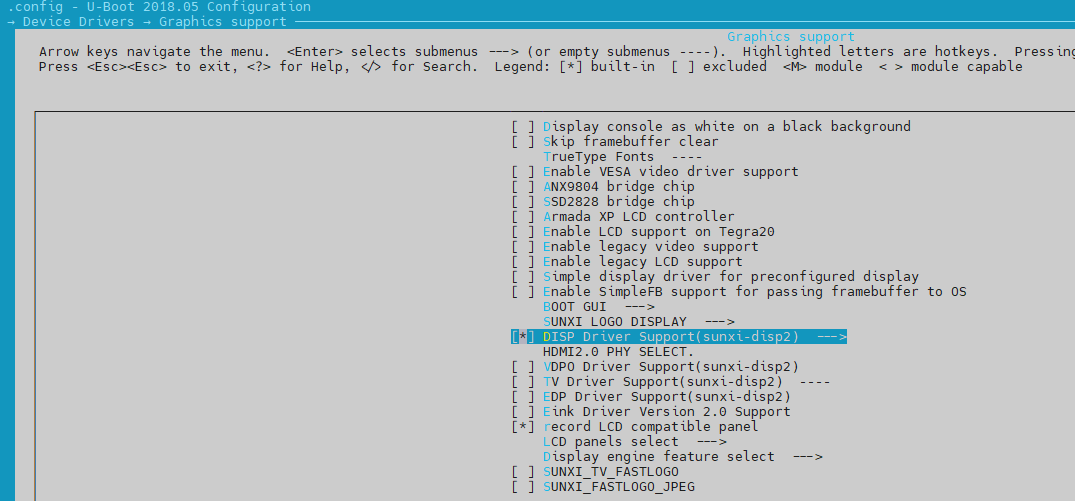

make kernel_menuconfig,进入内核配置界面。book@100ask:~/workspaces/tina-v853-open$ make kernel_menuconfig在选中屏驱动前,要确保

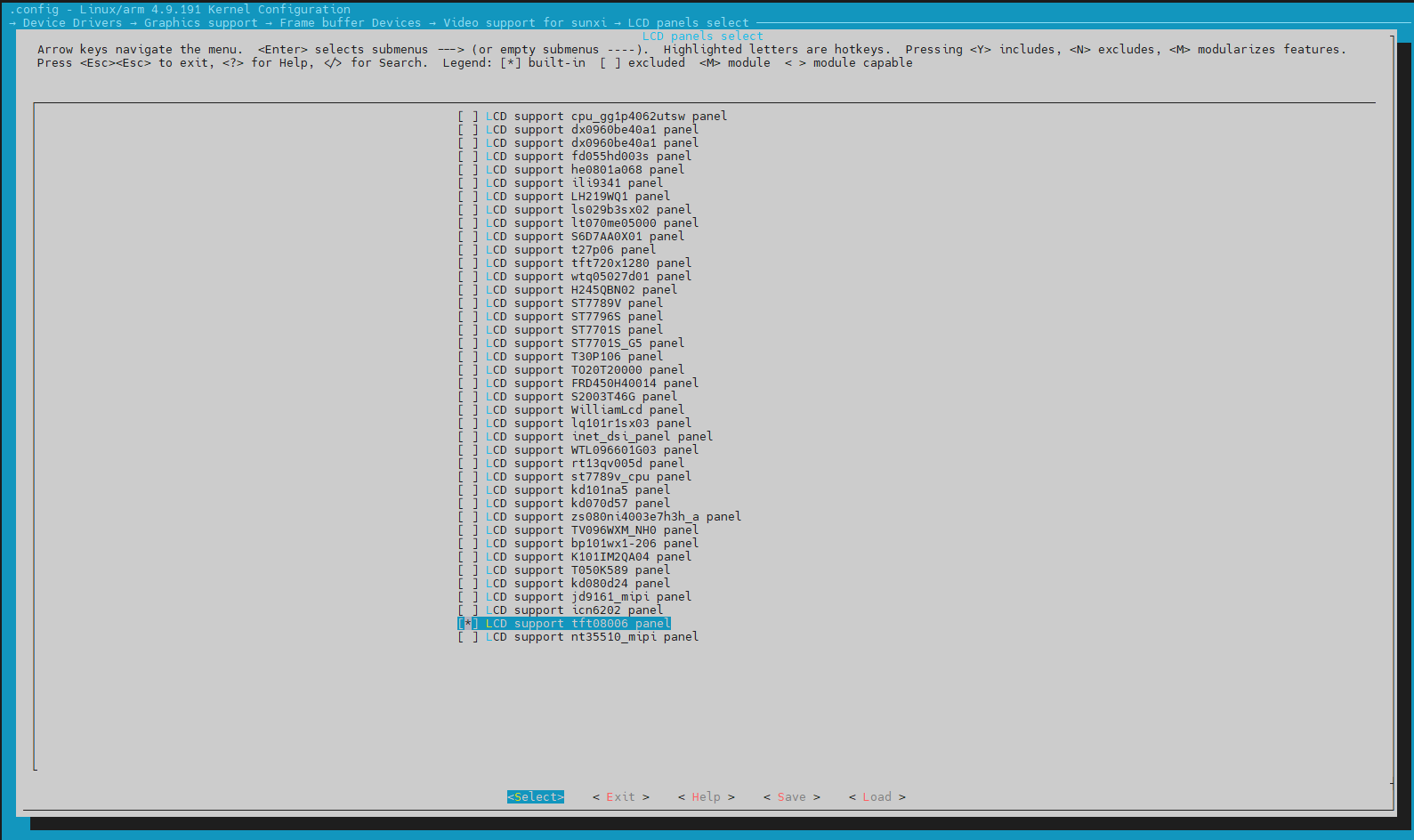

DISP Driver Support(sunxi-disp2),我们的提供的SDK默认已经打开了,如果您之前关闭了,需要在内核配置界面中,进入Video support for sunxi目录下输入Y选中sunxi-disp2打开lcd节点配置。→ Device Drivers → Graphics support → Frame buffer Devices → Video support for sunxi <*> DISP Driver Support(sunxi-disp2)进入屏驱动目录,输入Y选中tft08006

→ Device Drivers → Graphics support → Frame buffer Devices → Video support for sunxi → LCD panels select [*] LCD support tft08006 panel如下图所示,选中tft08006屏驱动,编译到内核中。

保存并推车内核配置界面。

5.修改uboot配置

进入uboot的根目录下,执行

make menuconfig,打开uboot配置界面。book@100ask:~/workspaces/tina-v853-open/brandy/brandy-2.0/u-boot-2018$ make menuconfig在选中屏驱动前,要确保

DISP Driver Support(sunxi-disp2),我们的提供的SDK默认已经打开了,如果您之前关闭了,需要在内核配置界面中,进入Graphics support目录下输入Y选中sunxi-disp2打开lcd节点配置。→ Device Drivers → Graphics support [*] DISP Driver Support(sunxi-disp2) --->进入屏驱动目录下,输入Y选中TFT08006屏驱动。

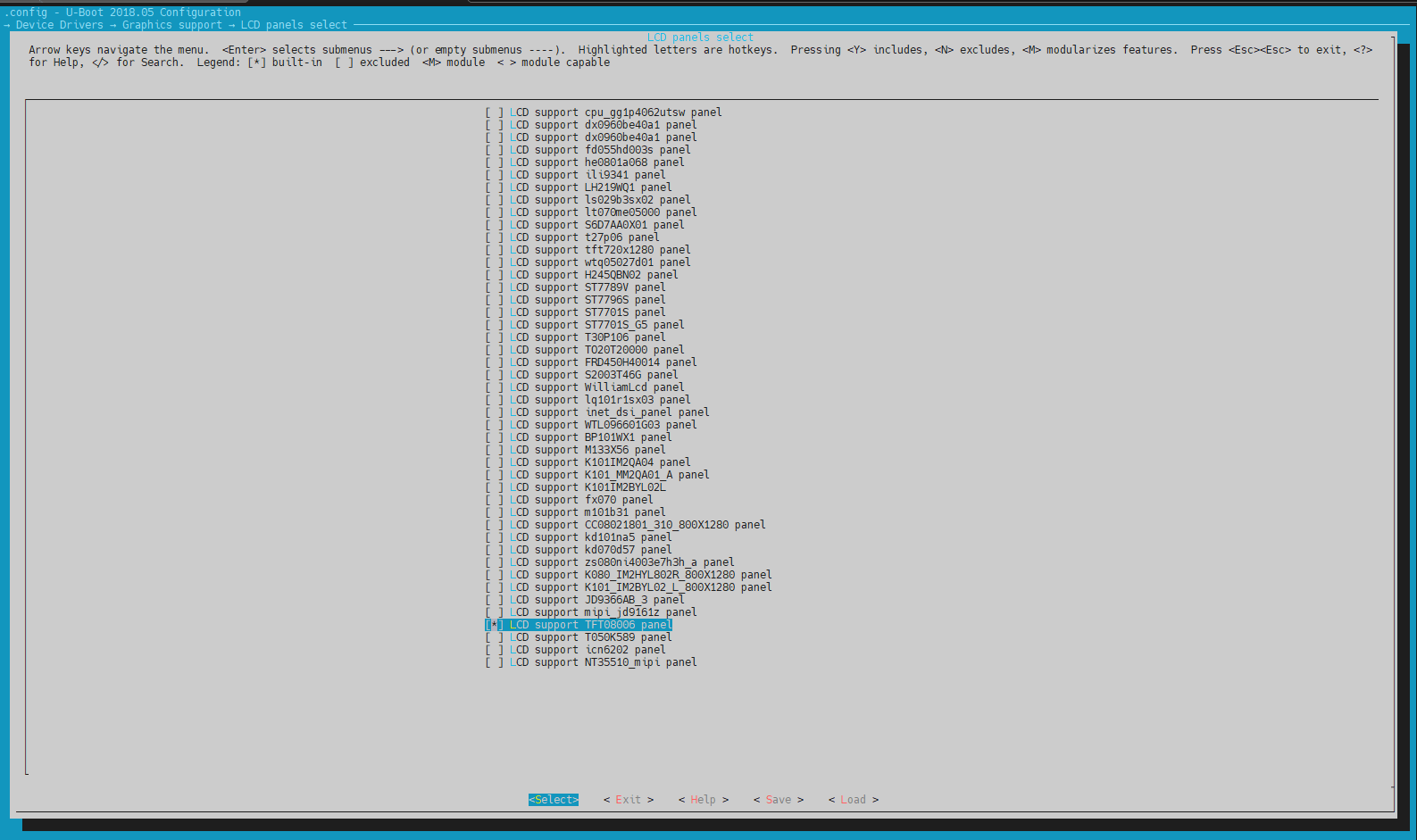

→ Device Drivers → Graphics support → LCD panels select [*] LCD support TFT08006 panel如下图所示,选中tft08006屏驱动。

保存并退出uboot配置界面6.修改设备树

设备树位置:tina-v853-open/device/config/chips/v853/configs/100ask/

book@100ask:~/workspaces/tina-v853-open/device/config/chips/v853/configs/100ask$ ls BoardConfig.mk board.dts buildroot env.cfg linux-4.9 sys_config.fex uboot-board.dts其中board.dts为内核设备树,uboot-board.dts为uboot设备树。

6.1 修改uboot设备树

在设备树的目录下输入

vi uboot-board.dts,编译uboot设备树。book@100ask:~/workspaces/tina-v853-open/device/config/chips/v853/configs/100ask$ vi uboot-board.dts注释掉原来的lcd0节点,修改tft08006屏lcd0节点

&lcd0 { base_config_start = <1>; lcd_used = <1>; lcd_driver_name = "tft08006"; lcd_backlight = <500>; lcd_if = <4>; lcd_x = <480>; lcd_y = <800>; lcd_width = <52>; lcd_height = <52>; lcd_dclk_freq = <25>; lcd_pwm_used = <1>; lcd_pwm_ch = <9>; lcd_pwm_freq = <50000>; lcd_pwm_pol = <1>; lcd_pwm_max_limit = <255>; lcd_hbp = <10>; lcd_ht = <515>; lcd_hspw = <5>; lcd_vbp = <20>; lcd_vt = <830>; lcd_vspw = <5>; lcd_dsi_if = <0>; lcd_dsi_lane = <2>; lcd_dsi_format = <0>; lcd_dsi_te = <0>; lcd_dsi_eotp = <0>; lcd_frm = <0>; lcd_io_phase = <0x0000>; lcd_hv_clk_phase = <0>; lcd_hv_sync_polarity= <0>; lcd_gamma_en = <0>; lcd_bright_curve_en = <0>; lcd_cmap_en = <0>; lcdgamma4iep = <22>; lcd_gpio_0 = <&pio PH 0 1 0 3 1>; pinctrl-0 = <&dsi4lane_pins_a>; pinctrl-1 = <&dsi4lane_pins_b>; base_config_end = <1>; };在&pio节点后增加复用引脚

dsi4lane_pins_a: dsi4lane@0 { allwinner,pins = "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD9", "PD10", "PD11"; allwinner,pname = "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD9", "PD10", "PD11"; allwinner,function = "dsi"; allwinner,muxsel = <5>; allwinner,drive = <3>; allwinner,pull = <0>; }; dsi4lane_pins_b: dsi4lane@1 { allwinner,pins = "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD9", "PD10", "PD11"; allwinner,pname = "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD9", "PD10", "DP11"; allwinner,function = "io_disabled"; allwinner,muxsel = <0xf>; allwinner,drive = <1>; allwinner,pull = <0>; };6.2 修改内核设备树

在设备树的目录下输入

vi board.dts,编译内核设备树。book@100ask:~/workspaces/tina-v853-open/device/config/chips/v853/configs/100ask$ vi board.dts注释掉原来的lcd0节点,修改tft08006屏lcd0节点

&lcd0 { base_config_start = <1>; lcd_used = <1>; lcd_driver_name = "tft08006"; lcd_backlight = <500>; lcd_if = <4>; lcd_x = <480>; lcd_y = <800>; lcd_width = <52>; lcd_height = <52>; lcd_dclk_freq = <25>; lcd_pwm_used = <1>; lcd_pwm_ch = <9>; lcd_pwm_freq = <50000>; lcd_pwm_pol = <1>; lcd_pwm_max_limit = <255>; lcd_hbp = <10>; lcd_ht = <515>; lcd_hspw = <5>; lcd_vbp = <20>; lcd_vt = <830>; lcd_vspw = <5>; lcd_dsi_if = <0>; lcd_dsi_lane = <2>; lcd_dsi_format = <0>; lcd_dsi_te = <0>; lcd_dsi_eotp = <0>; lcd_frm = <0>; lcd_io_phase = <0x0000>; lcd_hv_clk_phase = <0>; lcd_hv_sync_polarity= <0>; lcd_gamma_en = <0>; lcd_bright_curve_en = <0>; lcd_cmap_en = <0>; lcdgamma4iep = <22>; lcd_gpio_0 = <&pio PH 0 1 0 3 1>; pinctrl-0 = <&dsi4lane_pins_a>; pinctrl-1 = <&dsi4lane_pins_b>; base_config_end = <1>; };在&pio节点后增加复用引脚

dsi4lane_pins_a: dsi4lane@0 { allwinner,pins = "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD9", "PD10", "PD11"; allwinner,pname = "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD9", "PD10", "PD11"; allwinner,function = "dsi"; allwinner,muxsel = <5>; allwinner,drive = <3>; allwinner,pull = <0>; }; dsi4lane_pins_b: dsi4lane@1 { allwinner,pins = "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD9", "PD10", "PD11"; allwinner,pname = "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD9", "PD10", "DP11"; allwinner,function = "io_disabled"; allwinner,muxsel = <0xf>; allwinner,drive = <1>; allwinner,pull = <0>; };7.增加I2C触摸

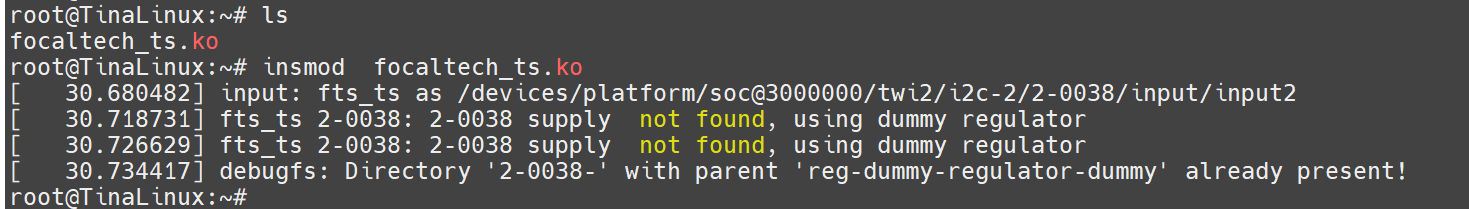

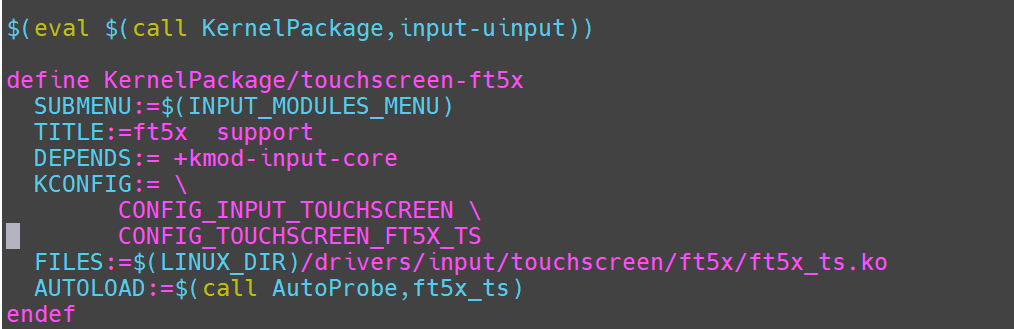

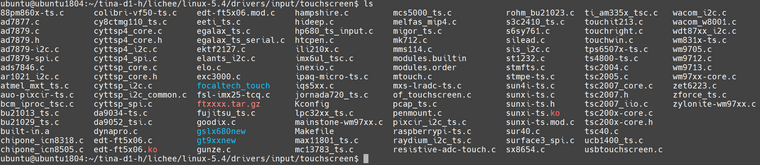

通过拿到的屏幕资料包,我们可以知道该MIPI屏的触摸芯片为FT5336,下面我们使用全志已经内置好的FT6336触摸驱动。

7.1 修改设备树

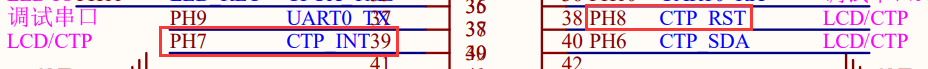

修改twi2节点,使用ft6336驱动,修改触摸的范围。宽X为480,高y为800。其中初始化引脚需要查看V853底板原理图,其中初始化引脚为PH7,唤醒引脚为PH8。

&twi2 { ctp@38 { status = "okay"; ctp_used = <1>; ctp_name = "ft6336"; ctp_twi_id = <0x2>; ctp_twi_addr = <0x38>; ctp_screen_max_x = <0x480>; ctp_screen_max_y = <0x800>; ctp_revert_x_flag = <0x0>; ctp_revert_y_flag = <0x1>; ctp_exchange_x_y_flag = <0x0>; ctp_int_port = <&pio PH 7 6 1 3 0xffffffff>; ctp_wakeup = <&pio PH 8 1 1 3 0xffffffff>; }; };对于设备树的参数意义,可以访问百问网的Tina站点:https://tina.100ask.net/SdkModule/Linux_Deploy_DevelopmentGuide-02/#39

7.2 修改内核配置

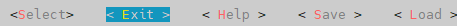

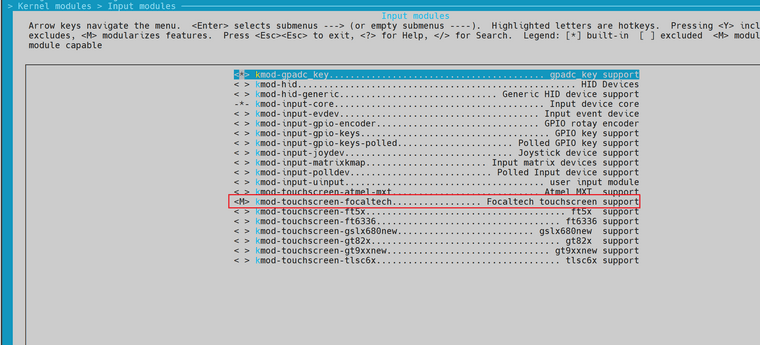

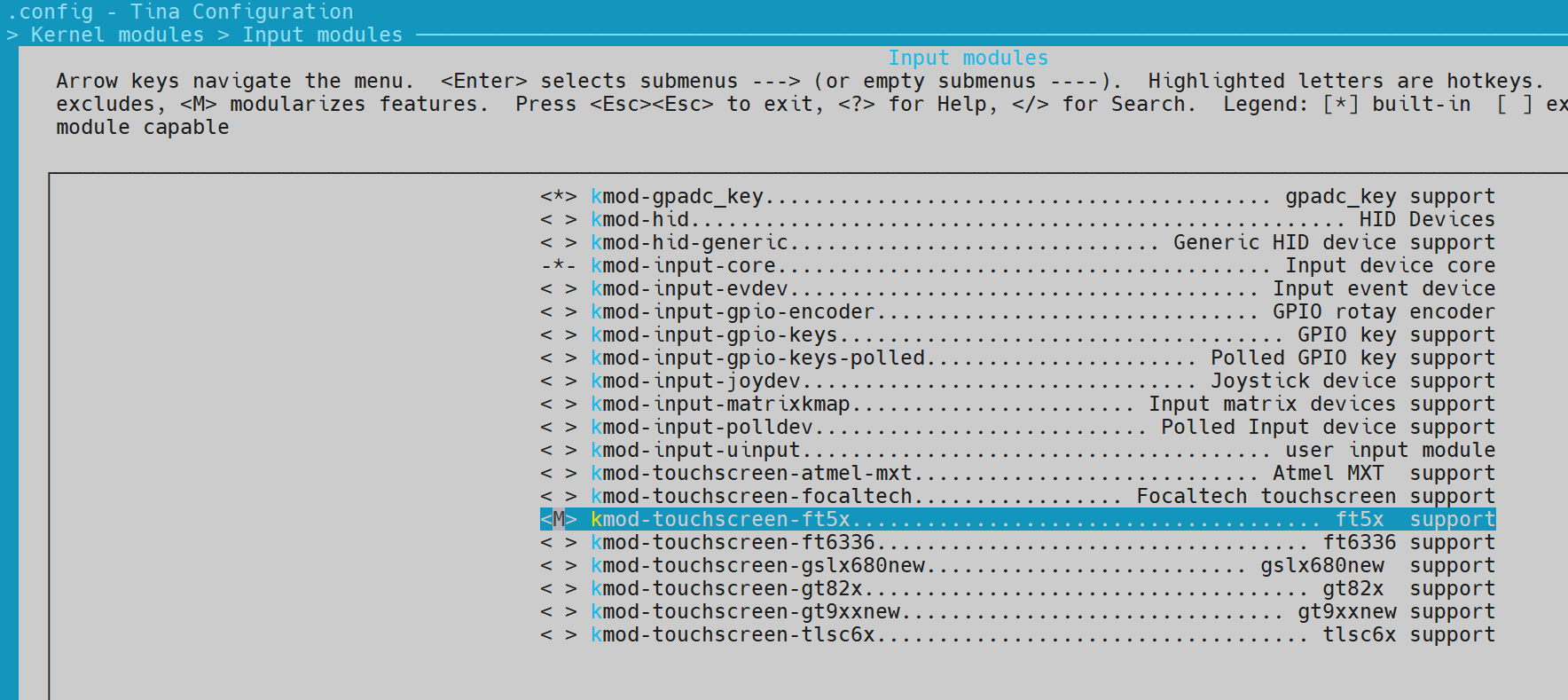

由于我们之前适配过了RGB屏触摸驱动,所以需要进入内核中修改为我们使用的新驱动,进入如下目录中,按下空格键取消勾选之前的触摸驱动gt9xxnew touchscreen driver,输入Y选中我们使用的ft6336 touchscreen driver新驱动,并保存退出。

→ Device Drivers → Input device support → Touchscreens <*> ft6336 touchscreen driver7.3 修改驱动程序

修改ft6336.c触摸驱动程序,这里只展示修改的部分,源文件可见4寸屏适配资源包中查看。

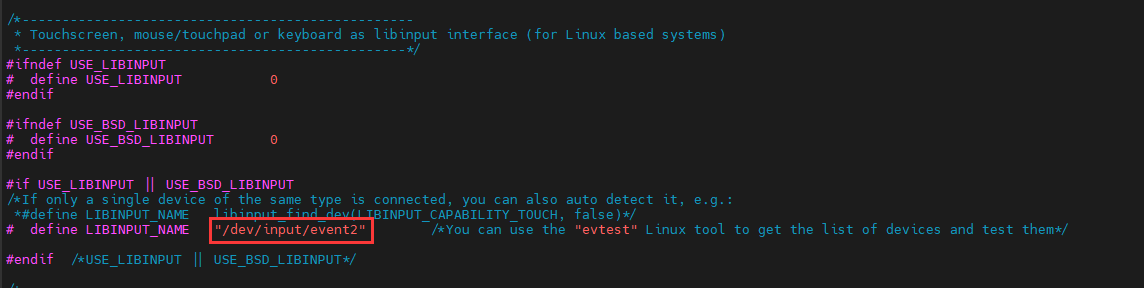

input_report_abs(ts->input_dev, ABS_MT_POSITION_X, -(event->au16_x[i]-480)); input_report_abs(ts->input_dev, ABS_MT_POSITION_Y, -(event->au16_y[i]-800));7.4 LVGL绑定新触摸节点

由于Tina使用的默认绑定的触摸节点为/dev/input/event0,我们需要修改lvgl驱动头文件中绑定的节点为我们触摸驱动上报数据的节点,我们触摸驱动上报的节点为event2,所以需要进入

tina-v853-open/platform/thirdparty/gui/lvgl-8/lv_examples/src目录下修改lv_drv_conf.h头文件,如下所示book@100ask:~/workspaces/tina-v853-open$ cd platform/thirdparty/gui/lvgl-8/lv_examples/src/ book@100ask:~/workspaces/tina-v853-open/platform/thirdparty/gui/lvgl-8/lv_examples/src$ vi lv_drv_conf.h找到触摸节点中的

LIBINPUT_NAME,将原来的/dev/input/event0修改/dev/input/event2,如下图红框内所示。

注意:我们这里修改的是头文件,可能之前编译生成过了之后再重新编译时可能不会再编译头文件,导致修改的节点不会生效,可以手动删除out目录中的

lv_examples示例程序或者直接删除out目录重新编译即可。具体原因可以观看韦东山老师的《ARM架构与编程》课程中的gcc编译过程详解。访问链接为:ARM架构与编程8.编译系统并打包生成镜像

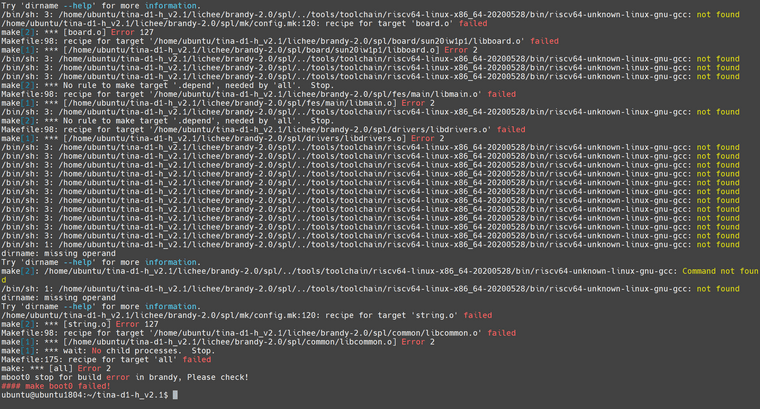

返回Tina根目录下,输入

make,编译系统book@100ask:~/workspaces/tina-v853-open$ make -j4 ... sun8iw21p1 compile Kernel successful INFO: ---------------------------------------- INFO: build Tina OK. INFO: ----------------------------------------打包生成镜像,输入

packbook@100ask:~/workspaces/tina-v853-open$ pack ... Dragon execute image.cfg SUCCESS ! ----------image is at---------- 33M /home/book/workspaces/tina-v853-open/out/v853/100ask/openwrt/v853_linux_100ask_uart0.img pack finish9.烧录并测试

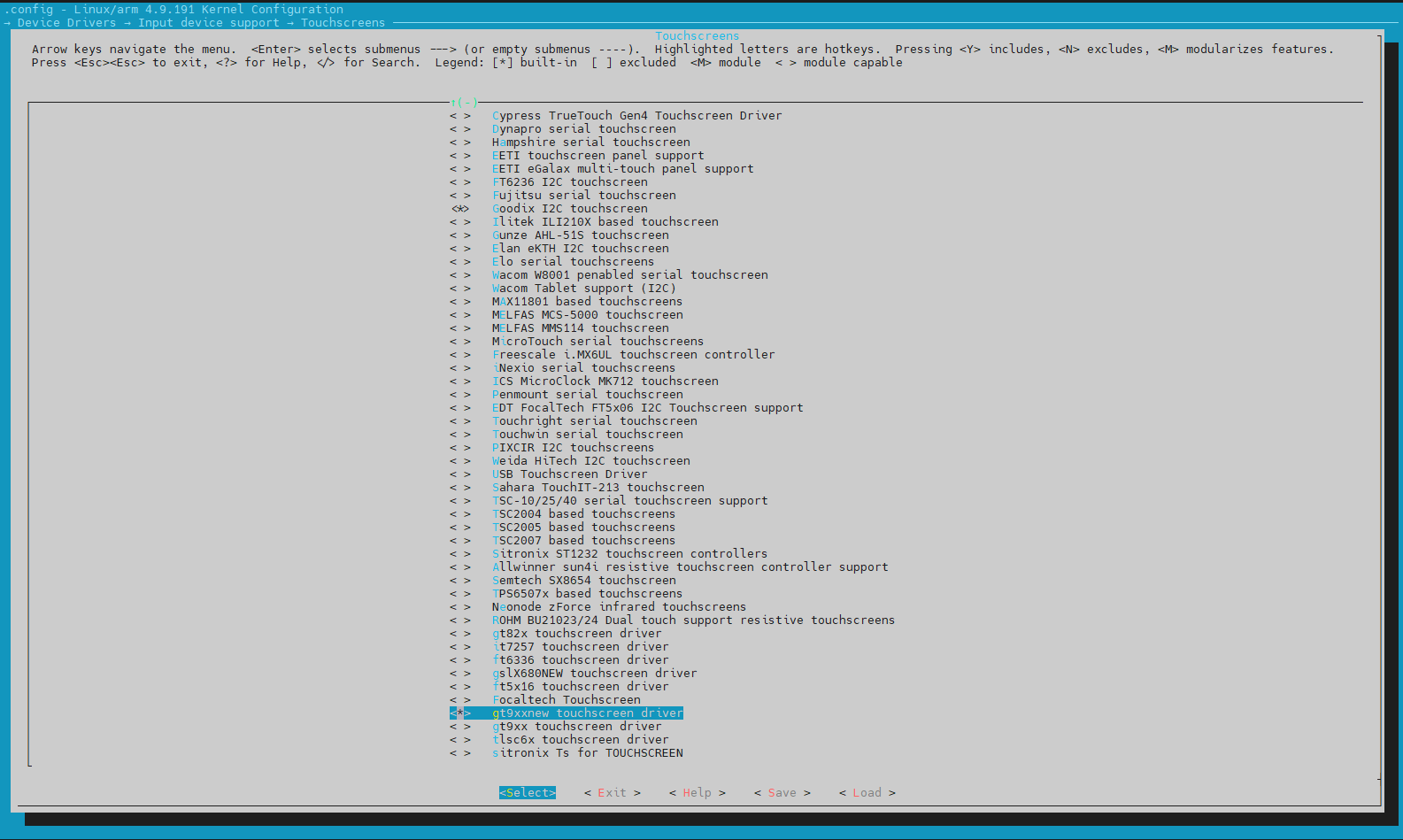

打包完成后,将新生成的镜像拷贝到Windows主机电脑上,使用全志PhoenixSuit烧写工具,烧写到开发板上。具体可以参考:https://forums.100ask.net/t/topic/2882。烧写完成后需要断电,才能连接MIPI屏的排线到MIPI屏接口,注意排线的线序是否一致。

接完排线后,重新接入电源,和2条Type-C数据线,再将开关拨向电源接口处上电启动,启动时会出现Tina Linux小企鹅logo,进入系统后,可以查看触摸节点

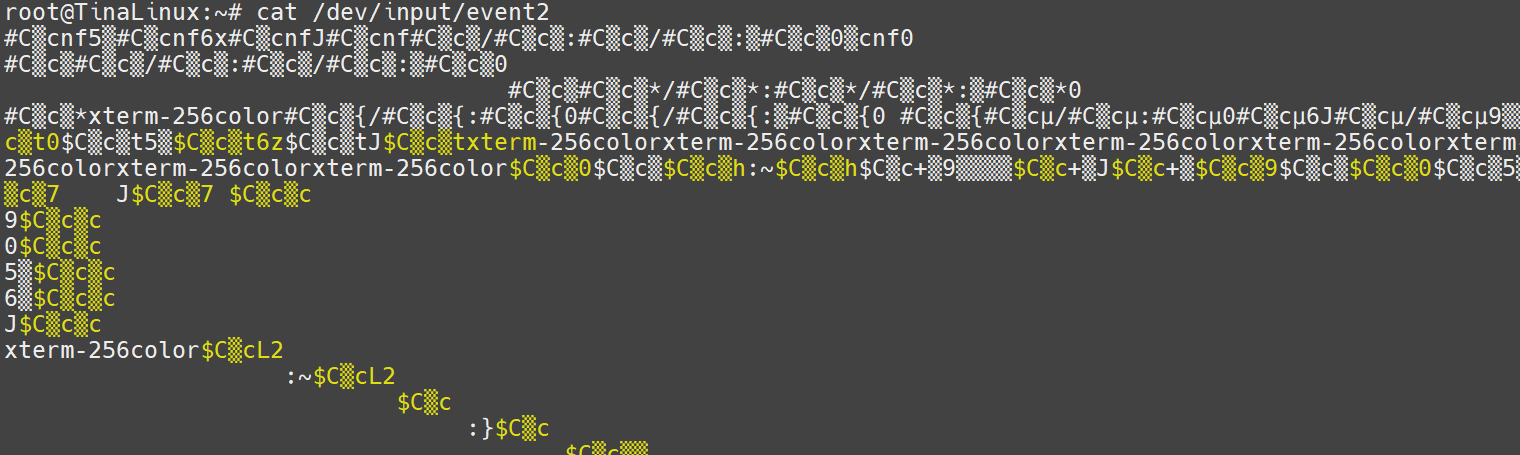

root@TinaLinux:/# ls /dev/input/ event0 event1 event2 我们使用的event2,如果你不确定您的触摸驱动程序使用的是哪个,可以通过

cat /dev/input/event*,其中*表示要查看的是哪一个触摸节点,例如我使用的是event2,则需要输入cat /dev/input/event2,此时触摸屏幕会有上报信息。 使用LVGL DEMO示例,输入

lv_examples 0启动lvgl示例,可以通过点击屏幕上的UI交互按钮测试触摸是否生效。root@TinaLinux:/# lv_examples 0 wh=480x800, vwh=480x1600, bpp=32, rotated=0 Turn on double buffering. Turn on 2d hardware acceleration. Turn on 2d hardware acceleration rotate. -

100ASK_V853-PRO开发板支持七寸RGB屏发布在 V Series

100ASK_V853-PRO开发板支持七寸RGB屏

0.前言

在前面我们已经学习了关于100ASK_V853-PRO编译和烧写,接下来就是在Tina SDK下去适配七寸RGB屏,购买链接为:https://item.taobao.com/item.htm?spm=a1z10.5-c-s.w4002-18944745104.11.669f1b7fE1ptyQ&id=611156659477

LCD_调试指南:https://tina.100ask.net/SdkModule/Linux_LCD_DevelopmentGuide-01/

Display_开发指南:https://tina.100ask.net/SdkModule/Linux_Display_DevelopmentGuide-01/

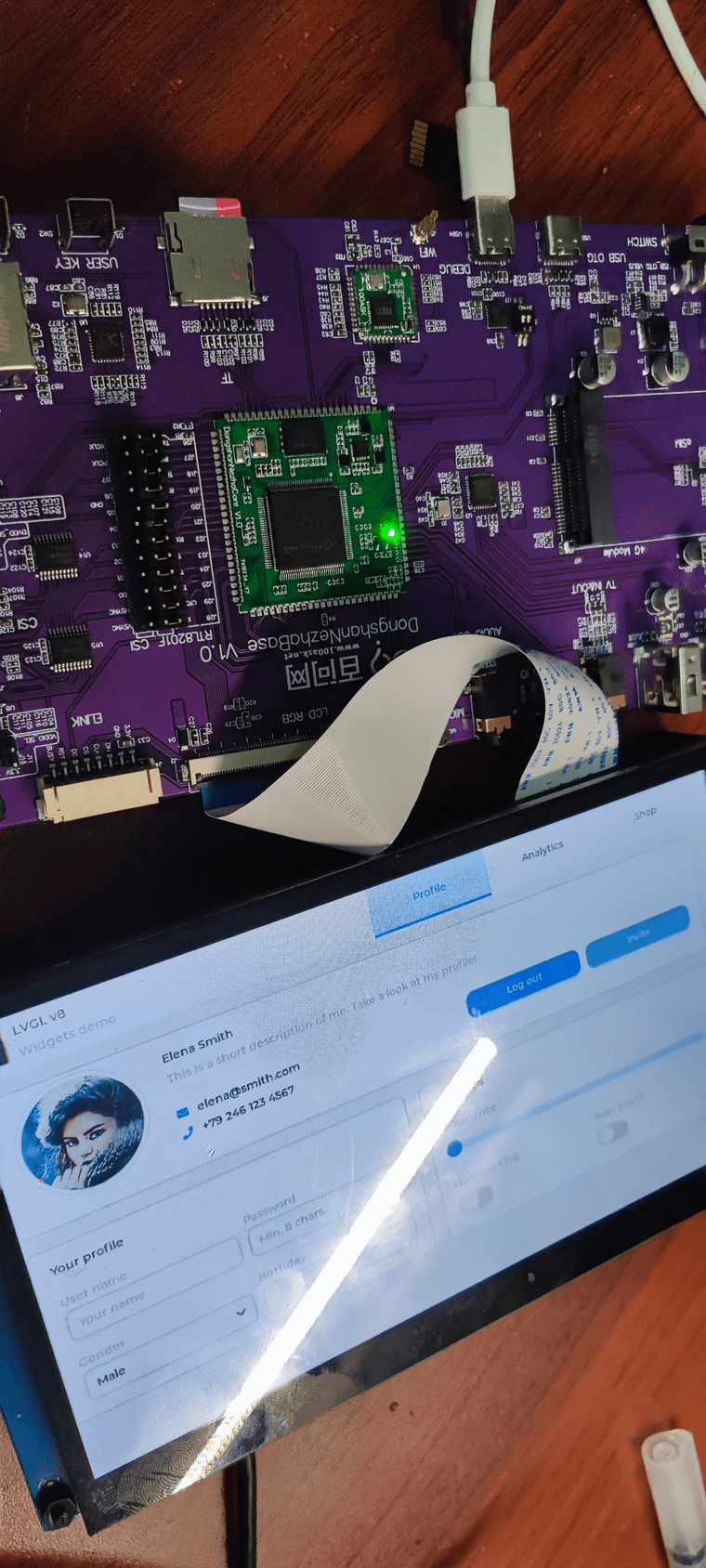

如果已经使用我们的增加的补丁文件,默认启动有Tina Linux的logo,同时还支持了lvgl示例和触摸。可在开发板的串口终端上输入

lv_examples,可以发现我们提供有5个lvgl示例。输入lv_examples 0,可运行第一个lvgl示例。root@TinaLinux:/# lv_examples lv_examples 0, is lv_demo_widgets lv_examples 1, is lv_demo_music lv_examples 2, is lv_demo_benchmark lv_examples 3, is lv_demo_keypad_encoder lv_examples 4, is lv_demo_stress root@TinaLinux:/# lv_examples 0 wh=1024x600, vwh=1024x1200, bpp=32, rotated=0 Turn on double buffering. Turn on 2d hardware acceleration. Turn on 2d hardware acceleration rotate.运行完成后可在七寸RGB屏上显示LVGL V8的示例界面,同时支持触摸控制示例。

1.适配七寸RGB屏的流程

由于Tina SDK中默认已经支持RGB屏驱动,所以适配七寸RGB屏只注意以下几个点:

1.修改设备树

2.配置内核

3.修改Uboot配置

内核设备树的位置:tina-v853-open/device/config/chips/v853/configs/100ask/board.dts

uboot设备树的位置:tina-v853-open/device/config/chips/v853/configs/100ask/board.dts

修改内核配置:在tina的根目录下执行

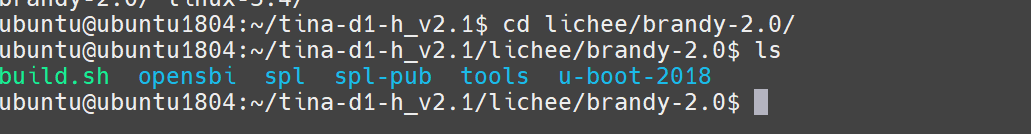

make kernel_menuconfig修改uboot配置:进入uboot的根目录tina-v853-open/brandy/brandy-2.0/u-boot-2018下执行

make menuconfig内核驱动位置:tina-v853-open/kernel/linux-4.9/drivers/video/fbdev/sunxi/disp2/disp/lcd/default_panel.c

uboot驱动位置:

tina-v853-open/brandy/brandy-2.0/u-boot-2018/drivers/video/sunxi/disp2/disp/lcd/default_panel.c

2.检查修改设备树

在Tina根目录下,输入

cd device/config/chips/v853/configs/100ask/book@100ask:~/workspaces/tina-v853-open$ cd device/config/chips/v853/configs/100ask/ book@100ask:~/workspaces/tina-v853-open/device/config/chips/v853/configs/100ask$ vi board.dts2.1 修改内核设备树

修改 board.dts中的lcd0为:

&lcd0 { /* part 1 */ lcd_used = <1>; lcd_driver_name = "default_lcd"; lcd_backlight = <100>; /* part 2 */ lcd_if = <0>; lcd_hv_if = <0>; /* part 3 */ lcd_x = <1024>; lcd_y = <600>; lcd_width = <154>; lcd_height = <85>; lcd_dclk_freq = <51>; lcd_hbp = <140>; lcd_ht = <1344>; lcd_hspw = <20>; lcd_vbp = <20>; lcd_vt = <635>; lcd_vspw = <3>; lcd_pwm_used = <1>; lcd_pwm_ch = <9>; lcd_pwm_freq = <500>; lcd_pwm_pol = <1>; /* part 5 */ lcd_frm = <1>; lcd_io_phase = <0x0000>; lcd_gamma_en = <0>; lcd_cmap_en = <0>; lcd_hv_clk_phase = <0>; lcd_hv_sync_polarity= <0>; /* part 6 */ lcd_power = "vcc-lcd"; lcd_pin_power = "vcc-pd"; pinctrl-0 = <&rgb18_pins_a>; pinctrl-1 = <&rgb18_pins_b>; };在&pio节点下增加rgb18_pins_a和rgb18_pins_b子节点,增加引脚复用功能

rgb18_pins_a: rgb18@0 { allwinner,pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", \ "PD6", "PD7", "PD8", "PD9", "PD10", "PD11", \ "PD12", "PD13", "PD14", "PD15", "PD16", "PD17", \ "PD18", "PD19", "PD20", "PD21"; allwinner,pname = "lcdd2", "lcdd3", "lcdd4", "lcdd5", "lcdd6", "lcdd7", \ "lcdd10", "lcdd11", "lcdd12", "lcdd13", "lcdd14", "lcdd15", \ "lcdd18", "lcdd19", "lcdd20", "lcdd21", "lcdd22", "lcdd23", \ "lcdpclk", "lcdde", "lcdhsync", "lcdvsync"; allwinner,function = "lcd"; allwinner,muxsel = <2>; allwinner,drive = <3>; allwinner,pull = <0>; }; rgb18_pins_b: rgb18@1 { allwinner,pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", \ "PD6", "PD7", "PD8", "PD9", "PD10", "PD11", \ "PD12", "PD13", "PD14", "PD15", "PD16", "PD17", \ "PD18", "PD19", "PD20", "PD21"; allwinner,pname = "lcdd2", "lcdd3", "lcdd4", "lcdd5", "lcdd6", "lcdd7", \ "lcdd10", "lcdd11", "lcdd12", "lcdd13", "lcdd14", "lcdd15", \ "lcdd18", "lcdd19", "lcdd20", "lcdd21", "lcdd22", "lcdd23", \ "lcdpclk", "lcdde", "lcdhsync", "lcdvsync"; allwinner,function = "io_disabled"; allwinner,muxsel = <0xf>; allwinner,drive = <3>; allwinner,pull = <0>; };2.2 修改uboot设备树

在同一目录下修改uboot设备树

book@100ask:~/workspaces/tina-v853-open/device/config/chips/v853/configs/100ask$ vi uboot-board.dts&lcd0 { lcd_used = <1>; lcd_driver_name = "default_lcd"; lcd_backlight = <100>; lcd_if = <0>; lcd_hv_if = <0>; lcd_x = <1024>; lcd_y = <600>; lcd_width = <154>; lcd_height = <85>; lcd_dclk_freq = <51>; lcd_hbp = <140>; lcd_ht = <1344>; lcd_hspw = <20>; lcd_vbp = <20>; lcd_vt = <635>; lcd_vspw = <3>; lcd_pwm_used = <1>; lcd_pwm_ch = <9>; lcd_pwm_freq = <500>; lcd_pwm_pol = <1>; lcd_frm = <1>; lcd_io_phase = <0x0000>; lcd_gamma_en = <0>; lcd_cmap_en = <0>; lcd_hv_clk_phase = <0>; lcd_hv_sync_polarity= <0>; lcd_power = "vcc-lcd"; lcd_pin_power = "vcc-pd"; pinctrl-0 = <&rgb18_pins_a>; pinctrl-1 = <&rgb18_pins_b>; };在&pio节点下增加rgb18_pins_a和rgb18_pins_b子节点,增加引脚复用功能

rgb18_pins_a: rgb18@0 { allwinner,pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", \ "PD6", "PD7", "PD8", "PD9", "PD10", "PD11", \ "PD12", "PD13", "PD14", "PD15", "PD16", "PD17", \ "PD18", "PD19", "PD20", "PD21"; allwinner,pname = "lcdd2", "lcdd3", "lcdd4", "lcdd5", "lcdd6", "lcdd7", \ "lcdd10", "lcdd11", "lcdd12", "lcdd13", "lcdd14", "lcdd15", \ "lcdd18", "lcdd19", "lcdd20", "lcdd21", "lcdd22", "lcdd23", \ "lcdpclk", "lcdde", "lcdhsync", "lcdvsync"; allwinner,function = "lcd"; allwinner,muxsel = <2>; allwinner,drive = <3>; allwinner,pull = <0>; }; rgb18_pins_b: rgb18@1 { allwinner,pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", \ "PD6", "PD7", "PD8", "PD9", "PD10", "PD11", \ "PD12", "PD13", "PD14", "PD15", "PD16", "PD17", \ "PD18", "PD19", "PD20", "PD21"; allwinner,pname = "lcdd2", "lcdd3", "lcdd4", "lcdd5", "lcdd6", "lcdd7", \ "lcdd10", "lcdd11", "lcdd12", "lcdd13", "lcdd14", "lcdd15", \ "lcdd18", "lcdd19", "lcdd20", "lcdd21", "lcdd22", "lcdd23", \ "lcdpclk", "lcdde", "lcdhsync", "lcdvsync"; allwinner,function = "io_disabled"; allwinner,muxsel = <0xf>; allwinner,drive = <3>; allwinner,pull = <0>; };3.检查修改内核配置和uboot配置

3.1 修改内核配置

在Tina的根目录下输入

make kernel_menuconfigbook@100ask:~/workspaces/tina-v853-open$ make kernel_menuconfig通过方向键,选择并进入如下目录,输入Y开启DISP Driver Support

→ Device Drivers → Graphics support → Frame buffer Devices → Video support for sunxi <*> DISP Driver Support(sunxi-disp2)如下图所示:

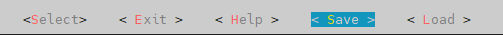

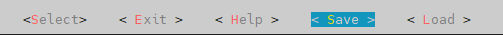

选中后,通过方向键选择Save,按下回车。

按下后会提示您是否确认保存备份,选择OK

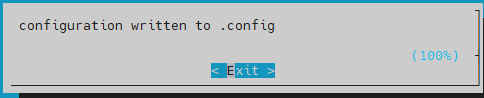

此时我们所修改的配置将保存在tina-v853-open/kernel/linux-4.9/.config文件中,继续按下回车退出。

保存完成后,通过方向键选择Exit,一直选择Exit,直到退出内核配置界面

3.2 修改uboot配置

想要修改uboot,需要进入tina-v853-open/brandy/brandy-2.0/u-boot-2018目录下,执行

make menuconfigbook@100ask:~/workspaces/tina-v853-open$ cd brandy/brandy-2.0/u-boot-2018/ book@100ask:~/workspaces/tina-v853-open/brandy/brandy-2.0/u-boot-2018$ make menuconfig通过方向键进入

→ Device Drivers → Graphics support [*] DISP Driver Support(sunxi-disp2) --->如下图所示:

选中后,通过方向键选择Save,按下回车。

按下后会提示您是否确认保存备份,选择OK

此时我们所修改的配置将保存在

tina-v853-open/brandy/brandy-2.0/u-boot-2018/.config文件中,继续按下回车退出。

保存完成后,通过方向键选择Exit,一直选择Exit,直到退出uboot配置界面

4.七寸RGB屏驱动程序

内核和uboot中的驱动程序都是同一套,可以复用的。由于我们选中了sunxi-disp2,都会默认去编译default_panel.c驱动程序。

内核驱动位置:tina-v853-open/kernel/linux-4.9/drivers/video/fbdev/sunxi/disp2/disp/lcd/default_panel.c

uboot驱动位置:

tina-v853-open/brandy/brandy-2.0/u-boot-2018/drivers/video/sunxi/disp2/disp/lcd/default_panel.c

/* * drivers/video/sunxi/disp2/disp/lcd/default_panel.c * * Copyright (c) 2007-2019 Allwinnertech Co., Ltd. * Author: zhengxiaobin <zhengxiaobin@allwinnertech.com> * * This software is licensed under the terms of the GNU General Public * License version 2, as published by the Free Software Foundation, and * may be copied, distributed, and modified under those terms. * * This program is distributed in the hope that it will be useful, * but WITHOUT ANY WARRANTY; without even the implied warranty of * MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the * GNU General Public License for more details. * */ #include "default_panel.h" static void LCD_power_on(u32 sel); static void LCD_power_off(u32 sel); static void LCD_bl_open(u32 sel); static void LCD_bl_close(u32 sel); static void LCD_panel_init(u32 sel); static void LCD_panel_exit(u32 sel); static void LCD_cfg_panel_info(panel_extend_para * info) { u32 i = 0, j=0; u32 items; u8 lcd_gamma_tbl[][2] = { //{input value, corrected value} {0, 0}, {15, 15}, {30, 30}, {45, 45}, {60, 60}, {75, 75}, {90, 90}, {105, 105}, {120, 120}, {135, 135}, {150, 150}, {165, 165}, {180, 180}, {195, 195}, {210, 210}, {225, 225}, {240, 240}, {255, 255}, }; u32 lcd_cmap_tbl[2][3][4] = { { {LCD_CMAP_G0,LCD_CMAP_B1,LCD_CMAP_G2,LCD_CMAP_B3}, {LCD_CMAP_B0,LCD_CMAP_R1,LCD_CMAP_B2,LCD_CMAP_R3}, {LCD_CMAP_R0,LCD_CMAP_G1,LCD_CMAP_R2,LCD_CMAP_G3}, }, { {LCD_CMAP_B3,LCD_CMAP_G2,LCD_CMAP_B1,LCD_CMAP_G0}, {LCD_CMAP_R3,LCD_CMAP_B2,LCD_CMAP_R1,LCD_CMAP_B0}, {LCD_CMAP_G3,LCD_CMAP_R2,LCD_CMAP_G1,LCD_CMAP_R0}, }, }; items = sizeof(lcd_gamma_tbl)/2; for (i=0; i<items-1; i++) { u32 num = lcd_gamma_tbl[i+1][0] - lcd_gamma_tbl[i][0]; for (j=0; j<num; j++) { u32 value = 0; value = lcd_gamma_tbl[i][1] + ((lcd_gamma_tbl[i+1][1] - lcd_gamma_tbl[i][1]) * j)/num; info->lcd_gamma_tbl[lcd_gamma_tbl[i][0] + j] = (value<<16) + (value<<8) + value; } } info->lcd_gamma_tbl[255] = (lcd_gamma_tbl[items-1][1]<<16) + (lcd_gamma_tbl[items-1][1]<<8) + lcd_gamma_tbl[items-1][1]; memcpy(info->lcd_cmap_tbl, lcd_cmap_tbl, sizeof(lcd_cmap_tbl)); } static s32 LCD_open_flow(u32 sel) { LCD_OPEN_FUNC(sel, LCD_power_on, 30); //open lcd power, and delay 50ms LCD_OPEN_FUNC(sel, LCD_panel_init, 50); //open lcd power, than delay 200ms LCD_OPEN_FUNC(sel, sunxi_lcd_tcon_enable, 100); //open lcd controller, and delay 100ms LCD_OPEN_FUNC(sel, LCD_bl_open, 0); //open lcd backlight, and delay 0ms return 0; } static s32 LCD_close_flow(u32 sel) { LCD_CLOSE_FUNC(sel, LCD_bl_close, 0); //close lcd backlight, and delay 0ms LCD_CLOSE_FUNC(sel, sunxi_lcd_tcon_disable, 0); //close lcd controller, and delay 0ms LCD_CLOSE_FUNC(sel, LCD_panel_exit, 200); //open lcd power, than delay 200ms LCD_CLOSE_FUNC(sel, LCD_power_off, 500); //close lcd power, and delay 500ms return 0; } static void LCD_power_on(u32 sel) { sunxi_lcd_power_enable(sel, 0);//config lcd_power pin to open lcd power0 sunxi_lcd_pin_cfg(sel, 1); } static void LCD_power_off(u32 sel) { sunxi_lcd_pin_cfg(sel, 0); sunxi_lcd_power_disable(sel, 0);//config lcd_power pin to close lcd power0 } static void LCD_bl_open(u32 sel) { sunxi_lcd_pwm_enable(sel); sunxi_lcd_backlight_enable(sel);//config lcd_bl_en pin to open lcd backlight } static void LCD_bl_close(u32 sel) { sunxi_lcd_backlight_disable(sel);//config lcd_bl_en pin to close lcd backlight sunxi_lcd_pwm_disable(sel); } static void LCD_panel_init(u32 sel) { return; } static void LCD_panel_exit(u32 sel) { return ; } //sel: 0:lcd0; 1:lcd1 static s32 LCD_user_defined_func(u32 sel, u32 para1, u32 para2, u32 para3) { return 0; } __lcd_panel_t default_panel = { /* panel driver name, must mach the name of lcd_drv_name in sys_config.fex */ .name = "default_lcd", .func = { .cfg_panel_info = LCD_cfg_panel_info, .cfg_open_flow = LCD_open_flow, .cfg_close_flow = LCD_close_flow, .lcd_user_defined_func = LCD_user_defined_func, }, };5.开启触摸功能

5.1修改设备树

修改设备树中的twi2节点下增加ctp触摸子节点

&twi2 { ctp@14 { compatible = "allwinner,gsl3680"; device_type = "ctp"; reg = <0x14>; status = "okay"; ctp_name = "gt9xxnew_ts"; ctp_twi_id = <0x2>; ctp_twi_addr = <0x14>; ctp_screen_max_x = <0x400>; ctp_screen_max_y = <0x258>; ctp_revert_x_flag = <0x0>; ctp_revert_y_flag = <0x0>; ctp_exchange_x_y_flag = <0x0>; ctp_int_port = <&pio PH 7 6 1 3 0xffffffff>; ctp_wakeup = <&pio PH 8 1 1 3 0xffffffff>; //ctp-supply = <®_aldo2>; //ctp_power_ldo = <®_dldo1>; //ctp_power_ldo_vol = <3300>; }; };并在lcd0节点后面使能twi2节点和引脚复用功能。

&twi2 { clock-frequency = <400000>; pinctrl-0 = <&twi2_pins_a>; pinctrl-1 = <&twi2_pins_b>; pinctrl-names = "default", "sleep"; /* For stability and backwards compatibility, we recommend setting ‘twi_drv_used’ to 0 */ twi_drv_used = <0>; twi-supply = <®_dcdc1>; twi_pkt_interval = <0>; //status = "disabled"; status = "okay"; };5.2 修改内核配置

在Tina的根目录下执行make kernel_menuconfig

book@100ask:~/workspaces/tina-v853-open$ make kernel_menuconfig进入下面的目录输入Y选中gt9xxnew touchscreen driver触摸驱动

→ Device Drivers → Input device support → Touchscreens <*> gt9xxnew touchscreen driver如下图所示

保存并退出内核配置界面6.打开lvgl示例程序

在Tina的根目录下,输入

make menuconfigbook@100ask:~/workspaces/tina-v853-open$ make menuconfig进入如下目录,并输入Y选中lv_examples

> Gui > Littlevgl <*> lv_examples................................. lvgl examples use lvgl-8.1.0选中后保存并退出配置界面。

7.编译并打包生成镜像

由于我们第一次已经完整编译了系统,现在修改后编译系统的时间就不会特别长,具体时间取决于CPU的性能,在Tina的根目录下执行

make -jN,其中N为线程数,增加线程数提高编译速度。book@100ask:~/workspaces/tina-v853-open$ make -j4等待编译完成后,输入pack,打包生成镜像

book@100ask:~/workspaces/tina-v853-open$ pack打包生成镜像后可以在tina-v853-open/out/v853/100ask/openwrt/目录下找到新的镜像文件

v853_linux_100ask_uart0.img,将该文件拷贝到windows电脑下备用。

8.烧录新镜像启动开发板

使用全志PhoenixSuit烧写工具进行新镜像的烧写,具体方法可以参见《100ASK_V853-PRO 环境配置及编译烧写》。

注意:需要在上电前连接七寸RGB屏,同时连接排线时需要注意排线的线序是否正确。

连接好七寸屏,再连接电源线和两条Type-C数据线,将开关拨向电源接口的方向即可上电启动开发板,在烧写新镜像完成后通过串口工具打开开发板的串口终端,进入Tina Linux的控制台界面,输入lv_examples 0,即可在七寸RGB屏上显示出LVGL的DEMO程序。root@TinaLinux:/# lv_examples 0 wh=1024x600, vwh=1024x1200, bpp=32, rotated=0 Turn on double buffering. Turn on 2d hardware acceleration. Turn on 2d hardware acceleration rotate. -

100ASK-V853-PRO开发板支持WIFI和有线网卡发布在 V Series

100ASK-V853-PRO开发板支持WIFI和有线网卡

0.前言

通过上一章节,我们已经成功下载Tina SDK包,完成编译并烧写Tina Linux系统,接下来展示100ASK-V853-PRO开发部如何通过WIFI和有线网卡进行上网。

1.使用WIFI实现上网

100ASK-V853-PRO全功能底板上板载有全志XR829,烧录的开发板系统已经进行了适配,可以直接使用,在开发板上输入ifconfig,可以显示已经使能的网络设备。

root@TinaLinux:/# ifconfig lo Link encap:Local Loopback inet addr:127.0.0.1 Mask:255.0.0.0 inet6 addr: ::1/128 Scope:Host UP LOOPBACK RUNNING MTU:65536 Metric:1 RX packets:0 errors:0 dropped:0 overruns:0 frame:0 TX packets:0 errors:0 dropped:0 overruns:0 carrier:0 collisions:0 txqueuelen:1 RX bytes:0 (0.0 B) TX bytes:0 (0.0 B) wlan0 Link encap:Ethernet HWaddr 84:B0:AC:67:95:EE UP BROADCAST MULTICAST MTU:1500 Metric:1 RX packets:0 errors:0 dropped:0 overruns:0 frame:0 TX packets:0 errors:0 dropped:0 overruns:0 carrier:0 collisions:0 txqueuelen:1000 RX bytes:0 (0.0 B) TX bytes:0 (0.0 B)可以看到wlan0默认已经使能了,如果没有使能可以输入

ifconfig -a,查看所有网络接口是否存在wlan0设备,如果存在wlan0,则可输入ifconfig wlan0 up使能wlan0。root@TinaLinux:/# ifconfig -a eth0 Link encap:Ethernet HWaddr 92:A8:E0:01:3D:F9 BROADCAST MULTICAST MTU:1500 Metric:1 RX packets:0 errors:0 dropped:0 overruns:0 frame:0 TX packets:0 errors:0 dropped:0 overruns:0 carrier:0 collisions:0 txqueuelen:1000 RX bytes:0 (0.0 B) TX bytes:0 (0.0 B) Interrupt:59 lo Link encap:Local Loopback inet addr:127.0.0.1 Mask:255.0.0.0 inet6 addr: ::1/128 Scope:Host UP LOOPBACK RUNNING MTU:65536 Metric:1 RX packets:0 errors:0 dropped:0 overruns:0 frame:0 TX packets:0 errors:0 dropped:0 overruns:0 carrier:0 collisions:0 txqueuelen:1 RX bytes:0 (0.0 B) TX bytes:0 (0.0 B) p2p0 Link encap:Ethernet HWaddr 84:B0:AC:67:95:EF BROADCAST MULTICAST MTU:1500 Metric:1 RX packets:0 errors:0 dropped:0 overruns:0 frame:0 TX packets:0 errors:0 dropped:0 overruns:0 carrier:0 collisions:0 txqueuelen:1000 RX bytes:0 (0.0 B) TX bytes:0 (0.0 B) wlan0 Link encap:Ethernet HWaddr 84:B0:AC:67:95:EE UP BROADCAST MULTICAST MTU:1500 Metric:1 RX packets:0 errors:0 dropped:0 overruns:0 frame:0 TX packets:0 errors:0 dropped:0 overruns:0 carrier:0 collisions:0 txqueuelen:1000 RX bytes:0 (0.0 B) TX bytes:0 (0.0 B) root@TinaLinux:/# ifconfig wlan0 up使能完成后,由于系统内置wifimanager-v2.0,可以使您快速实现配网,输入

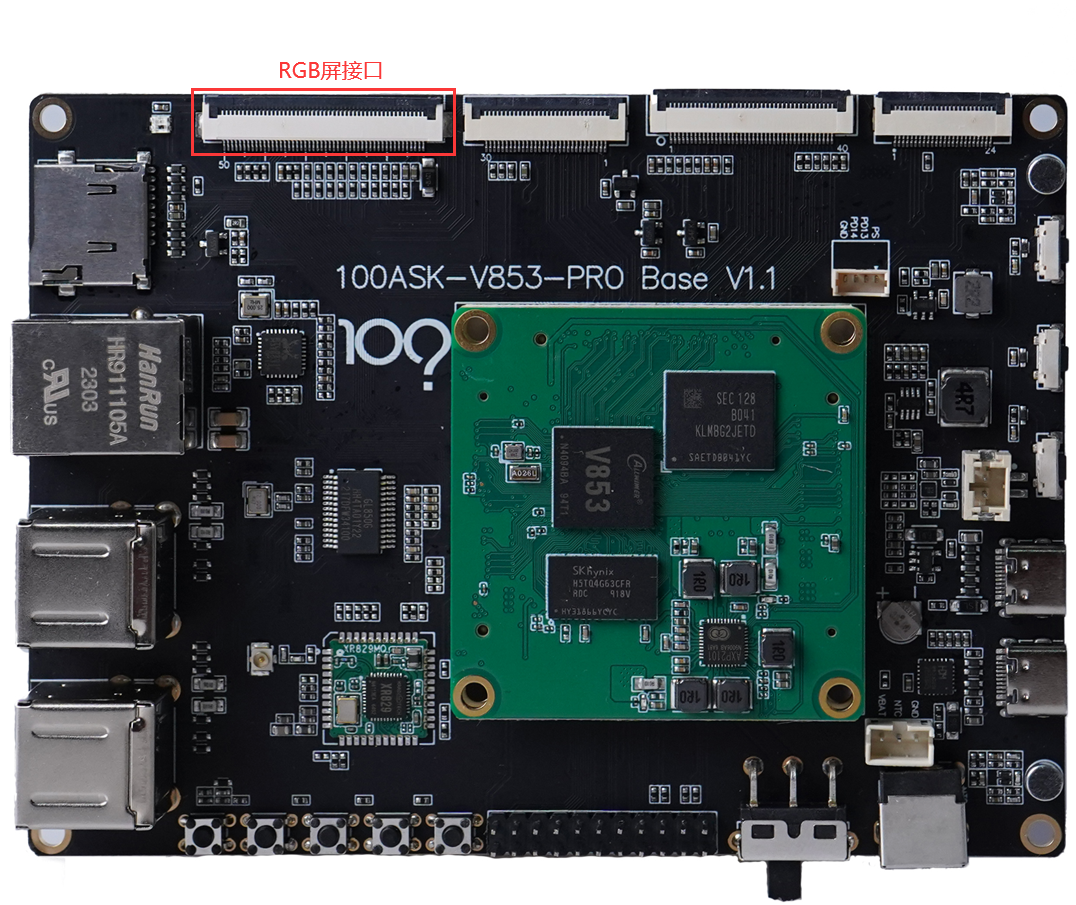

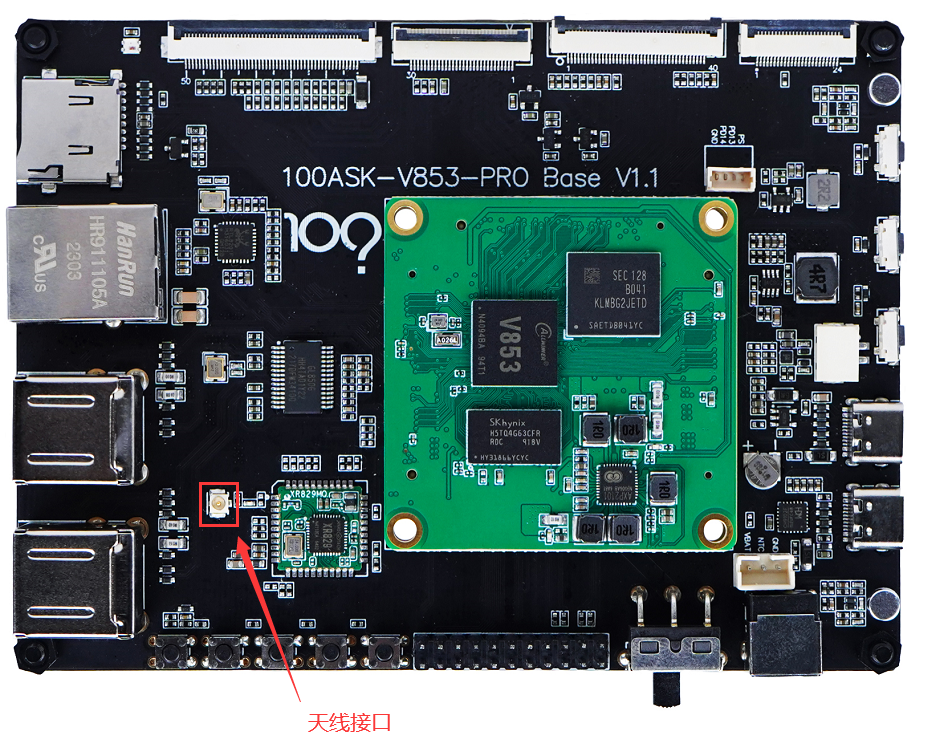

wifi -h,可以获得参数帮助root@TinaLinux:/# wifi -h ======================================================================= ************************* sta mode Options ************************** ======================================================================= wifi -o sta : open sta mode wifi -f : close sta mode wifi -s : scan wifi wifi -c ssid [passwd] : connect to an encrypted or non-encrypted ap wifi -d : disconnect from ap wifi -a [enable/disable] : Auto reconnect wifi -l [all] : list connected or saved ap information wifi -r [ssid/all] : remove a specified network or all networks wifi -p [softap/ble/xconfig/soundwave] : softap/ble/xconfig/soundwave distribution network ======================================================================= ************************* ap mode Options *************************** ======================================================================= wifi -o ap [ssid] [passwd] : open ap mode : if ssid and passwd is not set, start the default configuration: (allwinner-ap Aa123456) : if only set ssid, start the ap without passwd wifi -l : list current ap mode information wifi -f : close ap mode ======================================================================= *********************** monitor mode Options ************************ ======================================================================= wifi -o monitor : open monitor mode wifi -f : close monitor mode ======================================================================= *************************** other Options *************************** ======================================================================= wifi -D [error/warn/info/debug/dump/exce] : set debug level wifi -g : get system mac addr wifi -m [macaddr] : set system mac addr wifi -h : print help =======================================================================接下来可以进行扫描wifi,注意扫描前需要检查天线是否安装好,安装位置如下图所示。

检查安装完成后,在开发板的串口终端输入

wifi -sroot@TinaLinux:/# wifi -s root@TinaLinux:/# 1970-01-01 04:00:42:003: WMG_DEBUG [wifi_daemon.c:cmd_handle_thread:702]: get cmd: s 1970-01-01 04:00:42:003: WMG_DEBUG [wifi_daemon.c:cmd_handle_s:196]: cmd handle s: 1970-01-01 04:00:42:004: WMG_DEBUG [src/wmg_sta.c:sta_mode_ctl:463]: =====sta_mode_ctl cmd: 8===== 1970-01-01 04:00:42:004: WMG_EXCESSIVE [src/os/linux/linux_wpa.c:command_to_supplicant:195]: do cmd SCAN 1970-01-01 04:00:42:004: WMG_EXCESSIVE [src/os/linux/linux_wpa.c:command_to_supplicant:203]: do cmd SCAN, reply: OK ... 1970-01-01 04:00:45:185: WMG_INFO [wifi_daemon.c:cmd_handle_s:220]: bss[00]: bssid=94:d9:b3:b7:c9:0a ssid=100ASK channel=7(freq=2442) rssi=-23 sec=WPA_PSK 1970-01-01 04:00:45:185: WMG_INFO [wifi_daemon.c:cmd_handle_s:220]: bss[01]: bssid=d0:76:e7:f8:93:d8 ssid=TP-LINK_93D8 channel=6(freq=2437) rssi=-70 sec=WPA_PSK 1970-01-01 04:00:45:185: WMG_INFO [wifi_daemon.c:cmd_handle_s:220]: bss[02]: bssid=7a:60:5b:29:22:ab ssid= channel=2(freq=2417) rssi=-70 sec=WPA2_PSK 1970-01-01 04:00:45:185: WMG_INFO [wifi_daemon.c:cmd_handle_s:220]: bss[03]: bssid=7a:60:5b:59:22:ab ssid= channel=2(freq=2417) rssi=-70 sec=WPA_PSK 1970-01-01 04:00:45:517: WMG_INFO [wifi_daemon.c:cmd_handle_s:222]: ===Wi-Fi scan successful, total 21 ap(buff size: 60) time 3180.000000 ms===扫描完成后会打印Wi-Fi scan successful和所用的时间time,可以看到输出信息中的ssid为扫描出来的WIFI名称,注意WIFI名称如果是含有中文字符可能会无法显示。

接下来可以进行连接WIFI进行上网,输入

wifi -c ssid [passwd],其中ssid为WIFI名,passwd为密码假设我现在连接的WIFI名称为100ASK,密码为12345678,则需要输入

wifi -c 100ASK 12345678root@TinaLinux:/# wifi -c 100ASK 12345678 root@TinaLinux:/# 1970-01-01 04:16:49:482: WMG_DEBUG [wifi_daemon.c:cmd_handle_thread:702]: get cmd: c 100ASK 12345678 1970-01-01 04:16:49:482: WMG_DEBUG [wifi_daemon.c:cmd_handle_c:232]: cmd handle c: 100ASK 12345678 1970-01-01 04:16:49:482: WMG_INFO [wifi_daemon.c:cmd_handle_c:256]: connect to sta(100ASK) with pask(12345678) ... 1970-01-01 04:16:51:670: WMG_EXCESSIVE [src/os/linux/event.c:evt_read:128]: Excessive: read event 14 1970-01-01 04:16:51:670: WMG_DUMP [src/os/linux/linux_wpa.c:linux_supplicant_connect_to_ap:1531]: receive wpas event 'CONNECTED' 1970-01-01 04:16:51:671: WMG_EXCESSIVE [src/os/linux/linux_wpa.c:command_to_supplicant:195]: do cmd SAVE_CONFIG 1970-01-01 04:16:51:691: WMG_WARNG [src/os/linux/linux_wpa.c:linux_supplicant_connect_to_ap:1559]: failed to save config to wpa_supplicant.conf 1970-01-01 04:16:51:691: WMG_DEBUG [src/wifimg.c:__wifi_sta_connect:87]: wifi station connect success 1970-01-01 04:16:51:691: WMG_INFO [wifi_daemon.c:cmd_handle_c:265]: ===Wi-Fi connect successful,time 2210.000000 ms=== udhcpc: started, v1.33.2 udhcpc: sending discover udhcpc: sending select for 192.168.0.163 udhcpc: lease of 192.168.0.163 obtained, lease time 122 1970-01-01 04:16:53:689: WMG_DEBUG [src/os/linux/udhcpc.c:start_udhcpc:83]: vflag= 4 1970-01-01 04:16:53:689: WMG_INFO [src/os/linux/udhcpc.c:start_udhcpc:85]: get ip addr 192.168.0.163可以看到当我们输入完成后,开发板会自动连接到WIFI并会自动获取IP地址,此时我们可以执行ping www.100ask.net,测试wifi是否可以ping通百问网的官方网址,按下Crtl+C结束测试。

root@TinaLinux:/# ping www.100ask.net PING www.100ask.net (118.25.119.100): 56 data bytes 64 bytes from 118.25.119.100: seq=0 ttl=53 time=34.627 ms 64 bytes from 118.25.119.100: seq=1 ttl=53 time=34.894 ms 64 bytes from 118.25.119.100: seq=2 ttl=53 time=34.477 ms 64 bytes from 118.25.119.100: seq=3 ttl=53 time=36.828 ms ^C --- www.100ask.net ping statistics --- 4 packets transmitted, 4 packets received, 0% packet loss round-trip min/avg/max = 34.477/35.206/36.828 ms2.使用有线网卡实现上网

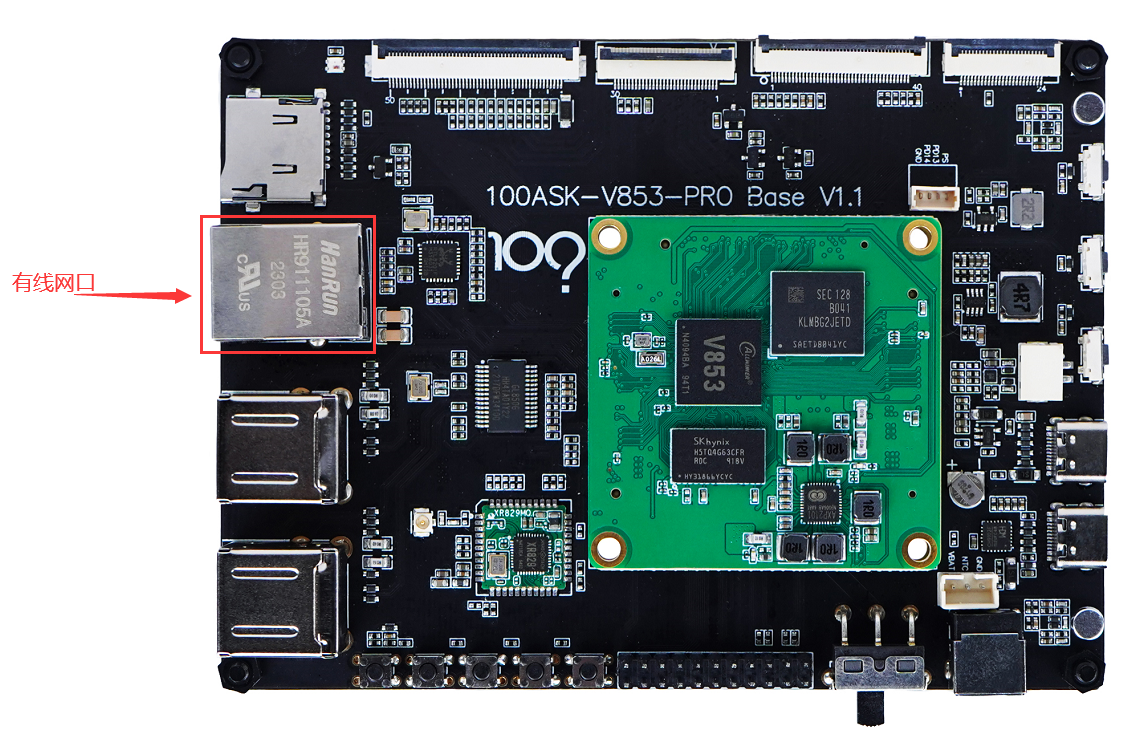

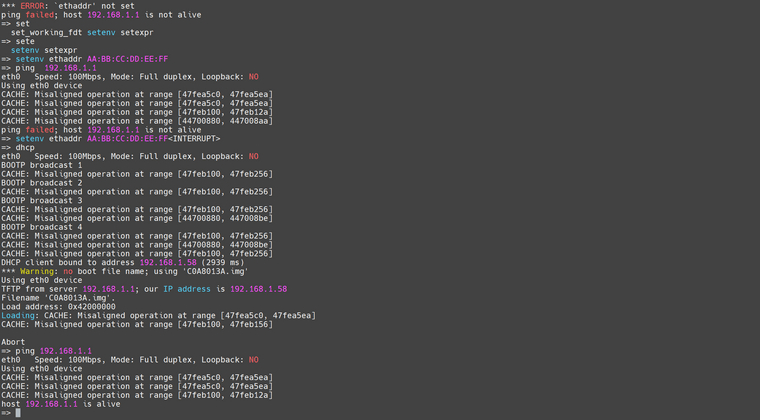

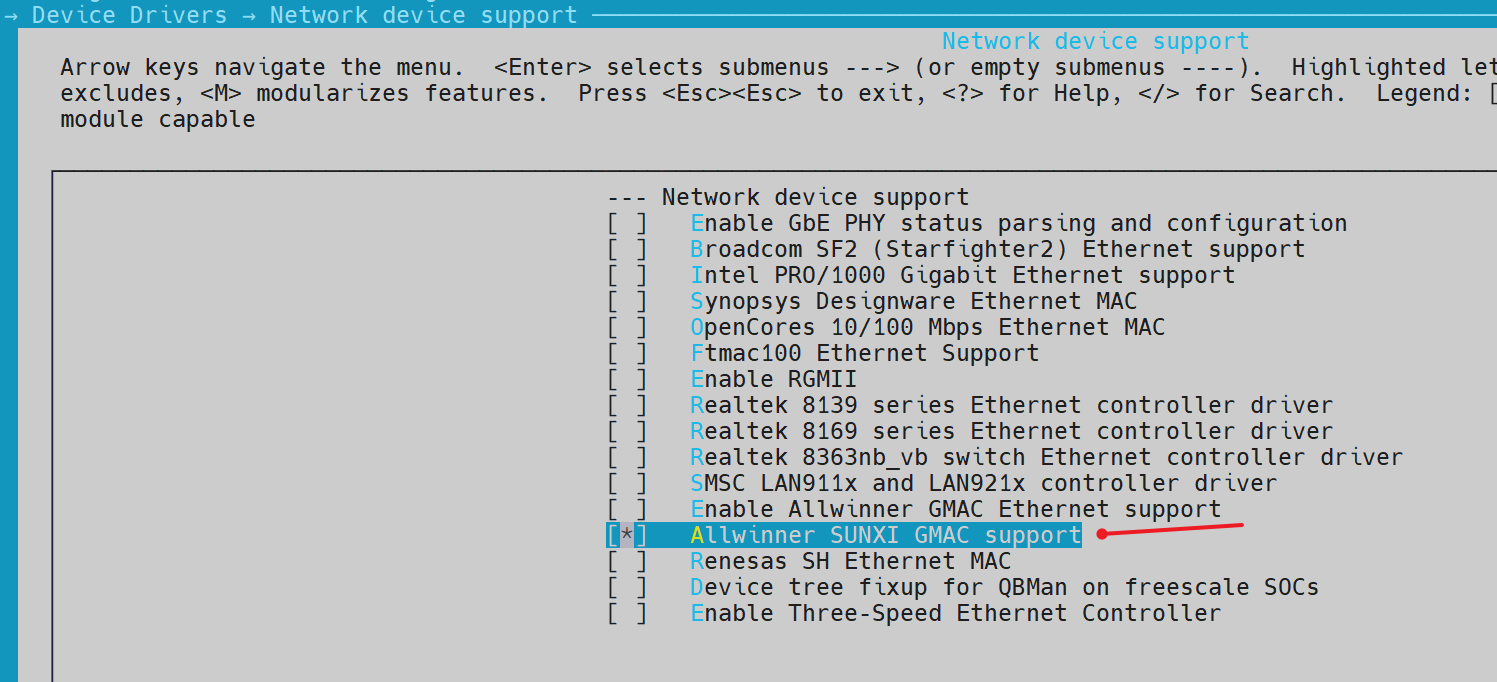

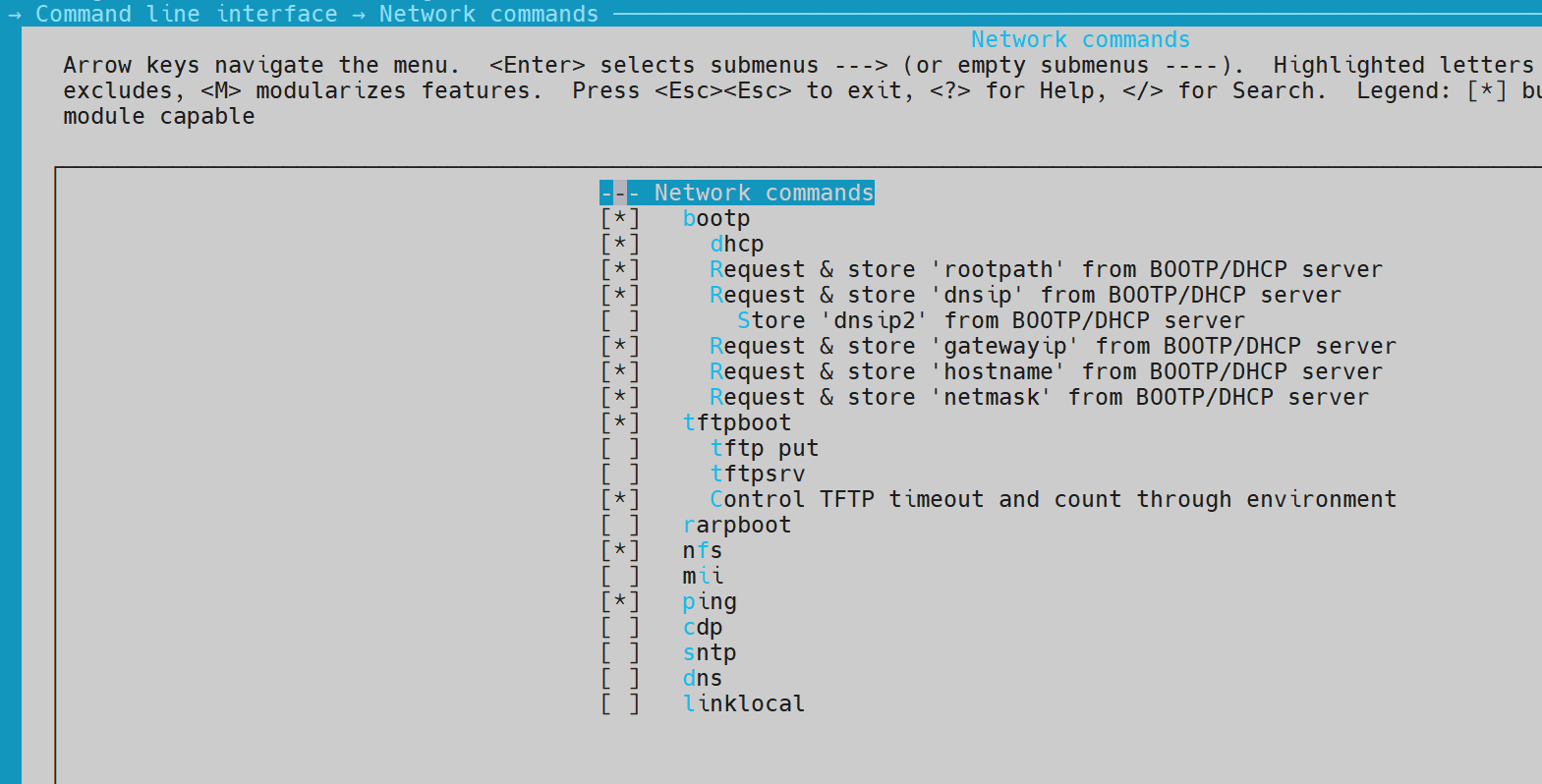

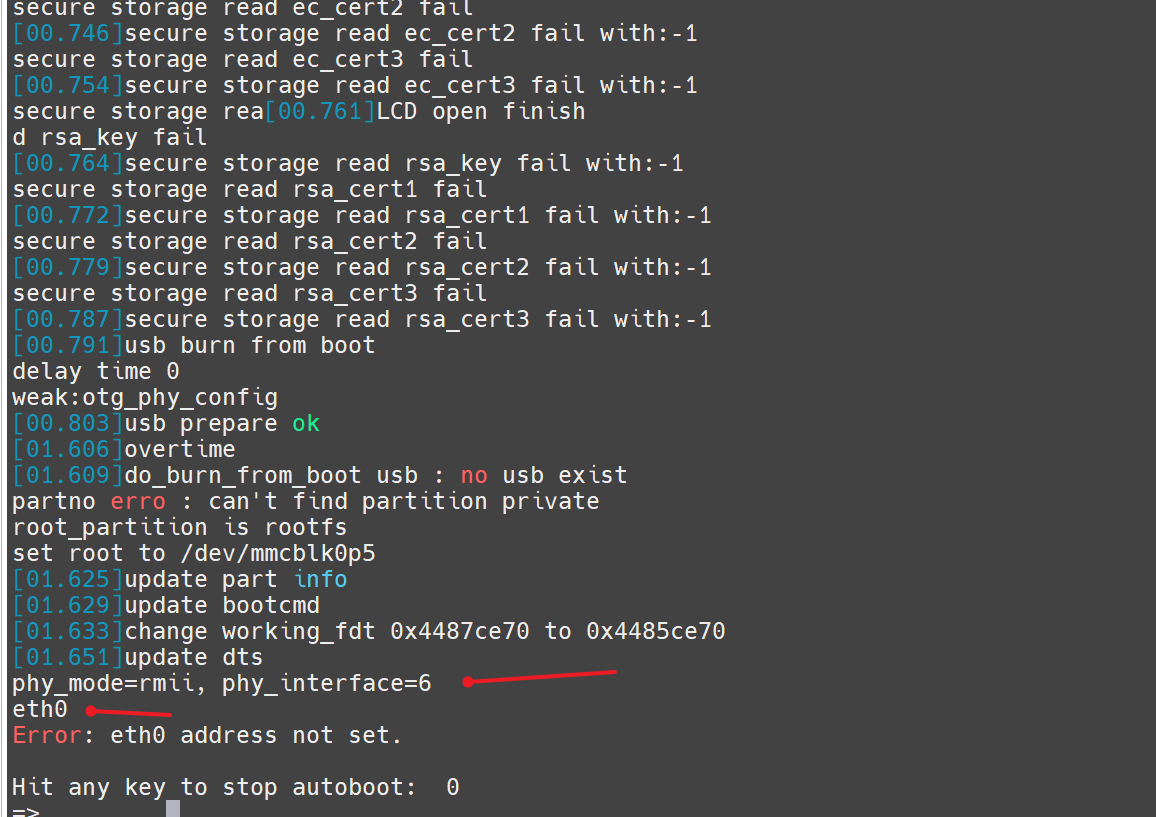

对于有线网卡,我们在我们的补丁文件中已经做了支持,但没有默认使能,需要我们手动进行使能,在开发板的串口终端输入