@wordiansom 已经可以拉了

WhycanService 发布的最佳帖子

-

新 SDK 平台下载 D1-H/D1s SDK发布在 MR Series

---->>>>>>水经验专帖:https://bbs.aw-ol.com/topic/4008/----<<<<<<

---->>>>>>请不要在本帖回复与技术问题无关的话题----<<<<<<获取SDK

SDK 使用 Repo 工具管理,拉取 SDK 需要配置安装 Repo 工具。

Repo is a tool built on top of Git. Repo helps manage many Git repositories, does the uploads to revision control systems, and automates parts of the development workflow. Repo is not meant to replace Git, only to make it easier to work with Git. The repo command is an executable Python script that you can put anywhere in your path.

Repo官网:git-repo

安装 Repo 工具

可以用包管理器进行安装:

# Debian/Ubuntu. $ sudo apt-get install repo # Gentoo. $ sudo emerge dev-vcs/repo也可以手动单独安装:

$ mkdir -p ~/.bin $ PATH="${HOME}/.bin:${PATH}" $ curl https://storage.googleapis.com/git-repo-downloads/repo > ~/.bin/repo $ chmod a+rx ~/.bin/repo国内镜像源安装:

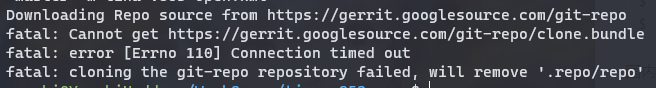

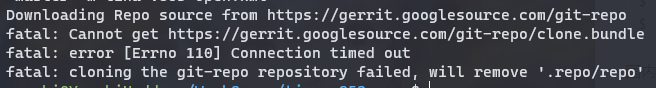

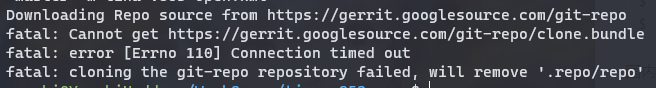

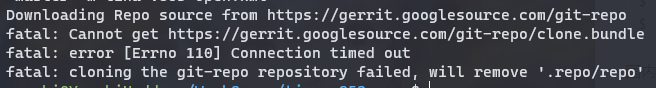

$ mkdir -p ~/.bin $ PATH="${HOME}/.bin:${PATH}" $ curl https://mirrors.bfsu.edu.cn/git/git-repo > ~/.bin/repo $ chmod a+rx ~/.bin/repo由于谷歌服务器位于国外,每次运行时Repo会检查更新导致下载较慢,国内用户可以配置镜像源。否则会像下图一样卡住不动然后失败。

更换镜像源

Repo 的运行过程中会尝试访问官方的 git 源更新自己,更换镜像源可以提高下载速度。将如下内容复制到你的

~/.bashrc里$ echo export REPO_URL='https://mirrors.bfsu.edu.cn/git/git-repo' >> ~/.bashrc $ source ~/.bashrc如果您使用的是 dash、hash、 zsh 等 shell,请参照 shell 的文档配置。

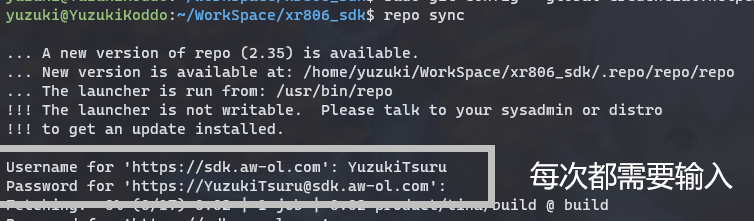

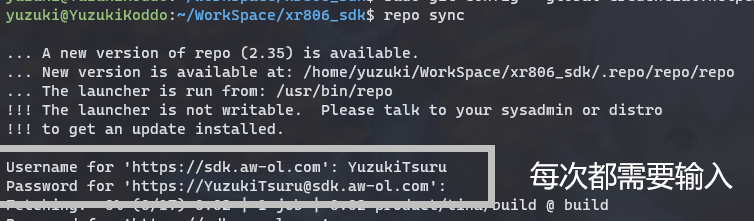

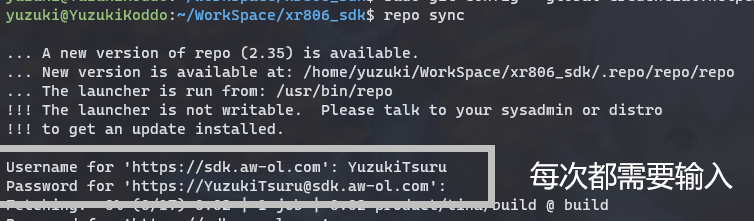

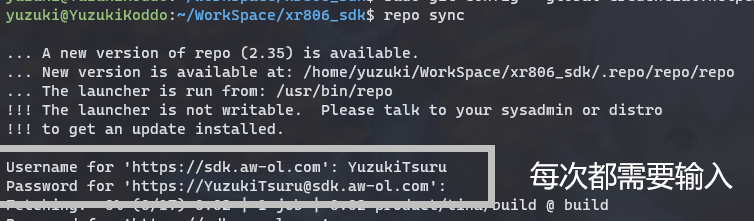

配置保存身份认证

新版本 git 默认加强了安全性,身份认证不会保存,导致拉取 repo 需要多次输入密码,可以用下列命令配置:

git config --global credential.helper store

常见问题

-

卡在

Downloading Repo source from https://gerrit.googlesource.com/git-repo不动。- 国内网络较慢,参照上面的更换镜像源解决。

-

配置保存身份认证无效不启用

- 检查是否运行了

sudo git config --global credential.helper store使用了sudo后保存的信息会存储到root用户下并非当前用户。

- 检查是否运行了

-

出现错误

fatal: cannot make directory: File exists- 之前拉取了 repo 但是不完整,需要删除

.repo文件夹重新拉取

- 之前拉取了 repo 但是不完整,需要删除

SDK 拉取

以

tina-d1-h为例,讲述如何拉取 SDK。新建文件夹保存 SDK

使用

mkdir命令新建文件夹,保存之后需要拉取的 SDK,然后cd进入到刚才新建的文件夹中。$ mkdir tina-d1-h $ cd tina-d1-h初始化 Repo 仓库

使用

repo init命令初始化仓库,tina-d1-h的仓库地址是https://sdk.aw-ol.com/git_repo/D1_Tina_Open/manifest.git需要执行命令:$ repo init -u https://sdk.aw-ol.com/git_repo/D1_Tina_Open/manifest.git -b master -m tina-d1-h.xml如果提示

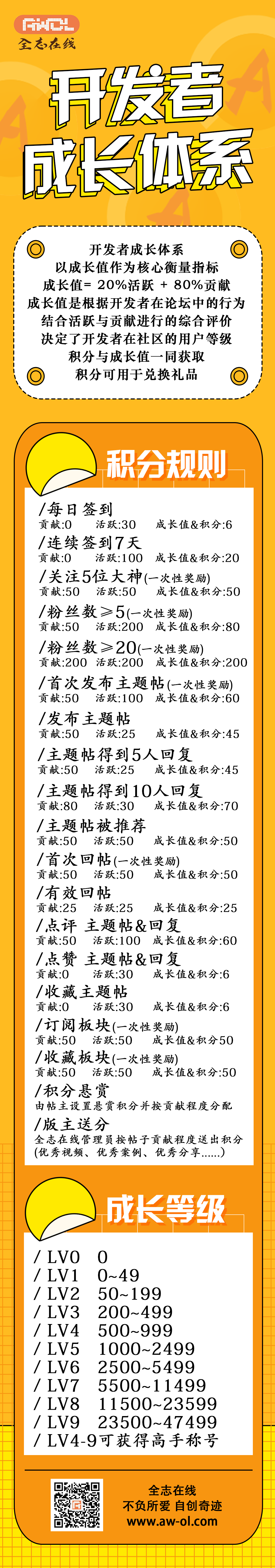

Username for 'https://sdk.aw-ol.com':请输入 全志在线开发者论坛 的用户名和密码。(注:需要全志在线开发者论坛LV2等级以上用户才有权限拉取 SDK)LV2 升级需要 49积分,获取积分方法如下:

① 1次主题帖发布(发帖):50积分

② 1次有效回帖:25积分

③ 1次点赞:6积分

④ 每日登录:6积分拉取 SDK

使用命令

repo sync拉取 SDK$ repo sync由于 SDK 普遍较大,拉取可能需要一定的时间。

创建开发环境

使用命令

repo start创建开发环境分支$ repo start product-smartx-d1-h-tina-stable-v2.0 --all至此,SDK 获取完毕。

-

-

新 SDK 平台下载 V853 SDK发布在 V Series

---->>>>>>水经验专帖:https://bbs.aw-ol.com/topic/4008/----<<<<<<

---->>>>>>请不要在本帖回复与技术问题无关的话题----<<<<<<获取SDK

SDK 使用 Repo 工具管理,拉取 SDK 需要配置安装 Repo 工具。

Repo is a tool built on top of Git. Repo helps manage many Git repositories, does the uploads to revision control systems, and automates parts of the development workflow. Repo is not meant to replace Git, only to make it easier to work with Git. The repo command is an executable Python script that you can put anywhere in your path.

Repo官网:git-repo

安装 Repo 工具

可以用包管理器进行安装:

# Debian/Ubuntu. $ sudo apt-get install repo # Gentoo. $ sudo emerge dev-vcs/repo也可以手动单独安装:

$ mkdir -p ~/.bin $ PATH="${HOME}/.bin:${PATH}" $ curl https://storage.googleapis.com/git-repo-downloads/repo > ~/.bin/repo $ chmod a+rx ~/.bin/repo国内镜像源安装:

$ mkdir -p ~/.bin $ PATH="${HOME}/.bin:${PATH}" $ curl https://mirrors.bfsu.edu.cn/git/git-repo > ~/.bin/repo $ chmod a+rx ~/.bin/repo由于谷歌服务器位于国外,每次运行时Repo会检查更新导致下载较慢,国内用户可以配置镜像源。否则会像下图一样卡住不动然后失败。

更换镜像源

Repo 的运行过程中会尝试访问官方的 git 源更新自己,更换镜像源可以提高下载速度。将如下内容复制到你的

~/.bashrc里$ echo export REPO_URL='https://mirrors.bfsu.edu.cn/git/git-repo' >> ~/.bashrc $ source ~/.bashrc如果您使用的是 dash、hash、 zsh 等 shell,请参照 shell 的文档配置。

配置保存身份认证

新版本 git 默认加强了安全性,身份认证不会保存,导致拉取 repo 需要多次输入密码,可以用下列命令配置:

git config --global credential.helper store

常见问题

-

卡在

Downloading Repo source from https://gerrit.googlesource.com/git-repo不动。- 国内网络较慢,参照上面的更换镜像源解决。

-

配置保存身份认证无效不启用

- 检查是否运行了

sudo git config --global credential.helper store使用了sudo后保存的信息会存储到root用户下并非当前用户。

- 检查是否运行了

-

出现错误

fatal: cannot make directory: File exists- 之前拉取了 repo 但是不完整,需要删除

.repo文件夹重新拉取

- 之前拉取了 repo 但是不完整,需要删除

SDK 拉取

以

tina-v853-open为例,讲述如何拉取 SDK。新建文件夹保存 SDK

使用

mkdir命令新建文件夹,保存之后需要拉取的 SDK,然后cd进入到刚才新建的文件夹中。$ mkdir tina-v853-open $ cd tina-v853-open初始化 Repo 仓库

使用

repo init命令初始化仓库,tina-d1-h的仓库地址是https://sdk.aw-ol.com/git_repo/V853Tina_Open/manifest.git需要执行命令:$ repo init -u https://sdk.aw-ol.com/git_repo/V853Tina_Open/manifest.git -b master -m tina-v853-open.xml如果提示

Username for 'https://sdk.aw-ol.com':请输入 全志在线开发者论坛 的用户名和密码。(注:需要全志在线开发者论坛LV2等级以上用户才有权限拉取 SDK)拉取 SDK

使用命令

repo sync拉取 SDK$ repo sync由于 SDK 普遍较大,拉取可能需要一定的时间。

创建开发环境

使用命令

repo start创建开发环境分支$ repo start devboard-v853-tina-for-awol --all至此,SDK 获取完毕。

-

-

回复: 全志在线开源芯片 新 SDK 平台下载方法汇总发布在 代码下载问题专区

@chrisvista T113-I 的 SDK AWOL 不提供,需要找原厂或代理合作商获取,另外 T113-I 使用的是 Linux 5.4/Linux 5.10 /Linux 5.15/ 三个版本的内核,V853的SDK提供的是 Linux 4.9,不受支持

-

新 SDK 平台下载 XR806 SDK发布在 Wireless & Analog Series

---->>>>>>水经验专帖:https://bbs.aw-ol.com/topic/4008/----<<<<<<

---->>>>>>请不要在本帖回复与技术问题无关的话题----<<<<<<获取SDK

SDK 拉取

以

xr806_sdk为例,讲述如何拉取 SDK。新建文件夹保存 SDK

使用

mkdir命令新建文件夹,保存之后需要拉取的 SDK,然后cd进入到刚才新建的文件夹中。$ mkdir xr806_sdk $ cd xr806_sdk初始化仓库

$ git clone https://sdk.aw-ol.com/git_repo/XR806/xr806_sdk/xr806_sdk.git -b xr806_sdk如果提示

Username for 'https://sdk.aw-ol.com':请输入 全志在线开发者论坛 的用户名和密码。(注:需要全志在线开发者论坛LV2等级以上用户才有权限拉取 SDK)LV2 升级需要 49积分,获取积分方法如下:

① 1次主题帖发布(发帖):50积分

② 1次有效回帖:25积分

③ 1次点赞:6积分

④ 每日登录:6积分由于 SDK 普遍较大,拉取可能需要一定的时间。

至此,SDK 获取完毕。可以安装开发环境

sudo apt-get install build-essential subversion git libncurses5-dev zlib1g-dev gawk flex bison quilt libssl-dev xsltproc libxml-parser-perl mercurial bzr ecj cvs unzip lsof kconfig-frontends android-tools-mkbootimg python2 libpython3-dev gcc-multilib libc6:i386 libstdc++6:i386 lib32z1 -

回复: 全志在线开源芯片 新 SDK 平台下载方法汇总发布在 代码下载问题专区

@roshen_007 低功耗参数需要根据实际开发形态来确定,比如是否使用PMU,休眠深度,外设控制参数等等,单独提供芯片的低功耗参数做参考没有意义。

-

新 SDK 平台下载 MR813 SDK发布在 A Series

获取SDK

SDK 使用 Repo 工具管理,拉取 SDK 需要配置安装 Repo 工具。

Repo is a tool built on top of Git. Repo helps manage many Git repositories, does the uploads to revision control systems, and automates parts of the development workflow. Repo is not meant to replace Git, only to make it easier to work with Git. The repo command is an executable Python script that you can put anywhere in your path.

Repo官网:git-repo

安装 Repo 工具

可以用包管理器进行安装:

# Debian/Ubuntu. $ sudo apt-get install repo # Gentoo. $ sudo emerge dev-vcs/repo也可以手动单独安装:

$ mkdir -p ~/.bin $ PATH="${HOME}/.bin:${PATH}" $ curl https://storage.googleapis.com/git-repo-downloads/repo > ~/.bin/repo $ chmod a+rx ~/.bin/repo国内镜像源安装:

$ mkdir -p ~/.bin $ PATH="${HOME}/.bin:${PATH}" $ curl https://mirrors.bfsu.edu.cn/git/git-repo > ~/.bin/repo $ chmod a+rx ~/.bin/repo由于谷歌服务器位于国外,每次运行时Repo会检查更新导致下载较慢,国内用户可以配置镜像源。否则会像下图一样卡住不动然后失败。

更换镜像源

Repo 的运行过程中会尝试访问官方的 git 源更新自己,更换镜像源可以提高下载速度。将如下内容复制到你的

~/.bashrc里$ echo export REPO_URL='https://mirrors.bfsu.edu.cn/git/git-repo' >> ~/.bashrc $ source ~/.bashrc如果您使用的是 dash、hash、 zsh 等 shell,请参照 shell 的文档配置。

配置保存身份认证

新版本 git 默认加强了安全性,身份认证不会保存,导致拉取 repo 需要多次输入密码,可以用下列命令配置:

git config --global credential.helper store

常见问题

-

卡在

Downloading Repo source from https://gerrit.googlesource.com/git-repo不动。- 国内网络较慢,参照上面的更换镜像源解决。

-

配置保存身份认证无效不启用

- 检查是否运行了

sudo git config --global credential.helper store使用了sudo后保存的信息会存储到root用户下并非当前用户。

- 检查是否运行了

-

出现错误

fatal: cannot make directory: File exists- 之前拉取了 repo 但是不完整,需要删除

.repo文件夹重新拉取

- 之前拉取了 repo 但是不完整,需要删除

SDK 拉取

以

Tina-MR813-OPEN为例,讲述如何拉取 SDK。新建文件夹保存 SDK

使用

mkdir命令新建文件夹,保存之后需要拉取的 SDK,然后cd进入到刚才新建的文件夹中。$ mkdir Tina-MR813-OPEN $ cd Tina-MR813-OPEN初始化 Repo 仓库

使用

repo init命令初始化仓库,Tina-MR813-OPEN的仓库地址是https://sdk.aw-ol.com/git_repo/MR813_Tina_OPEN/manifest.git需要执行命令:$ repo init -u https://sdk.aw-ol.com/git_repo/MR813_Tina_OPEN/manifest.git -b master -m Tina-MR813-OPEN.xml如果提示

Username for 'https://sdk.aw-ol.com':请输入 全志在线开发者论坛 的用户名和密码。(注:需要全志在线开发者论坛LV2等级以上用户才有权限拉取 SDK)拉取 SDK

使用命令

repo sync拉取 SDK$ repo sync由于 SDK 普遍较大,拉取可能需要一定的时间。

创建开发环境

使用命令

repo start创建开发环境分支$ repo start smartx-mr813-tina-v1.1 --all至此,SDK 获取完毕。

-

-

新 SDK 平台下载 R329 SDK发布在 其它全志芯片讨论区

---->>>>>>水经验专帖:https://bbs.aw-ol.com/topic/4008/----<<<<<<

---->>>>>>请不要在本帖回复与技术问题无关的话题----<<<<<<获取SDK

SDK 使用 Repo 工具管理,拉取 SDK 需要配置安装 Repo 工具。

Repo is a tool built on top of Git. Repo helps manage many Git repositories, does the uploads to revision control systems, and automates parts of the development workflow. Repo is not meant to replace Git, only to make it easier to work with Git. The repo command is an executable Python script that you can put anywhere in your path.

Repo官网:git-repo

安装 Repo 工具

可以用包管理器进行安装:

# Debian/Ubuntu. $ sudo apt-get install repo # Gentoo. $ sudo emerge dev-vcs/repo也可以手动单独安装:

$ mkdir -p ~/.bin $ PATH="${HOME}/.bin:${PATH}" $ curl https://storage.googleapis.com/git-repo-downloads/repo > ~/.bin/repo $ chmod a+rx ~/.bin/repo国内镜像源安装:

$ mkdir -p ~/.bin $ PATH="${HOME}/.bin:${PATH}" $ curl https://mirrors.bfsu.edu.cn/git/git-repo > ~/.bin/repo $ chmod a+rx ~/.bin/repo由于谷歌服务器位于国外,每次运行时Repo会检查更新导致下载较慢,国内用户可以配置镜像源。否则会像下图一样卡住不动然后失败。

更换镜像源

Repo 的运行过程中会尝试访问官方的 git 源更新自己,更换镜像源可以提高下载速度。将如下内容复制到你的

~/.bashrc里$ echo export REPO_URL='https://mirrors.bfsu.edu.cn/git/git-repo' >> ~/.bashrc $ source ~/.bashrc如果您使用的是 dash、hash、 zsh 等 shell,请参照 shell 的文档配置。

配置保存身份认证

新版本 git 默认加强了安全性,身份认证不会保存,导致拉取 repo 需要多次输入密码,可以用下列命令配置:

git config --global credential.helper store

常见问题

-

卡在

Downloading Repo source from https://gerrit.googlesource.com/git-repo不动。- 国内网络较慢,参照上面的更换镜像源解决。

-

配置保存身份认证无效不启用

- 检查是否运行了

sudo git config --global credential.helper store使用了sudo后保存的信息会存储到root用户下并非当前用户。

- 检查是否运行了

-

出现错误

fatal: cannot make directory: File exists- 之前拉取了 repo 但是不完整,需要删除

.repo文件夹重新拉取

- 之前拉取了 repo 但是不完整,需要删除

SDK 拉取

以

R329-Tina-jishu为例,讲述如何拉取 SDK。新建文件夹保存 SDK

使用

mkdir命令新建文件夹,保存之后需要拉取的 SDK,然后cd进入到刚才新建的文件夹中。$ mkdir R329-Tina-jishu $ cd R329-Tina-jishu初始化 Repo 仓库

使用

repo init命令初始化仓库,R329-Tina-jishu的仓库地址是https://sdk.aw-ol.com/git_repo/R329_Tina_jishu/manifest.git需要执行命令:$ repo init -u https://sdk.aw-ol.com/git_repo/R329_Tina_jishu/manifest.git -b master -m R329-Tina-jishu.xml如果提示

Username for 'https://sdk.aw-ol.com':请输入 全志在线开发者论坛 的用户名和密码。(注:需要全志在线开发者论坛LV2等级以上用户才有权限拉取 SDK)LV2 升级需要 49积分,获取积分方法如下:

① 1次主题帖发布(发帖):50积分

② 1次有效回帖:25积分

③ 1次点赞:6积分

④ 每日登录:6积分拉取 SDK

使用命令

repo sync拉取 SDK$ repo sync由于 SDK 普遍较大,拉取可能需要一定的时间。

创建开发环境

使用命令

repo start创建开发环境分支$ repo start smartx-r329-tina-jishu --all至此,SDK 获取完毕。

-

-

回复: 新 SDK 平台下载 D1-H/D1s SDK发布在 MR Series

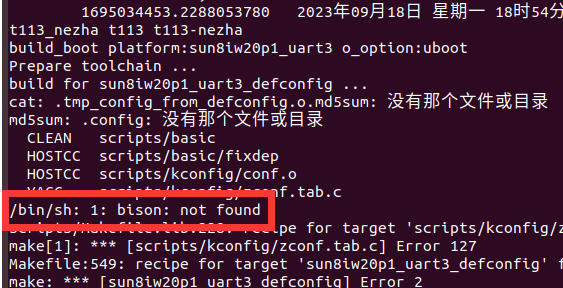

@vuiot 基础开发环境没有安装,缺少bison命令

sudo apt-get install build-essential subversion git libncurses5-dev zlib1g-dev gawk flex bison quilt libssl-dev xsltproc libxml-parser-perl mercurial bzr ecj cvs unzip lsof kconfig-frontends android-tools-mkbootimg python2 libpython3-dev gcc-multilib libc6:i386 libstdc++6:i386 lib32z1 -

回复: 全志在线开源芯片 新 SDK 平台下载方法汇总发布在 代码下载问题专区

@roshen_007 https://storage.googleapis.com/ 这个网址是谷歌官方源,由于众所周知的原因国内无法访问,请使用国内镜像源代替

$ mkdir -p ~/.bin $ PATH="${HOME}/.bin:${PATH}" $ curl https://mirrors.bfsu.edu.cn/git/git-repo > ~/.bin/repo $ chmod a+rx ~/.bin/repo -

【奇淫巧计】使用 PhoenixSuit 清空NAND,eMMC,Flash存储器发布在 代码下载问题专区

有的时候想把flash擦成空片或者只格式化普通分区如user data分区,但是又不想重新烧录固件,如何只进行擦除而不升级固件?

(1)把附件spec_tool_只擦除flash不烧录固件的插件.fex,重命名为spec_tool.fex放到烧录工具目录下。

(2)PhoenixSuit:选择机器对应的固件。选择工具界面上保留数据升级:勾选该按钮,则升级前不进行格式化,private,secure storage、user data、mbr分区保留,其他擦除;选择分区擦除升级:勾选该按钮,则升级前只格式化普通分区,private,secure storage分区保留,其他擦除(注意会擦除mbr然后重新烧录mbr);选择全盘擦除升级:勾选该按钮,则升级前格式化全盘,包括SN等数据整块flash全部擦除执行完后flash变成空片,然后执行烧录。

(3)PhoenixUsbpro:不勾选工具上的全盘擦除,是否擦除取决于sysconfig.fex的eraseflag字段;勾选工具上的全盘擦除,整块flash全部擦除。

(4)awflash:命令行烧录工具,加上参数-e表示全盘擦除,不带-e参数是否擦除取决于sysconfig.fex的eraseflag字段。注:全盘擦除需要是uboot2018及以上的uboot版本,如果需要恢复成正常烧录固件请把spec_tool.fex文件删除然后重启工具即可。擦成空片后的flash如果打开了工具会执行跳fel动作。如果操作不成功,请查看串口打印erase_flag的值是否对应正确。

-

回复: 移植RTL8188fu驱动编译报错,sw_usb_enable_hcd等函数未定义发布在 编译和烧写问题专区

@fanfan 我这里什么都没修改,勾选上直接编译完成了

编译log:

CALL scripts/checksyscalls.sh CALL scripts/atomic/check-atomics.sh CHK include/generated/compile.h CC [M] drivers/net/wireless/rtl8211cu/core/rtw_cmd.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_security.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_debug.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_io.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_ioctl_query.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_ioctl_set.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_ieee80211.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_mlme.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_mlme_ext.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_mi.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_wlan_util.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_vht.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_pwrctrl.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_rf.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_chplan.o CC [M] drivers/net/wireless/rtl8211cu/core/monitor/rtw_radiotap.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_recv.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_sta_mgt.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_ap.o CC [M] drivers/net/wireless/rtl8211cu/core/wds/rtw_wds.o CC [M] drivers/net/wireless/rtl8211cu/core/mesh/rtw_mesh.o CC [M] drivers/net/wireless/rtl8211cu/core/mesh/rtw_mesh_pathtbl.o CC [M] drivers/net/wireless/rtl8211cu/core/mesh/rtw_mesh_hwmp.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_xmit.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_p2p.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_rson.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_tdls.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_br_ext.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_iol.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_sreset.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_btcoex_wifionly.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_btcoex.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_beamforming.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_odm.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_rm.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_rm_fsm.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_ft.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_wnm.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_mbo.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_rm_util.o CC [M] drivers/net/wireless/rtl8211cu/core/efuse/rtw_efuse.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_roch.o CC [M] drivers/net/wireless/rtl8211cu/core/crypto/aes-internal.o CC [M] drivers/net/wireless/rtl8211cu/core/crypto/aes-internal-enc.o CC [M] drivers/net/wireless/rtl8211cu/core/crypto/aes-gcm.o CC [M] drivers/net/wireless/rtl8211cu/core/crypto/aes-ccm.o CC [M] drivers/net/wireless/rtl8211cu/core/crypto/aes-omac1.o CC [M] drivers/net/wireless/rtl8211cu/core/crypto/ccmp.o CC [M] drivers/net/wireless/rtl8211cu/core/crypto/gcmp.o CC [M] drivers/net/wireless/rtl8211cu/core/crypto/aes-siv.o CC [M] drivers/net/wireless/rtl8211cu/core/crypto/aes-ctr.o CC [M] drivers/net/wireless/rtl8211cu/core/crypto/sha256-internal.o CC [M] drivers/net/wireless/rtl8211cu/core/crypto/sha256.o CC [M] drivers/net/wireless/rtl8211cu/core/crypto/sha256-prf.o CC [M] drivers/net/wireless/rtl8211cu/core/crypto/rtw_crypto_wrap.o CC [M] drivers/net/wireless/rtl8211cu/core/rtw_swcrypto.o CC [M] drivers/net/wireless/rtl8211cu/os_dep/osdep_service.o CC [M] drivers/net/wireless/rtl8211cu/os_dep/linux/os_intfs.o CC [M] drivers/net/wireless/rtl8211cu/os_dep/linux/usb_intf.o CC [M] drivers/net/wireless/rtl8211cu/os_dep/linux/usb_ops_linux.o CC [M] drivers/net/wireless/rtl8211cu/os_dep/linux/ioctl_linux.o CC [M] drivers/net/wireless/rtl8211cu/os_dep/linux/xmit_linux.o CC [M] drivers/net/wireless/rtl8211cu/os_dep/linux/mlme_linux.o CC [M] drivers/net/wireless/rtl8211cu/os_dep/linux/recv_linux.o CC [M] drivers/net/wireless/rtl8211cu/os_dep/linux/ioctl_cfg80211.o CC [M] drivers/net/wireless/rtl8211cu/os_dep/linux/rtw_cfgvendor.o CC [M] drivers/net/wireless/rtl8211cu/os_dep/linux/wifi_regd.o CC [M] drivers/net/wireless/rtl8211cu/os_dep/linux/rtw_android.o CC [M] drivers/net/wireless/rtl8211cu/os_dep/linux/rtw_proc.o CC [M] drivers/net/wireless/rtl8211cu/os_dep/linux/nlrtw.o CC [M] drivers/net/wireless/rtl8211cu/os_dep/linux/rtw_rhashtable.o CC [M] drivers/net/wireless/rtl8211cu/hal/hal_intf.o CC [M] drivers/net/wireless/rtl8211cu/hal/hal_com.o CC [M] drivers/net/wireless/rtl8211cu/hal/hal_com_phycfg.o CC [M] drivers/net/wireless/rtl8211cu/hal/hal_phy.o CC [M] drivers/net/wireless/rtl8211cu/hal/hal_dm.o CC [M] drivers/net/wireless/rtl8211cu/hal/hal_dm_acs.o CC [M] drivers/net/wireless/rtl8211cu/hal/hal_btcoex_wifionly.o CC [M] drivers/net/wireless/rtl8211cu/hal/hal_btcoex.o CC [M] drivers/net/wireless/rtl8211cu/hal/hal_mp.o CC [M] drivers/net/wireless/rtl8211cu/hal/hal_mcc.o CC [M] drivers/net/wireless/rtl8211cu/hal/hal_hci/hal_usb.o CC [M] drivers/net/wireless/rtl8211cu/hal/led/hal_led.o CC [M] drivers/net/wireless/rtl8211cu/hal/led/hal_usb_led.o CC [M] drivers/net/wireless/rtl8211cu/hal/rtl8821c/rtl8821c_halinit.o CC [M] drivers/net/wireless/rtl8211cu/hal/rtl8821c/rtl8821c_mac.o CC [M] drivers/net/wireless/rtl8211cu/hal/rtl8821c/rtl8821c_cmd.o CC [M] drivers/net/wireless/rtl8211cu/hal/rtl8821c/rtl8821c_phy.o CC [M] drivers/net/wireless/rtl8211cu/hal/rtl8821c/rtl8821c_dm.o CC [M] drivers/net/wireless/rtl8211cu/hal/rtl8821c/rtl8821c_ops.o CC [M] drivers/net/wireless/rtl8211cu/hal/rtl8821c/hal8821c_fw.o CC [M] drivers/net/wireless/rtl8211cu/hal/rtl8821c/usb/rtl8821cu_halinit.o CC [M] drivers/net/wireless/rtl8211cu/hal/rtl8821c/usb/rtl8821cu_halmac.o CC [M] drivers/net/wireless/rtl8211cu/hal/rtl8821c/usb/rtl8821cu_io.o CC [M] drivers/net/wireless/rtl8211cu/hal/rtl8821c/usb/rtl8821cu_xmit.o CC [M] drivers/net/wireless/rtl8211cu/hal/rtl8821c/usb/rtl8821cu_recv.o CC [M] drivers/net/wireless/rtl8211cu/hal/rtl8821c/usb/rtl8821cu_led.o CC [M] drivers/net/wireless/rtl8211cu/hal/rtl8821c/usb/rtl8821cu_ops.o CC [M] drivers/net/wireless/rtl8211cu/hal/efuse/rtl8821c/HalEfuseMask8821C_USB.o CC [M] drivers/net/wireless/rtl8211cu/hal/hal_halmac.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_api.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_dbg.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_bb_rf_88xx.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_cfg_wmac_88xx.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_common_88xx.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_efuse_88xx.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_flash_88xx.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_fw_88xx.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_gpio_88xx.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_init_88xx.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_mimo_88xx.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_usb_88xx.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_8821c/halmac_cfg_wmac_8821c.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_8821c/halmac_common_8821c.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_8821c/halmac_gpio_8821c.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_8821c/halmac_init_8821c.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_8821c/halmac_phy_8821c.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_8821c/halmac_pwr_seq_8821c.o CC [M] drivers/net/wireless/rtl8211cu/hal/halmac/halmac_88xx/halmac_8821c/halmac_usb_8821c.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_debug.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_antdiv.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_soml.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_smt_ant.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_antdect.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_interface.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_phystatus.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_hwconfig.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_dig.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_pathdiv.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_rainfo.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_dynamictxpower.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_adaptivity.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_cfotracking.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_noisemonitor.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_beamforming.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_direct_bf.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_dfs.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/txbf/halcomtxbf.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/txbf/haltxbfinterface.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/txbf/phydm_hal_txbf_api.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_adc_sampling.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_ccx.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_psd.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_primary_cca.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_cck_pd.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_rssi_monitor.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_auto_dbg.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_math_lib.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_api.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_pow_train.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_lna_sat.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_pmac_tx_setting.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_mp.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/phydm_cck_rx_pathdiv.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/halrf/halrf.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/halrf/halrf_debug.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/halrf/halphyrf_ce.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/halrf/halrf_powertracking_ce.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/halrf/halrf_powertracking.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/halrf/halrf_kfree.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/halrf/halrf_psd.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/rtl8821c/halhwimg8821c_bb.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/rtl8821c/halhwimg8821c_mac.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/rtl8821c/phydm_hal_api8821c.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/rtl8821c/phydm_regconfig8821c.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/rtl8821c/phydm_rtl8821c.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/halrf/rtl8821c/halhwimg8821c_rf.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/halrf/rtl8821c/halrf_8821c.o CC [M] drivers/net/wireless/rtl8211cu/hal/phydm/halrf/rtl8821c/halrf_iqk_8821c.o CC [M] drivers/net/wireless/rtl8211cu/hal/btc/halbtc8821cwifionly.o CC [M] drivers/net/wireless/rtl8211cu/hal/btc/halbtc8821c1ant.o CC [M] drivers/net/wireless/rtl8211cu/hal/btc/halbtc8821c2ant.o CC [M] drivers/net/wireless/rtl8211cu/platform/platform_ops.o CC [M] drivers/net/wireless/rtl8211cu/platform/platform_ARM_SUNxI_usb.o drivers/net/wireless/rtl8211cu/platform/platform_ARM_SUNxI_usb.c: In function 'platform_wifi_power_on': drivers/net/wireless/rtl8211cu/platform/platform_ARM_SUNxI_usb.c:119:1: warning: label 'exit' defined but not used [-Wunused-label] exit: ^~~~ drivers/net/wireless/rtl8211cu/platform/platform_ARM_SUNxI_usb.c: At top level: cc1: warning: unrecognized command line option '-Wno-implicit-fallthrough' LD [M] drivers/net/wireless/rtl8211cu/8821cu.o可能是驱动不一样的问题,我这个驱动是原厂提供的。

platform_ARM_SUNxI_usb.c

/****************************************************************************** * * Copyright(c) 2013 Realtek Corporation. All rights reserved. * * This program is free software; you can redistribute it and/or modify it * under the terms of version 2 of the GNU General Public License as * published by the Free Software Foundation. * * This program is distributed in the hope that it will be useful, but WITHOUT * ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or * FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for * more details. * * You should have received a copy of the GNU General Public License along with * this program; if not, write to the Free Software Foundation, Inc., * 51 Franklin Street, Fifth Floor, Boston, MA 02110, USA * * ******************************************************************************/ /* * Description: * This file can be applied to following platforms: * CONFIG_PLATFORM_ARM_SUNXI Series platform * */ #include <drv_types.h> #ifdef CONFIG_PLATFORM_ARM_SUNxI extern int sunxi_usb_disable_hcd(__u32 usbc_no); extern int sunxi_usb_enable_hcd(__u32 usbc_no); extern int sunxi_wlan_get_bus_index(void); extern void sunxi_wlan_set_power(int on); #endif #if defined(CONFIG_PLATFORM_ARM_SUN6I) || defined(CONFIG_PLATFORM_ARM_SUN7I) extern int sw_usb_disable_hcd(__u32 usbc_no); extern int sw_usb_enable_hcd(__u32 usbc_no); extern void wifi_pm_power(int on); static script_item_u item; #endif #ifdef CONFIG_PLATFORM_ARM_SUN8I extern int sunxi_usb_disable_hcd(__u32 usbc_no); extern int sunxi_usb_enable_hcd(__u32 usbc_no); extern void wifi_pm_power(int on); static script_item_u item; #endif int platform_wifi_power_on(void) { int ret = 0; int usb_no = sunxi_wlan_get_bus_index(); printk("platform_wifi_power_on(), usb_index: %d\n", usb_no); #ifdef CONFIG_PLATFORM_ARM_SUNxI #ifndef CONFIG_RTL8723A { /* ----------get usb_wifi_usbc_num------------- */ sunxi_wlan_set_power(1); mdelay(100); } #endif //CONFIG_RTL8723A #endif //CONFIG_PLATFORM_ARM_SUNxI #if defined(CONFIG_PLATFORM_ARM_SUN6I) || defined(CONFIG_PLATFORM_ARM_SUN7I) { script_item_value_type_e type; type = script_get_item("wifi_para", "wifi_usbc_id", &item); if(SCIRPT_ITEM_VALUE_TYPE_INT != type){ printk("ERR: script_get_item wifi_usbc_id failed\n"); ret = -ENOMEM; goto exit; } printk("sw_usb_enable_hcd: usbc_num = %d\n", item.val); wifi_pm_power(1); mdelay(10); #if !(defined(CONFIG_RTL8723A)) && !(defined(CONFIG_RTL8723B)) sw_usb_enable_hcd(item.val); #endif } #endif //defined(CONFIG_PLATFORM_ARM_SUN6I) || defined(CONFIG_PLATFORM_ARM_SUN7I) #if defined(CONFIG_PLATFORM_ARM_SUN8I) { script_item_value_type_e type; type = script_get_item("wifi_para", "wifi_usbc_id", &item); if(SCIRPT_ITEM_VALUE_TYPE_INT != type){ printk("ERR: script_get_item wifi_usbc_id failed\n"); ret = -ENOMEM; goto exit; } printk("sw_usb_enable_hcd: usbc_num = %d\n", item.val); wifi_pm_power(1); mdelay(10); #if !(defined(CONFIG_RTL8723A)) && !(defined(CONFIG_RTL8723B)) sunxi_usb_enable_hcd(item.val); #endif } #endif //CONFIG_PLATFORM_ARM_SUN8I exit: return ret; } void platform_wifi_power_off(void) { int usb_no = sunxi_wlan_get_bus_index(); printk("platform_wifi_power_off(), usb_index: %d\n", usb_no); #ifdef CONFIG_PLATFORM_ARM_SUNxI #ifndef CONFIG_RTL8723A //DBG_8192C("sw_usb_disable_hcd: usbc_num = %d\n", usb_wifi_host); //sw_usb_disable_hcd(usb_wifi_host); mdelay(100); sunxi_wlan_set_power(0); #endif //ifndef CONFIG_RTL8723A #endif //CONFIG_PLATFORM_ARM_SUNxI #if defined(CONFIG_PLATFORM_ARM_SUN6I) || defined(CONFIG_PLATFORM_ARM_SUN7I) #if !(defined(CONFIG_RTL8723A)) && !(defined(CONFIG_RTL8723B)) sw_usb_disable_hcd(item.val); #endif wifi_pm_power(0); #endif //defined(CONFIG_PLATFORM_ARM_SUN6I) || defined(CONFIG_PLATFORM_ARM_SUN7I) #if defined(CONFIG_PLATFORM_ARM_SUN8I) #if !(defined(CONFIG_RTL8723A)) && !(defined(CONFIG_RTL8723B)) sunxi_usb_disable_hcd(item.val); #endif wifi_pm_power(0); #endif //defined(CONFIG_PLATFORM_ARM_SUN8I) }如果出现

WARNING: module 8821cu uses symbol kernel_read from namespace VFS_internal_I_am_really_a_filesystem_and_am_NOT_a_driver, but does not import it.可以参考:

D1 LicheeRV Dock 移植RTL8723DS驱动

-

回复: 全志在线开源芯片 新 SDK 平台下载方法汇总发布在 代码下载问题专区

@ufbycd 远程仓库只是一个git仓库,并不会影响repo的报错,这个问题是本地repo的问题,需要谷歌升级repo的python版本与全志无关。

-

回复: A133适配AMOLED屏幕,LCD时序参数过小导致无法进入U-Boot发布在 其它全志芯片讨论区

lcd_x = 屏厂给的实际的x lcd_hbp = 屏厂给的实际的hbp + 屏厂给的实际的hsync lcd_ht = 屏厂给的实际的lcd_h + 屏厂给的实际的hsync + 屏厂给的实际的hbp + 屏厂给的实际的hfp lcd_hspw = 屏厂给的实际的hsync lcd_y = 屏厂给的实际的y lcd_vbp = 屏厂给的实际的vbp + 屏厂给的实际的vsync lcd_vt = 屏厂给的实际的lcd_y + 屏厂给的实际的vsync + 屏厂给的实际的vbp + 屏厂给的实际的vfp lcd_vspw = 屏厂给的实际的vsync驱动会通过上面的参数计算lcd_xbp与lcd_xspw的值来确定实际的屏幕的参数(实际的vsync,实际的vbp等等),当给的值不对计算出现负数的时候会卡死不启动。

-

回复: 移植RTL8188fu驱动编译报错,sw_usb_enable_hcd等函数未定义发布在 编译和烧写问题专区

@hy123456 检查makefile的配置:

########################## WIFI IC ############################ CONFIG_MULTIDRV = n CONFIG_RTL8188E = n CONFIG_RTL8812A = n CONFIG_RTL8821A = n CONFIG_RTL8192E = n CONFIG_RTL8723B = n CONFIG_RTL8814A = n CONFIG_RTL8723C = n CONFIG_RTL8188F = y CONFIG_RTL8822B = n CONFIG_RTL8723D = n CONFIG_RTL8821C = n ######################### Interface ########################### CONFIG_USB_HCI = y CONFIG_PCI_HCI = n CONFIG_SDIO_HCI = n CONFIG_GSPI_HCI = n ########################## Features ########################### CONFIG_MP_INCLUDED = y CONFIG_POWER_SAVING = y CONFIG_USB_AUTOSUSPEND = n CONFIG_HW_PWRP_DETECTION = n CONFIG_WIFI_TEST = n CONFIG_BT_COEXIST = n CONFIG_INTEL_WIDI = n CONFIG_WAPI_SUPPORT = n CONFIG_EFUSE_CONFIG_FILE = y CONFIG_EXT_CLK = n CONFIG_TRAFFIC_PROTECT = n CONFIG_LOAD_PHY_PARA_FROM_FILE = y CONFIG_TXPWR_BY_RATE_EN = y CONFIG_TXPWR_LIMIT_EN = n CONFIG_RTW_CHPLAN = 0xFF CONFIG_RTW_ADAPTIVITY_EN = disable CONFIG_RTW_ADAPTIVITY_MODE = normal CONFIG_SIGNAL_SCALE_MAPPING = n CONFIG_80211W = n CONFIG_REDUCE_TX_CPU_LOADING = n CONFIG_BR_EXT = y CONFIG_TDLS = n CONFIG_WIFI_MONITOR = n CONFIG_MCC_MODE = n CONFIG_APPEND_VENDOR_IE_ENABLE = n CONFIG_RTW_NAPI = y CONFIG_RTW_GRO = y CONFIG_RTW_NETIF_SG = n CONFIG_RTW_IPCAM_APPLICATION = n CONFIG_RTW_REPEATER_SON = n CONFIG_RTW_WIFI_HAL = y ########################## Debug ########################### CONFIG_RTW_DEBUG = y # default log level is _DRV_INFO_ = 4, # please refer to "How_to_set_driver_debug_log_level.doc" to set the available level. CONFIG_RTW_LOG_LEVEL = 1 ######################## Wake On Lan ########################## CONFIG_WOWLAN = n CONFIG_WAKEUP_TYPE = 0x7 #bit2: deauth, bit1: unicast, bit0: magic pkt. CONFIG_GPIO_WAKEUP = n CONFIG_WAKEUP_GPIO_IDX = default CONFIG_HIGH_ACTIVE = n CONFIG_PNO_SUPPORT = n CONFIG_PNO_SET_DEBUG = n CONFIG_AP_WOWLAN = n ######### Notify SDIO Host Keep Power During Syspend ########## CONFIG_RTW_SDIO_PM_KEEP_POWER = y ###################### MP HW TX MODE FOR VHT ####################### CONFIG_MP_VHT_HW_TX_MODE = n ###################### Platform Related ####################### CONFIG_PLATFORM_I386_PC = n CONFIG_PLATFORM_ANDROID_X86 = n CONFIG_PLATFORM_ANDROID_INTEL_X86 = n CONFIG_PLATFORM_JB_X86 = n CONFIG_PLATFORM_ARM_S3C2K4 = n CONFIG_PLATFORM_ARM_PXA2XX = n CONFIG_PLATFORM_ARM_S3C6K4 = n CONFIG_PLATFORM_MIPS_RMI = n CONFIG_PLATFORM_RTD2880B = n CONFIG_PLATFORM_MIPS_AR9132 = n CONFIG_PLATFORM_RTK_DMP = n CONFIG_PLATFORM_MIPS_PLM = n CONFIG_PLATFORM_MSTAR389 = n CONFIG_PLATFORM_MT53XX = n CONFIG_PLATFORM_ARM_MX51_241H = n CONFIG_PLATFORM_FS_MX61 = n CONFIG_PLATFORM_ACTIONS_ATJ227X = n CONFIG_PLATFORM_TEGRA3_CARDHU = n CONFIG_PLATFORM_TEGRA4_DALMORE = n CONFIG_PLATFORM_ARM_TCC8900 = n CONFIG_PLATFORM_ARM_TCC8920 = n CONFIG_PLATFORM_ARM_TCC8920_JB42 = n CONFIG_PLATFORM_ARM_TCC8930_JB42 = n CONFIG_PLATFORM_ARM_RK2818 = n CONFIG_PLATFORM_ARM_RK3066 = n CONFIG_PLATFORM_ARM_RK3188 = n CONFIG_PLATFORM_ARM_URBETTER = n CONFIG_PLATFORM_ARM_TI_PANDA = n CONFIG_PLATFORM_MIPS_JZ4760 = n CONFIG_PLATFORM_DMP_PHILIPS = n CONFIG_PLATFORM_MSTAR_TITANIA12 = n CONFIG_PLATFORM_MSTAR = n CONFIG_PLATFORM_SZEBOOK = n CONFIG_PLATFORM_ARM_SUNxI = y CONFIG_PLATFORM_ARM_SUN6I = n CONFIG_PLATFORM_ARM_SUN7I = n CONFIG_PLATFORM_ARM_SUN8I_W3P1 = n CONFIG_PLATFORM_ARM_SUN8I_W5P1 = n CONFIG_PLATFORM_ACTIONS_ATM702X = n CONFIG_PLATFORM_ACTIONS_ATV5201 = n CONFIG_PLATFORM_ACTIONS_ATM705X = n CONFIG_PLATFORM_ARM_SUN50IW1P1 = n CONFIG_PLATFORM_ARM_RTD299X = n CONFIG_PLATFORM_ARM_SPREADTRUM_6820 = n CONFIG_PLATFORM_ARM_SPREADTRUM_8810 = n CONFIG_PLATFORM_ARM_WMT = n CONFIG_PLATFORM_TI_DM365 = n CONFIG_PLATFORM_MOZART = n CONFIG_PLATFORM_RTK119X = n CONFIG_PLATFORM_RTK129X = n CONFIG_PLATFORM_NOVATEK_NT72668 = n CONFIG_PLATFORM_HISILICON = n CONFIG_PLATFORM_HISILICON_HI3798 = n CONFIG_PLATFORM_NV_TK1 = n CONFIG_PLATFORM_NV_TK1_UBUNTU = n CONFIG_PLATFORM_RTL8197D = n CONFIG_PLATFORM_AML_S905 = n CONFIG_PLATFORM_ZTE_ZX296716 = n ###############################################################测试直接编译通过

-

回复: MQ-R F133 NandFlash 烧录失败 55% W25N02KVZEIR WSON-8 3V 2Gb 串行NAND发布在 其它全志芯片讨论区

W25N02KVZEIR 不在支持列表,没有适配测试

-

回复: 移植RTL8188fu驱动编译报错,sw_usb_enable_hcd等函数未定义发布在 编译和烧写问题专区

@hy123456 我这也搜索不到定义,但是貌似没有使用那一段代码,直接编译通过的

-

回复: V853/V851s 增加 OpenCV, FFmpeg 编译包发布在 V Series

@lingzhi12321 以aiohttp为例,参考下列makefile即可

tina-v853\openwrt\package\feeds\lang\python\python-aiohttp# # Copyright (C) 2019-2021 CZ.NIC, z. s. p. o. (https://www.nic.cz/) # # This is free software, licensed under the GNU General Public License v2. # See /LICENSE for more information. # include $(TOPDIR)/rules.mk PKG_NAME:=aiohttp PKG_VERSION:=3.7.4 PKG_RELEASE:=1 PYPI_NAME:=$(PKG_NAME) PKG_HASH:=5d84ecc73141d0a0d61ece0742bb7ff5751b0657dab8405f899d3ceb104cc7de PKG_MAINTAINER:=Josef Schlehofer <pepe.schlehofer@gmail.com> PKG_LICENSE:=Apache-2.0 PKG_LICENSE_FILES:=LICENSE PKG_CPE_ID:=cpe:/a:aio-libs_project:aiohttp include ../pypi.mk include $(INCLUDE_DIR)/package.mk include ../python3-package.mk define Package/python3-aiohttp SECTION:=lang CATEGORY:=Languages SUBMENU:=Python TITLE:=Async http client/server framework (asyncio) URL:=https://github.com/aio-libs/aiohttp DEPENDS:= \ +python3-light \ +python3-attrs \ +python3-chardet \ +python3-multidict \ +python3-async-timeout \ +python3-yarl \ +python3-logging \ +python3-codecs \ +python3-cgi \ +python3-openssl \ +python3-typing-extensions endef define Package/python3-aiohttp/description Asynchronous HTTP client/server framework for asyncio and Python3. endef $(eval $(call Py3Package,python3-aiohttp)) $(eval $(call BuildPackage,python3-aiohttp)) $(eval $(call BuildPackage,python3-aiohttp-src))请注意如果需要matpltlib需要移植完整的xserver到开发板上,会占用大量内存

-

回复: 请问D1H这么多分区都是干什么用的?发布在 MR Series

- BOOT_RESOURCE: 启动LOGO,开机动画

- ENV:启动参数,环境

- ENV-REDUND:启动参数,环境的备份分区,防止变砖

- BOOT:uboot,kernel,dtb打包的一个分区,包含内核

- DSP0:dsp小核固件

- ROOTFS:rootfs

-

回复: t507 4.9 linux xr829问题发布在 Wireless & Analog Series

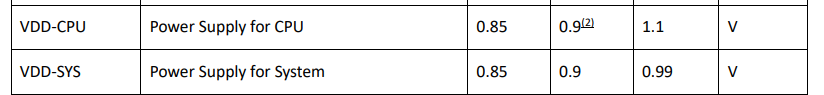

@yuhudnehao 这个问题表示SDIO通讯失败,有这些可能:

- 检查各路电源电压是否正确

- 检测模组的各个reset是否有被正确拉高,wl_reg_on, bt_rst

- 检查32K时钟是否正常

- 检查SDIO各个IO是否有上拉电阻

- 检查SDIO是否进行了扫卡

- 更换芯片或者样机进行测试

-

回复: 全志科技 D1s / T113-S3 驱动 8.8寸长条形瀚彩 HSD088 IPS 液晶,所有资料开源。发布在 其它全志芯片讨论区

&lcd0 { lcd_used = <1>; lcd_driver_name = "whycanpi_lcd_620"; lcd_backlight = <255>; lcd_if = <4>; lcd_x = <480>; lcd_y = <1920>; lcd_width = <52>; lcd_height = <52>; lcd_dclk_freq = <66>; lcd_pwm_used = <1>; lcd_pwm_ch = <7>; lcd_pwm_freq = <50000>; lcd_pwm_pol = <0>; lcd_pwm_max_limit = <255>; lcd_bright_curve_en = <0>; lcd_backlight = <255>; lcd_hbp = <60>; lcd_ht = <570>; lcd_hspw = <30>; lcd_vbp = <12>; lcd_vt = <1938>; lcd_vspw = <6>; lcd_dsi_if = <0>; lcd_dsi_lane = <4>; lcd_lvds_if = <0>; lcd_lvds_colordepth = <0>; lcd_lvds_mode = <0>; lcd_frm = <0>; lcd_hv_clk_phase = <0>; lcd_hv_sync_polarity= <0>; lcd_io_phase = <0x0000>; lcd_gamma_en = <0>; lcd_bright_curve_en = <0>; lcd_cmap_en = <0>; lcd_fsync_en = <0>; lcd_fsync_act_time = <1000>; lcd_fsync_dis_time = <1000>; lcd_fsync_pol = <0>; deu_mode = <0>; lcdgamma4iep = <22>; smart_color = <90>; lcd_gpio_0 = <&pio PD 20 GPIO_ACTIVE_HIGH>; pinctrl-0 = <&dsi4lane_pins_a>; pinctrl-1 = <&dsi4lane_pins_b>; } -

回复: 【哪吒开发板】Tina Linux SPI主从通信验证实录发布在 MR Series

@jaunenahy spi_dbi_enable 是使用dbi接口接屏幕,驱动挂载到dbi上了不兼容spidev

-

回复: 按键按下用万用表测出电平变化, 但是查看对应GPIO的value文件却没有变化发布在 其它全志芯片讨论区

按键可以用Linux内置的驱动gpio-keys,提供轮训中断等多种查询方式,而且直接对接了linux的event系统开发也很简单

-

回复: 【哪吒开发板】Tina Linux SPI主从通信验证实录发布在 MR Series

@jaunenahy 可以直接这样替换吗?我看了下好像没有这个时钟通路。如果需要低时钟可以打linux rt实时补丁然后软件模拟spi

-

回复: T113 modules insmod失败,并且什么提示也没有,modprobe也没用发布在 其它全志芯片讨论区

Tina Linux与百问网的Buildroot不一样,考虑是否因为是交叉编译编译器错误

dmesg -n 7 配置 loglevel 看看有没有报错

-

回复: wifi模块延迟高发布在 Wireless & Analog Series

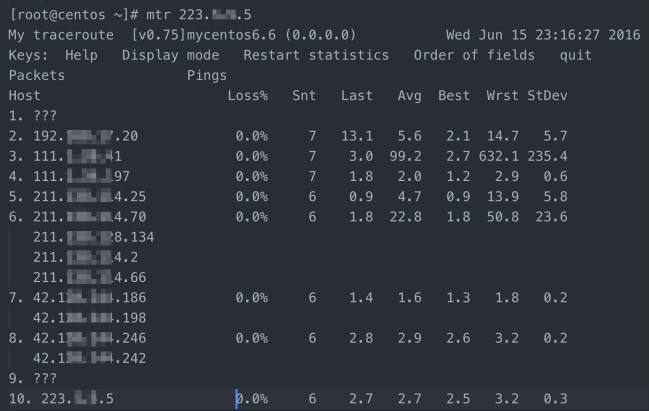

@nlj_moon 检查系统是否存在大量占用CPU时间的程序,也可以通过MTR等工具进行链路测试来判断问题来源。

1.MTR基本信息

MTR(My traceroute)是几乎所有Linux发行版本预装的网络测试工具,此工具也有对应的Windows版本,名称为WinMTR。

MTR工具将ping和traceroute命令的功能并入了同一个工具中,实现更强大的功能。

Linux版本的mtr命令默认发送ICMP数据包进行链路探测。可以通过“-u”参数来指定使用UDP数据包用于探测。

相对于traceroute命令只会做一次链路跟踪测试,mtr命令会对链路上的相关节点做持续探测并给出相应的统计信息。所以,mtr命令能避免节点波动对测试结果的影响,所以其测试结果更正确,建议优先使用。

2.MTR使用方法

在Linux系统上使用

用法说明mtr [-hvrctglspni46] [-help] [-version] [-report] [-report-cycles=COUNT] [-curses] [-gtk] [-raw] [-split] [-no-dns] [-address interface] [-psize=bytes/-s bytes] [-interval=SECONDS] HOSTNAME [PACKETSIZE]常见可选参数说明:

-r 或 -report:以报告模式显示输出。 -p 或 -split:将每次追踪的结果分别列出来。 -s 或 -psize:指定ping数据包的大小。 -n 或 -no-dns:不对IP地址做域名反解析。 -a 或 -address:设置发送数据包的IP地址。用于主机有多个IP时。 -4:只使用IPv4协议。 -6:只使用IPv6协议。 另外,也可以在mtr命令运行过程中,输入相应字母来快速切换模式。 ?或 h:显示帮助菜单。 d:切换显示模式。 n:切换启用或禁用DNS域名解析。 u:切换使用ICMP或UDP数据包进行探测。3.示例输出

默认配置下,返回结果中各数据列的说明如下。

第一列(Host):节点IP地址和域名。如前面所示,按n键可以切换显示。

第二列(Loss%):节点丢包率。

第三列(Snt):每秒发送数据包数。默认值是10,可以通过参数“-c”指定。

第四列(Last):最近一次的探测延迟值。

第五、六、七列(Avg、Best、Wrst):分别是探测延迟的平均值、最小值和最大值。

第八列(StDev):标准偏差。越大说明相应节点越不稳定。 -

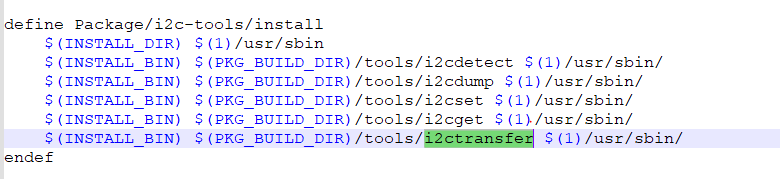

回复: 关于V853的i2c-tools-3.1.2怎么更换为i2c-tools-4.3呢?发布在 V Series

@fanfan 在 关于V853的i2c-tools-3.1.2怎么更换为i2c-tools-4.3呢? 中说:

i2ctranfer

tina 5.0亲测是有i2ctransfer的,而且Makefile里也有

可以试试把5.0的移植过去

-

回复: D1H-nezha-tina构建报错发布在 MR Series

@mc964203886 在 D1H-nezha-tina构建报错 中说:

from ./signal.h:52, from c-stack.c:49:c-stack.c:55:26: error: missing binary operator before token "("

55 | #elif HAVE_LIBSIGSEGV && SIGSTKSZ < 16384

|系统gcc版本过高,请使用gcc-7以下版本

-

回复: Ubuntu 22.04 编译报错 multiple definition of 'yylloc';发布在 V Series

打入以下补丁解决

From 11647f99b4de6bc460e106e876f72fc7af3e54a6 Mon Sep 17 00:00:00 2001 From: Dirk Mueller <dmueller@suse.com> Date: Tue, 14 Jan 2020 18:53:41 +0100 Subject: [PATCH] scripts/dtc: Remove redundant YYLOC global declaration commit e33a814e772cdc36436c8c188d8c42d019fda639 upstream. gcc 10 will default to -fno-common, which causes this error at link time: (.text+0x0): multiple definition of `yylloc'; dtc-lexer.lex.o (symbol from plugin):(.text+0x0): first defined here This is because both dtc-lexer as well as dtc-parser define the same global symbol yyloc. Before with -fcommon those were merged into one defintion. The proper solution would be to to mark this as "extern", however that leads to: dtc-lexer.l:26:16: error: redundant redeclaration of 'yylloc' [-Werror=redundant-decls] 26 | extern YYLTYPE yylloc; | ^~~~~~ In file included from dtc-lexer.l:24: dtc-parser.tab.h:127:16: note: previous declaration of 'yylloc' was here 127 | extern YYLTYPE yylloc; | ^~~~~~ cc1: all warnings being treated as errors which means the declaration is completely redundant and can just be dropped. Signed-off-by: Dirk Mueller <dmueller@suse.com> Signed-off-by: David Gibson <david@gibson.dropbear.id.au> [robh: cherry-pick from upstream] Cc: stable@vger.kernel.org Signed-off-by: Rob Herring <robh@kernel.org> [nc: Also apply to dtc-lexer.lex.c_shipped due to a lack of e039139be8c2, where dtc-lexer.l started being used] Signed-off-by: Nathan Chancellor <natechancellor@gmail.com> Signed-off-by: Greg Kroah-Hartman <gregkh@linuxfoundation.org> Change-Id: I7f299451e99aab09375883546e47505ec0937c26 --- scripts/dtc/dtc-lexer.l | 1 - scripts/dtc/dtc-lexer.lex.c_shipped | 1 - 2 files changed, 2 deletions(-) diff --git a/scripts/dtc/dtc-lexer.l b/scripts/dtc/dtc-lexer.l index c600603044f3..cf7707be43aa 100644 --- a/scripts/dtc/dtc-lexer.l +++ b/scripts/dtc/dtc-lexer.l @@ -38,7 +38,6 @@ LINECOMMENT "//".*\n #include "srcpos.h" #include "dtc-parser.tab.h" -YYLTYPE yylloc; extern bool treesource_error; /* CAUTION: this will stop working if we ever use yyless() or yyunput() */ diff --git a/scripts/dtc/dtc-lexer.lex.c_shipped b/scripts/dtc/dtc-lexer.lex.c_shipped index 2c862bc86ad0..e3663ce1af5d 100644 --- a/scripts/dtc/dtc-lexer.lex.c_shipped +++ b/scripts/dtc/dtc-lexer.lex.c_shipped @@ -631,7 +631,6 @@ char *yytext; #include "srcpos.h" #include "dtc-parser.tab.h" -YYLTYPE yylloc; extern bool treesource_error; /* CAUTION: this will stop working if we ever use yyless() or yyunput() */ -

回复: T507的SPI Flash设备,解析分区时出现错误,解析sunxi_gpt(GUID Partition Table)失败。发布在 其它全志芯片讨论区

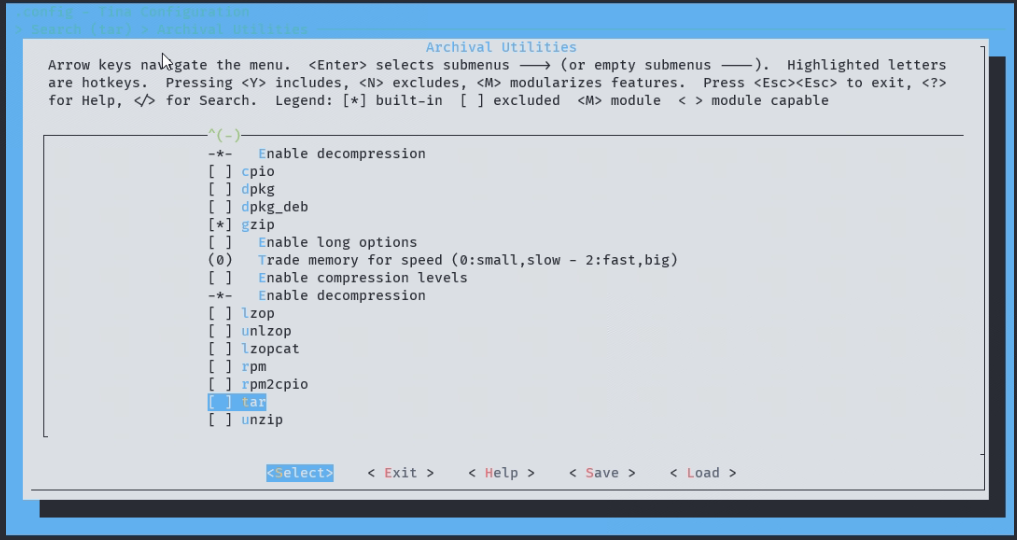

m25p80 是 NOR Flash,需要勾选mtd设备,spi设备驱动,如果不从 SPI Flash 启动需要手动格式化 NOR Flash,如果需要从 SPI Flash 启动需要配置mtd,jffs2这些

-

回复: D1-H的HiFi4 DSP怎么能使用起来?发布在 MR Series

@adaofu01 HIFI4 的DSP需要专用的编译器,这个编译器需要向Cadence 购买授权,也可以咨询全志FAE获得授权。目前暂无第三方编译器支持这个DSP。由于授权协议问题,需要连上授权服务器使用。

-

回复: 全志 DDR初始化 v3s发布在 其它全志芯片讨论区

DRAM寄存器

#define S3_DRAM_COM_BASE (0x01c62000) #define S3_DRAM_CTL_BASE (0x01c63000) #define MCTL_CR_BL8 (0x4 << 20) #define MCTL_CR_1T (0x1 << 19) #define MCTL_CR_2T (0x0 << 19) #define MCTL_CR_LPDDR3 (0x7 << 16) #define MCTL_CR_LPDDR2 (0x6 << 16) #define MCTL_CR_DDR3 (0x3 << 16) #define MCTL_CR_DDR2 (0x2 << 16) #define MCTL_CR_SEQUENTIAL (0x1 << 15) #define MCTL_CR_INTERLEAVED (0x0 << 15) #define MCTL_CR_32BIT (0x1 << 12) #define MCTL_CR_16BIT (0x0 << 12) #define MCTL_CR_BUS_WIDTH(x) ((x) == 32 ? MCTL_CR_32BIT : MCTL_CR_16BIT) #define MCTL_CR_PAGE_SIZE(x) ((gfls(x) - 4) << 8) #define MCTL_CR_ROW_BITS(x) (((x) - 1) << 4) #define MCTL_CR_EIGHT_BANKS (0x1 << 2) #define MCTL_CR_FOUR_BANKS (0x0 << 2) #define MCTL_CR_DUAL_RANK (0x1 << 0) #define MCTL_CR_SINGLE_RANK (0x0 << 0) #define DRAMTMG0_TWTP(x) ((x) << 24) #define DRAMTMG0_TFAW(x) ((x) << 16) #define DRAMTMG0_TRAS_MAX(x) ((x) << 8) #define DRAMTMG0_TRAS(x) ((x) << 0) #define DRAMTMG1_TXP(x) ((x) << 16) #define DRAMTMG1_TRTP(x) ((x) << 8) #define DRAMTMG1_TRC(x) ((x) << 0) #define DRAMTMG2_TCWL(x) ((x) << 24) #define DRAMTMG2_TCL(x) ((x) << 16) #define DRAMTMG2_TRD2WR(x) ((x) << 8) #define DRAMTMG2_TWR2RD(x) ((x) << 0) #define DRAMTMG3_TMRW(x) ((x) << 16) #define DRAMTMG3_TMRD(x) ((x) << 12) #define DRAMTMG3_TMOD(x) ((x) << 0) #define DRAMTMG4_TRCD(x) ((x) << 24) #define DRAMTMG4_TCCD(x) ((x) << 16) #define DRAMTMG4_TRRD(x) ((x) << 8) #define DRAMTMG4_TRP(x) ((x) << 0) #define DRAMTMG5_TCKSRX(x) ((x) << 24) #define DRAMTMG5_TCKSRE(x) ((x) << 16) #define DRAMTMG5_TCKESR(x) ((x) << 8) #define DRAMTMG5_TCKE(x) ((x) << 0) #define PTR3_TDINIT1(x) ((x) << 20) #define PTR3_TDINIT0(x) ((x) << 0) #define PTR4_TDINIT3(x) ((x) << 20) #define PTR4_TDINIT2(x) ((x) << 0) #define RFSHTMG_TREFI(x) ((x) << 16) #define RFSHTMG_TRFC(x) ((x) << 0) #define PIR_CLRSR (0x1 << 27) /* Clear status registers */ #define PIR_QSGATE (0x1 << 10) /* Read DQS gate training */ #define PIR_DRAMINIT (0x1 << 8) /* DRAM initialization */ #define PIR_DRAMRST (0x1 << 7) /* DRAM reset */ #define PIR_PHYRST (0x1 << 6) /* PHY reset */ #define PIR_DCAL (0x1 << 5) /* DDL calibration */ #define PIR_PLLINIT (0x1 << 4) /* PLL initialization */ #define PIR_ZCAL (0x1 << 1) /* ZQ calibration */ #define PIR_INIT (0x1 << 0) /* PHY initialization trigger */ #define PGSR_INIT_DONE (0x1 << 0) /* PHY init done */ #define ZQCR_PWRDOWN (0x1 << 31) /* ZQ power down */ #define DATX_IOCR_DQ(x) (x) #define DATX_IOCR_DM (8) #define DATX_IOCR_DQS (9) #define DATX_IOCR_DQSN (10) #define DATX_IOCR_WRITE_DELAY(x) ((x) << 8) #define DATX_IOCR_READ_DELAY(x) ((x) << 0)时钟寄存器

#define S3_CCU_BASE (0x01c20000) #define CCU_PLL_CPU_CTRL (0x000) #define CCU_PLL_AUDIO_CTRL (0x008) #define CCU_PLL_VIDEO_CTRL (0x010) #define CCU_PLL_VE_CTRL (0x018) #define CCU_PLL_DDR0_CTRL (0x020) #define CCU_PLL_PERIPH0_CTRL (0x028) #define CCU_PLL_ISP_CTRL (0x02c) #define CCU_PLL_PERIPH1_CTRL (0x044) #define CCU_PLL_DDR1_CTRL (0x04c) #define CCU_CPU_AXI_CFG (0x050) #define CCU_AHB_APB0_CFG (0x054) #define CCU_APB1_CFG (0x058) #define CCU_AHB2_CFG (0x05c) #define CCU_BUS_CLK_GATE0 (0x060) #define CCU_BUS_CLK_GATE1 (0x064) #define CCU_BUS_CLK_GATE2 (0x068) #define CCU_BUS_CLK_GATE3 (0x06c) #define CCU_BUS_CLK_GATE4 (0x070) #define CCU_SDMMC0_CLK (0x088) #define CCU_SDMMC1_CLK (0x08c) #define CCU_SDMMC2_CLK (0x090) #define CCU_CE_CLK (0x09c) #define CCU_SPI0_CLK (0x0a0) #define CCU_USBPHY_CFG (0x0cc) #define CCU_DRAM_CFG (0x0f4) #define CCU_PLL_DDR1_CFG (0x0f8) #define CCU_MBUS_RST (0x0fc) #define CCU_DRAM_CLK_GATE (0x100) #define CCU_TCON_CLK (0x118) #define CCU_CSI_MISC_CLK (0x130) #define CCU_CSI_CLK (0x134) #define CCU_VE_CLK (0x13c) #define CCU_AC_DIG_CLK (0x140) #define CCU_AVS_CLK (0x144) #define CCU_MBUS_CLK (0x15c) #define CCU_MIPI_CSI_CLK (0x16c) #define CCU_PLL_STABLE_TIME0 (0x200) #define CCU_PLL_STABLE_TIME1 (0x204) #define CCU_PLL_CPU_BIAS (0x220) #define CCU_PLL_AUDIO_BIAS (0x224) #define CCU_PLL_VIDEO_BIAS (0x228) #define CCU_PLL_VE_BIAS (0x22c) #define CCU_PLL_DDR0_BIAS (0x230) #define CCU_PLL_PERIPH0_BIAS (0x234) #define CCU_PLL_ISP_BIAS (0x238) #define CCU_PLL_PERIPH1_BIAS (0x244) #define CCU_PLL_DDR1_BIAS (0x24C) #define CCU_PLL_CPU_TUN (0x250) #define CCU_PLL_DDR0_TUN (0x260) #define CCU_PLL_CPU_PAT (0x280) #define CCU_PLL_AUDIO_PAT (0x284) #define CCU_PLL_VIDEO_PAT (0x288) #define CCU_PLL_VE_PAT (0x28c) #define CCU_PLL_DDR0_PAT (0x290) #define CCU_PLL_ISP_PAT (0x298) #define CCU_PLL_PERIPH1_PAT (0x2a4) #define CCU_PLL_DDR1_PAT0 (0x2ac) #define CCU_PLL_DDR1_PAT1 (0x2b0) #define CCU_BUS_SOFT_RST0 (0x2c0) #define CCU_BUS_SOFT_RST1 (0x2c4) #define CCU_BUS_SOFT_RST2 (0x2c8) #define CCU_BUS_SOFT_RST3 (0x2d0) #define CCU_BUS_SOFT_RST4 (0x2d8) #define CCU_PS_CTRL (0x300) #define CCU_PS_CNT (0x304)驱动

#include <reg-ccu.h> #include <reg-dram.h> #define CONFIG_DRAM_BASE (0x40000000) #define CONFIG_DRAM_CLK (360) #define CONFIG_DRAM_ZQ (14779) #define clrbits_le32(addr, clear) \ write32(((virtual_addr_t)(addr)), read32(((virtual_addr_t)(addr))) & ~(clear)) #define setbits_le32(addr, set) \ write32(((virtual_addr_t)(addr)), read32(((virtual_addr_t)(addr))) | (set)) #define clrsetbits_le32(addr, clear, set) \ write32(((virtual_addr_t)(addr)), (read32(((virtual_addr_t)(addr))) & ~(clear)) | (set)) #define DIV_ROUND_UP(n, d) (((n) + (d) - 1) / (d)) #define REPEAT_BYTE(x) ((~0ul / 0xff) * (x)) struct s3_dram_com_reg_t { u32_t cr; /* 0x00 control register */ u8_t res0[0xc]; /* 0x04 */ u32_t mcr[16][2]; /* 0x10 */ u32_t bwcr; /* 0x90 bandwidth control register */ u32_t maer; /* 0x94 master enable register */ u32_t mapr; /* 0x98 master priority register */ u32_t mcgcr; /* 0x9c */ u32_t cpu_bwcr; /* 0xa0 */ u32_t gpu_bwcr; /* 0xa4 */ u32_t ve_bwcr; /* 0xa8 */ u32_t disp_bwcr; /* 0xac */ u32_t other_bwcr; /* 0xb0 */ u32_t total_bwcr; /* 0xb4 */ u8_t res1[0x8]; /* 0xb8 */ u32_t swonr; /* 0xc0 */ u32_t swoffr; /* 0xc4 */ u8_t res2[0x8]; /* 0xc8 */ u32_t cccr; /* 0xd0 */ u8_t res3[0x72c]; /* 0xd4 */ u32_t protect; /* 0x800 */ }; struct s3_dram_ctl_reg_t { u32_t pir; /* 0x00 PHY initialization register */ u32_t pwrctl; /* 0x04 */ u32_t mrctrl; /* 0x08 */ u32_t clken; /* 0x0c */ u32_t pgsr[2]; /* 0x10 PHY general status registers */ u32_t statr; /* 0x18 */ u8_t res1[0x14]; /* 0x1c */ u32_t mr[4]; /* 0x30 mode registers */ u32_t pllgcr; /* 0x40 */ u32_t ptr[5]; /* 0x44 PHY timing registers */ u32_t dramtmg[9]; /* 0x58 DRAM timing registers */ u32_t odtcfg; /* 0x7c */ u32_t pitmg[2]; /* 0x80 PHY interface timing registers */ u8_t res2[0x4]; /* 0x88 */ u32_t rfshctl0; /* 0x8c */ u32_t rfshtmg; /* 0x90 refresh timing */ u32_t rfshctl1; /* 0x94 */ u32_t pwrtmg; /* 0x98 */ u8_t res3[0x20]; /* 0x9c */ u32_t dqsgmr; /* 0xbc */ u32_t dtcr; /* 0xc0 */ u32_t dtar[4]; /* 0xc4 */ u32_t dtdr[2]; /* 0xd4 */ u32_t dtmr[2]; /* 0xdc */ u32_t dtbmr; /* 0xe4 */ u32_t catr[2]; /* 0xe8 */ u32_t dtedr[2]; /* 0xf0 */ u8_t res4[0x8]; /* 0xf8 */ u32_t pgcr[4]; /* 0x100 PHY general configuration registers */ u32_t iovcr[2]; /* 0x110 */ u32_t dqsdr; /* 0x118 */ u32_t dxccr; /* 0x11c */ u32_t odtmap; /* 0x120 */ u32_t zqctl[2]; /* 0x124 */ u8_t res6[0x14]; /* 0x12c */ u32_t zqcr; /* 0x140 ZQ control register */ u32_t zqsr; /* 0x144 ZQ status register */ u32_t zqdr[3]; /* 0x148 ZQ data registers */ u8_t res7[0x6c]; /* 0x154 */ u32_t sched; /* 0x1c0 */ u32_t perfhpr[2]; /* 0x1c4 */ u32_t perflpr[2]; /* 0x1cc */ u32_t perfwr[2]; /* 0x1d4 */ u8_t res8[0x2c]; /* 0x1dc */ u32_t aciocr; /* 0x208 */ u8_t res9[0xf4]; /* 0x20c */ struct { /* 0x300 DATX8 modules*/ u32_t mdlr; /* 0x00 */ u32_t lcdlr[3]; /* 0x04 */ u32_t iocr[11]; /* 0x10 IO configuration register */ u32_t bdlr6; /* 0x3c */ u32_t gtr; /* 0x40 */ u32_t gcr; /* 0x44 */ u32_t gsr[3]; /* 0x48 */ u8_t res0[0x2c];/* 0x54 */ } datx[4]; u8_t res10[0x388]; /* 0x500 */ u32_t upd2; /* 0x888 */ }; struct dram_para_t { u32_t read_delays; u32_t write_delays; u16_t page_size; u8_t bus_width; u8_t dual_rank; u8_t row_bits; u8_t bank_bits; }; static inline void sdelay(int loops) { __asm__ __volatile__ ("1:\n" "subs %0, %1, #1\n" "bne 1b":"=r" (loops):"0"(loops)); } static inline int gfls(int x) { int r = 32; if(!x) return 0; if(!(x & 0xffff0000u)) { x <<= 16; r -= 16; } if(!(x & 0xff000000u)) { x <<= 8; r -= 8; } if(!(x & 0xf0000000u)) { x <<= 4; r -= 4; } if(!(x & 0xc0000000u)) { x <<= 2; r -= 2; } if(!(x & 0x80000000u)) { x <<= 1; r -= 1; } return r; } static inline int ns_to_t(int ns) { unsigned int freq = CONFIG_DRAM_CLK / 2; return DIV_ROUND_UP(freq * ns, 1000); } static u32_t bin_to_mgray(int val) { u8_t table[32]; table[0] = 0x00; table[1] = 0x01; table[2] = 0x02; table[3] = 0x03; table[4] = 0x06; table[5] = 0x07; table[6] = 0x04; table[7] = 0x05; table[8] = 0x0c; table[9] = 0x0d; table[10] = 0x0e; table[11] = 0x0f; table[12] = 0x0a; table[13] = 0x0b; table[14] = 0x08; table[15] = 0x09; table[16] = 0x18; table[17] = 0x19; table[18] = 0x1a; table[19] = 0x1b; table[20] = 0x1e; table[21] = 0x1f; table[22] = 0x1c; table[23] = 0x1d; table[24] = 0x14; table[25] = 0x15; table[26] = 0x16; table[27] = 0x17; table[28] = 0x12; table[29] = 0x13; table[30] = 0x10; table[31] = 0x11; return table[clamp(val, 0, 31)]; } static int mgray_to_bin(u32_t val) { u8_t table[32]; table[0] = 0x00; table[1] = 0x01; table[2] = 0x02; table[3] = 0x03; table[4] = 0x06; table[5] = 0x07; table[6] = 0x04; table[7] = 0x05; table[8] = 0x0e; table[9] = 0x0f; table[10] = 0x0c; table[11] = 0x0d; table[12] = 0x08; table[13] = 0x09; table[14] = 0x0a; table[15] = 0x0b; table[16] = 0x1e; table[17] = 0x1f; table[18] = 0x1c; table[19] = 0x1d; table[20] = 0x18; table[21] = 0x19; table[22] = 0x1a; table[23] = 0x1b; table[24] = 0x10; table[25] = 0x11; table[26] = 0x12; table[27] = 0x13; table[28] = 0x16; table[29] = 0x17; table[30] = 0x14; table[31] = 0x15; return table[val & 0x1f]; } static void clock_set_pll_ddr(u32_t clk) { int n = 32; int k = 1; int m = 2; u32_t val; /* ddr pll rate = 24000000 * n * k / m */ if(clk > 24000000 * k * n / m) { m = 1; if(clk > 24000000 * k * n / m) { k = 2; } } val = (0x1 << 31); val |= (0x0 << 24); val |= (0x1 << 20); val |= ((((clk / (24000000 * k / m)) - 1) & 0x1f) << 8); val |= (((k - 1) & 0x3) << 4); val |= (((m - 1) & 0x3) << 0); write32(S3_CCU_BASE + CCU_PLL_DDR0_CTRL, val); sdelay(5500); } static void mctl_await_completion(u32_t * reg, u32_t mask, u32_t val) { int timeout = 0; while((read32((virtual_addr_t)reg) & mask) != val) { if(timeout++ > 10000) break; } } static int mctl_mem_matches(u32_t offset) { write32(CONFIG_DRAM_BASE, 0); write32(CONFIG_DRAM_BASE + offset, 0xaa55aa55); __asm__ __volatile__ ("dsb" : : : "memory"); return (read32(CONFIG_DRAM_BASE) == read32(CONFIG_DRAM_BASE + offset)) ? 1 : 0; } static void mctl_phy_init(u32_t val) { struct s3_dram_ctl_reg_t * ctl = (struct s3_dram_ctl_reg_t *)S3_DRAM_CTL_BASE; write32((virtual_addr_t)&ctl->pir, val | PIR_INIT); mctl_await_completion(&ctl->pgsr[0], PGSR_INIT_DONE, 0x1); } static void mctl_dq_delay(u32_t read, u32_t write) { struct s3_dram_ctl_reg_t * ctl = (struct s3_dram_ctl_reg_t *)S3_DRAM_CTL_BASE; int i, j; u32_t val; for(i = 0; i < 4; i++) { val = DATX_IOCR_WRITE_DELAY((write >> (i * 4)) & 0xf) | DATX_IOCR_READ_DELAY(((read >> (i * 4)) & 0xf) * 2); for(j = DATX_IOCR_DQ(0); j <= DATX_IOCR_DM; j++) write32((virtual_addr_t)&ctl->datx[i].iocr[j], val); } clrbits_le32(&ctl->pgcr[0], 1 << 26); for(i = 0; i < 4; i++) { val = DATX_IOCR_WRITE_DELAY((write >> (16 + i * 4)) & 0xf) | DATX_IOCR_READ_DELAY((read >> (16 + i * 4)) & 0xf); write32((virtual_addr_t)&ctl->datx[i].iocr[DATX_IOCR_DQS], val); write32((virtual_addr_t)&ctl->datx[i].iocr[DATX_IOCR_DQSN], val); } setbits_le32(&ctl->pgcr[0], 1 << 26); sdelay(1); } static void mctl_set_master_priority(void) { struct s3_dram_com_reg_t * com = (struct s3_dram_com_reg_t *)S3_DRAM_COM_BASE; write32((virtual_addr_t)&com->bwcr, 0x00010190); write32((virtual_addr_t)&com->mapr, 0x00000001); write32((virtual_addr_t)&com->mcr[0][0], 0x0200000d); write32((virtual_addr_t)&com->mcr[0][1], 0x00800100); write32((virtual_addr_t)&com->mcr[1][0], 0x06000009); write32((virtual_addr_t)&com->mcr[1][1], 0x01000400); write32((virtual_addr_t)&com->mcr[2][0], 0x0200000d); write32((virtual_addr_t)&com->mcr[2][1], 0x00600100); write32((virtual_addr_t)&com->mcr[3][0], 0x0100000d); write32((virtual_addr_t)&com->mcr[3][1], 0x00200080); write32((virtual_addr_t)&com->mcr[4][0], 0x07000009); write32((virtual_addr_t)&com->mcr[4][1], 0x01000640); write32((virtual_addr_t)&com->mcr[5][0], 0x0100000d); write32((virtual_addr_t)&com->mcr[5][1], 0x00200080); write32((virtual_addr_t)&com->mcr[6][0], 0x01000009); write32((virtual_addr_t)&com->mcr[6][1], 0x00400080); write32((virtual_addr_t)&com->mcr[7][0], 0x0100000d); write32((virtual_addr_t)&com->mcr[7][1], 0x00400080); write32((virtual_addr_t)&com->mcr[8][0], 0x0100000d); write32((virtual_addr_t)&com->mcr[8][1], 0x00400080); write32((virtual_addr_t)&com->mcr[9][0], 0x04000009); write32((virtual_addr_t)&com->mcr[9][1], 0x00400100); write32((virtual_addr_t)&com->mcr[10][0], 0x2000030d); write32((virtual_addr_t)&com->mcr[10][1], 0x04001800); write32((virtual_addr_t)&com->mcr[11][0], 0x04000009); write32((virtual_addr_t)&com->mcr[11][1], 0x00400120); } static void mctl_set_timing_params(struct dram_para_t * para) { struct s3_dram_ctl_reg_t * ctl = (struct s3_dram_ctl_reg_t *)S3_DRAM_CTL_BASE; u8_t tccd = 2; u8_t tfaw = ns_to_t(50); u8_t trrd = max(ns_to_t(10), 4); u8_t trcd = ns_to_t(15); u8_t trc = ns_to_t(53); u8_t txp = max(ns_to_t(8), 3); u8_t twtr = max(ns_to_t(8), 4); u8_t trtp = max(ns_to_t(8), 4); u8_t twr = max(ns_to_t(15), 3); u8_t trp = ns_to_t(15); u8_t tras = ns_to_t(38); u16_t trefi = ns_to_t(7800) / 32; u16_t trfc = ns_to_t(350); u8_t tmrw = 0; u8_t tmrd = 4; u8_t tmod = 12; u8_t tcke = 3; u8_t tcksrx = 5; u8_t tcksre = 5; u8_t tckesr = 4; u8_t trasmax = 24; u8_t tcl = 6; /* CL 12 */ u8_t tcwl = 4; /* CWL 8 */ u8_t t_rdata_en = 4; u8_t wr_latency = 2; u32_t tdinit0 = (500 * CONFIG_DRAM_CLK) + 1; /* 500us */ u32_t tdinit1 = (360 * CONFIG_DRAM_CLK) / 1000 + 1; /* 360ns */ u32_t tdinit2 = (200 * CONFIG_DRAM_CLK) + 1; /* 200us */ u32_t tdinit3 = (1 * CONFIG_DRAM_CLK) + 1; /* 1us */ u8_t twtp = tcwl + 2 + twr; /* WL + BL / 2 + tWR */ u8_t twr2rd = tcwl + 2 + twtr; /* WL + BL / 2 + tWTR */ u8_t trd2wr = tcl + 2 + 1 - tcwl; /* RL + BL / 2 + 2 - WL */ write32((virtual_addr_t)&ctl->mr[0], 0x1c70); /* CL=11, WR=12 */ write32((virtual_addr_t)&ctl->mr[1], 0x40); write32((virtual_addr_t)&ctl->mr[2], 0x18); /* CWL=8 */ write32((virtual_addr_t)&ctl->mr[3], 0x0); /* Set DRAM timing */ write32((virtual_addr_t)&ctl->dramtmg[0], DRAMTMG0_TWTP(twtp) | DRAMTMG0_TFAW(tfaw) | DRAMTMG0_TRAS_MAX(trasmax) | DRAMTMG0_TRAS(tras)); write32((virtual_addr_t)&ctl->dramtmg[1], DRAMTMG1_TXP(txp) | DRAMTMG1_TRTP(trtp) | DRAMTMG1_TRC(trc)); write32((virtual_addr_t)&ctl->dramtmg[2], DRAMTMG2_TCWL(tcwl) | DRAMTMG2_TCL(tcl) | DRAMTMG2_TRD2WR(trd2wr) | DRAMTMG2_TWR2RD(twr2rd)); write32((virtual_addr_t)&ctl->dramtmg[3], DRAMTMG3_TMRW(tmrw) | DRAMTMG3_TMRD(tmrd) | DRAMTMG3_TMOD(tmod)); write32((virtual_addr_t)&ctl->dramtmg[4], DRAMTMG4_TRCD(trcd) | DRAMTMG4_TCCD(tccd) | DRAMTMG4_TRRD(trrd) | DRAMTMG4_TRP(trp)); write32((virtual_addr_t)&ctl->dramtmg[5], DRAMTMG5_TCKSRX(tcksrx) | DRAMTMG5_TCKSRE(tcksre) | DRAMTMG5_TCKESR(tckesr) | DRAMTMG5_TCKE(tcke)); /* Set two rank timing */ clrsetbits_le32(&ctl->dramtmg[8], (0xff << 8) | (0xff << 0), (0x66 << 8) | (0x10 << 0)); /* Set PHY interface timing, write latency and read latency configure */ write32((virtual_addr_t)&ctl->pitmg[0], (0x2 << 24) | (t_rdata_en << 16) | (0x1 << 8) | (wr_latency << 0)); /* Set PHY timing, PTR0-2 use default */ write32((virtual_addr_t)&ctl->ptr[3], PTR3_TDINIT0(tdinit0) | PTR3_TDINIT1(tdinit1)); write32((virtual_addr_t)&ctl->ptr[4], PTR4_TDINIT2(tdinit2) | PTR4_TDINIT3(tdinit3)); /* Set refresh timing */ write32((virtual_addr_t)&ctl->rfshtmg, RFSHTMG_TREFI(trefi) | RFSHTMG_TRFC(trfc)); } static void mctl_zq_calibration(struct dram_para_t * para) { struct s3_dram_ctl_reg_t * ctl = (struct s3_dram_ctl_reg_t *)S3_DRAM_CTL_BASE; u16_t zq_val[6]; u32_t val; u8_t zq; int i; if(((read32(0x01c00000 + 0x24) & 0xff) == 0) && ((read32(0x01c00000 + 0xf0) & 0x1) == 0)) { clrsetbits_le32(&ctl->zqcr, 0xffff, CONFIG_DRAM_ZQ & 0xffff); write32((virtual_addr_t)&ctl->pir, PIR_CLRSR); mctl_phy_init(PIR_ZCAL); val = read32((virtual_addr_t)&ctl->zqdr[0]); val &= (0x1f << 16) | (0x1f << 0); val |= val << 8; write32((virtual_addr_t)&ctl->zqdr[0], val); val = read32((virtual_addr_t)&ctl->zqdr[1]); val &= (0x1f << 16) | (0x1f << 0); val |= val << 8; write32((virtual_addr_t)&ctl->zqdr[1], val); write32((virtual_addr_t)&ctl->zqdr[2], val); } else { write32((virtual_addr_t)&ctl->zqdr[2], 0x0a0a0a0a); for(i = 0; i < 6; i++) { zq = (CONFIG_DRAM_ZQ >> (i * 4)) & 0xf; write32((virtual_addr_t)&ctl->zqcr, (zq << 20) | (zq << 16) | (zq << 12) | (zq << 8) | (zq << 4) | (zq << 0)); write32((virtual_addr_t)&ctl->pir, PIR_CLRSR); mctl_phy_init(PIR_ZCAL); zq_val[i] = read32((virtual_addr_t)&ctl->zqdr[0]) & 0xff; write32((virtual_addr_t)&ctl->zqdr[2], REPEAT_BYTE(zq_val[i])); write32((virtual_addr_t)&ctl->pir, PIR_CLRSR); mctl_phy_init(PIR_ZCAL); val = read32((virtual_addr_t)&ctl->zqdr[0]) >> 24; zq_val[i] |= bin_to_mgray(mgray_to_bin(val) - 1) << 8; } write32((virtual_addr_t)&ctl->zqdr[0], (zq_val[1] << 16) | zq_val[0]); write32((virtual_addr_t)&ctl->zqdr[1], (zq_val[3] << 16) | zq_val[2]); write32((virtual_addr_t)&ctl->zqdr[2], (zq_val[5] << 16) | zq_val[4]); } } static void mctl_set_cr(struct dram_para_t * para) { struct s3_dram_com_reg_t * com = (struct s3_dram_com_reg_t *)S3_DRAM_COM_BASE; write32((virtual_addr_t)&com->cr, MCTL_CR_BL8 | MCTL_CR_2T | MCTL_CR_DDR3 | MCTL_CR_EIGHT_BANKS | MCTL_CR_BUS_WIDTH(para->bus_width) | MCTL_CR_INTERLEAVED | (para->dual_rank ? MCTL_CR_DUAL_RANK : MCTL_CR_SINGLE_RANK) | MCTL_CR_PAGE_SIZE(para->page_size) | MCTL_CR_ROW_BITS(para->row_bits)); } static void mctl_sys_init(struct dram_para_t * para) { struct s3_dram_ctl_reg_t * ctl = (struct s3_dram_ctl_reg_t *)S3_DRAM_CTL_BASE; u32_t val; val = read32(S3_CCU_BASE + CCU_MBUS_CLK); val &= ~(0x1 << 31); write32(S3_CCU_BASE + CCU_MBUS_CLK, val); val = read32(S3_CCU_BASE + CCU_MBUS_RST); val &= ~(0x1 << 31); write32(S3_CCU_BASE + CCU_MBUS_RST, val); val = read32(S3_CCU_BASE + CCU_BUS_CLK_GATE0); val &= ~(0x1 << 14); write32(S3_CCU_BASE + CCU_BUS_CLK_GATE0, val); val = read32(S3_CCU_BASE + CCU_BUS_SOFT_RST0); val &= ~(0x1 << 14); write32(S3_CCU_BASE + CCU_BUS_SOFT_RST0, val); val = read32(S3_CCU_BASE + CCU_PLL_DDR0_CTRL); val &= ~(0x1 << 31); write32(S3_CCU_BASE + CCU_PLL_DDR0_CTRL, val); sdelay(10); val = read32(S3_CCU_BASE + CCU_DRAM_CLK_GATE); val &= ~(0x1 << 31); write32(S3_CCU_BASE + CCU_DRAM_CLK_GATE, val); sdelay(1000); clock_set_pll_ddr(CONFIG_DRAM_CLK * 2 * 1000000); val = read32(S3_CCU_BASE + CCU_DRAM_CFG); val &= ~(0xf << 0); val &= ~(0x3 << 20); val |= ((1 - 1) << 0); val |= (0x0 << 20); val |= (0x1 << 16); write32(S3_CCU_BASE + CCU_DRAM_CFG, val); mctl_await_completion((u32_t *)(S3_CCU_BASE + CCU_DRAM_CFG), 0x1 << 16, 0); val = read32(S3_CCU_BASE + CCU_BUS_SOFT_RST0); val |= (0x1 << 14); write32(S3_CCU_BASE + CCU_BUS_SOFT_RST0, val); val = read32(S3_CCU_BASE + CCU_BUS_CLK_GATE0); val |= (0x1 << 14); write32(S3_CCU_BASE + CCU_BUS_CLK_GATE0, val); val = read32(S3_CCU_BASE + CCU_MBUS_RST); val |= (0x1 << 31); write32(S3_CCU_BASE + CCU_MBUS_RST, val); val = read32(S3_CCU_BASE + CCU_MBUS_CLK); val |= (0x1 << 31); write32(S3_CCU_BASE + CCU_MBUS_CLK, val); val = read32(S3_CCU_BASE + CCU_DRAM_CFG); val |= (0x1 << 31); write32(S3_CCU_BASE + CCU_DRAM_CFG, val); sdelay(10); write32((virtual_addr_t)&ctl->clken, 0xc00e); sdelay(500); } static int mctl_channel_init(struct dram_para_t * para) { struct s3_dram_com_reg_t * com = (struct s3_dram_com_reg_t *)S3_DRAM_COM_BASE; struct s3_dram_ctl_reg_t * ctl = (struct s3_dram_ctl_reg_t *)S3_DRAM_CTL_BASE; int i; mctl_set_cr(para); mctl_set_timing_params(para); mctl_set_master_priority(); clrbits_le32(&ctl->pgcr[0], (1 << 30) | 0x3f); clrsetbits_le32(&ctl->pgcr[1], 1 << 24, 1 << 26); write32((virtual_addr_t)&com->protect, 0x94be6fa3); sdelay(100); clrsetbits_le32(&ctl->upd2, 0xfff << 16, 0x50 << 16); write32((virtual_addr_t)&com->protect, 0x0); sdelay(100); for(i = 0; i < 4; i++) clrsetbits_le32(&ctl->datx[i].gcr, (0x3 << 4) | (0x1 << 1) | (0x3 << 2) | (0x3 << 12) | (0x3 << 14), 0x20); setbits_le32(&ctl->aciocr, 0x1 << 1); setbits_le32(&ctl->pgcr[2], 0x3 << 6); clrbits_le32(&ctl->pgcr[0], (0x3 << 14) | (0x3 << 12)); clrsetbits_le32(&ctl->pgcr[2], (0x3 << 10) | (0x3 << 8), (0x1 << 10) | (0x2 << 8)); if(para->bus_width != 32) { write32((virtual_addr_t)&ctl->datx[2].gcr, 0x0); write32((virtual_addr_t)&ctl->datx[3].gcr, 0x0); } clrsetbits_le32(&ctl->dtcr, 0xf << 24, (para->dual_rank ? 0x3 : 0x1) << 24); if(para->read_delays || para->write_delays) { mctl_dq_delay(para->read_delays, para->write_delays); sdelay(50); } mctl_zq_calibration(para); mctl_phy_init(PIR_PLLINIT | PIR_DCAL | PIR_PHYRST | PIR_DRAMRST | PIR_DRAMINIT | PIR_QSGATE); if(read32((virtual_addr_t)&ctl->pgsr[0]) & (0xfe << 20)) { if(((read32((virtual_addr_t)&ctl->datx[0].gsr[0]) >> 24) & 0x2) || ((read32((virtual_addr_t)&ctl->datx[1].gsr[0]) >> 24) & 0x2)) { clrsetbits_le32(&ctl->dtcr, 0xf << 24, 0x1 << 24); para->dual_rank = 0; } if(((read32((virtual_addr_t)&ctl->datx[2].gsr[0]) >> 24) & 0x1) || ((read32((virtual_addr_t)&ctl->datx[3].gsr[0]) >> 24) & 0x1)) { write32((virtual_addr_t)&ctl->datx[2].gcr, 0x0); write32((virtual_addr_t)&ctl->datx[3].gcr, 0x0); para->bus_width = 16; } mctl_set_cr(para); sdelay(20); mctl_phy_init(PIR_QSGATE); if(read32((virtual_addr_t)&ctl->pgsr[0]) & (0xfe << 20)) return 1; } mctl_await_completion(&ctl->statr, 0x1, 0x1); setbits_le32(&ctl->rfshctl0, 0x1 << 31); sdelay(10); clrbits_le32(&ctl->rfshctl0, 0x1 << 31); sdelay(10); write32((virtual_addr_t)&ctl->pgcr[3], 0x00aa0060); setbits_le32(&ctl->zqcr, ZQCR_PWRDOWN); write32((virtual_addr_t)&com->maer, 0xffffffff); return 0; } static void mctl_auto_detect_dram_size(struct dram_para_t * para) { para->page_size = 512; para->row_bits = 16; para->bank_bits = 2; mctl_set_cr(para); for(para->row_bits = 11; para->row_bits < 16; para->row_bits++) { if(mctl_mem_matches((1 << (para->row_bits + para->bank_bits)) * para->page_size)) break; } para->bank_bits = 3; mctl_set_cr(para); for(para->bank_bits = 2; para->bank_bits < 3; para->bank_bits++) { if(mctl_mem_matches((1 << para->bank_bits) * para->page_size)) break; } para->page_size = 8192; mctl_set_cr(para); for(para->page_size = 512; para->page_size < 8192; para->page_size *= 2) { if(mctl_mem_matches(para->page_size)) break; } } void sys_dram_init(void) { struct s3_dram_com_reg_t * com = (struct s3_dram_com_reg_t *)S3_DRAM_COM_BASE; struct s3_dram_ctl_reg_t * ctl = (struct s3_dram_ctl_reg_t *)S3_DRAM_CTL_BASE; struct dram_para_t para = { .read_delays = 0x00007979, .write_delays = 0x6aaa0000, .dual_rank = 0, .bus_width = 32, .row_bits = 15, .bank_bits = 3, .page_size = 4096, }; u32_t * dsz = (void *)0x00000020; if(dsz[0] != 0) return; mctl_sys_init(¶); if(mctl_channel_init(¶)) { dsz[0] = 0; return; } if(para.dual_rank) write32((virtual_addr_t)&ctl->odtmap, 0x00000303); else write32((virtual_addr_t)&ctl->odtmap, 0x00000201); sdelay(1); write32((virtual_addr_t)&ctl->odtcfg, 0x0c000400); setbits_le32(&com->cccr, 1 << 31); sdelay(10); mctl_auto_detect_dram_size(¶); mctl_set_cr(¶); dsz[0] = (1UL << (para.row_bits + para.bank_bits)) * para.page_size * (para.dual_rank ? 2 : 1); }代码都有,咋这么喜欢自己从头造轮子呢?DRAM驱动也没这么容易写的吧。

-

回复: V853适配4.3寸屏lcd_width = <95>; lcd_height = <54>;显示出现问题发布在 V Series

这个是计算PPI使用的,是与分辨率成对应关系,由于屏幕不是完美的整数大小使用设置的时候如果出现分辨率与屏幕大小出现较大出入则会导致PPI计算错误显示异常。所以一般按照分辨率来设置的,例如800x600屏幕,实际大小为95x53,则设置80,60即可

-

回复: YuzuKi X 100ask V851s使用的rtsp传输实时预览摄像头数据发布在 V Series

@sergpenshin SDK is updated, and this command is deprecated. try to use this stand alone package for build https://github.com/YuzukiHD/Yuzukilizard/tree/master/Software/sunxi-mpp

-

回复: 编译 Android 13 SDK 出现 'libelf.h' file not found 应该怎么配置发布在 H/F/TV Series

sudo apt install libelf-dev

-

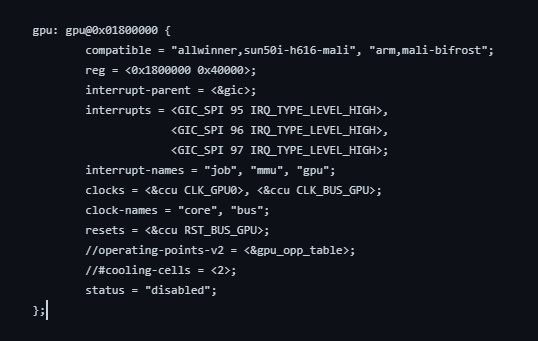

回复: H616 EMAC1 如何使用?发布在 H/F/TV Series

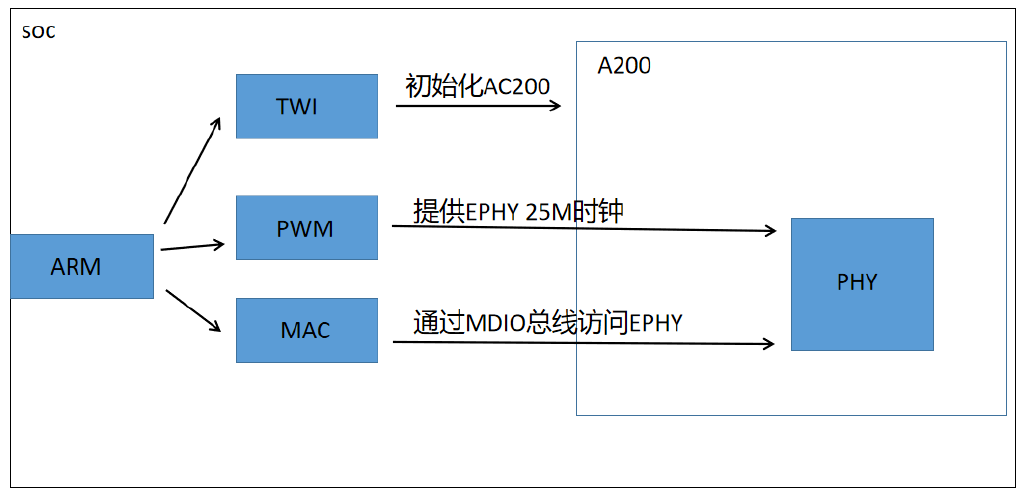

AW 部分SOC 集成了AC200 和AC300,而AC200 和AC300 内部又集成了EPHY

ARM 通过TWI 与AC200 进行通讯, 把EPHY 初始化,然后MAC 通过MDIO 总线是访问EPHY,PWM模块提供一个内部25M 时钟给EPHY。AC200 整体框图如下

-

回复: H616 EMAC1 如何使用?发布在 H/F/TV Series

另外主线的配置可以参考这个仓库:https://github.com/dumtux/Allwinner-H616 驱动了AC200