tcp传sockets

WhycanService 发布的帖子

-

回复: V853适配4.3寸屏lcd_width = <95>; lcd_height = <54>;显示出现问题发布在 V Series

这个是计算PPI使用的,是与分辨率成对应关系,由于屏幕不是完美的整数大小使用设置的时候如果出现分辨率与屏幕大小出现较大出入则会导致PPI计算错误显示异常。所以一般按照分辨率来设置的,例如800x600屏幕,实际大小为95x53,则设置80,60即可

-

回复: T113进入低功耗模式如何使用指定的GPIO唤醒发布在 Linux

&keyboard0 { key0 = <210 0x160>; wakeup-source; status = "okay"; };注册gpio-keys 绑定键值,或者gpio-keys增加wakeup-source;

-

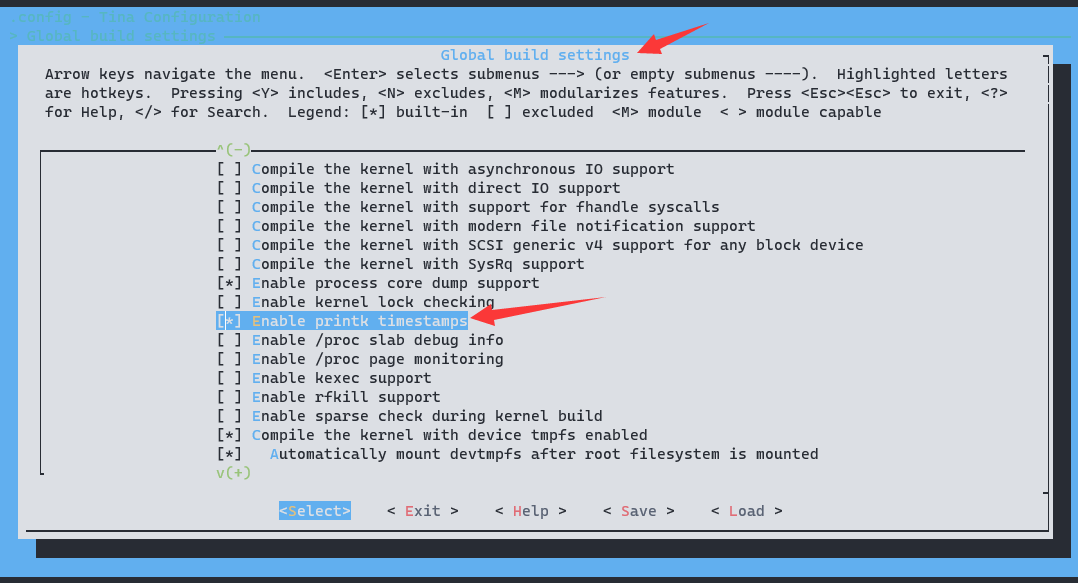

回复: D1s 使用Tina2.1内核日志不显示时间戳发布在 MR Series

一看就是没用过openwrt,openwrt可以一键设置开关kernel时间戳,并且强行覆盖内核的配置

m menuconfig

-

回复: 全志在线开源芯片 新 SDK 平台下载方法汇总发布在 代码下载问题专区

@ufbycd 远程仓库只是一个git仓库,并不会影响repo的报错,这个问题是本地repo的问题,需要谷歌升级repo的python版本与全志无关。

-

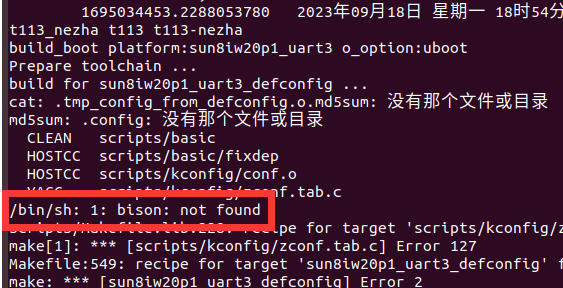

回复: D1H-nezha-tina构建报错发布在 MR Series

@mc964203886 在 D1H-nezha-tina构建报错 中说:

from ./signal.h:52, from c-stack.c:49:c-stack.c:55:26: error: missing binary operator before token "("

55 | #elif HAVE_LIBSIGSEGV && SIGSTKSZ < 16384

|系统gcc版本过高,请使用gcc-7以下版本

-

回复: parallel接口得SOC求推荐发布在 其它全志芯片讨论区

可以算一下,一般来说 2lane MIPI 是 200w 像素

也就是需要5lane MIPI 来驱动可以使用A523,有8lane MIPI CSI

-

回复: R128_RGB开发板,7寸屏LVGL例程问题发布在 A Series

配置问题,没有配置上PWM

修改

board/r128s2/devkit_rgb/configs/sys_config.fex文件末尾增加

[pwm7] pwm_used = 1 pwm_positive = port:PA22<4><0><2><default> -

回复: V851S tina linux ov5647 驱动程序没有 dmesg发布在 V Series

@kanken6174 可以检查一下驱动端是不是正确设置为了mipi模式Tina_Linux_Camera_开发指南.pdf

-

回复: MQ-R F133 NandFlash 烧录失败 55% W25N02KVZEIR WSON-8 3V 2Gb 串行NAND发布在 其它全志芯片讨论区

W25N02KVZEIR 不在支持列表,没有适配测试

-

回复: 全志 DDR初始化 v3s发布在 其它全志芯片讨论区

DRAM寄存器

#define S3_DRAM_COM_BASE (0x01c62000) #define S3_DRAM_CTL_BASE (0x01c63000) #define MCTL_CR_BL8 (0x4 << 20) #define MCTL_CR_1T (0x1 << 19) #define MCTL_CR_2T (0x0 << 19) #define MCTL_CR_LPDDR3 (0x7 << 16) #define MCTL_CR_LPDDR2 (0x6 << 16) #define MCTL_CR_DDR3 (0x3 << 16) #define MCTL_CR_DDR2 (0x2 << 16) #define MCTL_CR_SEQUENTIAL (0x1 << 15) #define MCTL_CR_INTERLEAVED (0x0 << 15) #define MCTL_CR_32BIT (0x1 << 12) #define MCTL_CR_16BIT (0x0 << 12) #define MCTL_CR_BUS_WIDTH(x) ((x) == 32 ? MCTL_CR_32BIT : MCTL_CR_16BIT) #define MCTL_CR_PAGE_SIZE(x) ((gfls(x) - 4) << 8) #define MCTL_CR_ROW_BITS(x) (((x) - 1) << 4) #define MCTL_CR_EIGHT_BANKS (0x1 << 2) #define MCTL_CR_FOUR_BANKS (0x0 << 2) #define MCTL_CR_DUAL_RANK (0x1 << 0) #define MCTL_CR_SINGLE_RANK (0x0 << 0) #define DRAMTMG0_TWTP(x) ((x) << 24) #define DRAMTMG0_TFAW(x) ((x) << 16) #define DRAMTMG0_TRAS_MAX(x) ((x) << 8) #define DRAMTMG0_TRAS(x) ((x) << 0) #define DRAMTMG1_TXP(x) ((x) << 16) #define DRAMTMG1_TRTP(x) ((x) << 8) #define DRAMTMG1_TRC(x) ((x) << 0) #define DRAMTMG2_TCWL(x) ((x) << 24) #define DRAMTMG2_TCL(x) ((x) << 16) #define DRAMTMG2_TRD2WR(x) ((x) << 8) #define DRAMTMG2_TWR2RD(x) ((x) << 0) #define DRAMTMG3_TMRW(x) ((x) << 16) #define DRAMTMG3_TMRD(x) ((x) << 12) #define DRAMTMG3_TMOD(x) ((x) << 0) #define DRAMTMG4_TRCD(x) ((x) << 24) #define DRAMTMG4_TCCD(x) ((x) << 16) #define DRAMTMG4_TRRD(x) ((x) << 8) #define DRAMTMG4_TRP(x) ((x) << 0) #define DRAMTMG5_TCKSRX(x) ((x) << 24) #define DRAMTMG5_TCKSRE(x) ((x) << 16) #define DRAMTMG5_TCKESR(x) ((x) << 8) #define DRAMTMG5_TCKE(x) ((x) << 0) #define PTR3_TDINIT1(x) ((x) << 20) #define PTR3_TDINIT0(x) ((x) << 0) #define PTR4_TDINIT3(x) ((x) << 20) #define PTR4_TDINIT2(x) ((x) << 0) #define RFSHTMG_TREFI(x) ((x) << 16) #define RFSHTMG_TRFC(x) ((x) << 0) #define PIR_CLRSR (0x1 << 27) /* Clear status registers */ #define PIR_QSGATE (0x1 << 10) /* Read DQS gate training */ #define PIR_DRAMINIT (0x1 << 8) /* DRAM initialization */ #define PIR_DRAMRST (0x1 << 7) /* DRAM reset */ #define PIR_PHYRST (0x1 << 6) /* PHY reset */ #define PIR_DCAL (0x1 << 5) /* DDL calibration */ #define PIR_PLLINIT (0x1 << 4) /* PLL initialization */ #define PIR_ZCAL (0x1 << 1) /* ZQ calibration */ #define PIR_INIT (0x1 << 0) /* PHY initialization trigger */ #define PGSR_INIT_DONE (0x1 << 0) /* PHY init done */ #define ZQCR_PWRDOWN (0x1 << 31) /* ZQ power down */ #define DATX_IOCR_DQ(x) (x) #define DATX_IOCR_DM (8) #define DATX_IOCR_DQS (9) #define DATX_IOCR_DQSN (10) #define DATX_IOCR_WRITE_DELAY(x) ((x) << 8) #define DATX_IOCR_READ_DELAY(x) ((x) << 0)时钟寄存器

#define S3_CCU_BASE (0x01c20000) #define CCU_PLL_CPU_CTRL (0x000) #define CCU_PLL_AUDIO_CTRL (0x008) #define CCU_PLL_VIDEO_CTRL (0x010) #define CCU_PLL_VE_CTRL (0x018) #define CCU_PLL_DDR0_CTRL (0x020) #define CCU_PLL_PERIPH0_CTRL (0x028) #define CCU_PLL_ISP_CTRL (0x02c) #define CCU_PLL_PERIPH1_CTRL (0x044) #define CCU_PLL_DDR1_CTRL (0x04c) #define CCU_CPU_AXI_CFG (0x050) #define CCU_AHB_APB0_CFG (0x054) #define CCU_APB1_CFG (0x058) #define CCU_AHB2_CFG (0x05c) #define CCU_BUS_CLK_GATE0 (0x060) #define CCU_BUS_CLK_GATE1 (0x064) #define CCU_BUS_CLK_GATE2 (0x068) #define CCU_BUS_CLK_GATE3 (0x06c) #define CCU_BUS_CLK_GATE4 (0x070) #define CCU_SDMMC0_CLK (0x088) #define CCU_SDMMC1_CLK (0x08c) #define CCU_SDMMC2_CLK (0x090) #define CCU_CE_CLK (0x09c) #define CCU_SPI0_CLK (0x0a0) #define CCU_USBPHY_CFG (0x0cc) #define CCU_DRAM_CFG (0x0f4) #define CCU_PLL_DDR1_CFG (0x0f8) #define CCU_MBUS_RST (0x0fc) #define CCU_DRAM_CLK_GATE (0x100) #define CCU_TCON_CLK (0x118) #define CCU_CSI_MISC_CLK (0x130) #define CCU_CSI_CLK (0x134) #define CCU_VE_CLK (0x13c) #define CCU_AC_DIG_CLK (0x140) #define CCU_AVS_CLK (0x144) #define CCU_MBUS_CLK (0x15c) #define CCU_MIPI_CSI_CLK (0x16c) #define CCU_PLL_STABLE_TIME0 (0x200) #define CCU_PLL_STABLE_TIME1 (0x204) #define CCU_PLL_CPU_BIAS (0x220) #define CCU_PLL_AUDIO_BIAS (0x224) #define CCU_PLL_VIDEO_BIAS (0x228) #define CCU_PLL_VE_BIAS (0x22c) #define CCU_PLL_DDR0_BIAS (0x230) #define CCU_PLL_PERIPH0_BIAS (0x234) #define CCU_PLL_ISP_BIAS (0x238) #define CCU_PLL_PERIPH1_BIAS (0x244) #define CCU_PLL_DDR1_BIAS (0x24C) #define CCU_PLL_CPU_TUN (0x250) #define CCU_PLL_DDR0_TUN (0x260) #define CCU_PLL_CPU_PAT (0x280) #define CCU_PLL_AUDIO_PAT (0x284) #define CCU_PLL_VIDEO_PAT (0x288) #define CCU_PLL_VE_PAT (0x28c) #define CCU_PLL_DDR0_PAT (0x290) #define CCU_PLL_ISP_PAT (0x298) #define CCU_PLL_PERIPH1_PAT (0x2a4) #define CCU_PLL_DDR1_PAT0 (0x2ac) #define CCU_PLL_DDR1_PAT1 (0x2b0) #define CCU_BUS_SOFT_RST0 (0x2c0) #define CCU_BUS_SOFT_RST1 (0x2c4) #define CCU_BUS_SOFT_RST2 (0x2c8) #define CCU_BUS_SOFT_RST3 (0x2d0) #define CCU_BUS_SOFT_RST4 (0x2d8) #define CCU_PS_CTRL (0x300) #define CCU_PS_CNT (0x304)驱动

#include <reg-ccu.h> #include <reg-dram.h> #define CONFIG_DRAM_BASE (0x40000000) #define CONFIG_DRAM_CLK (360) #define CONFIG_DRAM_ZQ (14779) #define clrbits_le32(addr, clear) \ write32(((virtual_addr_t)(addr)), read32(((virtual_addr_t)(addr))) & ~(clear)) #define setbits_le32(addr, set) \ write32(((virtual_addr_t)(addr)), read32(((virtual_addr_t)(addr))) | (set)) #define clrsetbits_le32(addr, clear, set) \ write32(((virtual_addr_t)(addr)), (read32(((virtual_addr_t)(addr))) & ~(clear)) | (set)) #define DIV_ROUND_UP(n, d) (((n) + (d) - 1) / (d)) #define REPEAT_BYTE(x) ((~0ul / 0xff) * (x)) struct s3_dram_com_reg_t { u32_t cr; /* 0x00 control register */ u8_t res0[0xc]; /* 0x04 */ u32_t mcr[16][2]; /* 0x10 */ u32_t bwcr; /* 0x90 bandwidth control register */ u32_t maer; /* 0x94 master enable register */ u32_t mapr; /* 0x98 master priority register */ u32_t mcgcr; /* 0x9c */ u32_t cpu_bwcr; /* 0xa0 */ u32_t gpu_bwcr; /* 0xa4 */ u32_t ve_bwcr; /* 0xa8 */ u32_t disp_bwcr; /* 0xac */ u32_t other_bwcr; /* 0xb0 */ u32_t total_bwcr; /* 0xb4 */ u8_t res1[0x8]; /* 0xb8 */ u32_t swonr; /* 0xc0 */ u32_t swoffr; /* 0xc4 */ u8_t res2[0x8]; /* 0xc8 */ u32_t cccr; /* 0xd0 */ u8_t res3[0x72c]; /* 0xd4 */ u32_t protect; /* 0x800 */ }; struct s3_dram_ctl_reg_t { u32_t pir; /* 0x00 PHY initialization register */ u32_t pwrctl; /* 0x04 */ u32_t mrctrl; /* 0x08 */ u32_t clken; /* 0x0c */ u32_t pgsr[2]; /* 0x10 PHY general status registers */ u32_t statr; /* 0x18 */ u8_t res1[0x14]; /* 0x1c */ u32_t mr[4]; /* 0x30 mode registers */ u32_t pllgcr; /* 0x40 */ u32_t ptr[5]; /* 0x44 PHY timing registers */ u32_t dramtmg[9]; /* 0x58 DRAM timing registers */ u32_t odtcfg; /* 0x7c */ u32_t pitmg[2]; /* 0x80 PHY interface timing registers */ u8_t res2[0x4]; /* 0x88 */ u32_t rfshctl0; /* 0x8c */ u32_t rfshtmg; /* 0x90 refresh timing */ u32_t rfshctl1; /* 0x94 */ u32_t pwrtmg; /* 0x98 */ u8_t res3[0x20]; /* 0x9c */ u32_t dqsgmr; /* 0xbc */ u32_t dtcr; /* 0xc0 */ u32_t dtar[4]; /* 0xc4 */ u32_t dtdr[2]; /* 0xd4 */ u32_t dtmr[2]; /* 0xdc */ u32_t dtbmr; /* 0xe4 */ u32_t catr[2]; /* 0xe8 */ u32_t dtedr[2]; /* 0xf0 */ u8_t res4[0x8]; /* 0xf8 */ u32_t pgcr[4]; /* 0x100 PHY general configuration registers */ u32_t iovcr[2]; /* 0x110 */ u32_t dqsdr; /* 0x118 */ u32_t dxccr; /* 0x11c */ u32_t odtmap; /* 0x120 */ u32_t zqctl[2]; /* 0x124 */ u8_t res6[0x14]; /* 0x12c */ u32_t zqcr; /* 0x140 ZQ control register */ u32_t zqsr; /* 0x144 ZQ status register */ u32_t zqdr[3]; /* 0x148 ZQ data registers */ u8_t res7[0x6c]; /* 0x154 */ u32_t sched; /* 0x1c0 */ u32_t perfhpr[2]; /* 0x1c4 */ u32_t perflpr[2]; /* 0x1cc */ u32_t perfwr[2]; /* 0x1d4 */ u8_t res8[0x2c]; /* 0x1dc */ u32_t aciocr; /* 0x208 */ u8_t res9[0xf4]; /* 0x20c */ struct { /* 0x300 DATX8 modules*/ u32_t mdlr; /* 0x00 */ u32_t lcdlr[3]; /* 0x04 */ u32_t iocr[11]; /* 0x10 IO configuration register */ u32_t bdlr6; /* 0x3c */ u32_t gtr; /* 0x40 */ u32_t gcr; /* 0x44 */ u32_t gsr[3]; /* 0x48 */ u8_t res0[0x2c];/* 0x54 */ } datx[4]; u8_t res10[0x388]; /* 0x500 */ u32_t upd2; /* 0x888 */ }; struct dram_para_t { u32_t read_delays; u32_t write_delays; u16_t page_size; u8_t bus_width; u8_t dual_rank; u8_t row_bits; u8_t bank_bits; }; static inline void sdelay(int loops) { __asm__ __volatile__ ("1:\n" "subs %0, %1, #1\n" "bne 1b":"=r" (loops):"0"(loops)); } static inline int gfls(int x) { int r = 32; if(!x) return 0; if(!(x & 0xffff0000u)) { x <<= 16; r -= 16; } if(!(x & 0xff000000u)) { x <<= 8; r -= 8; } if(!(x & 0xf0000000u)) { x <<= 4; r -= 4; } if(!(x & 0xc0000000u)) { x <<= 2; r -= 2; } if(!(x & 0x80000000u)) { x <<= 1; r -= 1; } return r; } static inline int ns_to_t(int ns) { unsigned int freq = CONFIG_DRAM_CLK / 2; return DIV_ROUND_UP(freq * ns, 1000); } static u32_t bin_to_mgray(int val) { u8_t table[32]; table[0] = 0x00; table[1] = 0x01; table[2] = 0x02; table[3] = 0x03; table[4] = 0x06; table[5] = 0x07; table[6] = 0x04; table[7] = 0x05; table[8] = 0x0c; table[9] = 0x0d; table[10] = 0x0e; table[11] = 0x0f; table[12] = 0x0a; table[13] = 0x0b; table[14] = 0x08; table[15] = 0x09; table[16] = 0x18; table[17] = 0x19; table[18] = 0x1a; table[19] = 0x1b; table[20] = 0x1e; table[21] = 0x1f; table[22] = 0x1c; table[23] = 0x1d; table[24] = 0x14; table[25] = 0x15; table[26] = 0x16; table[27] = 0x17; table[28] = 0x12; table[29] = 0x13; table[30] = 0x10; table[31] = 0x11; return table[clamp(val, 0, 31)]; } static int mgray_to_bin(u32_t val) { u8_t table[32]; table[0] = 0x00; table[1] = 0x01; table[2] = 0x02; table[3] = 0x03; table[4] = 0x06; table[5] = 0x07; table[6] = 0x04; table[7] = 0x05; table[8] = 0x0e; table[9] = 0x0f; table[10] = 0x0c; table[11] = 0x0d; table[12] = 0x08; table[13] = 0x09; table[14] = 0x0a; table[15] = 0x0b; table[16] = 0x1e; table[17] = 0x1f; table[18] = 0x1c; table[19] = 0x1d; table[20] = 0x18; table[21] = 0x19; table[22] = 0x1a; table[23] = 0x1b; table[24] = 0x10; table[25] = 0x11; table[26] = 0x12; table[27] = 0x13; table[28] = 0x16; table[29] = 0x17; table[30] = 0x14; table[31] = 0x15; return table[val & 0x1f]; } static void clock_set_pll_ddr(u32_t clk) { int n = 32; int k = 1; int m = 2; u32_t val; /* ddr pll rate = 24000000 * n * k / m */ if(clk > 24000000 * k * n / m) { m = 1; if(clk > 24000000 * k * n / m) { k = 2; } } val = (0x1 << 31); val |= (0x0 << 24); val |= (0x1 << 20); val |= ((((clk / (24000000 * k / m)) - 1) & 0x1f) << 8); val |= (((k - 1) & 0x3) << 4); val |= (((m - 1) & 0x3) << 0); write32(S3_CCU_BASE + CCU_PLL_DDR0_CTRL, val); sdelay(5500); } static void mctl_await_completion(u32_t * reg, u32_t mask, u32_t val) { int timeout = 0; while((read32((virtual_addr_t)reg) & mask) != val) { if(timeout++ > 10000) break; } } static int mctl_mem_matches(u32_t offset) { write32(CONFIG_DRAM_BASE, 0); write32(CONFIG_DRAM_BASE + offset, 0xaa55aa55); __asm__ __volatile__ ("dsb" : : : "memory"); return (read32(CONFIG_DRAM_BASE) == read32(CONFIG_DRAM_BASE + offset)) ? 1 : 0; } static void mctl_phy_init(u32_t val) { struct s3_dram_ctl_reg_t * ctl = (struct s3_dram_ctl_reg_t *)S3_DRAM_CTL_BASE; write32((virtual_addr_t)&ctl->pir, val | PIR_INIT); mctl_await_completion(&ctl->pgsr[0], PGSR_INIT_DONE, 0x1); } static void mctl_dq_delay(u32_t read, u32_t write) { struct s3_dram_ctl_reg_t * ctl = (struct s3_dram_ctl_reg_t *)S3_DRAM_CTL_BASE; int i, j; u32_t val; for(i = 0; i < 4; i++) { val = DATX_IOCR_WRITE_DELAY((write >> (i * 4)) & 0xf) | DATX_IOCR_READ_DELAY(((read >> (i * 4)) & 0xf) * 2); for(j = DATX_IOCR_DQ(0); j <= DATX_IOCR_DM; j++) write32((virtual_addr_t)&ctl->datx[i].iocr[j], val); } clrbits_le32(&ctl->pgcr[0], 1 << 26); for(i = 0; i < 4; i++) { val = DATX_IOCR_WRITE_DELAY((write >> (16 + i * 4)) & 0xf) | DATX_IOCR_READ_DELAY((read >> (16 + i * 4)) & 0xf); write32((virtual_addr_t)&ctl->datx[i].iocr[DATX_IOCR_DQS], val); write32((virtual_addr_t)&ctl->datx[i].iocr[DATX_IOCR_DQSN], val); } setbits_le32(&ctl->pgcr[0], 1 << 26); sdelay(1); } static void mctl_set_master_priority(void) { struct s3_dram_com_reg_t * com = (struct s3_dram_com_reg_t *)S3_DRAM_COM_BASE; write32((virtual_addr_t)&com->bwcr, 0x00010190); write32((virtual_addr_t)&com->mapr, 0x00000001); write32((virtual_addr_t)&com->mcr[0][0], 0x0200000d); write32((virtual_addr_t)&com->mcr[0][1], 0x00800100); write32((virtual_addr_t)&com->mcr[1][0], 0x06000009); write32((virtual_addr_t)&com->mcr[1][1], 0x01000400); write32((virtual_addr_t)&com->mcr[2][0], 0x0200000d); write32((virtual_addr_t)&com->mcr[2][1], 0x00600100); write32((virtual_addr_t)&com->mcr[3][0], 0x0100000d); write32((virtual_addr_t)&com->mcr[3][1], 0x00200080); write32((virtual_addr_t)&com->mcr[4][0], 0x07000009); write32((virtual_addr_t)&com->mcr[4][1], 0x01000640); write32((virtual_addr_t)&com->mcr[5][0], 0x0100000d); write32((virtual_addr_t)&com->mcr[5][1], 0x00200080); write32((virtual_addr_t)&com->mcr[6][0], 0x01000009); write32((virtual_addr_t)&com->mcr[6][1], 0x00400080); write32((virtual_addr_t)&com->mcr[7][0], 0x0100000d); write32((virtual_addr_t)&com->mcr[7][1], 0x00400080); write32((virtual_addr_t)&com->mcr[8][0], 0x0100000d); write32((virtual_addr_t)&com->mcr[8][1], 0x00400080); write32((virtual_addr_t)&com->mcr[9][0], 0x04000009); write32((virtual_addr_t)&com->mcr[9][1], 0x00400100); write32((virtual_addr_t)&com->mcr[10][0], 0x2000030d); write32((virtual_addr_t)&com->mcr[10][1], 0x04001800); write32((virtual_addr_t)&com->mcr[11][0], 0x04000009); write32((virtual_addr_t)&com->mcr[11][1], 0x00400120); } static void mctl_set_timing_params(struct dram_para_t * para) { struct s3_dram_ctl_reg_t * ctl = (struct s3_dram_ctl_reg_t *)S3_DRAM_CTL_BASE; u8_t tccd = 2; u8_t tfaw = ns_to_t(50); u8_t trrd = max(ns_to_t(10), 4); u8_t trcd = ns_to_t(15); u8_t trc = ns_to_t(53); u8_t txp = max(ns_to_t(8), 3); u8_t twtr = max(ns_to_t(8), 4); u8_t trtp = max(ns_to_t(8), 4); u8_t twr = max(ns_to_t(15), 3); u8_t trp = ns_to_t(15); u8_t tras = ns_to_t(38); u16_t trefi = ns_to_t(7800) / 32; u16_t trfc = ns_to_t(350); u8_t tmrw = 0; u8_t tmrd = 4; u8_t tmod = 12; u8_t tcke = 3; u8_t tcksrx = 5; u8_t tcksre = 5; u8_t tckesr = 4; u8_t trasmax = 24; u8_t tcl = 6; /* CL 12 */ u8_t tcwl = 4; /* CWL 8 */ u8_t t_rdata_en = 4; u8_t wr_latency = 2; u32_t tdinit0 = (500 * CONFIG_DRAM_CLK) + 1; /* 500us */ u32_t tdinit1 = (360 * CONFIG_DRAM_CLK) / 1000 + 1; /* 360ns */ u32_t tdinit2 = (200 * CONFIG_DRAM_CLK) + 1; /* 200us */ u32_t tdinit3 = (1 * CONFIG_DRAM_CLK) + 1; /* 1us */ u8_t twtp = tcwl + 2 + twr; /* WL + BL / 2 + tWR */ u8_t twr2rd = tcwl + 2 + twtr; /* WL + BL / 2 + tWTR */ u8_t trd2wr = tcl + 2 + 1 - tcwl; /* RL + BL / 2 + 2 - WL */ write32((virtual_addr_t)&ctl->mr[0], 0x1c70); /* CL=11, WR=12 */ write32((virtual_addr_t)&ctl->mr[1], 0x40); write32((virtual_addr_t)&ctl->mr[2], 0x18); /* CWL=8 */ write32((virtual_addr_t)&ctl->mr[3], 0x0); /* Set DRAM timing */ write32((virtual_addr_t)&ctl->dramtmg[0], DRAMTMG0_TWTP(twtp) | DRAMTMG0_TFAW(tfaw) | DRAMTMG0_TRAS_MAX(trasmax) | DRAMTMG0_TRAS(tras)); write32((virtual_addr_t)&ctl->dramtmg[1], DRAMTMG1_TXP(txp) | DRAMTMG1_TRTP(trtp) | DRAMTMG1_TRC(trc)); write32((virtual_addr_t)&ctl->dramtmg[2], DRAMTMG2_TCWL(tcwl) | DRAMTMG2_TCL(tcl) | DRAMTMG2_TRD2WR(trd2wr) | DRAMTMG2_TWR2RD(twr2rd)); write32((virtual_addr_t)&ctl->dramtmg[3], DRAMTMG3_TMRW(tmrw) | DRAMTMG3_TMRD(tmrd) | DRAMTMG3_TMOD(tmod)); write32((virtual_addr_t)&ctl->dramtmg[4], DRAMTMG4_TRCD(trcd) | DRAMTMG4_TCCD(tccd) | DRAMTMG4_TRRD(trrd) | DRAMTMG4_TRP(trp)); write32((virtual_addr_t)&ctl->dramtmg[5], DRAMTMG5_TCKSRX(tcksrx) | DRAMTMG5_TCKSRE(tcksre) | DRAMTMG5_TCKESR(tckesr) | DRAMTMG5_TCKE(tcke)); /* Set two rank timing */ clrsetbits_le32(&ctl->dramtmg[8], (0xff << 8) | (0xff << 0), (0x66 << 8) | (0x10 << 0)); /* Set PHY interface timing, write latency and read latency configure */ write32((virtual_addr_t)&ctl->pitmg[0], (0x2 << 24) | (t_rdata_en << 16) | (0x1 << 8) | (wr_latency << 0)); /* Set PHY timing, PTR0-2 use default */ write32((virtual_addr_t)&ctl->ptr[3], PTR3_TDINIT0(tdinit0) | PTR3_TDINIT1(tdinit1)); write32((virtual_addr_t)&ctl->ptr[4], PTR4_TDINIT2(tdinit2) | PTR4_TDINIT3(tdinit3)); /* Set refresh timing */ write32((virtual_addr_t)&ctl->rfshtmg, RFSHTMG_TREFI(trefi) | RFSHTMG_TRFC(trfc)); } static void mctl_zq_calibration(struct dram_para_t * para) { struct s3_dram_ctl_reg_t * ctl = (struct s3_dram_ctl_reg_t *)S3_DRAM_CTL_BASE; u16_t zq_val[6]; u32_t val; u8_t zq; int i; if(((read32(0x01c00000 + 0x24) & 0xff) == 0) && ((read32(0x01c00000 + 0xf0) & 0x1) == 0)) { clrsetbits_le32(&ctl->zqcr, 0xffff, CONFIG_DRAM_ZQ & 0xffff); write32((virtual_addr_t)&ctl->pir, PIR_CLRSR); mctl_phy_init(PIR_ZCAL); val = read32((virtual_addr_t)&ctl->zqdr[0]); val &= (0x1f << 16) | (0x1f << 0); val |= val << 8; write32((virtual_addr_t)&ctl->zqdr[0], val); val = read32((virtual_addr_t)&ctl->zqdr[1]); val &= (0x1f << 16) | (0x1f << 0); val |= val << 8; write32((virtual_addr_t)&ctl->zqdr[1], val); write32((virtual_addr_t)&ctl->zqdr[2], val); } else { write32((virtual_addr_t)&ctl->zqdr[2], 0x0a0a0a0a); for(i = 0; i < 6; i++) { zq = (CONFIG_DRAM_ZQ >> (i * 4)) & 0xf; write32((virtual_addr_t)&ctl->zqcr, (zq << 20) | (zq << 16) | (zq << 12) | (zq << 8) | (zq << 4) | (zq << 0)); write32((virtual_addr_t)&ctl->pir, PIR_CLRSR); mctl_phy_init(PIR_ZCAL); zq_val[i] = read32((virtual_addr_t)&ctl->zqdr[0]) & 0xff; write32((virtual_addr_t)&ctl->zqdr[2], REPEAT_BYTE(zq_val[i])); write32((virtual_addr_t)&ctl->pir, PIR_CLRSR); mctl_phy_init(PIR_ZCAL); val = read32((virtual_addr_t)&ctl->zqdr[0]) >> 24; zq_val[i] |= bin_to_mgray(mgray_to_bin(val) - 1) << 8; } write32((virtual_addr_t)&ctl->zqdr[0], (zq_val[1] << 16) | zq_val[0]); write32((virtual_addr_t)&ctl->zqdr[1], (zq_val[3] << 16) | zq_val[2]); write32((virtual_addr_t)&ctl->zqdr[2], (zq_val[5] << 16) | zq_val[4]); } } static void mctl_set_cr(struct dram_para_t * para) { struct s3_dram_com_reg_t * com = (struct s3_dram_com_reg_t *)S3_DRAM_COM_BASE; write32((virtual_addr_t)&com->cr, MCTL_CR_BL8 | MCTL_CR_2T | MCTL_CR_DDR3 | MCTL_CR_EIGHT_BANKS | MCTL_CR_BUS_WIDTH(para->bus_width) | MCTL_CR_INTERLEAVED | (para->dual_rank ? MCTL_CR_DUAL_RANK : MCTL_CR_SINGLE_RANK) | MCTL_CR_PAGE_SIZE(para->page_size) | MCTL_CR_ROW_BITS(para->row_bits)); } static void mctl_sys_init(struct dram_para_t * para) { struct s3_dram_ctl_reg_t * ctl = (struct s3_dram_ctl_reg_t *)S3_DRAM_CTL_BASE; u32_t val; val = read32(S3_CCU_BASE + CCU_MBUS_CLK); val &= ~(0x1 << 31); write32(S3_CCU_BASE + CCU_MBUS_CLK, val); val = read32(S3_CCU_BASE + CCU_MBUS_RST); val &= ~(0x1 << 31); write32(S3_CCU_BASE + CCU_MBUS_RST, val); val = read32(S3_CCU_BASE + CCU_BUS_CLK_GATE0); val &= ~(0x1 << 14); write32(S3_CCU_BASE + CCU_BUS_CLK_GATE0, val); val = read32(S3_CCU_BASE + CCU_BUS_SOFT_RST0); val &= ~(0x1 << 14); write32(S3_CCU_BASE + CCU_BUS_SOFT_RST0, val); val = read32(S3_CCU_BASE + CCU_PLL_DDR0_CTRL); val &= ~(0x1 << 31); write32(S3_CCU_BASE + CCU_PLL_DDR0_CTRL, val); sdelay(10); val = read32(S3_CCU_BASE + CCU_DRAM_CLK_GATE); val &= ~(0x1 << 31); write32(S3_CCU_BASE + CCU_DRAM_CLK_GATE, val); sdelay(1000); clock_set_pll_ddr(CONFIG_DRAM_CLK * 2 * 1000000); val = read32(S3_CCU_BASE + CCU_DRAM_CFG); val &= ~(0xf << 0); val &= ~(0x3 << 20); val |= ((1 - 1) << 0); val |= (0x0 << 20); val |= (0x1 << 16); write32(S3_CCU_BASE + CCU_DRAM_CFG, val); mctl_await_completion((u32_t *)(S3_CCU_BASE + CCU_DRAM_CFG), 0x1 << 16, 0); val = read32(S3_CCU_BASE + CCU_BUS_SOFT_RST0); val |= (0x1 << 14); write32(S3_CCU_BASE + CCU_BUS_SOFT_RST0, val); val = read32(S3_CCU_BASE + CCU_BUS_CLK_GATE0); val |= (0x1 << 14); write32(S3_CCU_BASE + CCU_BUS_CLK_GATE0, val); val = read32(S3_CCU_BASE + CCU_MBUS_RST); val |= (0x1 << 31); write32(S3_CCU_BASE + CCU_MBUS_RST, val); val = read32(S3_CCU_BASE + CCU_MBUS_CLK); val |= (0x1 << 31); write32(S3_CCU_BASE + CCU_MBUS_CLK, val); val = read32(S3_CCU_BASE + CCU_DRAM_CFG); val |= (0x1 << 31); write32(S3_CCU_BASE + CCU_DRAM_CFG, val); sdelay(10); write32((virtual_addr_t)&ctl->clken, 0xc00e); sdelay(500); } static int mctl_channel_init(struct dram_para_t * para) { struct s3_dram_com_reg_t * com = (struct s3_dram_com_reg_t *)S3_DRAM_COM_BASE; struct s3_dram_ctl_reg_t * ctl = (struct s3_dram_ctl_reg_t *)S3_DRAM_CTL_BASE; int i; mctl_set_cr(para); mctl_set_timing_params(para); mctl_set_master_priority(); clrbits_le32(&ctl->pgcr[0], (1 << 30) | 0x3f); clrsetbits_le32(&ctl->pgcr[1], 1 << 24, 1 << 26); write32((virtual_addr_t)&com->protect, 0x94be6fa3); sdelay(100); clrsetbits_le32(&ctl->upd2, 0xfff << 16, 0x50 << 16); write32((virtual_addr_t)&com->protect, 0x0); sdelay(100); for(i = 0; i < 4; i++) clrsetbits_le32(&ctl->datx[i].gcr, (0x3 << 4) | (0x1 << 1) | (0x3 << 2) | (0x3 << 12) | (0x3 << 14), 0x20); setbits_le32(&ctl->aciocr, 0x1 << 1); setbits_le32(&ctl->pgcr[2], 0x3 << 6); clrbits_le32(&ctl->pgcr[0], (0x3 << 14) | (0x3 << 12)); clrsetbits_le32(&ctl->pgcr[2], (0x3 << 10) | (0x3 << 8), (0x1 << 10) | (0x2 << 8)); if(para->bus_width != 32) { write32((virtual_addr_t)&ctl->datx[2].gcr, 0x0); write32((virtual_addr_t)&ctl->datx[3].gcr, 0x0); } clrsetbits_le32(&ctl->dtcr, 0xf << 24, (para->dual_rank ? 0x3 : 0x1) << 24); if(para->read_delays || para->write_delays) { mctl_dq_delay(para->read_delays, para->write_delays); sdelay(50); } mctl_zq_calibration(para); mctl_phy_init(PIR_PLLINIT | PIR_DCAL | PIR_PHYRST | PIR_DRAMRST | PIR_DRAMINIT | PIR_QSGATE); if(read32((virtual_addr_t)&ctl->pgsr[0]) & (0xfe << 20)) { if(((read32((virtual_addr_t)&ctl->datx[0].gsr[0]) >> 24) & 0x2) || ((read32((virtual_addr_t)&ctl->datx[1].gsr[0]) >> 24) & 0x2)) { clrsetbits_le32(&ctl->dtcr, 0xf << 24, 0x1 << 24); para->dual_rank = 0; } if(((read32((virtual_addr_t)&ctl->datx[2].gsr[0]) >> 24) & 0x1) || ((read32((virtual_addr_t)&ctl->datx[3].gsr[0]) >> 24) & 0x1)) { write32((virtual_addr_t)&ctl->datx[2].gcr, 0x0); write32((virtual_addr_t)&ctl->datx[3].gcr, 0x0); para->bus_width = 16; } mctl_set_cr(para); sdelay(20); mctl_phy_init(PIR_QSGATE); if(read32((virtual_addr_t)&ctl->pgsr[0]) & (0xfe << 20)) return 1; } mctl_await_completion(&ctl->statr, 0x1, 0x1); setbits_le32(&ctl->rfshctl0, 0x1 << 31); sdelay(10); clrbits_le32(&ctl->rfshctl0, 0x1 << 31); sdelay(10); write32((virtual_addr_t)&ctl->pgcr[3], 0x00aa0060); setbits_le32(&ctl->zqcr, ZQCR_PWRDOWN); write32((virtual_addr_t)&com->maer, 0xffffffff); return 0; } static void mctl_auto_detect_dram_size(struct dram_para_t * para) { para->page_size = 512; para->row_bits = 16; para->bank_bits = 2; mctl_set_cr(para); for(para->row_bits = 11; para->row_bits < 16; para->row_bits++) { if(mctl_mem_matches((1 << (para->row_bits + para->bank_bits)) * para->page_size)) break; } para->bank_bits = 3; mctl_set_cr(para); for(para->bank_bits = 2; para->bank_bits < 3; para->bank_bits++) { if(mctl_mem_matches((1 << para->bank_bits) * para->page_size)) break; } para->page_size = 8192; mctl_set_cr(para); for(para->page_size = 512; para->page_size < 8192; para->page_size *= 2) { if(mctl_mem_matches(para->page_size)) break; } } void sys_dram_init(void) { struct s3_dram_com_reg_t * com = (struct s3_dram_com_reg_t *)S3_DRAM_COM_BASE; struct s3_dram_ctl_reg_t * ctl = (struct s3_dram_ctl_reg_t *)S3_DRAM_CTL_BASE; struct dram_para_t para = { .read_delays = 0x00007979, .write_delays = 0x6aaa0000, .dual_rank = 0, .bus_width = 32, .row_bits = 15, .bank_bits = 3, .page_size = 4096, }; u32_t * dsz = (void *)0x00000020; if(dsz[0] != 0) return; mctl_sys_init(¶); if(mctl_channel_init(¶)) { dsz[0] = 0; return; } if(para.dual_rank) write32((virtual_addr_t)&ctl->odtmap, 0x00000303); else write32((virtual_addr_t)&ctl->odtmap, 0x00000201); sdelay(1); write32((virtual_addr_t)&ctl->odtcfg, 0x0c000400); setbits_le32(&com->cccr, 1 << 31); sdelay(10); mctl_auto_detect_dram_size(¶); mctl_set_cr(¶); dsz[0] = (1UL << (para.row_bits + para.bank_bits)) * para.page_size * (para.dual_rank ? 2 : 1); }代码都有,咋这么喜欢自己从头造轮子呢?DRAM驱动也没这么容易写的吧。

-

回复: 新 SDK 平台下载 D1-H/D1s SDK发布在 MR Series

@vuiot 基础开发环境没有安装,缺少bison命令

sudo apt-get install build-essential subversion git libncurses5-dev zlib1g-dev gawk flex bison quilt libssl-dev xsltproc libxml-parser-perl mercurial bzr ecj cvs unzip lsof kconfig-frontends android-tools-mkbootimg python2 libpython3-dev gcc-multilib libc6:i386 libstdc++6:i386 lib32z1 -

回复: 新 SDK 平台下载 XR806 SDK发布在 Wireless & Analog Series

@rookie 后面缺一些命令,完整命令如下

git clone https://sdk.aw-ol.com/git_repo/XR806/xr806_sdk/xr806_sdk.git -b xr806_sdk -

回复: V583S MPP UVC摄像头存储成mp4发布在 V Series

//#define LOG_NDEBUG 0 #define LOG_TAG "sample_uvc2vdec_vo" #include <utils/plat_log.h> #include <stdio.h> #include <errno.h> #include <stdlib.h> #include <string.h> #include <unistd.h> #include <fcntl.h> #include <signal.h> #include <time.h> #include <confparser.h> #include <mpi_uvc.h> #include <mpi_vdec.h> #include <mpi_vo.h> #include "vo/hwdisplay.h" #include "sample_uvc2vdec_vo.h" #include "sample_uvc2vdec_vo_config.h" static SampleUvc2VdecVoContext *gpSampleUvc2VdecVoContext = NULL; int initSampleUvc2VdecVoContext(SampleUvc2VdecVoContext *pContext) { memset(pContext, 0, sizeof *pContext); pContext->mUILayer = HLAY(2, 0); pContext->mVoLayer = MM_INVALID_LAYER; pContext->mVOChn = MM_INVALID_CHN; pContext->mSubVoLayer = MM_INVALID_LAYER; pContext->mSubVOChn = MM_INVALID_CHN; cdx_sem_init(&pContext->mSemExit, 0); int ret = pthread_mutex_init(&pContext->mFrameLock, NULL); if (ret!=0) { aloge("fatal error! pthread mutex init fail!"); } int i; for(i=0; i< MAX_FRAMEPAIR_ARRAY_SIZE; i++) { pContext->mDoubleFrameArray[i].mMainFrame.mId = -1; pContext->mDoubleFrameArray[i].mSubFrame.mId = -1; } return 0; } int destroySampleUvc2VdecVoContext(SampleUvc2VdecVoContext *pContext) { cdx_sem_deinit(&pContext->mSemExit); pthread_mutex_destroy(&pContext->mFrameLock); return 0; } static int ParseCmdLine(int argc, char **argv, SampleUvc2VdecVoCmdLineParam *pCmdLinePara) { //alogd("sample_region input path is : %s", argv[0]); int ret = 0; int i = 1; memset(pCmdLinePara, 0, sizeof *pCmdLinePara); while(i < argc) { if(!strcmp(argv[i], "-path")) { if((++i) >= argc) { aloge("fatal error!"); ret = -1; break; } if(strlen(argv[i]) >= MAX_FILE_PATH_SIZE) { aloge("fatal error!"); } strncpy(pCmdLinePara->mConfigFilePath, argv[i], strlen(argv[i])); pCmdLinePara->mConfigFilePath[strlen(argv[i])] = '\0'; } else if(!strcmp(argv[i], "-h")) { printf("CmdLine param example:\n" "\t run -path /home/sample_uvc2vo.conf\n"); ret = 1; break; } else { printf("CmdLine param example:\n" "\t run -path /home/sample_uvc2vo.conf\n"); } ++i; } return ret; } static ERRORTYPE LoadSampleUvc2VdecVoConfig(SampleUvc2VdecVoConfig *pConfig, const char *conf_path) { int ret = 0; char *ptr = NULL; if(!conf_path) { alogd("user not set config file. use default test parameter!"); strcpy(pConfig->mDevName, (void *)"/dev/video0"); pConfig->mPicFormat = UVC_MJPEG; pConfig->mCaptureVideoBufCnt = 5; pConfig->mCaptureWidth = 1280; pConfig->mCaptureHeight = 720; pConfig->mCaptureFrameRate = 30; pConfig->mbDecodeSubOutEnable = FALSE; pConfig->mDecodeSubOutWidthScalePower = 0; pConfig->mDecodeSubOutHeightScalePower = 0; pConfig->mDisplayMainX = 0; pConfig->mDisplayMainY = 0; pConfig->mDisplayMainWidth = 320; pConfig->mDisplayMainHeight = 240; pConfig->mDisplaySubX = 320; pConfig->mDisplaySubY = 0; pConfig->mDisplaySubWidth = 320; pConfig->mDisplaySubHeight = 240; pConfig->mTestFrameCount = 0; } else { CONFPARSER_S stConfParser; ret = createConfParser(conf_path, &stConfParser); if(ret < 0) { aloge("load conf fail!"); return FAILURE; } memset(pConfig, 0, sizeof *pConfig); ptr = (char *)GetConfParaString(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_DEV_NAME, NULL); if(ptr) { strcpy(pConfig->mDevName, ptr); } else { aloge("fatal error! the uvc dev name is error!"); return FAILURE; } char* pStrPixelFormat = (char *)GetConfParaString(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_PIC_FORMAT, NULL); if(!strcmp(pStrPixelFormat, "UVC_MJPEG")) { pConfig->mPicFormat = UVC_MJPEG; } else if(!strcmp(pStrPixelFormat, "UVC_H264")) { pConfig->mPicFormat = UVC_H264; } else if(!strcmp(pStrPixelFormat, "UVC_YUY2")) { pConfig->mPicFormat = UVC_YUY2; } else { aloge("fatal error! conf file pic_format is [%s]?", pStrPixelFormat); pConfig->mPicFormat = UVC_YUY2; } pConfig->mCaptureVideoBufCnt = GetConfParaInt(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_CAPTURE_VIDEOBUFCNT, 0); pConfig->mCaptureWidth = GetConfParaInt(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_CAPTURE_WIDTH, 640); pConfig->mCaptureHeight = GetConfParaInt(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_CAPTURE_HEIGHT, 480); pConfig->mCaptureFrameRate = GetConfParaInt(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_CAPTURE_FRAMERATE, 0); pConfig->mbDecodeSubOutEnable = GetConfParaInt(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_DECODE_SUB_OUT_ENABLE, 0); pConfig->mDecodeSubOutWidthScalePower = GetConfParaInt(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_DECODE_SUB_OUT_WIDTH_SCALE_POWER, 0); pConfig->mDecodeSubOutHeightScalePower = GetConfParaInt(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_DECODE_SUB_OUT_HEIGHT_SCALE_POWER, 0); pConfig->mDisplayMainX = GetConfParaInt(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_DISPLAY_MAIN_X, 0); pConfig->mDisplayMainY = GetConfParaInt(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_DISPLAY_MAIN_Y, 0); pConfig->mDisplayMainWidth = GetConfParaInt(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_DISPLAY_MAIN_WIDTH, 0); pConfig->mDisplayMainHeight = GetConfParaInt(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_DISPLAY_MAIN_HEIGHT, 0); pConfig->mDisplaySubX = GetConfParaInt(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_DISPLAY_SUB_X, 0); pConfig->mDisplaySubY = GetConfParaInt(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_DISPLAY_SUB_Y, 0); pConfig->mDisplaySubWidth = GetConfParaInt(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_DISPLAY_SUB_WIDTH, 0); pConfig->mDisplaySubHeight = GetConfParaInt(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_DISPLAY_SUB_HEIGHT, 0); pConfig->mTestFrameCount = GetConfParaInt(&stConfParser, SAMPLE_UVC2VDEC_VO_KEY_TEST_FRAME_COUNT, 0); destroyConfParser(&stConfParser); } return SUCCESS; } /** * * @return suffix of array, if not find, return -1. */ int FindFrameIdInArray(SampleUvc2VdecVoContext *pContext, unsigned int nFrameId) { int suffix = -1; int matchNum = 0; int i; for(i=0; i<MAX_FRAMEPAIR_ARRAY_SIZE; i++) { if(nFrameId == pContext->mDoubleFrameArray[i].mMainFrame.mId) { if(0 == matchNum) { suffix = i; } else { aloge("fatal error! already match num[%d], current suffix[%d], id[%d]", matchNum, i, nFrameId); } matchNum++; } } return suffix; } static ERRORTYPE SampleUvc2VdecVo_VOCallbackWrapper(void *cookie, MPP_CHN_S *pChn, MPP_EVENT_TYPE event, void *pEventData) { ERRORTYPE ret = SUCCESS; SampleUvc2VdecVoContext *pContext = (SampleUvc2VdecVoContext*)cookie; if(MOD_ID_VOU == pChn->mModId) { int bMainFrameFlag = 0; if(pChn->mDevId == pContext->mVoLayer && pChn->mChnId == pContext->mVOChn) { bMainFrameFlag = 1; } else { if(pContext->mConfigParam.mbDecodeSubOutEnable) { if(pChn->mDevId == pContext->mSubVoLayer && pChn->mChnId == pContext->mSubVOChn) { bMainFrameFlag = 0; } else { aloge("fatal error! VO layerId[%d]chnId[%d] is invalid! main/sub frame all wrong!", pChn->mDevId, pChn->mChnId); } } else { aloge("fatal error! VO layerId[%d]!=[%d], chnId[%d]!=[%d]", pChn->mDevId, pContext->mVoLayer, pChn->mChnId, pContext->mVOChn); } } switch(event) { case MPP_EVENT_RELEASE_VIDEO_BUFFER: { VIDEO_FRAME_INFO_S *pVideoFrameInfo = (VIDEO_FRAME_INFO_S*)pEventData; pthread_mutex_lock(&pContext->mFrameLock); VdecDoubleFrameInfo *pDbFramePair = NULL; int suffix = FindFrameIdInArray(pContext, pVideoFrameInfo->mId); if(suffix >= 0) { pDbFramePair = &pContext->mDoubleFrameArray[suffix]; } else { aloge("fatal error! why not find frameId[%d]?", pVideoFrameInfo->mId); } if(bMainFrameFlag) { pDbFramePair->mMainRefCnt--; if(pDbFramePair->mMainRefCnt < 0) { aloge("fatal error! mainRefCnt[%d] wrong!", pDbFramePair->mMainRefCnt); } } else { pDbFramePair->mSubRefCnt--; if(pDbFramePair->mSubRefCnt < 0) { aloge("fatal error! subRefCnt[%d] wrong!", pDbFramePair->mSubRefCnt); } } if(0 == pDbFramePair->mMainRefCnt && 0 == pDbFramePair->mSubRefCnt) { ret = AW_MPI_VDEC_ReleaseDoubleImage(pContext->mVdecChn, &pDbFramePair->mMainFrame, &pDbFramePair->mSubFrame); if(SUCCESS == ret) { pContext->mHoldFrameNum--; if(pContext->mHoldFrameNum < 0) { aloge("fatal error! holdframe num[%d] < 0, check code!", pContext->mHoldFrameNum); } } else { aloge("fatal error! why release frame to vdec fail[0x%x]?", ret); } } pthread_mutex_unlock(&pContext->mFrameLock); break; } case MPP_EVENT_SET_VIDEO_SIZE: { SIZE_S *pDisplaySize = (SIZE_S*)pEventData; alogd("volayer[%d][%d] report video display size[%dx%d]", pChn->mDevId, pChn->mChnId, pDisplaySize->Width, pDisplaySize->Height); break; } case MPP_EVENT_RENDERING_START: { alogd("volayer[%d][%d] report rendering start", pChn->mDevId, pChn->mChnId); break; } default: { //postEventFromNative(this, event, 0, 0, pEventData); aloge("fatal error! unknown event[0x%x] from channel[0x%x][0x%x][0x%x]!", event, pChn->mModId, pChn->mDevId, pChn->mChnId); ret = ERR_VO_ILLEGAL_PARAM; break; } } } else { aloge("fatal error! why modId[0x%x]?", pChn->mModId); ret = FAILURE; } return ret; } void handle_exit(int signo) { alogd("user want to exit!"); if(gpSampleUvc2VdecVoContext != NULL) { cdx_sem_up(&gpSampleUvc2VdecVoContext->mSemExit); } } int main(int argc, char **argv) { int result = 0; SampleUvc2VdecVoContext *pContext = (SampleUvc2VdecVoContext*)malloc(sizeof(SampleUvc2VdecVoContext)); initSampleUvc2VdecVoContext(pContext); gpSampleUvc2VdecVoContext = pContext; if(ParseCmdLine(argc, argv, &pContext->mCmdLineParam) != 0) { result = -1; goto _exit; } char *pConfigFilePath = NULL; if(strlen(pContext->mCmdLineParam.mConfigFilePath) > 0) { pConfigFilePath = pContext->mCmdLineParam.mConfigFilePath; } if(LoadSampleUvc2VdecVoConfig(&pContext->mConfigParam, pConfigFilePath) != SUCCESS) { aloge("fatal error! no config file or parse conf file fail"); result = -1; goto _exit; } if (signal(SIGINT, handle_exit) == SIG_ERR) { perror("error:can't catch SIGSEGV"); } memset(&pContext->mSysconf, 0, sizeof(MPP_SYS_CONF_S)); pContext->mSysconf.nAlignWidth = 32; AW_MPI_SYS_SetConf(&pContext->mSysconf); AW_MPI_SYS_Init(); AW_MPI_VDEC_SetVEFreq(MM_INVALID_CHN, 648); ERRORTYPE eRet = AW_MPI_UVC_CreateDevice(pContext->mConfigParam.mDevName); if(eRet != SUCCESS) { aloge("error: the %s UVC device can not create!", pContext->mConfigParam.mDevName); } UVC_ATTR_S attr; memset(&attr, 0, sizeof attr); attr.mPixelformat = pContext->mConfigParam.mPicFormat; attr.mUvcVideo_BufCnt = pContext->mConfigParam.mCaptureVideoBufCnt; attr.mUvcVideo_Width = pContext->mConfigParam.mCaptureWidth; attr.mUvcVideo_Height = pContext->mConfigParam.mCaptureHeight; attr.mUvcVideo_Fps = pContext->mConfigParam.mCaptureFrameRate; eRet = AW_MPI_UVC_SetDeviceAttr(pContext->mConfigParam.mDevName, &attr); if(eRet != SUCCESS) { aloge("error: the %s UVC can not set device attr", pContext->mConfigParam.mDevName); } eRet = AW_MPI_UVC_GetDeviceAttr(pContext->mConfigParam.mDevName, &attr); if(eRet != SUCCESS) { aloge("error: the %UVC can not get device attr", pContext->mConfigParam.mDevName); } pContext->mUvcChn = 0; eRet = AW_MPI_UVC_CreateVirChn(pContext->mConfigParam.mDevName, pContext->mUvcChn); if(eRet != SUCCESS) { aloge("error: the %s UVC can not create virchannel[%d]", pContext->mConfigParam.mDevName, pContext->mUvcChn); } pContext->mVdecChn = 0; VDEC_CHN_ATTR_S VdecChnAttr; memset(&VdecChnAttr, 0, sizeof VdecChnAttr); VdecChnAttr.mType = PT_MJPEG; VdecChnAttr.mPicWidth = 0; VdecChnAttr.mPicHeight = 0; VdecChnAttr.mInitRotation = ROTATE_NONE; VdecChnAttr.mOutputPixelFormat = MM_PIXEL_FORMAT_YVU_SEMIPLANAR_420; VdecChnAttr.mSubPicEnable = pContext->mConfigParam.mbDecodeSubOutEnable; VdecChnAttr.mSubPicWidthRatio = pContext->mConfigParam.mDecodeSubOutWidthScalePower; VdecChnAttr.mSubPicHeightRatio = pContext->mConfigParam.mDecodeSubOutHeightScalePower; VdecChnAttr.mSubOutputPixelFormat = MM_PIXEL_FORMAT_YVU_SEMIPLANAR_420; VdecChnAttr.mVdecVideoAttr.mMode = VIDEO_MODE_FRAME; VdecChnAttr.mVdecVideoAttr.mSupportBFrame = 1; eRet = AW_MPI_VDEC_CreateChn(pContext->mVdecChn, &VdecChnAttr); if(eRet != SUCCESS) { aloge("fatal error: the %s uvc can not create vdec chn[%s]", pContext->mConfigParam.mDevName, pContext->mVdecChn); } pContext->mVoDev = 0; AW_MPI_VO_Enable(pContext->mVoDev); AW_MPI_VO_AddOutsideVideoLayer(pContext->mUILayer); AW_MPI_VO_CloseVideoLayer(pContext->mUILayer); VO_PUB_ATTR_S stPubAttr; memset(&stPubAttr, 0, sizeof(VO_PUB_ATTR_S)); AW_MPI_VO_GetPubAttr(pContext->mVoDev, &stPubAttr); stPubAttr.enIntfType = VO_INTF_LCD; stPubAttr.enIntfSync = VO_OUTPUT_NTSC; AW_MPI_VO_SetPubAttr(pContext->mVoDev, &stPubAttr); int hlay0 = 0; while(hlay0 < VO_MAX_LAYER_NUM) { if(SUCCESS == AW_MPI_VO_EnableVideoLayer(hlay0)) { break; } hlay0+=4; } if(hlay0 >= VO_MAX_LAYER_NUM) { aloge("error: enable video layer failed"); } pContext->mVoLayer = hlay0; AW_MPI_VO_GetVideoLayerAttr(pContext->mVoLayer, &pContext->mLayerAttr); pContext->mLayerAttr.stDispRect.X = pContext->mConfigParam.mDisplayMainX; pContext->mLayerAttr.stDispRect.Y = pContext->mConfigParam.mDisplayMainY; pContext->mLayerAttr.stDispRect.Width = pContext->mConfigParam.mDisplayMainWidth; pContext->mLayerAttr.stDispRect.Height = pContext->mConfigParam.mDisplayMainHeight; AW_MPI_VO_SetVideoLayerAttr(pContext->mVoLayer, &pContext->mLayerAttr); BOOL bSuccessFlag = FALSE; pContext->mVOChn = 0; while(pContext->mVOChn < VO_MAX_CHN_NUM) { eRet = AW_MPI_VO_CreateChn(pContext->mVoLayer, pContext->mVOChn); if(SUCCESS == eRet) { bSuccessFlag = TRUE; break; } else if(ERR_VO_CHN_NOT_DISABLE == eRet) { alogd("vo channel[%d] is exist, find next", pContext->mVOChn); pContext->mVOChn++; } else { aloge("error:create vo channel[%d] ret[0x%x]", pContext->mVOChn, eRet); pContext->mVOChn++; } } if(!bSuccessFlag) { pContext->mVOChn = MM_INVALID_CHN; aloge("fatal error: create vo channel failed"); } MPPCallbackInfo cbInfo; cbInfo.cookie = (void *)pContext; cbInfo.callback = (MPPCallbackFuncType)&SampleUvc2VdecVo_VOCallbackWrapper; AW_MPI_VO_RegisterCallback(pContext->mVoLayer, pContext->mVOChn, &cbInfo); AW_MPI_VO_SetChnDispBufNum(pContext->mVoLayer, pContext->mVOChn, 2); if(pContext->mConfigParam.mbDecodeSubOutEnable) { int hlay0 = 0; while(hlay0 < VO_MAX_LAYER_NUM) { if(SUCCESS == AW_MPI_VO_EnableVideoLayer(hlay0)) { break; } hlay0+=4; } if(hlay0 >= VO_MAX_LAYER_NUM) { aloge("error: enable video layer failed"); } pContext->mSubVoLayer = hlay0; AW_MPI_VO_GetVideoLayerAttr(pContext->mSubVoLayer, &pContext->mSubLayerAttr); pContext->mSubLayerAttr.stDispRect.X = pContext->mConfigParam.mDisplaySubX; pContext->mSubLayerAttr.stDispRect.Y = pContext->mConfigParam.mDisplaySubY; pContext->mSubLayerAttr.stDispRect.Width = pContext->mConfigParam.mDisplaySubWidth; pContext->mSubLayerAttr.stDispRect.Height = pContext->mConfigParam.mDisplaySubHeight; AW_MPI_VO_SetVideoLayerAttr(pContext->mSubVoLayer, &pContext->mSubLayerAttr); BOOL bSuccessFlag = FALSE; pContext->mSubVOChn = 0; while(pContext->mSubVOChn < VO_MAX_CHN_NUM) { eRet = AW_MPI_VO_CreateChn(pContext->mSubVoLayer, pContext->mSubVOChn); if(SUCCESS == eRet) { bSuccessFlag = TRUE; break; } else if(ERR_VO_CHN_NOT_DISABLE == eRet) { alogd("vo channel[%d] is exist, find next", pContext->mSubVOChn); pContext->mSubVOChn++; } else { aloge("error:create vo channel[%d] ret[0x%x]", pContext->mSubVOChn, eRet); pContext->mSubVOChn++; } } if(!bSuccessFlag) { pContext->mSubVOChn = MM_INVALID_CHN; aloge("fatal error: create vo channel failed"); } AW_MPI_VO_RegisterCallback(pContext->mSubVoLayer, pContext->mSubVOChn, &cbInfo); AW_MPI_VO_SetChnDispBufNum(pContext->mSubVoLayer, pContext->mSubVOChn, 2); } MPP_CHN_S UvcChn = {MOD_ID_UVC, (int)pContext->mConfigParam.mDevName, pContext->mUvcChn}; // note: UvcChn->mDevId is the pointer of char *; MPP_CHN_S VdecChn = {MOD_ID_VDEC, 0, pContext->mVdecChn}; eRet = AW_MPI_SYS_Bind(&UvcChn, &VdecChn); if(eRet != SUCCESS) { aloge("fatal error! bind uvc2vdec fail[0x%x]", eRet); } eRet = AW_MPI_UVC_EnableDevice(pContext->mConfigParam.mDevName); if(eRet != SUCCESS) { aloge("fatal error: the %UVC device can not start", pContext->mConfigParam.mDevName); } eRet = AW_MPI_UVC_StartRecvPic(pContext->mConfigParam.mDevName, pContext->mUvcChn); if(eRet != SUCCESS) { aloge("fatal error: the %s UVC can not start virchannel[%d]", pContext->mConfigParam.mDevName, pContext->mUvcChn); } AW_MPI_VDEC_StartRecvStream(pContext->mVdecChn); AW_MPI_VO_StartChn(pContext->mVoLayer, pContext->mVOChn); if(pContext->mConfigParam.mbDecodeSubOutEnable) { AW_MPI_VO_StartChn(pContext->mSubVoLayer, pContext->mSubVOChn); } //get frame from vdec, send frame to vo. VIDEO_FRAME_INFO_S mainFrameInfo; VIDEO_FRAME_INFO_S subFrameInfo; while(1) { if(pContext->mConfigParam.mTestFrameCount > 0) { if(pContext->mFrameCounter>=pContext->mConfigParam.mTestFrameCount) { alogd("get [%d] frames from vdec, prepare to exit!", pContext->mFrameCounter); break; } } if(cdx_sem_get_val(&pContext->mSemExit) > 0) { alogd("detect user exit signal! prepare to exit!"); break; } eRet = AW_MPI_VDEC_GetDoubleImage(pContext->mVdecChn, &mainFrameInfo, &subFrameInfo, 500); VdecDoubleFrameInfo *pDstDbFrame = NULL; if(SUCCESS == eRet) { pthread_mutex_lock(&pContext->mFrameLock); int suffix = FindFrameIdInArray(pContext, mainFrameInfo.mId); if(-1 == suffix) { if(pContext->mValidDoubleFrameBufferNum >= MAX_FRAMEPAIR_ARRAY_SIZE) { aloge("fatal error! frame number [%d] too much!", pContext->mValidDoubleFrameBufferNum); } pDstDbFrame = &pContext->mDoubleFrameArray[pContext->mValidDoubleFrameBufferNum]; pContext->mValidDoubleFrameBufferNum++; } else { pDstDbFrame = &pContext->mDoubleFrameArray[suffix]; } if(pDstDbFrame->mMainRefCnt!=0 || pDstDbFrame->mSubRefCnt!=0) { aloge("fatal error! refCnt[%d],[%d] != 0", pDstDbFrame->mMainRefCnt, pDstDbFrame->mSubRefCnt); } pDstDbFrame->mMainFrame = mainFrameInfo; if(pContext->mConfigParam.mbDecodeSubOutEnable) { pDstDbFrame->mSubFrame = subFrameInfo; } pContext->mFrameCounter++; pContext->mHoldFrameNum++; pthread_mutex_unlock(&pContext->mFrameLock); } else { alogw("why not get frame from vdec for too long? ret=0x%x", eRet); continue; } pthread_mutex_lock(&pContext->mFrameLock); pDstDbFrame->mMainRefCnt++; if(pContext->mConfigParam.mbDecodeSubOutEnable) { pDstDbFrame->mSubRefCnt++; } eRet = AW_MPI_VO_SendFrame(pContext->mVoLayer, pContext->mVOChn, &pDstDbFrame->mMainFrame, 0); if(SUCCESS == eRet) { } else { aloge("fatal error! why send frame to vo fail? layer[%d]chn[%d], ret[0x%x]", pContext->mVoLayer, pContext->mVOChn, eRet); pDstDbFrame->mMainRefCnt--; } if(pContext->mConfigParam.mbDecodeSubOutEnable) { eRet = AW_MPI_VO_SendFrame(pContext->mSubVoLayer, pContext->mSubVOChn, &pDstDbFrame->mSubFrame, 0); if(SUCCESS == eRet) { } else { aloge("fatal error! why send frame to vo fail? layer[%d]chn[%d], ret[0x%x]", pContext->mSubVoLayer, pContext->mSubVOChn, eRet); pDstDbFrame->mSubRefCnt--; } } pthread_mutex_unlock(&pContext->mFrameLock); } AW_MPI_VO_StopChn(pContext->mVoLayer, pContext->mVOChn); if(pContext->mConfigParam.mbDecodeSubOutEnable) { AW_MPI_VO_StopChn(pContext->mSubVoLayer, pContext->mSubVOChn); } AW_MPI_VDEC_StopRecvStream(pContext->mVdecChn); AW_MPI_UVC_StopRecvPic(pContext->mConfigParam.mDevName, pContext->mUvcChn); AW_MPI_VO_DestroyChn(pContext->mVoLayer, pContext->mVOChn); pContext->mVOChn = MM_INVALID_CHN; if(pContext->mConfigParam.mbDecodeSubOutEnable) { AW_MPI_VO_DestroyChn(pContext->mSubVoLayer, pContext->mSubVOChn); pContext->mSubVOChn = MM_INVALID_CHN; } AW_MPI_VDEC_DestroyChn(pContext->mVdecChn); pContext->mVdecChn = MM_INVALID_CHN; AW_MPI_UVC_DestroyVirChn(pContext->mConfigParam.mDevName, pContext->mUvcChn); pContext->mUvcChn = MM_INVALID_CHN; AW_MPI_UVC_DisableDevice(pContext->mConfigParam.mDevName); AW_MPI_UVC_DestroyDevice(pContext->mConfigParam.mDevName); //stContext.mConfigParam.mDevName = NULL; AW_MPI_VO_OpenVideoLayer(pContext->mUILayer); /* open ui layer. */ AW_MPI_VO_DisableVideoLayer(pContext->mVoLayer); pContext->mVoLayer = MM_INVALID_LAYER; if(pContext->mConfigParam.mbDecodeSubOutEnable) { AW_MPI_VO_DisableVideoLayer(pContext->mSubVoLayer); pContext->mSubVoLayer = MM_INVALID_LAYER; } AW_MPI_VO_RemoveOutsideVideoLayer(pContext->mUILayer); /* disalbe vo dev */ AW_MPI_VO_Disable(pContext->mVoDev); pContext->mVoDev = MM_INVALID_DEV; AW_MPI_SYS_Exit(); if(pContext->mHoldFrameNum != 0) { aloge("fatal error! why holdframe num[%d] != 0?", pContext->mHoldFrameNum); } alogd("vdec buffer number is [%d]", pContext->mValidDoubleFrameBufferNum); int i; for(i=0;i<pContext->mValidDoubleFrameBufferNum;i++) { alogd("vdec buffer[%d] id =[%d]", i, pContext->mDoubleFrameArray[i].mMainFrame.mId); } _exit: destroySampleUvc2VdecVoContext(pContext); free(pContext); alogd("%s test result: %s", argv[0], ((0 == result) ? "success" : "fail")); return result; } -

回复: repo 拉取代码不正常发布在 代码下载问题专区

https://storage.googleapis.com/ 这个网址是谷歌官方源,由于众所周知的原因国内无法访问,请使用国内镜像源代替,另外,安装repo需要Python3环境,使用 sudo apt install python3 安装

$ mkdir -p ~/.bin $ PATH="${HOME}/.bin:${PATH}" $ curl https://mirrors.bfsu.edu.cn/git/git-repo > ~/.bin/repo $ chmod a+rx ~/.bin/repo -

回复: 全志在线开源芯片 新 SDK 平台下载方法汇总发布在 代码下载问题专区

@roshen_007 https://storage.googleapis.com/ 这个网址是谷歌官方源,由于众所周知的原因国内无法访问,请使用国内镜像源代替

$ mkdir -p ~/.bin $ PATH="${HOME}/.bin:${PATH}" $ curl https://mirrors.bfsu.edu.cn/git/git-repo > ~/.bin/repo $ chmod a+rx ~/.bin/repo -

回复: 全志在线开源芯片 新 SDK 平台下载方法汇总发布在 代码下载问题专区

@roshen_007 低功耗参数需要根据实际开发形态来确定,比如是否使用PMU,休眠深度,外设控制参数等等,单独提供芯片的低功耗参数做参考没有意义。

-

回复: 100ASK V853 pro上部署mobilenet发布在 V Series

yolo使用的是RGB格式输入,这里的decode_jpeg仅仅是获取文件大小确定文件是否正确,这个格式取决于你的网络的格式

-

回复: 全志在线开源芯片 新 SDK 平台下载方法汇总发布在 代码下载问题专区

@chrisvista T113-I 的 SDK AWOL 不提供,需要找原厂或代理合作商获取,另外 T113-I 使用的是 Linux 5.4/Linux 5.10 /Linux 5.15/ 三个版本的内核,V853的SDK提供的是 Linux 4.9,不受支持

-

回复: wifi模块延迟高发布在 Wireless & Analog Series

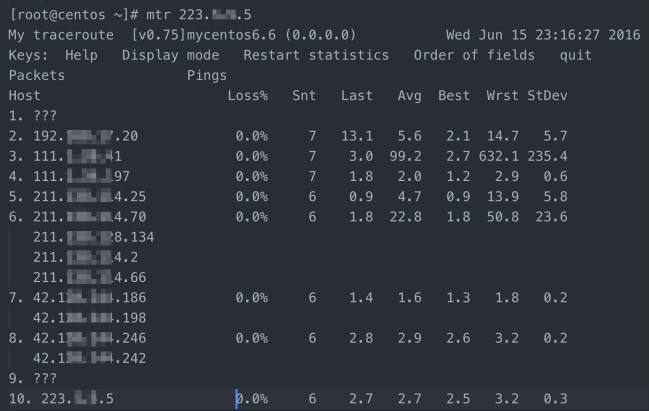

@nlj_moon 检查系统是否存在大量占用CPU时间的程序,也可以通过MTR等工具进行链路测试来判断问题来源。

1.MTR基本信息

MTR(My traceroute)是几乎所有Linux发行版本预装的网络测试工具,此工具也有对应的Windows版本,名称为WinMTR。

MTR工具将ping和traceroute命令的功能并入了同一个工具中,实现更强大的功能。

Linux版本的mtr命令默认发送ICMP数据包进行链路探测。可以通过“-u”参数来指定使用UDP数据包用于探测。

相对于traceroute命令只会做一次链路跟踪测试,mtr命令会对链路上的相关节点做持续探测并给出相应的统计信息。所以,mtr命令能避免节点波动对测试结果的影响,所以其测试结果更正确,建议优先使用。

2.MTR使用方法

在Linux系统上使用

用法说明mtr [-hvrctglspni46] [-help] [-version] [-report] [-report-cycles=COUNT] [-curses] [-gtk] [-raw] [-split] [-no-dns] [-address interface] [-psize=bytes/-s bytes] [-interval=SECONDS] HOSTNAME [PACKETSIZE]常见可选参数说明:

-r 或 -report:以报告模式显示输出。 -p 或 -split:将每次追踪的结果分别列出来。 -s 或 -psize:指定ping数据包的大小。 -n 或 -no-dns:不对IP地址做域名反解析。 -a 或 -address:设置发送数据包的IP地址。用于主机有多个IP时。 -4:只使用IPv4协议。 -6:只使用IPv6协议。 另外,也可以在mtr命令运行过程中,输入相应字母来快速切换模式。 ?或 h:显示帮助菜单。 d:切换显示模式。 n:切换启用或禁用DNS域名解析。 u:切换使用ICMP或UDP数据包进行探测。3.示例输出

默认配置下,返回结果中各数据列的说明如下。

第一列(Host):节点IP地址和域名。如前面所示,按n键可以切换显示。

第二列(Loss%):节点丢包率。

第三列(Snt):每秒发送数据包数。默认值是10,可以通过参数“-c”指定。

第四列(Last):最近一次的探测延迟值。

第五、六、七列(Avg、Best、Wrst):分别是探测延迟的平均值、最小值和最大值。

第八列(StDev):标准偏差。越大说明相应节点越不稳定。 -

回复: T113-S3 LONGAN SDC2接XR829 内核无法启动发布在 Linux

@shanhai8372 SDC2使用的是v4p6x驱动,这个驱动是eMMC专用的,WIFI请使用v5p3x 驱动

-

回复: D1s 无法从EMMC启动发布在 MR Series

@lvjun0728 在 D1s 无法从EMMC启动 中说:

[ 2.145275] sunxi-mmc 4022000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B

从这里可以看出,挂载文件系统的时候eMMC的时序还没有配置好。

D1s的没试过eMMC,D1测试可以使用,并从eMMC启动。两个芯片仅为封装不同,核心一样的

-

回复: D1s 无法从EMMC启动发布在 MR Series

@lvjun0728 在 D1s 无法从EMMC启动 中说:

[ 2.215965] VFS: Cannot open root device "mmcblk0p5" or unknown-block(0,0): error -6

emmc应该是mmcblk2

-

回复: T507的SPI Flash设备,解析分区时出现错误,解析sunxi_gpt(GUID Partition Table)失败。发布在 其它全志芯片讨论区

m25p80 是 NOR Flash,需要勾选mtd设备,spi设备驱动,如果不从 SPI Flash 启动需要手动格式化 NOR Flash,如果需要从 SPI Flash 启动需要配置mtd,jffs2这些

-

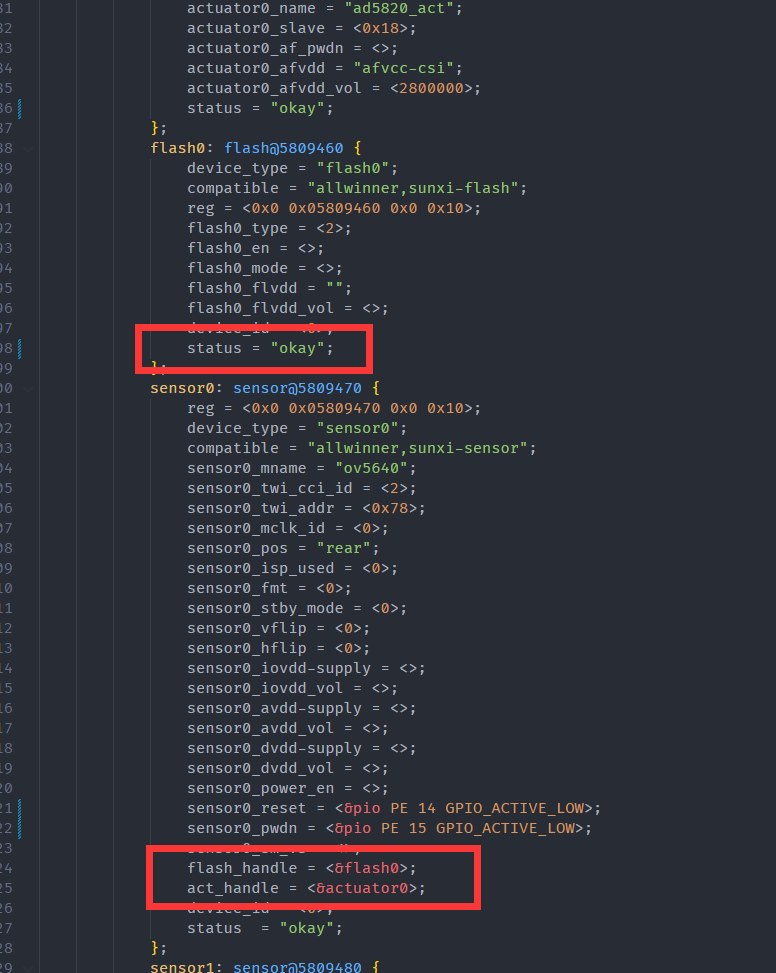

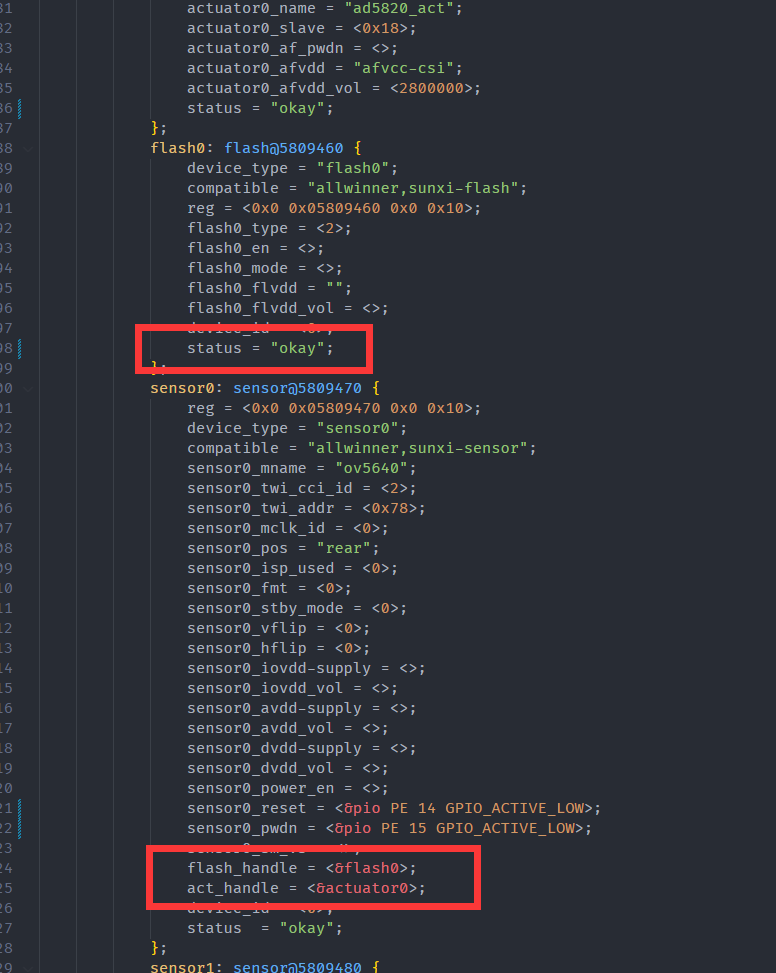

回复: 全志T113-s3使用ov5640加载insmod vin_v4l2.ko报错发布在 MR Series

D1-H (MQ-Pro)驱动 OV5640 摄像头

https://bbs.aw-ol.com/topic/4017/share/1 -

回复: T113驱动ov5640 报错发布在 其它全志芯片讨论区

D1-H (MQ-Pro)驱动 OV5640 摄像头

https://bbs.aw-ol.com/topic/4017/share/1 -

回复: D1H 使用OV5640 报错发布在 MR Series

D1-H (MQ-Pro)驱动 OV5640 摄像头

https://bbs.aw-ol.com/topic/4017/share/1 -

回复: T113 ov5640加载驱动报错,PE11申请不到,被占用了。发布在 Linux

D1-H (MQ-Pro)驱动 OV5640 摄像头

https://bbs.aw-ol.com/topic/4017/share/1 -

回复: 柚木PI蜥蜴 V851S MPP sample rtsp 运行不了发布在 V Series

@aw2022 在 柚木PI蜥蜴 V851S MPP sample rtsp 运行不了 中说:

iniparser: cannot open /etc/cedarx.conf

iniparser: cannot open /vendor/etc/cedarx.conf缺少编码器的配置文件,需要复制一份到指定位置

-

回复: D1芯片无法启动发布在 MR Series

@furyfangyu 在 无法启动 中说:

[205]error:bad checksum.

[209]error:bad magic.

[211]Loading boot-pkg fail(error=4)刷写的固件有问题,magic头错误了

-

回复: 导出yolact模型时报错发布在 V Series

@yzr1992 那就用这个链接

IDE v5.7.1: https://netstorage.allwinnertech.com:5001/sharing/9gbytImwj

pwd:allwinnertech -

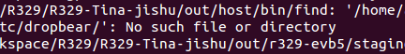

回复: V853s 如何将dropbear服务编译到文件系统发布在 V Series

参考 OpenWRT 说明配置 dropbear 服务

https://openwrt.org/docs/guide-user/base-system/dropbear可以看到 dropbear 由 luci 管理,可能需要增加 luci 服务才可以运行

推荐使用 openssh 替代 dropbear