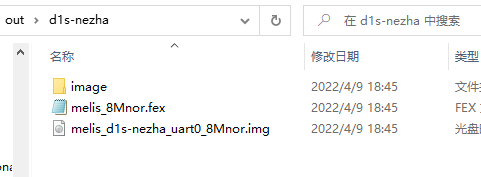

烧录教程

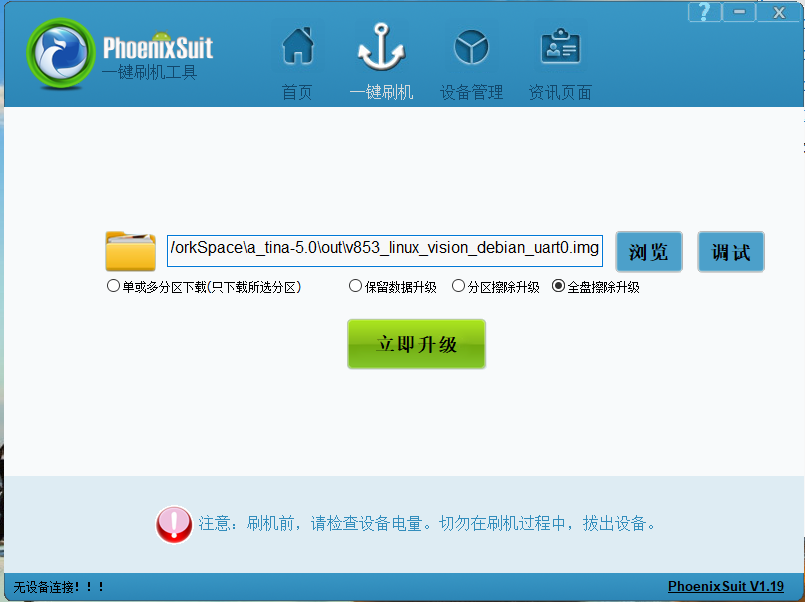

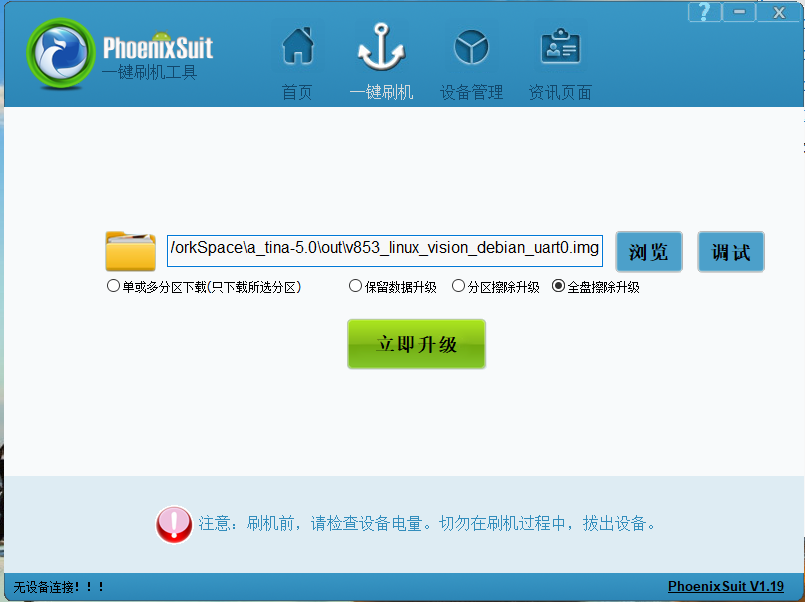

线刷固件:

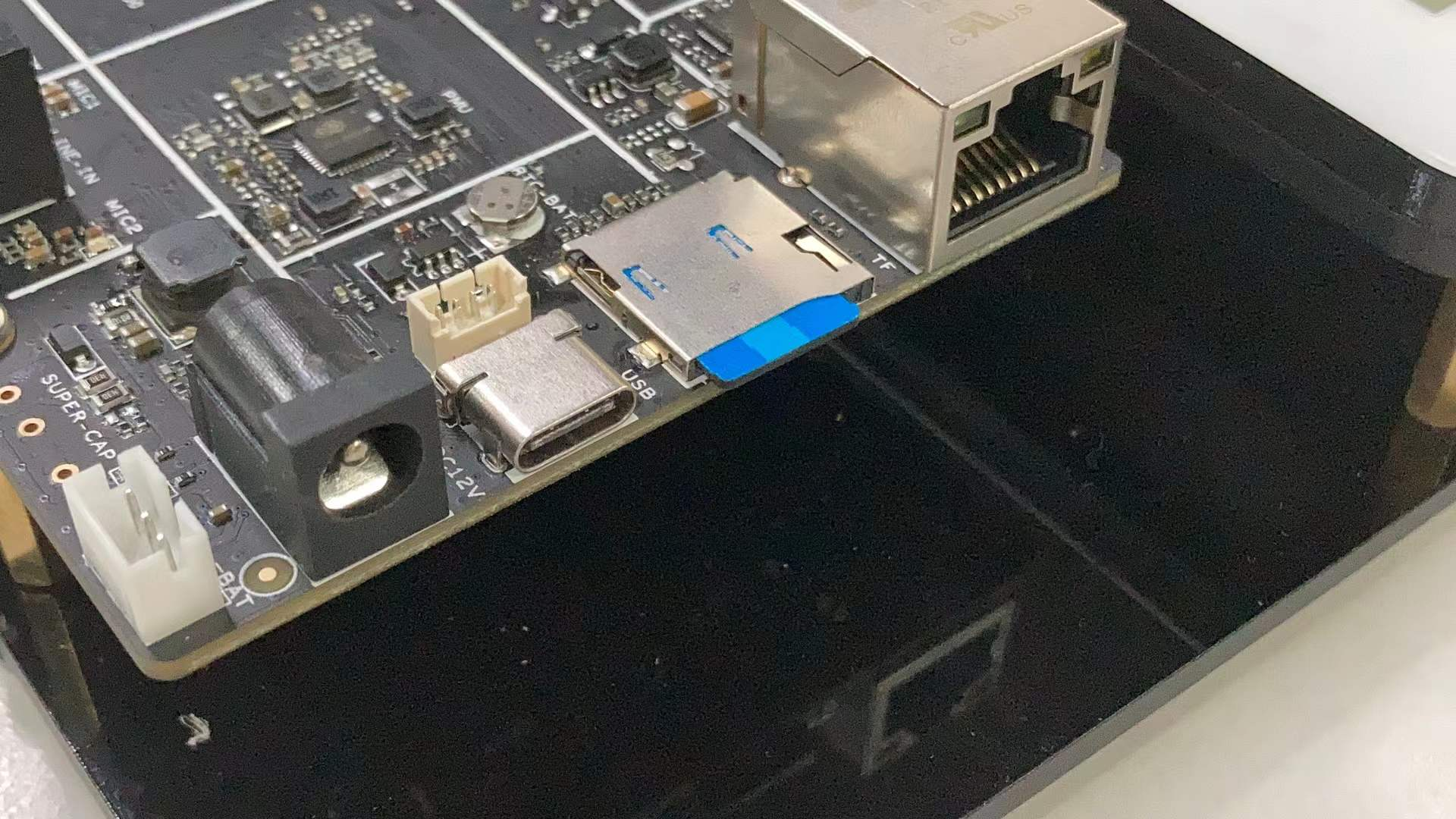

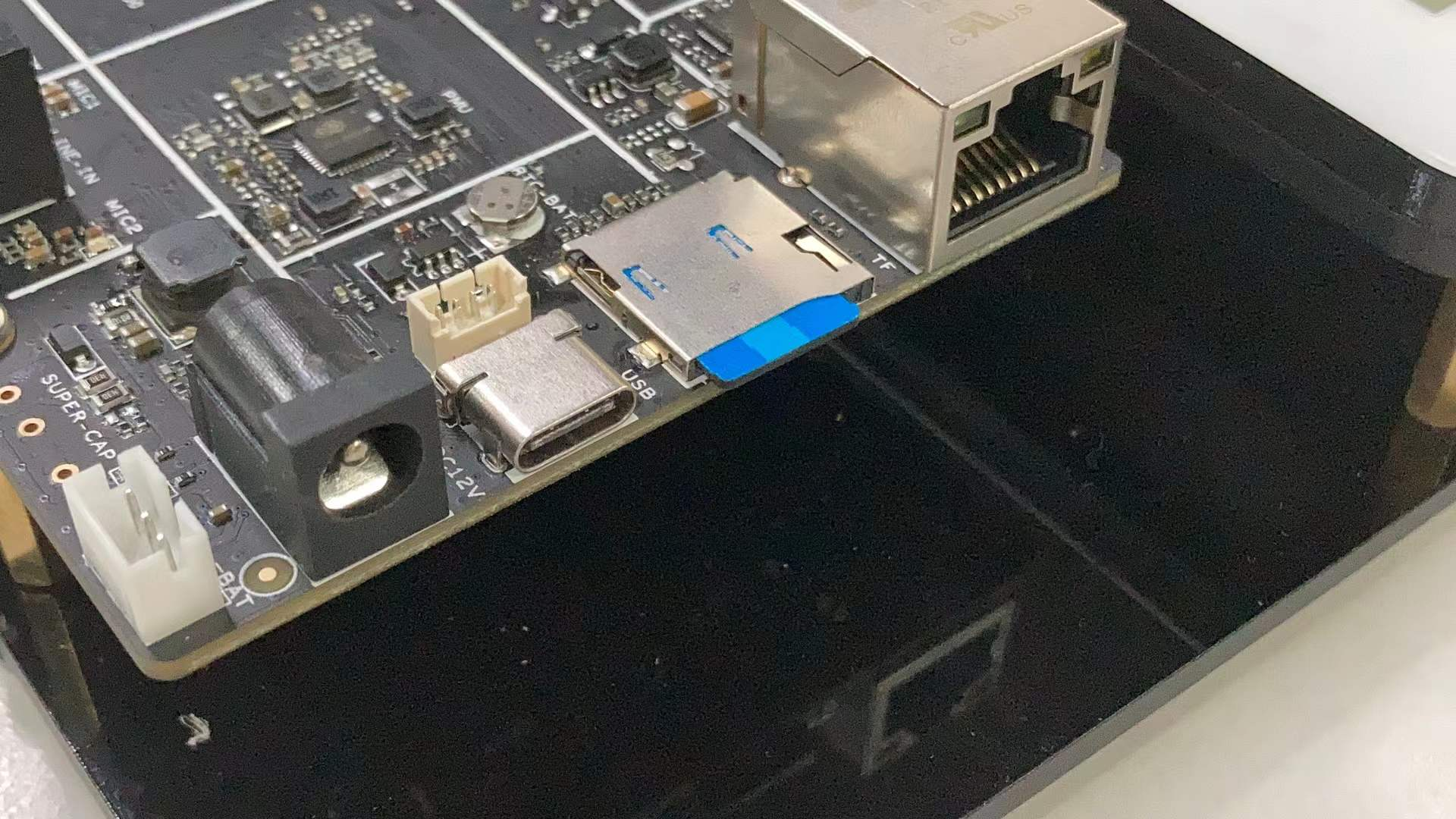

1) 插入格式化好的 SD 卡(不论线刷还是卡刷)

2)使用 PhoenixSuit 刷机即可

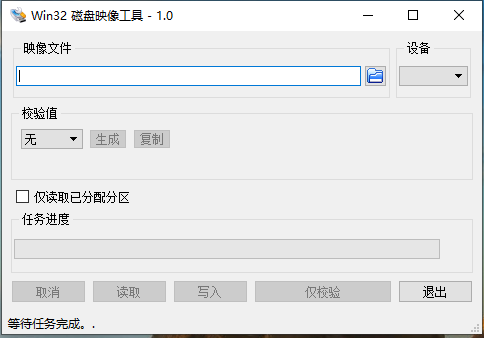

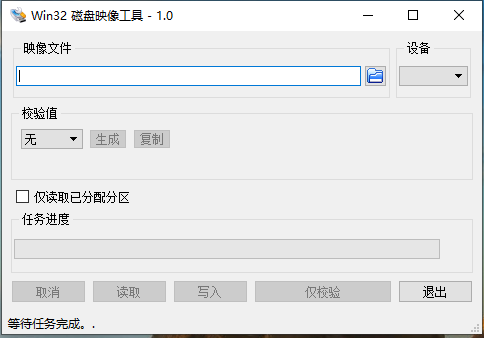

卡刷固件:

1)使用 Win32diskimager、etcher等软件 刷卡后插入开发板上电启动

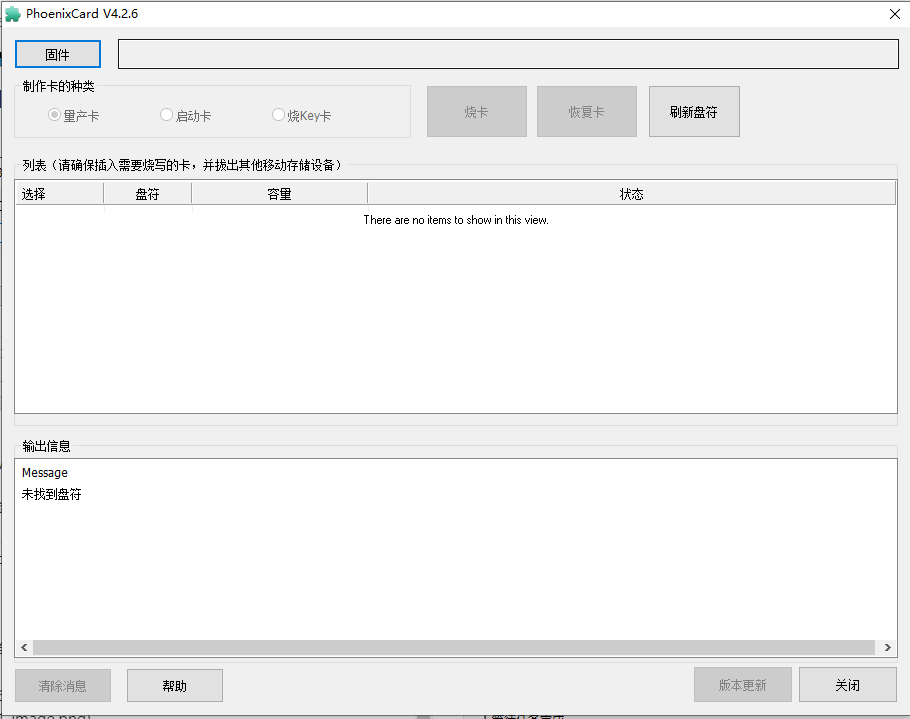

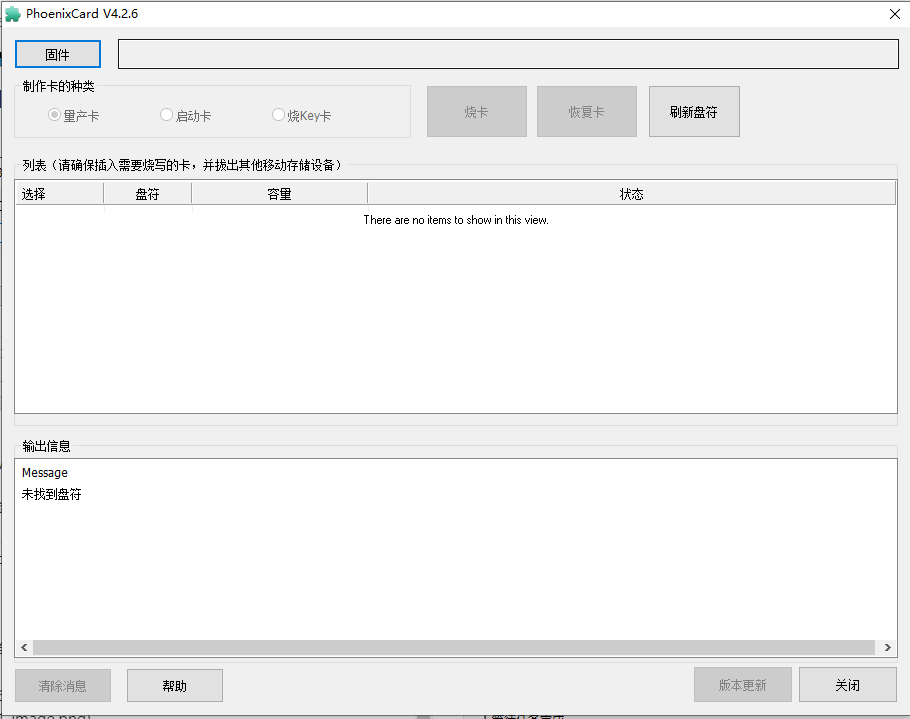

PhoenixCard固件:

1)使用 PhoenixCard 刷卡后插入开发板上电启动

修复叻,手残打开了Boot Time Optimization

#

# Boot Time Optimization

#

# CONFIG_BOOT_TIME_OPTIMIZATION is not set

测试镜像:

百度云:链接:https://pan.baidu.com/s/1dPSaKJQrOMy8X1Xs_604Dw 提取码:awol

奶牛快传:https://cowtransfer.com/s/76711e52ad304f 或 打开【奶牛快传】cowtransfer.com 使用传输口令:gl9jyq 提取;

串口是PE2,PE3

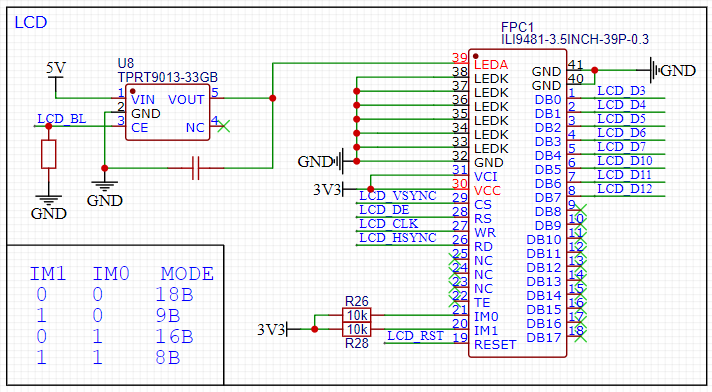

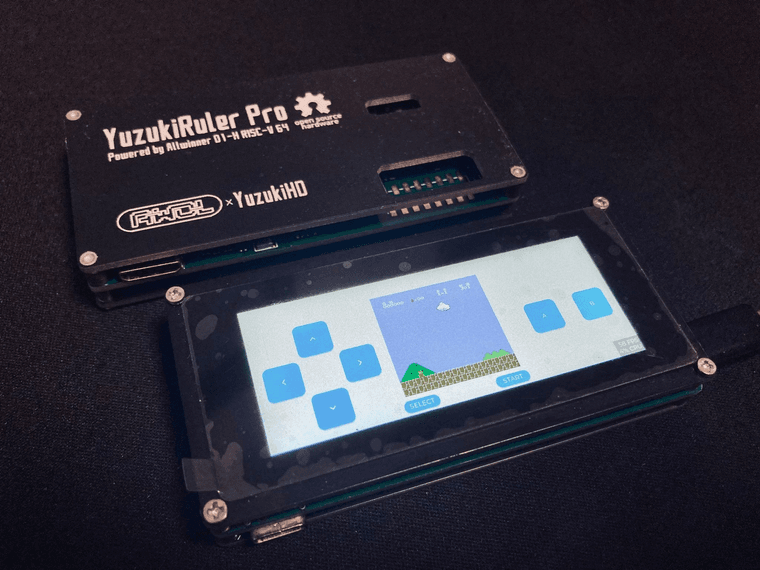

V831没有RGB也没有MIPI,正好手上有几片i80 MCU屏幕可以用(320*480 3.5寸的,15块钱一片)

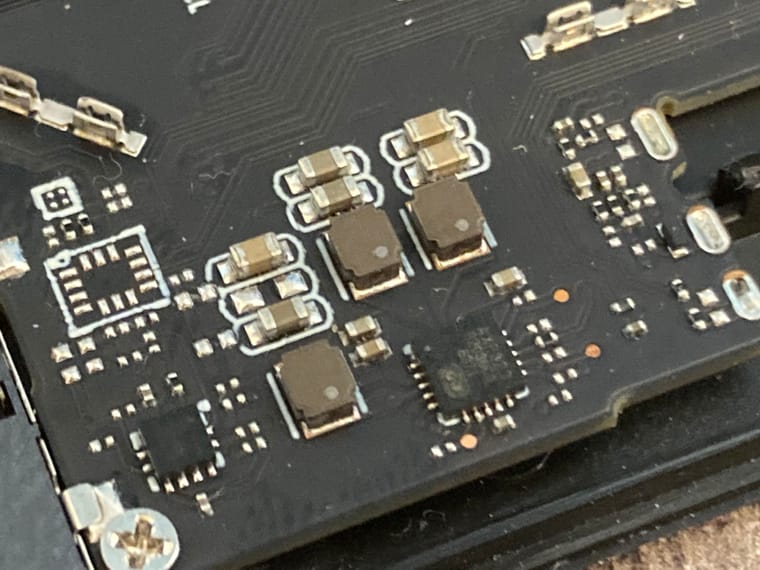

屏幕部分:

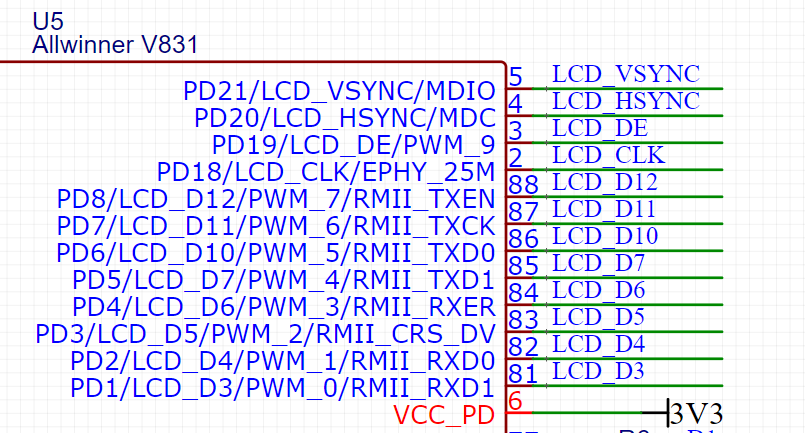

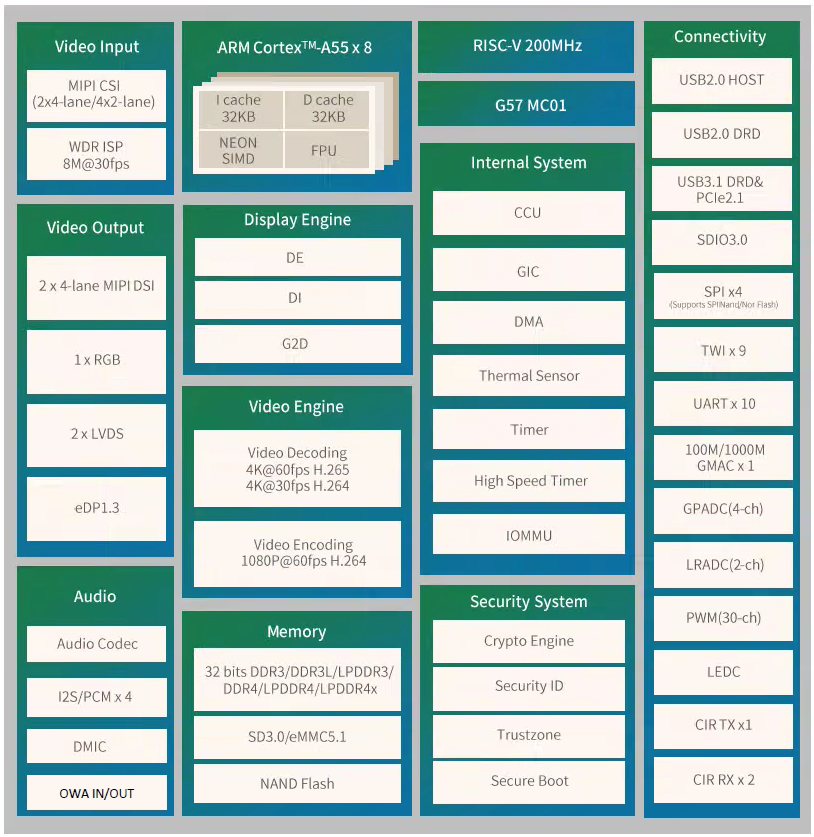

主控部分:

没啥好说的,照着Sipeed的抄就行了

lcd0: lcd0@01c0c000 {

lcd_used = <1>;

lcd_driver_name = "ili9481";

lcd_x = <320>;

lcd_y = <480>;

lcd_width = <108>;

lcd_height = <64>;

lcd_dclk_freq = <5>;

lcd_pwm_used = <0>;

lcd_hbp = <20>;

lcd_ht = <382>;

lcd_hspw = <2>;

lcd_vbp = <2>; // 320

lcd_vt = <486>; // 320

lcd_vspw = <2>;

lcd_if = <1>;

lcd_frm = <2>;

lcd_cpu_mode = <1>;

lcd_cpu_te = <0>;

lcd_cpu_if = <14>;

lcd_io_phase = <0x0000>;

lcdgamma4iep = <22>;

lcd_gamma_en = <0>;

lcd_cmap_en = <0>;

lcd_bright_curve_en = <0>;

lcd_rb_swap = <0>;

lcd_gpio_0 = <&pio PH 5 1 0 3 0>; /* rst */

lcd_gpio_1 = <&pio PD 21 1 0 3 0>; /* cs */

lcd_bl_en = <&pio PH 6 1 0 3 1>;

pinctrl-0 = <&rgb8_pins_a>;

pinctrl-1 = <&rgb8_pins_b>;

};

因为这里用的是Kernel刷屏,所以就不配uboot的了

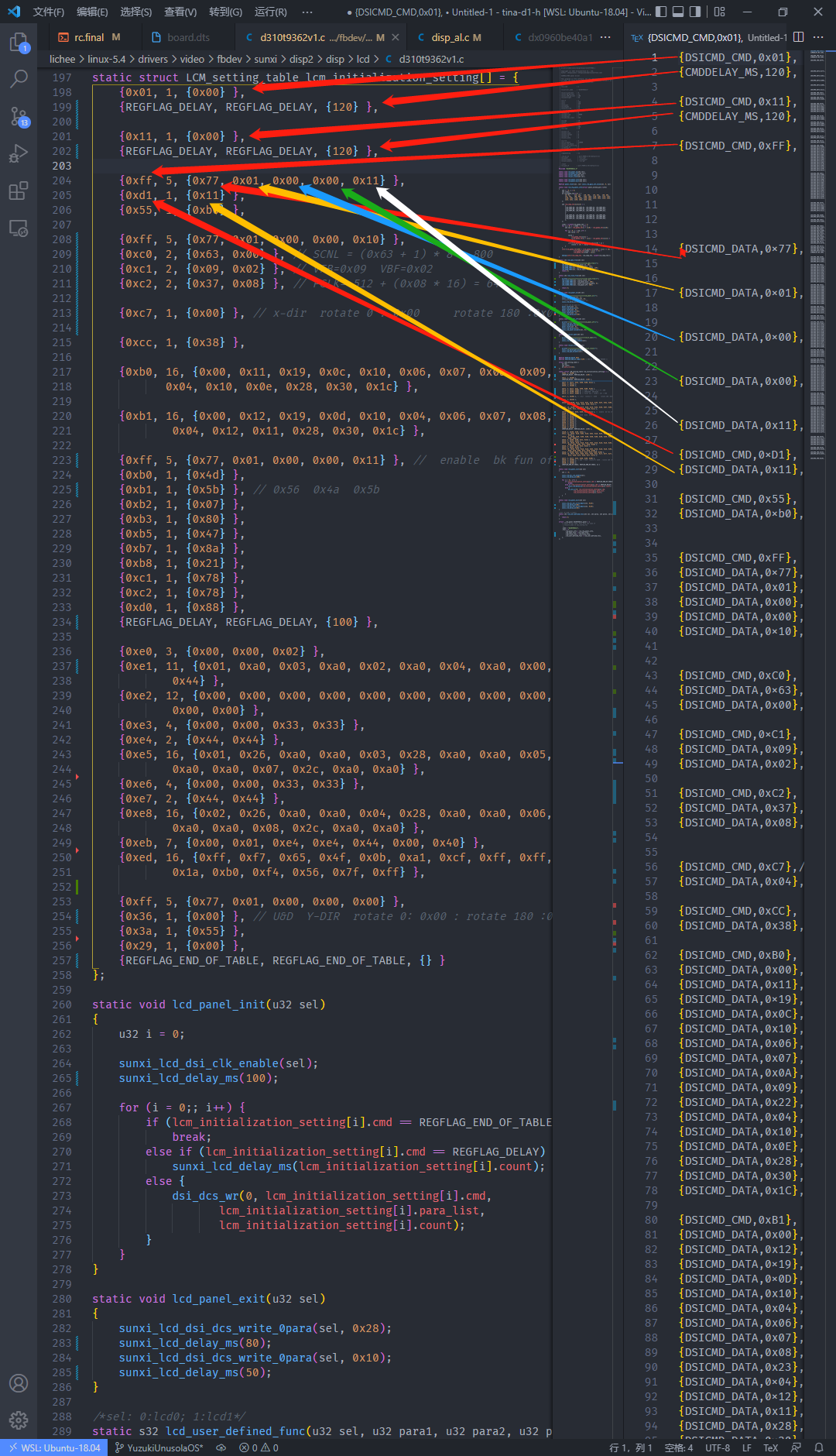

然后找大佬鼠嫖驱动,放到 lichee/linux-4.9/drivers/video/fbdev/sunxi/disp2/disp/lcd/文件夹下。

编辑 lichee/linux-4.9/drivers/video/fbdev/sunxi/disp2/disp/lcd/panels.c,找一个顺眼的地方加一下配置。

#ifdef CONFIG_LCD_SUPPORT_ILI9481

&ili9481_panel,

#endif

编辑lichee/linux-4.9/drivers/video/fbdev/sunxi/disp2/disp/lcd/panels.h,找一个顺眼的地方加一下配置。

#ifdef CONFIG_LCD_SUPPORT_ILI9481

extern struct __lcd_panel ili9481_panel;

#endif

编辑lichee/linux-4.9/drivers/video/fbdev/sunxi/disp2/disp/lcd/Kconfig,找一个顺眼的地方加一下配置。

config LCD_SUPPORT_ILI9481

bool "LCD support ili9481 panel"

default n

---help---

If you want to support ili9481 panel for display driver, select it.

编辑 lichee/linux-4.9/drivers/video/fbdev/sunxi/disp2/disp/Makefile,找一个顺眼的地方加一下配置。

disp-$(CONFIG_LCD_SUPPORT_ILI9481) += lcd/ili9481.o

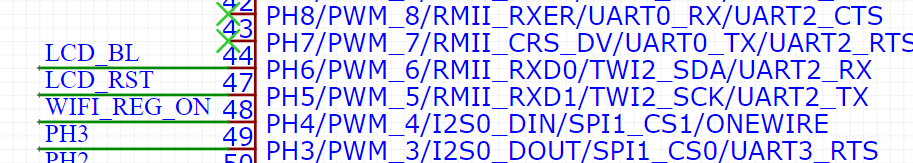

再打开 m kernel_menuconfig

Device Drivers --->

Graphics support --->

Frame buffer Devices --->

Video support for sunxi --->

LCD panels select --->

[*] LCD support ili9481 panel

保存,编译kernel打包就好了。

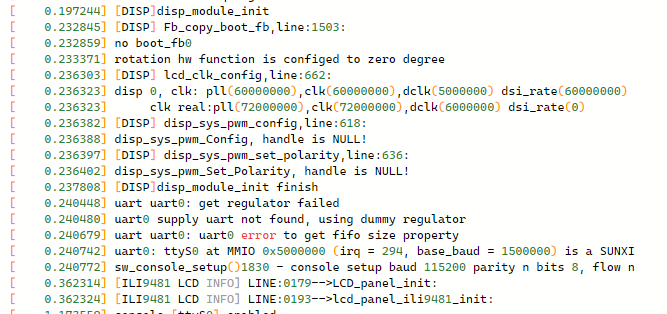

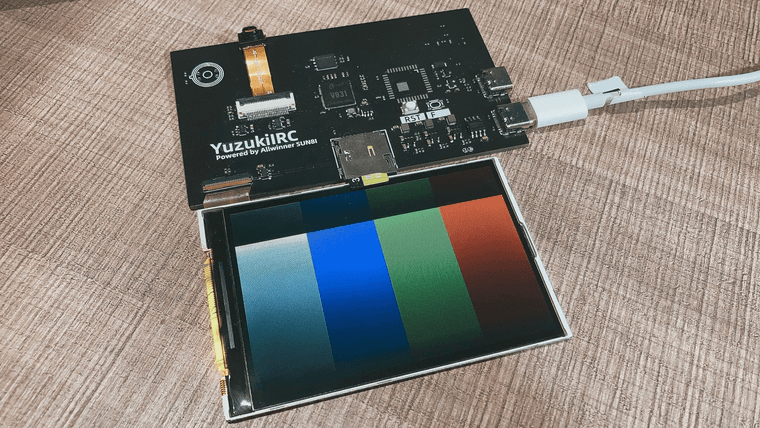

刷卡,启动系统,可以看到屏幕背光已经亮了。

测试一下

echo 1 > sys/class/disp/disp/attr/colorbar

驱动和配置已经上传Github,自取

可以,详见:D1咋把控制台弄到hdmi上呢?

https://bbs.aw-ol.com/topic/1320/share/4

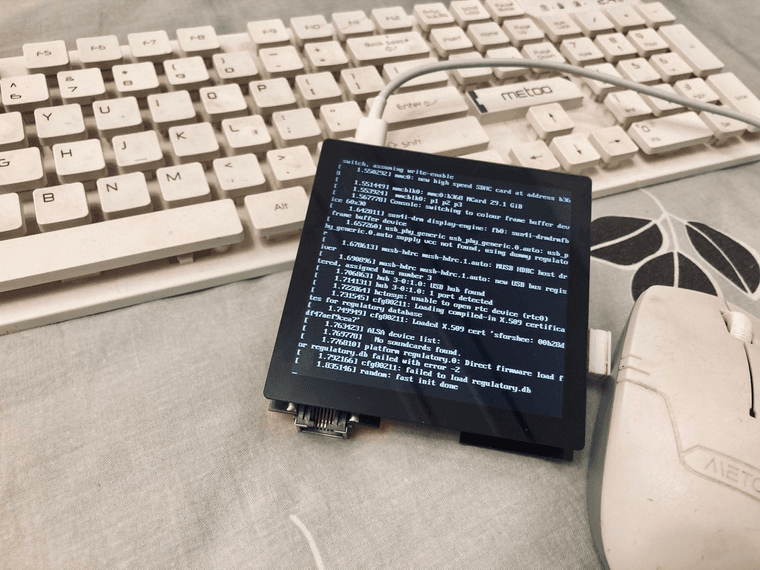

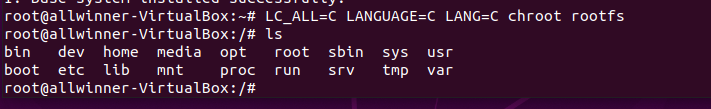

串口可以输入了。抓到完整的设备树

/ {

model = "sun50iw10";

compatible = "allwinner,a100", "arm,sun50iw10p1";

interrupt-parent = <0x00000001>;

#address-cells = <0x00000002>;

#size-cells = <0x00000002>;

clocks {

compatible = "allwinner,clk-init";

device_type = "clocks";

#address-cells = <0x00000002>;

#size-cells = <0x00000002>;

ranges;

reg = <0x00000000 0x03001000 0x00000000 0x00001000 0x00000000 0x07010000 0x00000000 0x00000400 0x00000000 0x07000000 0x00000000 0x00000004>;

losc {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-clock";

clock-frequency = <0x00008000>;

clock-output-names = "losc";

phandle = <0x000000b3>;

};

iosc {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-clock";

clock-frequency = "", ".$";

clock-output-names = "iosc";

phandle = <0x000000b4>;

};

hosc {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-clock";

clock-frequency = <0x016e3600>;

clock-output-names = "hosc";

phandle = <0x0000000a>;

};

osc48m {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-clock";

clock-frequency = <0x02dc6c00>;

clock-output-names = "osc48m";

phandle = <0x0000000b>;

};

hoscdiv32k {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-clock";

clock-frequency = <0x00008000>;

clock-output-names = "hoscdiv32k";

phandle = <0x000000b5>;

};

pll_periph0div25m {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-clock";

clock-frequency = <0x017d7840>;

clock-output-names = "pll_periph0div25m";

phandle = <0x000000b6>;

};

pll_cpu {

#clock-cells = <0x00000000>;

compatible = "allwinner,pll-clock";

lock-mode = "new";

clock-output-names = "pll_cpu";

phandle = <0x000000b7>;

};

pll_ddr {

#clock-cells = <0x00000000>;

compatible = "allwinner,pll-clock";

lock-mode = "new";

clock-output-names = "pll_ddr";

phandle = <0x000000b8>;

};

pll_periph0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,pll-clock";

assigned-clock-rates = "#.F";

lock-mode = "new";

clock-output-names = "pll_periph0";

phandle = <0x00000006>;

};

pll_periph1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,pll-clock";

assigned-clock-rates = "#.F";

lock-mode = "new";

clock-output-names = "pll_periph1";

phandle = <0x00000007>;

};

pll_gpu {

#clock-cells = <0x00000000>;

compatible = "allwinner,pll-clock";

lock-mode = "new";

clock-output-names = "pll_gpu";

phandle = <0x000000b9>;

};

pll_video0x4 {

#clock-cells = <0x00000000>;

compatible = "allwinner,pll-clock";

lock-mode = "new";

clock-output-names = "pll_video0x4";

phandle = <0x00000008>;

};

pll_video1x4 {

#clock-cells = <0x00000000>;

compatible = "allwinner,pll-clock";

lock-mode = "new";

clock-output-names = "pll_video1x4";

phandle = <0x00000009>;

};

pll_video2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,pll-clock";

lock-mode = "new";

assigned-clocks = <0x00000002>;

assigned-clock-rates = <0x1406f400>;

clock-output-names = "pll_video2";

phandle = <0x00000002>;

};

pll_video3 {

#clock-cells = <0x00000000>;

compatible = "allwinner,pll-clock";

lock-mode = "new";

assigned-clocks = <0x00000003>;

assigned-clock-rates = <0x11e1a300>;

clock-output-names = "pll_video3";

phandle = <0x00000003>;

};

pll_ve {

#clock-cells = <0x00000000>;

compatible = "allwinner,pll-clock";

device_type = "clk_pll_ve";

lock-mode = "new";

clock-output-names = "pll_ve";

phandle = <0x000000ba>;

};

pll_com {

#clock-cells = <0x00000000>;

compatible = "allwinner,pll-clock";

assigned-clocks = <0x00000004>;

assigned-clock-rates = "#.F";

lock-mode = "new";

clock-output-names = "pll_com";

phandle = <0x00000004>;

};

pll_audiox4 {

#clock-cells = <0x00000000>;

compatible = "allwinner,pll-clock";

assigned-clocks = <0x00000005>;

assigned-clock-rates = <0x05dc0000>;

lock-mode = "new";

clock-output-names = "pll_audiox4";

phandle = <0x00000005>;

};

pll_periph0x2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000006>;

clock-mult = <0x00000002>;

clock-div = <0x00000001>;

clock-output-names = "pll_periph0x2";

phandle = <0x0000000c>;

};

pll_periph0x4 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000006>;

clock-mult = <0x00000004>;

clock-div = <0x00000001>;

clock-output-names = "pll_periph0x4";

phandle = <0x000000bb>;

};

periph32k {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000006>;

clock-mult = <0x00000002>;

clock-div = <0x00008f0d>;

clock-output-names = "periph32k";

phandle = <0x000000bc>;

};

pll_periph1x2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000007>;

clock-mult = <0x00000002>;

clock-div = <0x00000001>;

clock-output-names = "pll_periph1x2";

phandle = <0x000000bd>;

};

pll_comdiv5 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000004>;

clock-mult = <0x00000001>;

clock-div = <0x00000005>;

clock-output-names = "pll_comdiv5";

phandle = <0x000000be>;

};

pll_audiox8 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000005>;

clock-mult = <0x00000002>;

clock-div = <0x00000001>;

clock-output-names = "pll_audiox8";

phandle = <0x000000bf>;

};

pll_audio {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000005>;

clock-mult = <0x00000001>;

clock-div = <0x00000004>;

clock-output-names = "pll_audio";

phandle = <0x000000c0>;

};

pll_audiox2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000005>;

clock-mult = <0x00000001>;

clock-div = <0x00000002>;

clock-output-names = "pll_audiox2";

phandle = <0x000000c1>;

};

pll_video0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000008>;

clock-mult = <0x00000001>;

clock-div = <0x00000004>;

clock-output-names = "pll_video0";

phandle = <0x000000c2>;

};

pll_video0x2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000008>;

clock-mult = <0x00000001>;

clock-div = <0x00000002>;

clock-output-names = "pll_video0x2";

phandle = <0x000000c3>;

};

pll_video1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000009>;

clock-mult = <0x00000001>;

clock-div = <0x00000004>;

clock-output-names = "pll_video1";

phandle = <0x000000c4>;

};

pll_video1x2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000009>;

clock-mult = <0x00000001>;

clock-div = <0x00000002>;

clock-output-names = "pll_video1x2";

phandle = <0x000000c5>;

};

pll_video2x2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000002>;

clock-mult = <0x00000002>;

clock-div = <0x00000001>;

clock-output-names = "pll_video2x2";

phandle = <0x000000c6>;

};

pll_video2x4 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000002>;

clock-mult = <0x00000004>;

clock-div = <0x00000001>;

clock-output-names = "pll_video2x4";

phandle = <0x000000c7>;

};

pll_video3x2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000003>;

clock-mult = <0x00000002>;

clock-div = <0x00000001>;

clock-output-names = "pll_video3x2";

phandle = <0x000000c8>;

};

pll_video3x4 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000003>;

clock-mult = <0x00000004>;

clock-div = <0x00000001>;

clock-output-names = "pll_video3x4";

phandle = <0x000000c9>;

};

hoscd2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x0000000a>;

clock-mult = <0x00000001>;

clock-div = <0x00000002>;

clock-output-names = "hoscd2";

phandle = <0x000000ca>;

};

osc48md4 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x0000000b>;

clock-mult = <0x00000001>;

clock-div = <0x00000004>;

clock-output-names = "osc48md4";

phandle = <0x000000cb>;

};

pll_periph0d6 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000006>;

clock-mult = <0x00000001>;

clock-div = <0x00000006>;

clock-output-names = "pll_periph0d6";

phandle = <0x000000cc>;

};

cpu {

#clock-cells = <0x00000000>;

compatible = "allwinner,cpu-clock";

clock-output-names = "cpu";

phandle = <0x000000cd>;

};

axi {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "axi";

phandle = <0x000000ce>;

};

cpuapb {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "cpuapb";

phandle = <0x000000cf>;

};

psi {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "psi";

phandle = <0x000000d0>;

};

ahb1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "ahb1";

phandle = <0x000000d1>;

};

ahb2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "ahb2";

phandle = <0x000000d2>;

};

ahb3 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "ahb3";

phandle = <0x000000d3>;

};

apb1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "apb1";

phandle = <0x000000d4>;

};

apb2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "apb2";

phandle = <0x000000d5>;

};

de0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

assigned-clock-parents = <0x0000000c>;

assigned-clock-rates = <0x11e1a300>;

assigned-clocks = <0x0000000d>;

clock-output-names = "de0";

phandle = <0x0000000d>;

};

de1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

assigned-clock-parents = <0x0000000c>;

assigned-clock-rates = <0x11e1a300>;

assigned-clocks = <0x0000000e>;

clock-output-names = "de1";

phandle = <0x0000000e>;

};

g2d {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "g2d";

assigned-clock-parents = <0x0000000c>;

assigned-clock-rates = <0x11e1a300>;

assigned-clocks = <0x0000000f>;

phandle = <0x0000000f>;

};

ee {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

assigned-clock-parents = <0x0000000c>;

assigned-clock-rates = <0x11e1a300>;

assigned-clocks = <0x00000010>;

clock-output-names = "ee";

phandle = <0x00000010>;

};

panel {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

assigned-clock-parents = <0x00000002>;

assigned-clock-rates = <0x01c9c380>;

assigned-clocks = <0x00000011>;

clock-output-names = "panel";

phandle = <0x00000011>;

};

gpu {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "gpu";

phandle = <0x000000d6>;

};

ce {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "ce";

phandle = <0x000000d7>;

};

ve {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "ve";

phandle = <0x000000d8>;

};

dma {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "dma";

phandle = <0x000000d9>;

};

msgbox {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "msgbox";

phandle = <0x000000da>;

};

hwspinlock_rst {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "hwspinlock_rst";

phandle = <0x000000db>;

};

hwspinlock_bus {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "hwspinlock_bus";

phandle = <0x000000dc>;

};

hstimer {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "hstimer";

phandle = <0x000000dd>;

};

avs {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "avs";

phandle = <0x000000de>;

};

dbgsys {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "dbgsys";

phandle = <0x000000df>;

};

pwm {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "pwm";

phandle = <0x000000e0>;

};

iommu {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "iommu";

phandle = <0x000000e1>;

};

nand0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "nand0";

phandle = <0x000000e2>;

};

nand1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "nand1";

phandle = <0x000000e3>;

};

sdmmc0_mod {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "sdmmc0_mod";

phandle = <0x000000e4>;

};

sdmmc0_bus {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "sdmmc0_bus";

phandle = <0x000000e5>;

};

sdmmc0_rst {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "sdmmc0_rst";

phandle = <0x000000e6>;

};

sdmmc1_mod {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "sdmmc1_mod";

phandle = <0x000000e7>;

};

sdmmc1_bus {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "sdmmc1_bus";

phandle = <0x000000e8>;

};

sdmmc1_rst {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "sdmmc1_rst";

phandle = <0x000000e9>;

};

sdmmc2_mod {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "sdmmc2_mod";

phandle = <0x000000ea>;

};

sdmmc2_bus {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "sdmmc2_bus";

phandle = <0x000000eb>;

};

sdmmc2_rst {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "sdmmc2_rst";

phandle = <0x000000ec>;

};

uart0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "uart0";

phandle = <0x000000ed>;

};

uart1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "uart1";

phandle = <0x000000ee>;

};

uart2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "uart2";

phandle = <0x000000ef>;

};

uart3 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "uart3";

phandle = <0x000000f0>;

};

uart4 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "uart4";

phandle = <0x000000f1>;

};

uart5 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "uart5";

phandle = <0x000000f2>;

};

uart6 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "uart6";

phandle = <0x000000f3>;

};

scr0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "scr0";

phandle = <0x000000f4>;

};

gmac0_25m {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "gmac0_25m";

phandle = <0x000000f5>;

};

gmac1_25m {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "gmac1_25m";

phandle = <0x000000f6>;

};

gmac0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "gmac0";

phandle = <0x000000f7>;

};

gmac1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "gmac1";

phandle = <0x000000f8>;

};

gpadc {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "gpadc";

phandle = <0x000000f9>;

};

irtx {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "irtx";

phandle = <0x000000fa>;

};

ths {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "ths";

phandle = <0x000000fb>;

};

i2s0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "i2s0";

phandle = <0x000000fc>;

};

i2s1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "i2s1";

phandle = <0x000000fd>;

};

i2s2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "i2s2";

phandle = <0x000000fe>;

};

i2s3 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "i2s3";

phandle = <0x000000ff>;

};

spdif {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "spdif";

phandle = <0x00000100>;

};

dmic {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "dmic";

phandle = <0x00000101>;

};

codec_dac_1x {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "codec_dac_1x";

phandle = <0x00000102>;

};

codec_adc_1x {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "codec_adc_1x";

phandle = <0x00000103>;

};

codec_4x {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "codec_4x";

phandle = <0x00000104>;

};

usbphy0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "usbphy0";

phandle = <0x00000105>;

};

usbphy1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "usbphy1";

phandle = <0x00000106>;

};

usbohci0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "usbohci0";

phandle = <0x00000107>;

};

usbohci0_12m {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "usbohci0_12m";

phandle = <0x00000108>;

};

usbohci1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "usbohci1";

phandle = <0x00000109>;

};

usbohci1_12m {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "usbohci1_12m";

phandle = <0x0000010a>;

};

usbehci0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "usbehci0";

phandle = <0x0000010b>;

};

usbehci1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "usbehci1";

phandle = <0x0000010c>;

};

usbotg {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "usbotg";

phandle = <0x0000010d>;

};

display_top {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "display_top";

phandle = <0x00000092>;

};

dpss_top0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "dpss_top0";

phandle = <0x00000093>;

};

dpss_top1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "dpss_top1";

phandle = <0x00000094>;

};

tcon_lcd0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "tcon_lcd0";

assigned-clocks = <0x00000012>;

assigned-clock-parents = <0x00000008>;

phandle = <0x00000012>;

};

tcon_lcd1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "tcon_lcd1";

assigned-clocks = <0x00000013>;

assigned-clock-parents = <0x00000009>;

phandle = <0x00000013>;

};

lvds {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "lvds";

phandle = <0x00000095>;

};

lvds1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "lvds1";

phandle = <0x00000096>;

};

mipi_host {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "mipi_host";

assigned-clocks = <0x00000014>;

assigned-clock-parents = <0x00000006>;

assigned-clock-rates = <0x08f0d180>;

phandle = <0x00000014>;

};

csi_top {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "csi_top";

phandle = <0x0000010e>;

};

csi_isp {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "csi_isp";

phandle = <0x0000010f>;

};

csi_master0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "csi_master0";

phandle = <0x00000110>;

};

csi_master1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "csi_master1";

phandle = <0x00000111>;

};

pio {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "pio";

phandle = <0x00000112>;

};

ledc {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "ledc";

phandle = <0x00000113>;

};

cpurcir {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-cpus-clock";

clock-output-names = "cpurcir";

phandle = <0x00000114>;

};

losc_out {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-cpus-clock";

clock-output-names = "losc_out";

phandle = <0x00000115>;

};

cpurcpus_pll {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-cpus-clock";

clock-output-names = "cpurcpus_pll";

phandle = <0x00000116>;

};

cpurcpus {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-cpus-clock";

clock-output-names = "cpurcpus";

phandle = <0x00000117>;

};

cpurahbs {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-cpus-clock";

clock-output-names = "cpurahbs";

phandle = <0x00000118>;

};

cpurapbs1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-cpus-clock";

clock-output-names = "cpurapbs1";

phandle = <0x00000119>;

};

cpurapbs2_pll {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-cpus-clock";

clock-output-names = "cpurapbs2_pll";

phandle = <0x0000011a>;

};

cpurapbs2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-cpus-clock";

clock-output-names = "cpurapbs2";

phandle = <0x0000011b>;

};

ppu {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-cpus-clock";

clock-output-names = "ppu";

phandle = <0x0000011c>;

};

cpurpio {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-cpus-clock";

clock-output-names = "cpurpio";

phandle = <0x0000011d>;

};

dcxo_out {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-cpus-clock";

clock-output-names = "dcxo_out";

phandle = <0x0000011e>;

};

suart {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-cpus-clock";

clock-output-names = "suart";

phandle = <0x0000011f>;

};

lradc {

#clock-cells = <0x00000000>;

compatible = "allwinner,periph-clock";

clock-output-names = "lradc";

phandle = <0x00000120>;

};

};

aliases {

serial0 = "/soc@2900000/uart@5000000";

serial1 = "/soc@2900000/uart@5000400";

serial2 = "/soc@2900000/uart@5000800";

serial3 = "/soc@2900000/uart@5000c00";

serial4 = "/soc@2900000/uart@5001000";

serial5 = "/soc@2900000/uart@5001400";

serial6 = "/soc@2900000/uart@5001800";

serial7 = "/soc@2900000/uart@7080000";

disp = "/soc@2900000/uboot_disp@06100000";

lcd0 = "/soc@2900000/lcd0@1c0c000";

lcd1 = "/soc@2900000/lcd1@1";

eink = "/soc@2900000/uboot_eink@6400000";

mmc0 = "/soc@2900000/sdmmc@4020000";

mmc2 = "/soc@2900000/sdmmc@4022000";

nand0 = "/soc@2900000/nand0@04011000";

twi0 = "/soc@2900000/twi@5002000";

twi1 = "/soc@2900000/twi@5002400";

twi2 = "/soc@2900000/twi@5002800";

twi3 = "/soc@2900000/twi@5002c00";

twi4 = "/soc@2900000/twi@5003000";

twi5 = "/soc@2900000/twi@5003400";

twi6 = "/soc@2900000/s_twi@7081400";

twi7 = "/soc@2900000/s_twi@7081800";

spi0 = "/soc@2900000/spi@5010000";

spi1 = "/soc@2900000/spi@5011000";

spi2 = "/soc@2900000/spi@5012000";

ledc = "/soc@2900000/ledc@0x5018000";

pwm = "/soc@2900000/pwm@300a000";

pwm0 = "/soc@2900000/pwm0@300a010";

pwm1 = "/soc@2900000/pwm1@300a011";

pwm2 = "/soc@2900000/pwm2@300a012";

pwm3 = "/soc@2900000/pwm3@300a013";

pwm4 = "/soc@2900000/pwm4@300a014";

pwm5 = "/soc@2900000/pwm5@300a015";

pwm6 = "/soc@2900000/pwm6@300a016";

pwm7 = "/soc@2900000/pwm7@300a017";

pwm8 = "/soc@2900000/pwm8@300a018";

pwm9 = "/soc@2900000/pwm9@300a019";

global-timer0 = "/soc@2900000/timer@3009000";

pmu0 = "/soc@2900000/s_twi@7081400/pmu@34";

standby-param = "/soc@2900000/standby_param@7000400";

ctp = "/soc@2900000/twi@5002000/ctp@0";

};

reserved-memory {

#address-cells = <0x00000002>;

#size-cells = <0x00000002>;

ranges;

bl31 {

reg = <0x00000000 0x48000000 0x00000000 0x01000000>;

};

};

chosen {

bootargs = "earlyprintk=sunxi-uart,0x05000000 loglevel=8 initcall_debug=0 console=ttyS0 init=/init";

linux,initrd-start = <0x00000000 0x00000000>;

linux,initrd-end = <0x00000000 0x00000000>;

};

firmware {

android {

compatible = "android,firmware";

boot_devices = "soc@2900000/4020000.sdmmc,soc@2900000/4022000.sdmmc,soc@2900000";

vbmeta {

compatible = "android,vbmeta";

parts = "vbmeta,vbmeta_system,vbmeta_vendor,boot";

};

};

optee {

compatible = "linaro,optee-tz";

method = "smc";

};

};

cpus {

#address-cells = <0x00000002>;

#size-cells = <0x00000000>;

cpu@0 {

device_type = "cpu";

compatible = "arm,cortex-a53", "arm,armv8";

reg = <0x00000000 0x00000000>;

enable-method = "psci";

clocks = <0x00000015 0x00000018>;

clock-latency = <0x001e8480>;

clock-frequency = <0x4ead9a00>;

dynamic-power-coefficient = <0x000000be>;

operating-points-v2 = <0x00000016>;

cpu-idle-states = <0x00000017 0x00000018>;

#cooling-cells = <0x00000002>;

cpu-supply = <0x00000019>;

phandle = <0x0000001f>;

};

cpu@1 {

device_type = "cpu";

compatible = "arm,cortex-a53", "arm,armv8";

reg = <0x00000000 0x00000001>;

enable-method = "psci";

clocks = <0x00000015 0x00000018>;

clock-frequency = <0x4ead9a00>;

operating-points-v2 = <0x00000016>;

cpu-idle-states = <0x00000017 0x00000018>;

#cooling-cells = <0x00000002>;

phandle = <0x00000021>;

};

cpu@2 {

device_type = "cpu";

compatible = "arm,cortex-a53", "arm,armv8";

reg = <0x00000000 0x00000002>;

enable-method = "psci";

clocks = <0x00000015 0x00000018>;

clock-frequency = <0x4ead9a00>;

operating-points-v2 = <0x00000016>;

cpu-idle-states = <0x00000017 0x00000018>;

#cooling-cells = <0x00000002>;

phandle = <0x00000022>;

};

cpu@3 {

device_type = "cpu";

compatible = "arm,cortex-a53", "arm,armv8";

reg = <0x00000000 0x00000003>;

enable-method = "psci";

clocks = <0x00000015 0x00000018>;

clock-frequency = <0x4ead9a00>;

operating-points-v2 = <0x00000016>;

cpu-idle-states = <0x00000017 0x00000018>;

#cooling-cells = <0x00000002>;

phandle = <0x00000023>;

};

idle-states {

entry-method = "arm,psci";

cpu-sleep-0 {

compatible = "arm,idle-state";

arm,psci-suspend-param = <0x00010000>;

entry-latency-us = <0x0000002e>;

exit-latency-us = <0x0000003b>;

min-residency-us = <0x00000df2>;

local-timer-stop;

phandle = <0x00000017>;

};

cluster-sleep-0 {

compatible = "arm,idle-state";

arm,psci-suspend-param = <0x01010000>;

entry-latency-us = <0x0000002f>;

exit-latency-us = <0x0000004a>;

min-residency-us = <0x00001388>;

local-timer-stop;

phandle = <0x00000018>;

};

};

};

cpu-opp-table {

compatible = "allwinner,sun50i-operating-points";

nvmem-cells = <0x0000001a 0x0000001b 0x0000001c>;

nvmem-cell-names = "speed", "bin", "bin_ext";

opp-shared;

phandle = <0x00000016>;

opp@408000000 {

opp-hz = <0x00000000 0x18519600>;

clock-latency-ns = <0x0003b9b0>;

opp-microvolt-a0 = <0x000dbba0>;

opp-microvolt-a1 = <0x000dbba0>;

opp-microvolt-a2 = <0x000dbba0>;

opp-microvolt-a3 = <0x000e57e0>;

opp-microvolt-a4 = <0x000e57e0>;

opp-microvolt-a5 = <0x000e09c0>;

opp-microvolt-a6 = <0x000e09c0>;

opp-microvolt-b0 = <0x000dbba0>;

opp-microvolt-b1 = <0x000dbba0>;

opp-microvolt-b2 = <0x000e57e0>;

opp-microvolt-b3 = <0x000e09c0>;

opp-supported-hw = <0x00000007>;

};

opp@600000000 {

opp-hz = <0x00000000 0x23c34600>;

clock-latency-ns = <0x0003b9b0>;

opp-microvolt-a0 = <0x000dbba0>;

opp-microvolt-a1 = <0x000dbba0>;

opp-microvolt-a2 = <0x000dbba0>;

opp-microvolt-a3 = <0x000e57e0>;

opp-microvolt-a4 = <0x000e57e0>;

opp-microvolt-a5 = <0x000e09c0>;

opp-microvolt-a6 = <0x000e09c0>;

opp-microvolt-b0 = <0x000dbba0>;

opp-microvolt-b1 = <0x000dbba0>;

opp-microvolt-b2 = <0x000e57e0>;

opp-microvolt-b3 = <0x000e09c0>;

opp-supported-hw = <0x00000007>;

};

opp@816000000 {

opp-hz = <0x00000000 0x30a32c00>;

clock-latency-ns = <0x0003b9b0>;

opp-microvolt-a0 = <0x000e57e0>;

opp-microvolt-a1 = <0x000dbba0>;

opp-microvolt-a2 = <0x000dbba0>;

opp-microvolt-a3 = <0x000e57e0>;

opp-microvolt-a4 = <0x000e57e0>;

opp-microvolt-a5 = <0x000e09c0>;

opp-microvolt-a6 = <0x000e09c0>;

opp-microvolt-b0 = <0x000dbba0>;

opp-microvolt-b1 = <0x000dbba0>;

opp-microvolt-b2 = <0x000e57e0>;

opp-microvolt-b3 = <0x000e09c0>;

opp-supported-hw = <0x00000007>;

};

opp@1008000000 {

opp-hz = <0x00000000 0x3c14dc00>;

clock-latency-ns = <0x0003b9b0>;

opp-microvolt-a0 = <0x000f9060>;

opp-microvolt-a1 = <0x000ef420>;

opp-microvolt-a2 = <0x000e7ef0>;

opp-microvolt-a3 = <0x000f9060>;

opp-microvolt-a4 = <0x000ea600>;

opp-microvolt-a5 = <0x000e57e0>;

opp-microvolt-a6 = <0x000e57e0>;

opp-microvolt-b0 = <0x000ef420>;

opp-microvolt-b1 = <0x000e7ef0>;

opp-microvolt-b2 = <0x000ea600>;

opp-microvolt-b3 = <0x000e57e0>;

opp-supported-hw = <0x00000007>;

};

opp@1200000000 {

opp-hz = <0x00000000 0x47868c00>;

clock-latency-ns = <0x0003b9b0>;

opp-microvolt-a0 = <0x0010c8e0>;

opp-microvolt-a1 = <0x000f9060>;

opp-microvolt-a2 = <0x000f4240>;

opp-microvolt-a3 = <0x0010c8e0>;

opp-microvolt-a4 = <0x000ef420>;

opp-microvolt-a5 = <0x000ea600>;

opp-microvolt-a6 = <0x000ea600>;

opp-microvolt-b0 = <0x000f9060>;

opp-microvolt-b1 = <0x000f4240>;

opp-microvolt-b2 = <0x000ef420>;

opp-microvolt-b3 = <0x000ea600>;

opp-supported-hw = <0x00000007>;

};

opp@1320000000 {

opp-hz = <0x00000000 0x4ead9a00>;

clock-latency-ns = <0x0003b9b0>;

opp-microvolt-a0 = <0x0011b340>;

opp-microvolt-a1 = <0x00102ca0>;

opp-microvolt-a2 = <0x000fb770>;

opp-microvolt-a3 = <0x0011b340>;

opp-microvolt-a4 = <0x000f9060>;

opp-microvolt-a5 = <0x000f4240>;

opp-microvolt-a6 = <0x000f4240>;

opp-microvolt-b0 = <0x00102ca0>;

opp-microvolt-b1 = <0x000fb770>;

opp-microvolt-b2 = <0x000f9060>;

opp-microvolt-b3 = <0x000f4240>;

opp-supported-hw = <0x00000007>;

};

opp@1416000000 {

opp-hz = <0x00000000 0x54667200>;

clock-latency-ns = <0x0003b9b0>;

opp-microvolt-b0 = <0x0010c8e0>;

opp-microvolt-b1 = <0x001053b0>;

opp-microvolt-b2 = <0x00102ca0>;

opp-microvolt-b3 = <0x000fde80>;

opp-supported-hw = <0x00000006>;

};

opp@1464000000 {

opp-hz = <0x00000000 0x5742de00>;

clock-latency-ns = <0x0003b9b0>;

opp-microvolt-a0 = <0x00120160>;

opp-microvolt-a1 = <0x00120160>;

opp-microvolt-a2 = <0x00113e10>;

opp-microvolt-a3 = <0x00120160>;

opp-microvolt-a4 = <0x0010c8e0>;

opp-microvolt-a5 = <0x00107ac0>;

opp-microvolt-a6 = <0x00107ac0>;

opp-supported-hw = <0x00000001>;

};

opp@1512000000 {

opp-hz = <0x00000000 0x5a1f4a00>;

clock-latency-ns = <0x0003b9b0>;

opp-microvolt-b0 = <0x00120160>;

opp-microvolt-b1 = <0x00113e10 0x00113e10 0x00116520>;

opp-microvolt-b2 = <0x0010c8e0>;

opp-microvolt-b3 = <0x00107ac0>;

opp-supported-hw = <0x00000006>;

};

opp@1608000000 {

opp-hz = <0x00000000 0x5fd82200>;

clock-latency-ns = <0x0003b9b0>;

opp-microvolt-b0 = <0x00120160>;

opp-microvolt-b1 = <0x00113e10 0x00113e10 0x00116520>;

opp-supported-hw = <0x00000000>;

};

};

dcxo24M-clk {

#clock-cells = <0x00000000>;

compatible = "fixed-clock";

clock-frequency = <0x016e3600>;

clock-output-names = "dcxo24M";

phandle = <0x00000028>;

};

thermal-zones {

cpu_thermal_zone {

polling-delay-passive = <0x000001f4>;

polling-delay = <0x000003e8>;

thermal-sensors = <0x0000001d 0x00000000>;

sustainable-power = <0x000004b0>;

trips {

phandle = <0x00000121>;

trip-point@0 {

temperature = <0x00011170>;

type = "passive";

hysteresis = <0x00000000>;

phandle = <0x00000122>;

};

trip-point@1 {

temperature = <0x00015f90>;

type = "passive";

hysteresis = <0x00000000>;

phandle = <0x0000001e>;

};

cpu_crit@0 {

temperature = <0x0001adb0>;

type = "critical";

hysteresis = <0x00000000>;

phandle = <0x00000123>;

};

};

cooling-maps {

map0 {

trip = <0x0000001e>;

cooling-device = <0x0000001f 0xffffffff 0xffffffff>;

contribution = <0x00000400>;

};

};

};

gpu_thermal_zone {

polling-delay-passive = <0x000001f4>;

polling-delay = <0x000003e8>;

thermal-sensors = <0x0000001d 0x00000001>;

sustainable-power = <0x0000044c>;

};

ddr_thermal_zone {

polling-delay-passive = <0x00000000>;

polling-delay = <0x00000000>;

thermal-sensors = <0x0000001d 0x00000002>;

};

};

psci {

compatible = "arm,psci-1.0";

method = "smc";

};

memory@40000000 {

device_type = "memory";

reg = <0x00000000 0x40000000 0x00000000 0x20000000>;

};

interrupt-controller@3020000 {

compatible = "arm,cortex-a15-gic", "arm,cortex-a9-gic";

#interrupt-cells = <0x00000003>;

#address-cells = <0x00000000>;

device_type = "gic";

interrupt-controller;

reg = <0x00000000 0x03021000 0x00000000 0x00001000 0x00000000 0x03022000 0x00000000 0x00002000 0x00000000 0x03024000 0x00000000 0x00002000 0x00000000 0x03026000 0x00000000 0x00002000>;

interrupts = <0x00000001 0x00000009 0x00000f04>;

interrupt-parent = <0x00000020>;

phandle = <0x00000020>;

};

interrupt-controller@0 {

compatible = "allwinner,sunxi-wakeupgen";

interrupt-controller;

#interrupt-cells = <0x00000003>;

interrupt-parent = <0x00000020>;

phandle = <0x00000001>;

};

timer_arch {

compatible = "arm,armv8-timer";

interrupts = <0x00000001 0x0000000d 0x00000f08 0x00000001 0x0000000e 0x00000f08 0x00000001 0x0000000b 0x00000f08 0x00000001 0x0000000a 0x00000f08>;

clock-frequency = <0x016e3600>;

interrupt-parent = <0x00000020>;

arm,no-tick-in-suspend;

};

pmu {

compatible = "arm,armv8-pmuv3";

interrupts = <0x00000000 0x0000008c 0x00000004 0x00000000 0x0000008d 0x00000004 0x00000000 0x0000008e 0x00000004 0x00000000 0x0000008f 0x00000004>;

interrupt-affinity = <0x0000001f 0x00000021 0x00000022 0x00000023>;

};

gpu-power-domain@7001000 {

compatible = "allwinner,gpu-pd", "syscon";

reg = <0x00000000 0x07001000 0x00000000 0x00000040>;

interrupts = <0x00000000 0x00000077 0x00000004>;

interrupt-names = "ppu-irq";

clocks = <0x00000024 0x00000008>;

clock-names = "ppu";

resets = <0x00000024 0x00000002>;

reset-names = "ppu_rst";

#power-domain-cells = <0x00000000>;

phandle = <0x000000b2>;

};

intc-nmi@7010320 {

compatible = "allwinner,sun8i-nmi";

interrupt-parent = <0x00000020>;

#interrupt-cells = <0x00000002>;

#address-cells = <0x00000000>;

interrupt-controller;

reg = <0x00000000 0x07010320 0x00000000 0x0000000c>;

interrupts = <0x00000000 0x00000067 0x00000004>;

phandle = <0x0000005e>;

};

dram {

compatible = "allwinner,dram";

clocks = <0x00000015 0x00000002>;

clock-names = "pll_ddr";

dram_clk = <0x000002a0>;

dram_type = <0x00000008>;

dram_zq = <0x07070707>;

dram_odt_en = <0x0d0d0d0d>;

dram_para1 = <0x00000e0e>;

dram_para2 = <0x0d0a050c>;

dram_mr0 = <0x000030fa>;

dram_mr1 = <0x08001000>;

dram_mr2 = <0x00000000>;

dram_mr3 = <0x00000034>;

dram_tpr0 = <0x0000001b>;

dram_tpr1 = <0x00000033>;

dram_tpr2 = <0x00000003>;

dram_tpr3 = <0x00000000>;

dram_tpr4 = <0x00000000>;

dram_tpr5 = <0x00000004>;

dram_tpr6 = <0x00000072>;

dram_tpr7 = <0x00000000>;

dram_tpr8 = <0x00000007>;

dram_tpr9 = <0x00000000>;

dram_tpr10 = <0x00000000>;

dram_tpr11 = <0x00000026>;

dram_tpr12 = <0x06060606>;

dram_tpr13 = <0x04040404>;

phandle = <0x00000124>;

};

clk_ddr {

compatible = "allwinner,clock_ddr";

reg = <0x00000000 0x03001000 0x00000000 0x00001000 0x00000000 0x04810000 0x00000000 0x00002000>;

clocks = <0x00000015 0x00000002>;

clock-names = "pll_ddr";

#clock-cells = <0x00000000>;

phandle = <0x00000025>;

};

nsi-pmu@3100000 {

compatible = "allwinner,sunxi-dfi", "syscon";

reg = <0x00000000 0x03100000 0x00000000 0x00010000>;

clocks = <0x00000025>;

clock-names = "dram";

phandle = <0x00000026>;

};

opp_table {

compatible = "operating-points-v2";

phandle = <0x00000027>;

opp@336000000 {

opp-hz = <0x00000000 0x1406f400>;

};

opp@448000000 {

opp-hz = <0x00000000 0x1ab3f000>;

};

opp@537600000 {

opp-hz = <0x00000000 0x200b2000>;

};

opp@672000000 {

opp-hz = <0x00000000 0x280de800>;

};

};

sunxi-dmcfreq {

compatible = "allwinner,sunxi-dmc";

devfreq-events = <0x00000026>;

clocks = <0x00000025>;

clock-names = "dram";

operating-points-v2 = <0x00000027>;

upthreshold = <0x00000032>;

downdifferential = <0x00000014>;

};

uboot {

phandle = <0x00000125>;

};

iommu@30f0000 {

compatible = "allwinner,sunxi-iommu";

reg = <0x00000000 0x030f0000 0x00000000 0x00001000>;

interrupts = <0x00000000 0x00000042 0x00000004>;

interrupt-names = "iommu-irq";

clocks = <0x00000015 0x00000037>;

clock-names = "iommu";

#iommu-cells = <0x00000002>;

phandle = <0x00000081>;

};

dump_reg@20000 {

compatible = "allwinner,sunxi-dump-reg";

reg = <0x00000000 0x00020000 0x00000000 0x00000004>;

phandle = <0x00000126>;

};

pio-18 {

compatible = "regulator-fixed";

regulator-name = "pio-18";

regulator-min-microvolt = <0x001b7740>;

regulator-max-microvolt = <0x001b7740>;

phandle = <0x000000b0>;

};

pio-28 {

compatible = "regulator-fixed";

regulator-name = "pio-28";

regulator-min-microvolt = <0x002ab980>;

regulator-max-microvolt = <0x002ab980>;

phandle = <0x00000127>;

};

pio-33 {

compatible = "regulator-fixed";

regulator-name = "pio-33";

regulator-min-microvolt = <0x00325aa0>;

regulator-max-microvolt = <0x00325aa0>;

phandle = <0x000000b1>;

};

soc@2900000 {

compatible = "simple-bus";

#address-cells = <0x00000002>;

#size-cells = <0x00000002>;

ranges;

device_type = "soc";

phandle = <0x00000128>;

sram_ctrl@3000000 {

compatible = "allwinner,sram_ctrl";

reg = <0x00000000 0x03000000 0x00000000 0x0000016c>;

phandle = <0x00000129>;

soc_ver {

offset = <0x00000024>;

mask = <0x00000007>;

shift = <0x00000000>;

ver_a = <0x18550000>;

ver_b = <0x18550001>;

};

soc_id {

offset = <0x00000200>;

mask = <0x00000001>;

shift = <0x00000016>;

};

soc_bin {

offset = <0x00000000>;

mask = <0x000003ff>;

shift = <0x00000000>;

};

};

clock@3001000 {

compatible = "allwinner,sun50iw10-ccu";

reg = <0x00000000 0x03001000 0x00000000 0x00001000>;

clocks = <0x00000028 0x00000029 0x00000002 0x00000029 0x00000001>;

clock-names = "hosc", "losc", "iosc";

#clock-cells = <0x00000001>;

#reset-cells = <0x00000001>;

phandle = <0x00000015>;

};

clock@7010000 {

compatible = "allwinner,sun50iw10-r-ccu";

reg = <0x00000000 0x07010000 0x00000000 0x00000240>;

clocks = <0x00000028 0x00000029 0x00000002 0x00000029 0x00000001 0x00000015 0x00000003>;

clock-names = "hosc", "losc", "iosc", "pll-periph";

#clock-cells = <0x00000001>;

#reset-cells = <0x00000001>;

phandle = <0x00000024>;

};

dma-controller@3002000 {

compatible = "allwinner,sun50iw10-dma";

reg = <0x00000000 0x03002000 0x00000000 0x00001000>;

interrupts = <0x00000000 0x0000002d 0x00000004>;

clocks = <0x00000015 0x0000002f 0x00000015 0x00000038>;

clock-names = "bus", "mbus";

dma-channels = <0x00000008>;

dma-requests = <0x00000034>;

resets = <0x00000015 0x00000008>;

#dma-cells = <0x00000001>;

phandle = <0x00000055>;

};

rtc@7000000 {

compatible = "allwinner,sun50iw10p1-rtc";

device_type = "rtc";

wakeup-source;

reg = <0x00000000 0x07000000 0x00000000 0x00000200>;

interrupts = <0x00000000 0x0000006c 0x00000004>;

clocks = <0x00000024 0x0000000e 0x00000029 0x00000004>;

clock-names = "r-ahb-rtc", "rtc-1k";

resets = <0x00000024 0x00000007>;

gpr_offset = <0x00000100>;

gpr_len = <0x00000008>;

gpr_cur_pos = <0x00000006>;

phandle = <0x0000012a>;

};

rtc_ccu@7000000 {

compatible = "allwinner,sun50iw10p1-rtc-ccu";

device_type = "rtc-ccu";

reg = <0x00000000 0x07000000 0x00000000 0x00000200>;

#clock-cells = <0x00000001>;

clock-output-names = "dcxo24M-out", "iosc", "osc32k", "osc32k-out", "rtc-1k";

phandle = <0x00000029>;

};

nsi-controller@3100000 {

compatible = "allwinner,sun50i-nsi";

interrupts = <0x00000000 0x0000003f 0x00000004>;

reg = <0x00000000 0x03100000 0x00000000 0x00010000>;

clocks = <0x00000015 0x00000004 0x00000015 0x0000001f 0x00000015 0x00000002>;

clock-names = "pll", "bus", "sdram";

resets = <0x00000015 0x00000000>;

clock-frequency = <0x17d78400>;

#nsi-cells = <0x00000001>;

phandle = <0x0000012b>;

cpu {

mode = <0x00000000>;

pri = <0x00000000>;

select = <0x00000000>;

};

gpu {

mode = <0x00000000>;

pri = <0x00000003>;

select = <0x00000001>;

};

sd1 {

mode = <0x00000001>;

pri = <0x00000002>;

select = <0x00000000>;

};

mstg {

mode = <0x00000000>;

pri = <0x00000001>;

select = <0x00000000>;

};

ce {

mode = <0x00000001>;

pri = <0x00000000>;

select = <0x00000001>;

};

};

sid@3006000 {

compatible = "allwinner,sun50iw10p1-sid", "allwinner,sunxi-sid";

reg = <0x00000000 0x03006000 0x00000000 0x00001000>;

#address-cells = <0x00000001>;

#size-cells = <0x00000001>;

speed@00 {

reg = <0x00000000 0x00000002>;

phandle = <0x0000001a>;

};

calib@14 {

reg = <0x00000014 0x00000008>;

phandle = <0x0000002a>;

};

calib@1c {

reg = <0x0000001c 0x00000002>;

phandle = <0x0000001b>;

};

calib@28 {

reg = <0x00000028 0x00000004>;

phandle = <0x0000001c>;

};

secure_status {

reg = <0x00000000 0x00000000>;

offset = <0x000000a0>;

size = <0x00000004>;

};

chipid {

reg = <0x00000000 0x00000000>;

offset = <0x00000200>;

size = <0x00000010>;

};

rotpk {

reg = <0x00000000 0x00000000>;

offset = <0x00000270>;

size = <0x00000020>;

};

};

ce@1904000 {

compatible = "allwinner,sunxi-ce";

device_name = "ce";

reg = <0x00000000 0x01904000 0x00000000 0x000000a0 0x00000000 0x01904800 0x00000000 0x000000a0>;

interrupts = <0x00000000 0x0000005c 0x00000001 0x00000000 0x0000005d 0x00000001>;

clock-frequency = <0x17d78400>;

clocks = <0x00000015 0x0000002c 0x00000015 0x0000002b 0x00000015 0x0000003a 0x00000015 0x00000004>;

clock-names = "bus_ce", "ce_clk", "mbus_ce", "pll_periph0_2x";

resets = <0x00000015 0x00000006>;

phandle = <0x0000012c>;

};

ths@5070400 {

compatible = "allwinner,sun50iw10p1-ths";

reg = <0x00000000 0x05070400 0x00000000 0x00000400>;

clocks = <0x00000015 0x00000067>;

clock-names = "bus";

resets = <0x00000015 0x0000002a>;

nvmem-cells = <0x0000002a>;

nvmem-cell-names = "calibration";

#thermal-sensor-cells = <0x00000001>;

phandle = <0x0000001d>;

};

timer@3009000 {

compatible = "allwinner,sun4i-a10-timer";

device_type = "soc_timer";

reg = <0x00000000 0x03009000 0x00000000 0x000000a0>;

interrupt-parent = <0x00000020>;

interrupts = <0x00000000 0x00000033 0x00000004>;

clocks = <0x00000028>;

phandle = <0x0000012d>;

};

uart@5000000 {

compatible = "allwinner,sun50i-uart";

device_type = "uart0";

reg = <0x00000000 0x05000000 0x00000000 0x00000400>;

interrupts = <0x00000000 0x00000000 0x00000004>;

sunxi,uart-fifosize = <0x00000040>;

clocks = <0x00000015 0x0000004b>;

clock-names = "uart0";

resets = <0x00000015 0x00000015>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x0000002b>;

pinctrl-1 = <0x0000002c>;

uart0_port = <0x00000000>;

uart0_type = <0x00000002>;

uart-supply = <0x0000002d>;

phandle = <0x0000012e>;

};

uart@5000400 {

compatible = "allwinner,sun50i-uart";

device_type = "uart1";

reg = <0x00000000 0x05000400 0x00000000 0x00000400>;

interrupts = <0x00000000 0x00000001 0x00000004>;

sunxi,uart-fifosize = <0x00000040>;

clocks = <0x00000015 0x0000004c>;

clock-names = "uart1";

resets = <0x00000015 0x00000016>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x0000002e>;

pinctrl-1 = <0x0000002f>;

uart1_port = <0x00000001>;

uart1_type = <0x00000004>;

status = "okay";

phandle = <0x0000012f>;

};

uart@5000800 {

compatible = "allwinner,sun50i-uart";

device_type = "uart2";

reg = <0x00000000 0x05000800 0x00000000 0x00000400>;

interrupts = <0x00000000 0x00000002 0x00000004>;

sunxi,uart-fifosize = <0x00000040>;

clocks = <0x00000015 0x0000004d>;

clock-names = "uart2";

resets = <0x00000015 0x00000017>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x00000030>;

pinctrl-1 = <0x00000031>;

uart2_port = <0x00000002>;

uart2_type = <0x00000004>;

status = "disabled";

phandle = <0x00000130>;

};

uart@5000c00 {

compatible = "allwinner,sun50i-uart";

device_type = "uart3";

reg = <0x00000000 0x05000c00 0x00000000 0x00000400>;

interrupts = <0x00000000 0x00000003 0x00000004>;

sunxi,uart-fifosize = <0x00000040>;

clocks = <0x00000015 0x0000004e>;

clock-names = "uart3";

resets = <0x00000015 0x00000018>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x00000032>;

pinctrl-1 = <0x00000033>;

uart3_port = <0x00000003>;

uart3_type = <0x00000004>;

status = "disabled";

phandle = <0x00000131>;

};

uart@5001000 {

compatible = "allwinner,sun50i-uart";

device_type = "uart4";

reg = <0x00000000 0x05001000 0x00000000 0x00000400>;

interrupts = <0x00000000 0x00000004 0x00000004>;

clocks = <0x00000015 0x0000004f>;

clock-names = "uart4";

resets = <0x00000015 0x00000019>;

sunxi,uart-fifosize = <0x00000040>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x00000034>;

pinctrl-1 = <0x00000035>;

uart4_port = <0x00000004>;

uart4_type = <0x00000004>;

status = "disabled";

phandle = <0x00000132>;

};

uart@5001400 {

compatible = "allwinner,sun50i-uart";

device_type = "uart5";

reg = <0x00000000 0x05001400 0x00000000 0x00000400>;

interrupts = <0x00000000 0x00000005 0x00000004>;

sunxi,uart-fifosize = <0x00000040>;

clocks = <0x00000015 0x00000050>;

clock-names = "uart5";

resets = <0x00000015 0x0000001a>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x00000036>;

pinctrl-1 = <0x00000037>;

uart5_port = <0x00000005>;

uart5_type = <0x00000004>;

status = "disabled";

phandle = <0x00000133>;

};

uart@5001800 {

compatible = "allwinner,sun50i-uart";

device_type = "uart6";

reg = <0x00000000 0x05001800 0x00000000 0x00000400>;

interrupts = <0x00000000 0x00000006 0x00000004>;

sunxi,uart-fifosize = <0x00000040>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x00000038>;

pinctrl-1 = <0x00000039>;

uart6_port = <0x00000006>;

uart6_type = <0x00000004>;

status = "disabled";

phandle = <0x00000134>;

};

uart@7080000 {

compatible = "allwinner,sun50i-uart";

device_type = "uart7";

reg = <0x00000000 0x07080000 0x00000000 0x00000400>;

interrupts = <0x00000000 0x00000070 0x00000004>;

sunxi,uart-fifosize = <0x00000040>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x0000003a>;

pinctrl-1 = <0x0000003b>;

uart7_port = <0x00000007>;

uart7_type = <0x00000002>;

status = "disabled";

phandle = <0x00000135>;

};

sdmmc@4022000 {

compatible = "allwinner,sunxi-mmc-v4p6x";

device_type = "sdc2";

reg = <0x00000000 0x04022000 0x00000000 0x00001000>;

interrupts = <0x00000000 0x00000029 0x00000004>;

clocks = <0x00000028 0x00000015 0x00000006 0x00000015 0x00000045 0x00000015 0x00000049>;

clock-names = "osc24m", "pll_periph", "mmc", "ahb";

resets = <0x00000015 0x00000013>;

reset-names = "rst";

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x0000003c 0x0000003d>;

pinctrl-1 = <0x0000003e>;

bus-width = <0x00000008>;

req-page-count = <0x00000002>;

cap-mmc-highspeed;

cap-cmd23;

mmc-cache-ctrl;

non-removable;

max-frequency = <0x05f5e100>;

cap-erase;

mmc-high-capacity-erase-size;

no-sdio;

no-sd;

sdc_tm4_sm0_freq0 = <0x00000000>;

sdc_tm4_sm0_freq1 = <0x00000000>;

sdc_tm4_sm1_freq0 = <0x00000000>;

sdc_tm4_sm1_freq1 = <0x00000000>;

sdc_tm4_sm2_freq0 = <0x00000000>;

sdc_tm4_sm2_freq1 = <0x00000000>;

sdc_tm4_sm3_freq0 = <0x05000000>;

sdc_tm4_sm3_freq1 = <0x00000005>;

sdc_tm4_sm4_freq0 = <0x00050000>;

sdc_tm4_sm4_freq1 = <0x00000004>;

sdc_tm4_sm4_freq0_cmd = <0x00000000>;

sdc_tm4_sm4_freq1_cmd = <0x00000000>;

mmc-ddr-1_8v;

mmc-hs200-1_8v;

mmc-hs400-1_8v;

ctl-spec-caps = <0x00000308>;

sunxi-power-save-mode;

sunxi-dis-signal-vol-sw;

mmc-bootpart-noacc;

vmmc-supply = <0x0000002d>;

vqmmc-supply = <0x0000003f>;

status = "disabled";

phandle = <0x00000136>;

};

sdmmc@4020000 {

compatible = "allwinner,sunxi-mmc-v5p3x";

device_type = "sdc0";

reg = <0x00000000 0x04020000 0x00000000 0x00001000>;

interrupts = <0x00000000 0x00000027 0x00000004>;

clocks = <0x00000028 0x00000015 0x00000006 0x00000015 0x00000043 0x00000015 0x00000047>;

clock-names = "osc24m", "pll_periph", "mmc", "ahb";

resets = <0x00000015 0x00000011>;

reset-names = "rst";

pinctrl-names = "default", "mmc_1v8", "sleep", "uart_jtag";

pinctrl-0 = <0x00000040>;

pinctrl-1 = <0x00000041>;

pinctrl-2 = <0x00000042>;

pinctrl-3 = <0x00000043 0x00000044>;

max-frequency = <0x08f0d180>;

bus-width = <0x00000004>;

req-page-count = <0x00000002>;

cap-sd-highspeed;

cap-wait-while-busy;

no-sdio;

no-mmc;

cd-gpios = <0x00000045 0x00000005 0x00000006 0x00000011>;

cd-used-24M;

sd-uhs-sdr50;

sd-uhs-ddr50;

sd-uhs-sdr104;

sunxi-power-save-mode;

ctl-spec-caps = <0x00000008>;

vmmc-supply = <0x0000002d>;

vqmmc33sw-supply = <0x0000002d>;

vdmmc33sw-supply = <0x0000002d>;

vqmmc18sw-supply = <0x0000003f>;

vdmmc18sw-supply = <0x0000003f>;

status = "okay";

phandle = <0x00000137>;

};

sdmmc@4021000 {

compatible = "allwinner,sunxi-mmc-v5p3x";

device_type = "sdc1";

reg = <0x00000000 0x04021000 0x00000000 0x00001000>;

interrupts = <0x00000000 0x00000028 0x00000004>;

clocks = <0x00000028 0x00000015 0x00000006 0x00000015 0x00000044 0x00000015 0x00000048>;

clock-names = "osc24m", "pll_periph", "mmc", "ahb";

resets = <0x00000015 0x00000012>;

reset-names = "rst";

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x00000046>;

pinctrl-1 = <0x00000047>;

max-frequency = <0x08f0d180>;

bus-width = <0x00000004>;

cap-sd-highspeed;

no-mmc;

keep-power-in-suspend;

sunxi-dly-52M-ddr4 = <0x00000001 0x00000000 0x00000000 0x00000000 0x00000002>;

sunxi-dly-104M = <0x00000001 0x00000001 0x00000000 0x00000000 0x00000001>;

sunxi-dly-208M = <0x00000001 0x00000000 0x00000000 0x00000000 0x00000001>;

status = "okay";

no-sd;

sd-uhs-sdr25;

sd-uhs-sdr50;

sd-uhs-ddr50;

sd-uhs-sdr104;

cap-sdio-irq;

ignore-pm-notify;

ctl-spec-caps = <0x00000008>;

phandle = <0x00000138>;

};

sdmmc@4023000 {

compatible = "allwinner,sunxi-mmc-v5p3x";

device_type = "sdc3";

reg = <0x00000000 0x04023000 0x00000000 0x00001000>;

interrupts = <0x00000000 0x0000002a 0x00000004>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x00000048>;

pinctrl-1 = <0x00000049>;

max-frequency = <0x02faf080>;

bus-width = <0x00000004>;

cap-sd-highspeed;

no-sdio;

no-mmc;

status = "disabled";

phandle = <0x00000139>;

};

nand0@04011000 {

compatible = "allwinner,sun50iw10-nand";

device_type = "nand0";

reg = <0x00000000 0x04011000 0x00000000 0x00001000>;

interrupts = <0x00000000 0x00000026 0x00000004>;

clocks = <0x00000015 0x00000006 0x00000015 0x00000040 0x00000015 0x00000041 0x00000015 0x00000042 0x00000015 0x0000003b>;

clock-names = "pll_periph", "mclk", "ecc", "bus", "mbus";

resets = <0x00000015 0x00000010>;

reset-names = "rst";

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x0000004a 0x0000004b>;

pinctrl-1 = <0x0000004c>;

nand0_regulator1 = "none";

nand0_regulator2 = "none";

nand0_cache_level = <0x55aaaa55>;

nand0_flush_cache_num = <0x55aaaa55>;

nand0_capacity_level = <0x55aaaa55>;

nand0_id_number_ctl = <0x55aaaa55>;

nand0_print_level = <0x55aaaa55>;

nand0_p0 = <0x55aaaa55>;

nand0_p1 = <0x55aaaa55>;

nand0_p2 = <0x55aaaa55>;

nand0_p3 = <0x55aaaa55>;

chip_code = "sun50iw10";

status = "disabled";

phandle = <0x0000013a>;

};

twi@5002000 {

#address-cells = <0x00000001>;

#size-cells = <0x00000000>;

compatible = "allwinner,sun50i-twi";

device_type = "twi0";

reg = <0x00000000 0x05002000 0x00000000 0x00000400>;

interrupts = <0x00000000 0x00000007 0x00000004>;

clocks = <0x00000015 0x00000052>;

resets = <0x00000015 0x0000001c>;

clock-names = "bus";

clock-frequency = <0x00061a80>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x0000004d>;

pinctrl-1 = <0x0000004e>;

status = "okay";

twi-supply = <0x0000002d>;

phandle = <0x0000013b>;

ctp@0 {

ctp_fw_idx = "2";

compatible = "allwinner,gslX680";

reg = <0x00000040>;

device_type = "ctp";

status = "okay";

ctp_name = "gslX680_3676_1280x800";

ctp_twi_id = <0x00000000>;

ctp_twi_addr = <0x00000040>;

ctp_screen_max_x = <0x00000320>;

ctp_screen_max_y = <0x00000500>;

ctp_revert_x_flag = <0x00000000>;

ctp_revert_y_flag = <0x00000000>;

ctp_exchange_x_y_flag = <0x00000001>;

ctp_int_port = <0x00000045 0x00000007 0x00000009 0x00000001>;

ctp_wakeup = <0x00000045 0x00000007 0x0000000a 0x00000001>;

ctp-supply = <0x0000004f>;

ctp_power_ldo_vol = <0x00000ce4>;

phandle = <0x0000013c>;

};

};

twi@5002400 {

#address-cells = <0x00000001>;

#size-cells = <0x00000000>;

compatible = "allwinner,sun50i-twi";

device_type = "twi1";

reg = <0x00000000 0x05002400 0x00000000 0x00000400>;

interrupts = <0x00000000 0x00000008 0x00000004>;

clocks = <0x00000015 0x00000053>;

resets = <0x00000015 0x0000001d>;

clock-names = "bus";

clock-frequency = <0x00030d40>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x00000050>;

pinctrl-1 = <0x00000051>;

status = "okay";

phandle = <0x0000013d>;

gsensor {

compatible = "allwinner,mir3da";

reg = <0x00000027>;

device_type = "gsensor";

status = "okay";

gsensor_twi_id = <0x00000001>;

gsensor_twi_addr = <0x00000027>;

gsensor_int1 = <0x00000045 0x00000007 0x0000000b 0x00000001>;

gsensor-supply = <0x0000002d>;

gsensor_vcc_io_val = <0x00000ce4>;

};

lightsensor {

compatible = "allwinner,stk3x1x";

reg = <0x00000048>;

device_type = "lightsensor";

status = "okay";

ls_twi_id = <0x00000001>;

ls_twi_addr = <0x00000048>;

ls_int = <0x00000045 0x00000007 0x00000004 0x00000001>;

lightsensor-supply = <0x0000002d>;

};

};

twi@5002800 {

#address-cells = <0x00000001>;

#size-cells = <0x00000000>;

compatible = "allwinner,sun50i-twi";

device_type = "twi2";

reg = <0x00000000 0x05002800 0x00000000 0x00000400>;

interrupts = <0x00000000 0x00000009 0x00000004>;

clocks = <0x00000015 0x00000054>;

resets = <0x00000015 0x0000001e>;

clock-names = "bus";

clock-frequency = <0x00030d40>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x00000052>;

pinctrl-1 = <0x00000053>;

status = "okay";

twi-supply = <0x00000054>;

twi_vol = <0x001b7740>;

dmas = <0x00000055 0x0000002d 0x00000055 0x0000002d>;

dma-names = "tx", "rx";

twi_drv_used = <0x00000001>;

phandle = <0x0000013e>;

};

twi@5002c00 {

#address-cells = <0x00000001>;

#size-cells = <0x00000000>;

compatible = "allwinner,sun50i-twi";

device_type = "twi3";

reg = <0x00000000 0x05002c00 0x00000000 0x00000400>;

interrupts = <0x00000000 0x0000000a 0x00000004>;

clocks = <0x00000015 0x00000055>;

resets = <0x00000015 0x0000001f>;

clock-names = "bus";

clock-frequency = <0x00030d40>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x00000056>;

pinctrl-1 = <0x00000057>;

status = "okay";

twi-supply = <0x00000054>;

twi_vol = <0x001b7740>;

dmas = <0x00000055 0x0000002e 0x00000055 0x0000002e>;

dma-names = "tx", "rx";

twi_drv_used = <0x00000001>;

phandle = <0x0000013f>;

};

twi@5003000 {

#address-cells = <0x00000001>;

#size-cells = <0x00000000>;

compatible = "allwinner,sun50i-twi";

device_type = "twi4";

reg = <0x00000000 0x05003000 0x00000000 0x00000400>;

interrupts = <0x00000000 0x0000000b 0x00000004>;

clocks = <0x00000015 0x00000056>;

resets = <0x00000015 0x00000020>;

clock-names = "bus";

clock-frequency = <0x000186a0>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x00000058>;

pinctrl-1 = <0x00000059>;

status = "disabled";

phandle = <0x00000140>;

};

twi@5003400 {

#address-cells = <0x00000001>;

#size-cells = <0x00000000>;

compatible = "allwinner,sun50i-twi";

device_type = "twi5";

reg = <0x00000000 0x05003400 0x00000000 0x00000400>;

interrupts = <0x00000000 0x0000000c 0x00000004>;

clocks = <0x00000015 0x00000057>;

resets = <0x00000015 0x00000021>;

clock-names = "bus";

clock-frequency = <0x000186a0>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x0000005a>;

pinctrl-1 = <0x0000005b>;

status = "disabled";

phandle = <0x00000141>;

};

s_twi@7081400 {

#address-cells = <0x00000001>;

#size-cells = <0x00000000>;

compatible = "allwinner,sun50i-twi";

reg = <0x00000000 0x07081400 0x00000000 0x00000200>;

interrupts = <0x00000000 0x00000071 0x00000004>;

clocks = <0x00000024 0x0000000a>;

resets = <0x00000024 0x00000004>;

clock-names = "bus";

clock-frequency = <0x00030d40>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x0000005c>;

status = "okay";

pinctrl-1 = <0x0000005d>;

no_suspend = <0x00000001>;

twi_drv_used = <0x00000001>;

phandle = <0x00000142>;

pmu@34 {

compatible = "x-powers,axp2202";

reg = <0x00000034>;

status = "okay";

interrupts = <0x00000000 0x00000008>;

interrupt-parent = <0x0000005e>;

x-powers,drive-vbus-en;

pmu_reset = <0x00000000>;

pmu_irq_wakeup = <0x00000001>;

pmu_hot_shutdown = <0x00000001>;

wakeup-source;

phandle = <0x00000143>;

usb_power_supply {

compatible = "x-powers,axp2202-usb-power-supply";

status = "okay";

pmu_usbpc_vol = <0x00001194>;

pmu_usbpc_cur = <0x000001f4>;

pmu_usbad_vol = <0x00001194>;

pmu_usbad_cur = <0x000009c4>;

pmu_usb_typec_used = <0x00000001>;

wakeup_usb_in;

wakeup_usb_out;

phandle = <0x00000090>;

};

gpio_power_supply {

compatible = "x-powers,gpio-supply";

status = "disabled";

pmu_acin_det_gpio = <0x00000045 0x00000001 0x00000004 0x00000001>;

pmu_acin_usbid_drv = <0x00000045 0x00000001 0x00000006 0x00000001>;

wakeup_gpio;

phandle = <0x00000144>;

};

bat-power-supply {

compatible = "x-powers,axp2202-bat-power-supply";

param = <0x0000005f>;

status = "okay";

pmu_chg_ic_temp = <0x00000000>;

pmu_battery_rdc = <0x00000069>;

pmu_battery_cap = <0x00001360>;

pmu_runtime_chgcur = <0x000005dc>;

pmu_suspend_chgcur = <0x000007bc>;

pmu_shutdown_chgcur = <0x000005dc>;

pmu_init_chgvol = <0x000010fe>;

pmu_battery_warning_level1 = <0x0000000f>;

pmu_battery_warning_level2 = <0x00000000>;

pmu_chgled_func = <0x00000000>;

pmu_chgled_type = <0x00000000>;

ocv_coulumb_100 = <0x00000001>;

pmu_bat_para1 = <0x00000000>;

pmu_bat_para2 = <0x00000000>;

pmu_bat_para3 = <0x00000000>;

pmu_bat_para4 = <0x00000000>;

pmu_bat_para5 = <0x00000000>;

pmu_bat_para6 = <0x00000000>;

pmu_bat_para7 = <0x00000002>;

pmu_bat_para8 = <0x00000003>;

pmu_bat_para9 = <0x00000004>;

pmu_bat_para10 = <0x00000006>;

pmu_bat_para11 = <0x00000009>;

pmu_bat_para12 = <0x0000000e>;

pmu_bat_para13 = <0x0000001a>;

pmu_bat_para14 = <0x00000026>;

pmu_bat_para15 = <0x00000031>;

pmu_bat_para16 = <0x00000034>;

pmu_bat_para17 = <0x00000038>;

pmu_bat_para18 = <0x0000003c>;

pmu_bat_para19 = <0x00000040>;

pmu_bat_para20 = <0x00000046>;

pmu_bat_para21 = <0x0000004d>;

pmu_bat_para22 = <0x00000053>;

pmu_bat_para23 = <0x00000057>;

pmu_bat_para24 = <0x0000005a>;

pmu_bat_para25 = <0x0000005f>;

pmu_bat_para26 = <0x00000063>;

pmu_bat_para27 = <0x00000063>;

pmu_bat_para28 = <0x00000064>;

pmu_bat_para29 = <0x00000064>;

pmu_bat_para30 = <0x00000064>;

pmu_bat_para31 = <0x00000064>;

pmu_bat_para32 = <0x00000064>;

pmu_bat_temp_enable = <0x00000000>;

pmu_bat_charge_ltf = <0x00000451>;

pmu_bat_charge_htf = <0x00000079>;

pmu_bat_shutdown_ltf = <0x00000565>;

pmu_bat_shutdown_htf = <0x00000059>;

pmu_bat_temp_para1 = <0x00000afe>;

pmu_bat_temp_para2 = <0x0000089a>;

pmu_bat_temp_para3 = <0x000006c9>;

pmu_bat_temp_para4 = <0x00000565>;

pmu_bat_temp_para5 = <0x00000451>;

pmu_bat_temp_para6 = <0x0000037a>;

pmu_bat_temp_para7 = <0x000002d2>;

pmu_bat_temp_para8 = <0x000001e4>;

pmu_bat_temp_para9 = <0x0000014c>;

pmu_bat_temp_para10 = <0x000000e9>;

pmu_bat_temp_para11 = <0x000000c4>;

pmu_bat_temp_para12 = <0x000000a6>;

pmu_bat_temp_para13 = <0x0000008d>;

pmu_bat_temp_para14 = <0x00000079>;

pmu_bat_temp_para15 = <0x00000059>;

pmu_bat_temp_para16 = <0x00000042>;

wakeup_bat_out;

phandle = <0x00000145>;

};

powerkey@0 {

status = "okay";

compatible = "x-powers,axp2101-pek";

pmu_powkey_off_time = <0x00001770>;

pmu_powkey_off_func = <0x00000000>;

pmu_powkey_off_en = <0x00000001>;

pmu_powkey_long_time = <0x000005dc>;

pmu_powkey_on_time = <0x00000200>;

wakeup_rising;

wakeup_falling;

phandle = <0x00000146>;

};

regulators@0 {

phandle = <0x00000147>;

dcdc1 {

regulator-name = "axp2202-dcdc1";

regulator-min-microvolt = <0x0007a120>;

regulator-max-microvolt = <0x00177fa0>;

regulator-ramp-delay = <0x000000fa>;

regulator-enable-ramp-delay = <0x000003e8>;

regulator-boot-on;

regulator-always-on;

phandle = <0x00000019>;

};

dcdc2 {

regulator-name = "axp2202-dcdc2";

regulator-min-microvolt = <0x0007a120>;

regulator-max-microvolt = <0x0033e140>;

regulator-ramp-delay = <0x000000fa>;

regulator-enable-ramp-delay = <0x000003e8>;

regulator-boot-on;

regulator-always-on;

phandle = <0x00000060>;

};

dcdc3 {

regulator-name = "axp2202-dcdc3";

regulator-min-microvolt = <0x0007a120>;

regulator-max-microvolt = <0x001c1380>;

regulator-ramp-delay = <0x000000fa>;

regulator-enable-ramp-delay = <0x000003e8>;

regulator-always-on;

phandle = <0x00000061>;

};

dcdc4 {

regulator-name = "axp2202-dcdc4";

regulator-min-microvolt = <0x000f4240>;

regulator-max-microvolt = <0x00387520>;

regulator-ramp-delay = <0x000000fa>;

regulator-enable-ramp-delay = <0x000003e8>;

phandle = <0x00000062>;

};

rtcldo {

regulator-name = "axp2202-rtcldo";

regulator-min-microvolt = <0x001b7740>;

regulator-max-microvolt = <0x001b7740>;

regulator-boot-on;

regulator-always-on;

phandle = <0x00000063>;

};

aldo1 {

regulator-name = "axp2202-aldo1";

regulator-min-microvolt = <0x0007a120>;

regulator-max-microvolt = <0x003567e0>;

regulator-enable-ramp-delay = <0x000003e8>;

phandle = <0x00000064>;

};

aldo2 {

regulator-name = "axp2202-aldo2";

regulator-min-microvolt = <0x0007a120>;

regulator-max-microvolt = <0x003567e0>;

regulator-enable-ramp-delay = <0x000003e8>;

phandle = <0x00000054>;

};

aldo3 {

regulator-name = "axp2202-aldo3";

regulator-min-microvolt = <0x0007a120>;

regulator-max-microvolt = <0x003567e0>;

regulator-enable-ramp-delay = <0x000003e8>;

regulator-always-on;

regulator-boot-on;

phandle = <0x00000065>;

};

aldo4 {

regulator-name = "axp2202-aldo4";

regulator-min-microvolt = <0x0007a120>;

regulator-max-microvolt = <0x003567e0>;

regulator-enable-ramp-delay = <0x000003e8>;

regulator-always-on;

regulator-boot-on;

phandle = <0x00000066>;

};

bldo1 {

regulator-name = "axp2202-bldo1";

regulator-min-microvolt = <0x0007a120>;

regulator-max-microvolt = <0x003567e0>;

regulator-enable-ramp-delay = <0x000003e8>;

phandle = <0x00000067>;

};

bldo2 {

regulator-name = "axp2202-bldo2";

regulator-min-microvolt = <0x0007a120>;

regulator-max-microvolt = <0x003567e0>;

regulator-enable-ramp-delay = <0x000003e8>;

regulator-boot-on;

regulator-always-on;

phandle = <0x00000068>;

};

bldo3 {

regulator-name = "axp2202-bldo3";

regulator-min-microvolt = <0x0007a120>;

regulator-max-microvolt = <0x003567e0>;

regulator-enable-ramp-delay = <0x000003e8>;

phandle = <0x00000069>;

};

bldo4 {

regulator-name = "axp2202-bldo4";

regulator-min-microvolt = <0x0007a120>;

regulator-max-microvolt = <0x003567e0>;

regulator-enable-ramp-delay = <0x000003e8>;

phandle = <0x0000006a>;

};

cldo1 {

regulator-name = "axp2202-cldo1";

regulator-min-microvolt = <0x0007a120>;

regulator-max-microvolt = <0x003567e0>;

regulator-enable-ramp-delay = <0x000003e8>;

phandle = <0x0000003f>;

};

cldo2 {

regulator-name = "axp2202-cldo2";

regulator-min-microvolt = <0x0007a120>;

regulator-max-microvolt = <0x003567e0>;

regulator-enable-ramp-delay = <0x000003e8>;

phandle = <0x0000004f>;

};

cldo3 {

regulator-name = "axp2202-cldo3";

regulator-min-microvolt = <0x0007a120>;

regulator-max-microvolt = <0x003567e0>;

regulator-ramp-delay = <0x000009c4>;

regulator-enable-ramp-delay = <0x000003e8>;

regulator-boot-on;

phandle = <0x0000002d>;

};

cldo4 {

regulator-name = "axp2202-cldo4";

regulator-min-microvolt = <0x0007a120>;