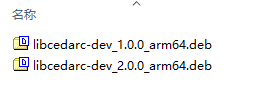

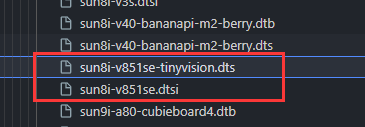

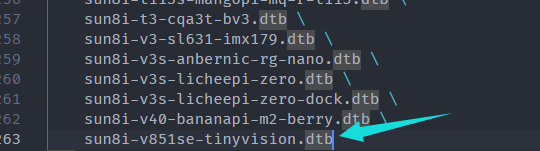

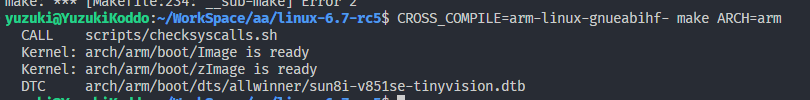

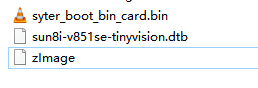

SDK 里有这两个安装包

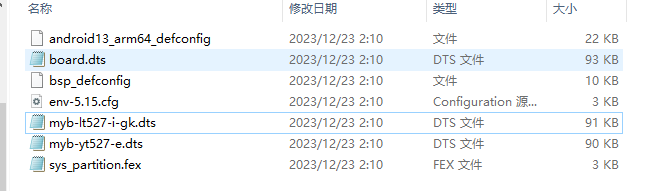

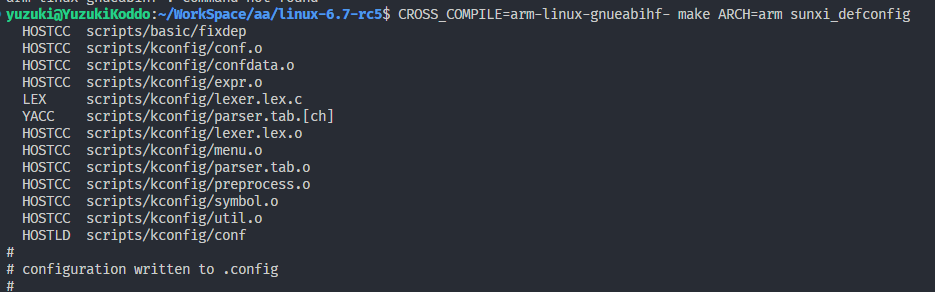

Avaota-A1 使用主线 SDK,不适用原厂的工具

// SPDX-License-Identifier: (GPL-2.0+ or MIT)

/*

* Copyright (C) 2021 liujuan1@allwinnertech.com

*/

#include <dt-bindings/clock/sun55iw3-ccu.h>

#include <dt-bindings/clock/sun55iw3-rtc.h>

#include <dt-bindings/clock/sun55iw3-r-ccu.h>

#include <dt-bindings/clock/sun55iw3-mcu-ccu.h>

#include <dt-bindings/clock/sun55iw3-displl-ccu.h>

#include <dt-bindings/gpio/gpio.h>

#include <dt-bindings/gpio/sun4i-gpio.h>

#include <dt-bindings/interrupt-controller/arm-gic.h>

#include <dt-bindings/reset/sun55iw3-ccu.h>

#include <dt-bindings/reset/sun55iw3-r-ccu.h>

#include <dt-bindings/reset/sun55iw3-mcu-ccu.h>

#include <dt-bindings/power/a523-power.h>

#include <dt-bindings/phy/phy.h>

#include <dt-bindings/usb/pd.h>

#include <dt-bindings/thermal/thermal.h>

#include <dt-bindings/spi/sunxi-spi.h>

#include <dt-bindings/clock/sunxi-ccu.h>

/ {

model = "sun55iw3";

interrupt-parent = <&wakeupgen>;

#address-cells = <2>;

#size-cells = <2>;

aliases {

serial0 = &uart0;

serial1 = &uart1;

serial2 = &uart2;

serial3 = &uart3;

serial4 = &uart4;

serial5 = &uart5;

serial6 = &uart6;

serial7 = &uart7;

serial8 = &uart8;

serial9 = &uart9;

ir0 = &irrx;

ir1 = &s_irrx;

ir2 = &irtx;

pcie = &pcie;

gpadc0 = &gpadc0;

gpadc1 = &gpadc1;

twi0 = &twi0;

twi1 = &twi1;

twi2 = &twi2;

twi3 = &twi3;

twi4 = &twi4;

twi5 = &twi5;

twi6 = &twi6;

twi7 = &twi7;

twi8 = &twi8;

spi0 = &spi0;

spi1 = &spi1;

spi2 = &spi2;

spi3 = &r_spi0;

spif0 = &spif0;

nand0 = &nand0;

ve0 = &ve;

ve1 = &ve1;

sunxi-mmc0 = &sdc0;

sunxi-mmc2 = &sdc2;

gmac0 = &gmac0;

gmac1 = &gmac1;

edp0 = &edp0;

nsi0 = &nsi0;

};

reg_vdd_sys: vdd-sys {

compatible = "regulator-fixed";

regulator-name = "vdd_sys";

regulator-min-microvolt = <900000>;

regulator-max-microvolt = <900000>;

regulator-boot-on;

regulator-always-on;

};

reserved-memory {

#address-cells = <2>;

#size-cells = <2>;

ranges;

bl31 {

reg = <0x0 0x48000000 0x0 0x01000000>;

};

};

firmware {

android {

compatible = "android,firmware";

name = "android";

boot_devices = "soc@3000000/4020000.sdmmc,soc@3000000/4022000.sdmmc,soc@3000000";

vbmeta {

compatible = "android,vbmeta";

parts = "vbmeta,vbmeta_system,vbmeta_vendor,boot,init_boot";

};

};

optee {

compatible = "linaro,optee-tz";

method = "smc";

};

};

cpus {

#address-cells = <2>;

#size-cells = <0>;

cpu0: cpu@0 {

device_type = "cpu";

compatible = "arm,cortex-a55";

reg = <0x0 0x0>;

enable-method = "psci";

cpu-idle-states = <&CPU_SLEEP_0 &CLUSTER_SLEEP_0>;

capacity-dmips-mhz = <922>;

clocks = <&cpupll_ccu CLK_PLL_CPU1>;

operating-points-v2 = <&cluster0_opp_table>;

#cooling-cells = <2>;

dynamic-power-coefficient = <286>;

};

cpu1: cpu@100 {

device_type = "cpu";

compatible = "arm,cortex-a55";

reg = <0x0 0x100>;

enable-method = "psci";

cpu-idle-states = <&CPU_SLEEP_0 &CLUSTER_SLEEP_0>;

capacity-dmips-mhz = <922>;

clocks = <&cpupll_ccu CLK_PLL_CPU1>;

operating-points-v2 = <&cluster0_opp_table>;

#cooling-cells = <2>;

};

cpu2: cpu@200 {

device_type = "cpu";

compatible = "arm,cortex-a55";

reg = <0x0 0x200>;

enable-method = "psci";

cpu-idle-states = <&CPU_SLEEP_0 &CLUSTER_SLEEP_0>;

capacity-dmips-mhz = <922>;

clocks = <&cpupll_ccu CLK_PLL_CPU1>;

operating-points-v2 = <&cluster0_opp_table>;

#cooling-cells = <2>;

};

cpu3: cpu@300 {

device_type = "cpu";

compatible = "arm,cortex-a55";

reg = <0x0 0x300>;

enable-method = "psci";

cpu-idle-states = <&CPU_SLEEP_0 &CLUSTER_SLEEP_0>;

capacity-dmips-mhz = <922>;

clocks = <&cpupll_ccu CLK_PLL_CPU1>;

operating-points-v2 = <&cluster0_opp_table>;

#cooling-cells = <2>;

};

cpu4: cpu@400 {

device_type = "cpu";

compatible = "arm,cortex-a55";

reg = <0x0 0x400>;

enable-method = "psci";

cpu-idle-states = <&CPU_SLEEP_0 &CLUSTER_SLEEP_0>;

capacity-dmips-mhz = <1024>;

clocks = <&cpupll_ccu CLK_PLL_CPU3>;

operating-points-v2 = <&cluster1_opp_table>;

#cooling-cells = <2>;

dynamic-power-coefficient = <354>;

};

cpu5: cpu@500 {

device_type = "cpu";

compatible = "arm,cortex-a55";

reg = <0x0 0x500>;

enable-method = "psci";

cpu-idle-states = <&CPU_SLEEP_0 &CLUSTER_SLEEP_0>;

capacity-dmips-mhz = <1024>;

clocks = <&cpupll_ccu CLK_PLL_CPU3>;

operating-points-v2 = <&cluster1_opp_table>;

#cooling-cells = <2>;

};

cpu6: cpu@600 {

device_type = "cpu";

compatible = "arm,cortex-a55";

reg = <0x0 0x600>;

enable-method = "psci";

cpu-idle-states = <&CPU_SLEEP_0 &CLUSTER_SLEEP_0>;

capacity-dmips-mhz = <1024>;

clocks = <&cpupll_ccu CLK_PLL_CPU3>;

operating-points-v2 = <&cluster1_opp_table>;

#cooling-cells = <2>;

};

cpu7: cpu@700 {

device_type = "cpu";

compatible = "arm,cortex-a55";

reg = <0x0 0x700>;

enable-method = "psci";

cpu-idle-states = <&CPU_SLEEP_0 &CLUSTER_SLEEP_0>;

capacity-dmips-mhz = <1024>;

clocks = <&cpupll_ccu CLK_PLL_CPU3>;

operating-points-v2 = <&cluster1_opp_table>;

#cooling-cells = <2>;

};

cpu-map {

cluster0 {

core0 {

cpu = <&cpu0>;

};

core1 {

cpu = <&cpu1>;

};

core2 {

cpu = <&cpu2>;

};

core3 {

cpu = <&cpu3>;

};

};

cluster1 {

core0 {

cpu = <&cpu4>;

};

core1 {

cpu = <&cpu5>;

};

core2 {

cpu = <&cpu6>;

};

core3 {

cpu = <&cpu7>;

};

};

};

idle-states {

entry-method = "arm,psci";

CPU_SLEEP_0: cpu-sleep-0 {

compatible = "arm,idle-state";

arm,psci-suspend-param = <0x0010000>;

entry-latency-us = <46>;

exit-latency-us = <59>;

min-residency-us = <3570>;

local-timer-stop;

};

CLUSTER_SLEEP_0: cluster-sleep-0 {

compatible = "arm,idle-state";

arm,psci-suspend-param = <0x1010000>;

entry-latency-us = <47>;

exit-latency-us = <74>;

min-residency-us = <5000>;

local-timer-stop;

};

};

};

vf_mapping_table: vf_mapping_table {

vf-version = "V0.60";

table = <

0x00 0x0000

0x01 0x0100

0x02 0x0200

0x12 0x0201

0x04 0x0300

0x14 0x0301

0x05 0x0400

0x06 0x0500

>;

};

gpu_vf_mapping_table: gpu_vf_mapping_table {

table = <

0x01 1

0x02 2

0x12 21

0x04 3

0x14 31

0x05 4

0x06 5

>;

};

npu_vf_mapping_table: npu_vf_mapping_table {

table = <

0x01 1

0x02 2

0x12 21

0x04 3

0x14 31

0x05 4

0x06 5

>;

};

cluster0_opp_table: cluster0-opp-table {

compatible = "allwinner,sun50i-operating-points";

opp-shared;

opp@408000000 {

opp-hz = /bits/ 64 <408000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <900000>;

opp-microvolt-vf0100 = <900000>;

opp-microvolt-vf0200 = <900000>;

opp-microvolt-vf0201 = <900000>;

opp-microvolt-vf0300 = <900000>;

opp-microvolt-vf0301 = <900000>;

opp-microvolt-vf0400 = <900000>;

opp-microvolt-vf0500 = <900000>;

};

opp@672000000 {

opp-hz = /bits/ 64 <672000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <900000>;

opp-microvolt-vf0200 = <900000>;

opp-microvolt-vf0201 = <900000>;

opp-microvolt-vf0300 = <900000>;

opp-microvolt-vf0301 = <900000>;

opp-microvolt-vf0400 = <900000>;

opp-microvolt-vf0500 = <900000>;

};

opp@720000000 {

opp-hz = /bits/ 64 <720000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <900000>;

opp-microvolt-vf0100 = <0>;

opp-microvolt-vf0200 = <0>;

opp-microvolt-vf0201 = <0>;

opp-microvolt-vf0300 = <0>;

opp-microvolt-vf0301 = <0>;

opp-microvolt-vf0400 = <0>;

opp-microvolt-vf0500 = <0>;

};

opp@792000000 {

opp-hz = /bits/ 64 <792000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <900000>;

opp-microvolt-vf0200 = <900000>;

opp-microvolt-vf0201 = <900000>;

opp-microvolt-vf0300 = <900000>;

opp-microvolt-vf0301 = <900000>;

opp-microvolt-vf0400 = <900000>;

opp-microvolt-vf0500 = <900000>;

};

opp@936000000 {

opp-hz = /bits/ 64 <936000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <900000>;

opp-microvolt-vf0100 = <920000>;

opp-microvolt-vf0200 = <920000>;

opp-microvolt-vf0201 = <920000>;

opp-microvolt-vf0300 = <900000>;

opp-microvolt-vf0301 = <900000>;

opp-microvolt-vf0400 = <900000>;

opp-microvolt-vf0500 = <900000>;

};

opp@1008000000 {

opp-hz = /bits/ 64 <1008000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <960000>;

opp-microvolt-vf0200 = <960000>;

opp-microvolt-vf0201 = <960000>;

opp-microvolt-vf0300 = <920000>;

opp-microvolt-vf0301 = <920000>;

opp-microvolt-vf0400 = <0>;

opp-microvolt-vf0500 = <920000>;

};

opp@1032000000 {

opp-hz = /bits/ 64 <1032000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <0>;

opp-microvolt-vf0200 = <0>;

opp-microvolt-vf0201 = <0>;

opp-microvolt-vf0300 = <0>;

opp-microvolt-vf0301 = <0>;

opp-microvolt-vf0400 = <920000>;

opp-microvolt-vf0500 = <0>;

};

opp@1104000000 {

opp-hz = /bits/ 64 <1104000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <1000000>;

opp-microvolt-vf0200 = <1000000>;

opp-microvolt-vf0201 = <1000000>;

opp-microvolt-vf0300 = <960000>;

opp-microvolt-vf0301 = <960000>;

opp-microvolt-vf0400 = <0>;

opp-microvolt-vf0500 = <960000>;

};

opp@1128000000 {

opp-hz = /bits/ 64 <1128000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <1000000>;

opp-microvolt-vf0100 = <0>;

opp-microvolt-vf0200 = <0>;

opp-microvolt-vf0201 = <0>;

opp-microvolt-vf0300 = <0>;

opp-microvolt-vf0301 = <0>;

opp-microvolt-vf0400 = <960000>;

opp-microvolt-vf0500 = <0>;

};

opp@1224000000 {

opp-hz = /bits/ 64 <1224000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <1050000>;

opp-microvolt-vf0100 = <1050000>;

opp-microvolt-vf0200 = <1050000>;

opp-microvolt-vf0201 = <1050000>;

opp-microvolt-vf0300 = <1000000>;

opp-microvolt-vf0301 = <1000000>;

opp-microvolt-vf0400 = <1000000>;

opp-microvolt-vf0500 = <1000000>;

};

opp@1296000000 {

opp-hz = /bits/ 64 <1296000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <1100000>;

opp-microvolt-vf0100 = <0>;

opp-microvolt-vf0200 = <0>;

opp-microvolt-vf0201 = <0>;

opp-microvolt-vf0300 = <0>;

opp-microvolt-vf0301 = <0>;

opp-microvolt-vf0400 = <0>;

opp-microvolt-vf0500 = <0>;

};

opp@1320000000 {

opp-hz = /bits/ 64 <1320000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <1120000>;

opp-microvolt-vf0200 = <1120000>;

opp-microvolt-vf0201 = <1120000>;

opp-microvolt-vf0300 = <1050000>;

opp-microvolt-vf0301 = <1050000>;

opp-microvolt-vf0400 = <1050000>;

opp-microvolt-vf0500 = <1050000>;

};

opp@1416000000 {

opp-hz = /bits/ 64 <1416000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <1150000>;

opp-microvolt-vf0100 = <1150000>;

opp-microvolt-vf0200 = <1150000>;

opp-microvolt-vf0201 = <1150000>;

opp-microvolt-vf0300 = <1100000>;

opp-microvolt-vf0301 = <1100000>;

opp-microvolt-vf0400 = <1100000>;

opp-microvolt-vf0500 = <1100000>;

};

};

cluster1_opp_table: cluster1-opp-table {

compatible = "allwinner,sun50i-operating-points";

opp-shared;

opp@408000000 {

opp-hz = /bits/ 64 <408000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <900000>;

opp-microvolt-vf0100 = <900000>;

opp-microvolt-vf0200 = <900000>;

opp-microvolt-vf0201 = <900000>;

opp-microvolt-vf0300 = <900000>;

opp-microvolt-vf0301 = <900000>;

opp-microvolt-vf0400 = <900000>;

opp-microvolt-vf0500 = <900000>;

};

opp@672000000 {

opp-hz = /bits/ 64 <672000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <900000>;

opp-microvolt-vf0200 = <900000>;

opp-microvolt-vf0201 = <900000>;

opp-microvolt-vf0300 = <900000>;

opp-microvolt-vf0301 = <900000>;

opp-microvolt-vf0400 = <900000>;

opp-microvolt-vf0500 = <900000>;

};

opp@720000000 {

opp-hz = /bits/ 64 <720000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <900000>;

opp-microvolt-vf0100 = <0>;

opp-microvolt-vf0200 = <0>;

opp-microvolt-vf0201 = <0>;

opp-microvolt-vf0300 = <0>;

opp-microvolt-vf0301 = <0>;

opp-microvolt-vf0400 = <0>;

opp-microvolt-vf0500 = <0>;

};

opp@840000000 {

opp-hz = /bits/ 64 <840000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <900000>;

opp-microvolt-vf0200 = <900000>;

opp-microvolt-vf0201 = <900000>;

opp-microvolt-vf0300 = <900000>;

opp-microvolt-vf0301 = <900000>;

opp-microvolt-vf0400 = <900000>;

opp-microvolt-vf0500 = <900000>;

};

opp@1008000000 {

opp-hz = /bits/ 64 <1008000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <900000>;

opp-microvolt-vf0200 = <900000>;

opp-microvolt-vf0201 = <900000>;

opp-microvolt-vf0300 = <900000>;

opp-microvolt-vf0301 = <900000>;

opp-microvolt-vf0400 = <900000>;

opp-microvolt-vf0500 = <900000>;

};

opp@1200000000 {

opp-hz = /bits/ 64 <1200000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <920000>;

opp-microvolt-vf0200 = <920000>;

opp-microvolt-vf0201 = <920000>;

opp-microvolt-vf0300 = <920000>;

opp-microvolt-vf0301 = <920000>;

opp-microvolt-vf0400 = <920000>;

opp-microvolt-vf0500 = <920000>;

};

opp@1248000000 {

opp-hz = /bits/ 64 <1248000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <900000>;

opp-microvolt-vf0100 = <0>;

opp-microvolt-vf0200 = <0>;

opp-microvolt-vf0201 = <0>;

opp-microvolt-vf0300 = <0>;

opp-microvolt-vf0301 = <0>;

opp-microvolt-vf0400 = <0>;

opp-microvolt-vf0500 = <0>;

};

opp@1344000000 {

opp-hz = /bits/ 64 <1344000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <960000>;

opp-microvolt-vf0200 = <960000>;

opp-microvolt-vf0201 = <960000>;

opp-microvolt-vf0300 = <960000>;

opp-microvolt-vf0301 = <960000>;

opp-microvolt-vf0400 = <960000>;

opp-microvolt-vf0500 = <960000>;

};

opp@1488000000 {

opp-hz = /bits/ 64 <1488000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <1000000>;

opp-microvolt-vf0100 = <1000000>;

opp-microvolt-vf0200 = <1000000>;

opp-microvolt-vf0201 = <1000000>;

opp-microvolt-vf0300 = <1000000>;

opp-microvolt-vf0301 = <1000000>;

opp-microvolt-vf0400 = <1000000>;

opp-microvolt-vf0500 = <1000000>;

};

opp@1584000000 {

opp-hz = /bits/ 64 <1584000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <1050000>;

opp-microvolt-vf0100 = <1050000>;

opp-microvolt-vf0200 = <1050000>;

opp-microvolt-vf0201 = <1050000>;

opp-microvolt-vf0300 = <1050000>;

opp-microvolt-vf0301 = <1050000>;

opp-microvolt-vf0400 = <1050000>;

opp-microvolt-vf0500 = <1050000>;

};

opp@1680000000 {

opp-hz = /bits/ 64 <1680000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <1100000>;

opp-microvolt-vf0100 = <1100000>;

opp-microvolt-vf0200 = <1100000>;

opp-microvolt-vf0201 = <1100000>;

opp-microvolt-vf0300 = <1100000>;

opp-microvolt-vf0301 = <1100000>;

opp-microvolt-vf0400 = <1100000>;

opp-microvolt-vf0500 = <0>;

};

opp@1800000000 {

opp-hz = /bits/ 64 <1800000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <1150000>;

opp-microvolt-vf0100 = <1150000>;

opp-microvolt-vf0200 = <1150000>;

opp-microvolt-vf0201 = <1150000>;

opp-microvolt-vf0300 = <1150000>;

opp-microvolt-vf0301 = <1150000>;

opp-microvolt-vf0400 = <1150000>;

opp-microvolt-vf0500 = <0>;

};

opp@1992000000 {

opp-hz = /bits/ 64 <1992000000>;

clock-latency-ns = <244144>; /* 8 32k periods */

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <0>;

opp-microvolt-vf0200 = <0>;

opp-microvolt-vf0201 = <0>;

opp-microvolt-vf0300 = <0>;

opp-microvolt-vf0301 = <0>;

opp-microvolt-vf0400 = <1220000>;

opp-microvolt-vf0500 = <0>;

};

};

dsufreq: dsufreq@0 {

compatible = "allwinner,sun55iw3-dsufreq";

reg = <0x0 0x08815000 0x0 0x1000>;

clocks = <&cpupll_ccu CLK_PLL_CPU2>;

operating-points-v2 = <&dsu_opp_table>;

};

dsu_opp_table: dsu-opp-table {

compatible = "allwinner,dsu-operating-points";

opp@288000000 {

opp-hz = /bits/ 64 <288000000>;

opp-microvolt-vf0000 = <900000>;

opp-microvolt-vf0100 = <0>;

opp-microvolt-vf0200 = <0>;

opp-microvolt-vf0201 = <0>;

opp-microvolt-vf0300 = <0>;

opp-microvolt-vf0301 = <0>;

opp-microvolt-vf0400 = <0>;

opp-microvolt-vf0500 = <0>;

};

opp@408000000 {

opp-hz = /bits/ 64 <408000000>;

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <900000>;

opp-microvolt-vf0200 = <900000>;

opp-microvolt-vf0201 = <900000>;

opp-microvolt-vf0300 = <900000>;

opp-microvolt-vf0301 = <900000>;

opp-microvolt-vf0400 = <900000>;

opp-microvolt-vf0500 = <900000>;

};

opp@528000000 {

opp-hz = /bits/ 64 <528000000>;

opp-microvolt-vf0000 = <900000>;

opp-microvolt-vf0100 = <0>;

opp-microvolt-vf0200 = <0>;

opp-microvolt-vf0201 = <0>;

opp-microvolt-vf0300 = <0>;

opp-microvolt-vf0301 = <0>;

opp-microvolt-vf0400 = <0>;

opp-microvolt-vf0500 = <0>;

};

opp@600000000 {

opp-hz = /bits/ 64 <600000000>;

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <900000>;

opp-microvolt-vf0200 = <900000>;

opp-microvolt-vf0201 = <900000>;

opp-microvolt-vf0300 = <900000>;

opp-microvolt-vf0301 = <900000>;

opp-microvolt-vf0400 = <900000>;

opp-microvolt-vf0500 = <900000>;

};

opp@696000000 {

opp-hz = /bits/ 64 <696000000>;

opp-microvolt-vf0000 = <900000>;

opp-microvolt-vf0100 = <900000>;

opp-microvolt-vf0200 = <900000>;

opp-microvolt-vf0201 = <900000>;

opp-microvolt-vf0300 = <900000>;

opp-microvolt-vf0301 = <900000>;

opp-microvolt-vf0400 = <900000>;

opp-microvolt-vf0500 = <900000>;

};

opp@792000000 {

opp-hz = /bits/ 64 <792000000>;

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <920000>;

opp-microvolt-vf0200 = <920000>;

opp-microvolt-vf0201 = <920000>;

opp-microvolt-vf0300 = <900000>;

opp-microvolt-vf0301 = <900000>;

opp-microvolt-vf0400 = <900000>;

opp-microvolt-vf0500 = <900000>;

};

opp@864000000 {

opp-hz = /bits/ 64 <864000000>;

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <960000>;

opp-microvolt-vf0200 = <960000>;

opp-microvolt-vf0201 = <960000>;

opp-microvolt-vf0300 = <920000>;

opp-microvolt-vf0301 = <920000>;

opp-microvolt-vf0400 = <920000>;

opp-microvolt-vf0500 = <920000>;

};

opp@936000000 {

opp-hz = /bits/ 64 <936000000>;

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <1000000>;

opp-microvolt-vf0200 = <1000000>;

opp-microvolt-vf0201 = <1000000>;

opp-microvolt-vf0300 = <960000>;

opp-microvolt-vf0301 = <960000>;

opp-microvolt-vf0400 = <960000>;

opp-microvolt-vf0500 = <960000>;

};

opp@984000000 {

opp-hz = /bits/ 64 <984000000>;

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <1050000>;

opp-microvolt-vf0200 = <1050000>;

opp-microvolt-vf0201 = <1050000>;

opp-microvolt-vf0300 = <1000000>;

opp-microvolt-vf0301 = <1000000>;

opp-microvolt-vf0400 = <1000000>;

opp-microvolt-vf0500 = <1000000>;

};

opp@1008000000 {

opp-hz = /bits/ 64 <1008000000>;

opp-microvolt-vf0000 = <1000000>;

opp-microvolt-vf0100 = <0>;

opp-microvolt-vf0200 = <0>;

opp-microvolt-vf0201 = <0>;

opp-microvolt-vf0300 = <0>;

opp-microvolt-vf0301 = <0>;

opp-microvolt-vf0400 = <0>;

opp-microvolt-vf0500 = <0>;

};

opp@1056000000 {

opp-hz = /bits/ 64 <1056000000>;

opp-microvolt-vf0000 = <0>;

opp-microvolt-vf0100 = <1100000>;

opp-microvolt-vf0200 = <1100000>;

opp-microvolt-vf0201 = <1100000>;

opp-microvolt-vf0300 = <1050000>;

opp-microvolt-vf0301 = <1050000>;

opp-microvolt-vf0400 = <1050000>;

opp-microvolt-vf0500 = <1050000>;

};

opp@1104000000 {

opp-hz = /bits/ 64 <1104000000>;

opp-microvolt-vf0000 = <1050000>;

opp-microvolt-vf0100 = <0>;

opp-microvolt-vf0200 = <0>;

opp-microvolt-vf0201 = <0>;

opp-microvolt-vf0300 = <0>;

opp-microvolt-vf0301 = <0>;

opp-microvolt-vf0400 = <0>;

opp-microvolt-vf0500 = <0>;

};

opp@1128000000 {

opp-hz = /bits/ 64 <1128000000>;

opp-microvolt-vf0000 = <1100000>;

opp-microvolt-vf0100 = <0>;

opp-microvolt-vf0200 = <0>;

opp-microvolt-vf0201 = <0>;

opp-microvolt-vf0300 = <0>;

opp-microvolt-vf0301 = <0>;

opp-microvolt-vf0400 = <0>;

opp-microvolt-vf0500 = <0>;

};

opp@1152000000 {

opp-hz = /bits/ 64 <1152000000>;

opp-microvolt-vf0000 = <1150000>;

opp-microvolt-vf0100 = <1150000>;

opp-microvolt-vf0200 = <1150000>;

opp-microvolt-vf0201 = <1150000>;

opp-microvolt-vf0300 = <1100000>;

opp-microvolt-vf0301 = <1100000>;

opp-microvolt-vf0400 = <1100000>;

opp-microvolt-vf0500 = <1100000>;

};

};

thermal-zones {

cpul_thermal_zone: cpul_thermal_zone {

polling-delay-passive = <100>;

polling-delay = <1000>;

thermal-sensors = <&ths1 1>;

sustainable-power = <1200>;

cpul_trips: trips {

cpul_threshold: trip-point@0 {

temperature = <70000>;

type = "passive";

hysteresis = <0>;

};

cpul_target: trip-point@1 {

temperature = <90000>;

type = "passive";

hysteresis = <0>;

};

cpul_crit: cpu_crit@0 {

temperature = <110000>;

type = "critical";

hysteresis = <0>;

};

};

cooling-maps {

map0 {

trip = <&cpul_target>;

cooling-device = <&cpu0

THERMAL_NO_LIMIT

THERMAL_NO_LIMIT>;

contribution = <1024>;

};

};

};

cpub_thermal_zone: cpub_thermal_zone {

polling-delay-passive = <100>;

polling-delay = <1000>;

thermal-sensors = <&ths1 0>;

sustainable-power = <1600>;

cpub_trips: trips {

cpub_threshold: trip-point@0 {

temperature = <70000>;

type = "passive";

hysteresis = <0>;

};

cpub_target: trip-point@1 {

temperature = <90000>;

type = "passive";

hysteresis = <0>;

};

cpub_crit: cpu_crit@0 {

temperature = <110000>;

type = "critical";

hysteresis = <0>;

};

};

cooling-maps {

map0 {

trip = <&cpub_target>;

cooling-device = <&cpu4

THERMAL_NO_LIMIT

THERMAL_NO_LIMIT>;

contribution = <1024>;

};

};

};

gpu_thermal_zone: gpu_thermal_zone {

polling-delay-passive = <100>;

polling-delay = <1000>;

thermal-sensors = <&ths1 2>;

sustainable-power = <2400>;

gpu_trips: trips {

gpu_threshold: trip-point@0 {

temperature = <60000>;

type = "passive";

hysteresis = <0>;

};

gpu_target: trip-point@1 {

temperature = <90000>;

type = "passive";

hysteresis = <0>;

};

gpu_crit: gpu_crit@0 {

temperature = <110000>;

type = "critical";

hysteresis = <0>;

};

};

cooling-maps {

map0 {

trip = <&gpu_target>;

cooling-device = <&gpu

THERMAL_NO_LIMIT

THERMAL_NO_LIMIT>;

contribution = <1024>;

};

};

};

npu_thermal_zone {

polling-delay-passive = <100>;

polling-delay = <1000>;

thermal-sensors = <&ths1 3>;

};

ddr_thermal_zone {

polling-delay-passive = <0>;

polling-delay = <0>;

thermal-sensors = <&ths0 0>;

};

};

psci {

compatible = "arm,psci-1.0";

method = "smc";

};

dcxo24M: dcxo24M_clk {

#clock-cells = <0>;

compatible = "fixed-clock";

clock-frequency = <24000000>;

clock-output-names = "dcxo24M";

};

rc_16m: rc16m_clk {

#clock-cells = <0>;

compatible = "fixed-clock";

clock-frequency = <16000000>;

clock-accuracy = <300000000>;

clock-output-names = "rc-16m";

};

ext_32k: ext32k_clk {

#clock-cells = <0>;

compatible = "fixed-clock";

clock-frequency = <32768>;

clock-output-names = "ext-32k";

};

gic: interrupt-controller@3400000 {

compatible = "arm,gic-v3";

#interrupt-cells = <3>;

#address-cells = <0>;

interrupt-controller;

reg = <0x0 0x03400000 0 0x10000>, /* GIC Dist */

<0x0 0x03460000 0 0xFF004>; /* GIC Re */

interrupt-parent = <&gic>;

};

wakeupgen: interrupt-controller@0 {

compatible = "allwinner,sunxi-wakeupgen";

interrupt-controller;

#interrupt-cells = <3>;

#address-cells = <0>;

interrupt-parent = <&gic>;

};

timer_arch {

compatible = "arm,armv8-timer";

interrupts = <GIC_PPI 13 (GIC_CPU_MASK_SIMPLE(4) | IRQ_TYPE_LEVEL_LOW)>,

<GIC_PPI 14 (GIC_CPU_MASK_SIMPLE(4) | IRQ_TYPE_LEVEL_LOW)>,

<GIC_PPI 11 (GIC_CPU_MASK_SIMPLE(4) | IRQ_TYPE_LEVEL_LOW)>,

<GIC_PPI 10 (GIC_CPU_MASK_SIMPLE(4) | IRQ_TYPE_LEVEL_LOW)>;

clock-frequency = <24000000>;

interrupt-parent = <&gic>;

arm,no-tick-in-suspend;

};

power: power-management@7001400 {

compatible = "allwinner,a523-pmu", "syscon", "simple-mfd";

reg = <0x0 0x07001400 0x0 0x400>;

pd: power-controller {

compatible = "allwinner,a523-power-controller";

clocks = <&r_ccu CLK_R_PPU1>;

clock-names = "ppu";

resets = <&r_ccu RST_R_PPU1>;

reset-names = "ppu_rst";

#power-domain-cells = <1>;

#address-cells = <1>;

#size-cells = <0>;

pd_dsp@A523_PD_DSP {

reg = <A523_PD_DSP>;

ppu-always-on;

};

pd_npu@A523_PD_NPU {

reg = <A523_PD_NPU>;

};

pd_sram@A523_PD_SRAM {

reg = <A523_PD_SRAM>;

ppu-always-on;

};

pd_riscv@A523_PD_RISCV {

reg = <A523_PD_RISCV>;

};

};

};

pck: pck-600@7060000 {

compatible = "allwinner,a523-pck", "syscon", "simple-mfd";

reg = <0x0 0x07060000 0x0 0x8000>;

pd1: power-controller {

compatible = "allwinner,a523-pck-600";

clocks = <&r_ccu CLK_R_PPU>;

clock-names = "pck";

resets = <&r_ccu RST_R_PPU>;

reset-names = "pck_rst";

#power-domain-cells = <1>;

#address-cells = <1>;

#size-cells = <0>;

pd1_ve@A523_PCK_VE {

reg = <A523_PCK_VE>;

};

pd1_vi@A523_PCK_VI {

reg = <A523_PCK_VI>;

};

pd1_vo0@A523_PCK_VO0 {

reg = <A523_PCK_VO0>;

};

pd1_vo1@A523_PCK_VO1 {

reg = <A523_PCK_VO1>;

};

pd1_de@A523_PCK_DE {

reg = <A523_PCK_DE>;

};

pd1_nand@A523_PCK_NAND {

reg = <A523_PCK_NAND>;

};

pd1_pcie@A523_PCK_PCIE {

reg = <A523_PCK_PCIE>;

};

};

};

nmi_intc: intc-nmi@7010320 {

compatible = "allwinner,sun8i-nmi";

interrupt-parent = <&gic>;

#interrupt-cells = <2>;

#address-cells = <0>;

interrupt-controller;

reg = <0x0 0x07010320 0 0xc>;

interrupts = <GIC_SPI 148 IRQ_TYPE_LEVEL_HIGH>;

};

mmu_aw: iommu@2010000 {

compatible = "allwinner,iommu-v15-sun55iw3";

reg = <0x0 0x02010000 0x0 0x1000>;

interrupts = <GIC_SPI 65 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "iommu-irq";

clocks = <&ccu CLK_IOMMU>;

clock-names = "iommu";

/* clock-frequency = <24000000>; */

#iommu-cells = <2>;

};

dram: dram {

compatible = "allwinner,dram";

clocks = <&ccu CLK_PLL_DDR>;

clock-names = "pll_ddr";

};

ddr_clk: clk_ddr {

compatible = "allwinner,clock_ddr";

reg = <0x0 0x02001000 0x0 0x1000>;

clocks = <&ccu CLK_PLL_DDR>;

clock-names = "pll_ddr";

#clock-cells = <0>;

};

dram_opp_table: opp_table {

compatible = "operating-points-v2";

opp@150000000 {

opp-hz = /bits/ 64 <150000000>;

clock-latency-ns = <150000>;

opp-microvolt = <900000>;

};

};

sunxi_dmcfreq: dmcfreq@3120000 {

compatible = "allwinner,sun55iw3-dmc", "syscon";

reg = <0x0 0x03120000 0x0 0x11000>,

<0x0 0x02020000 0x0 0x4000>;

interrupts = <GIC_SPI 121 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ddr_clk>, <&ccu CLK_NSI>;

clock-names = "dram", "bus";

operating-points-v2 = <&dram_opp_table>;

upthreshold = <60>;

downdifferential = <20>;

vddcore-supply = <®_vdd_sys>;

normalvoltage = <900000>;

boostvoltage = <900000>;

};

soc: soc@3000000 {

compatible = "simple-bus";

#address-cells = <2>;

#size-cells = <2>;

ranges;

rt-media@1c0e000 {

compatible = "allwinner,rt-media";

};

ve: ve@1c0e000 {

compatible = "allwinner,sunxi-cedar-ve";

reg = <0x0 0x01c0e000 0x0 0x1000>,

<0x0 0x03000000 0x0 0x10>;

interrupts = <GIC_SPI 120 IRQ_TYPE_LEVEL_HIGH>;

clocks =<&ccu CLK_BUS_VE>, <&ccu CLK_VE>, <&ccu CLK_VE_MBUS_GATE>;

clock-names = "bus_ve", "ve", "mbus_ve";

resets = <&ccu RST_BUS_VE>;

reset-names = "reset_ve";

iommus = <&mmu_aw 2 1>;

power-domains = <&pd1 A523_PCK_VE>;

};

ve1: ve1@1c0e000 {

compatible = "allwinner,sunxi-cedar-ve";

iommus = <&mmu_aw 3 1>;

};

pd_ve_test: pd-ve-test@0 {

compatible = "allwinner,sunxi-power-domain-test";

reg = <0x0 0x0 0x0 0x0>;

power-domains = <&pd1 A523_PCK_VE>;

status = "okay";

};

pd_vi_test: pd-vi-test@0 {

compatible = "allwinner,sunxi-power-domain-test";

reg = <0x0 0x0 0x0 0x0>;

power-domains = <&pd1 A523_PCK_VI>;

status = "okay";

};

pd_vo0_test: pd-vo0-test@0 {

compatible = "allwinner,sunxi-power-domain-test";

reg = <0x0 0x0 0x0 0x0>;

power-domains = <&pd1 A523_PCK_VO0>;

status = "okay";

};

pd_vo1_test: pd-vo1-test@0 {

compatible = "allwinner,sunxi-power-domain-test";

reg = <0x0 0x0 0x0 0x0>;

power-domains = <&pd1 A523_PCK_VO1>;

status = "okay";

};

pd_de_test: pd-de-test@0 {

compatible = "allwinner,sunxi-power-domain-test";

reg = <0x0 0x0 0x0 0x0>;

power-domains = <&pd1 A523_PCK_DE>;

status = "okay";

};

pd_nand_test: pd-nand-test@0 {

compatible = "allwinner,sunxi-power-domain-test";

reg = <0x0 0x0 0x0 0x0>;

power-domains = <&pd1 A523_PCK_NAND>;

status = "okay";

};

pd_pcie_test: pd-pcie-test@0 {

compatible = "allwinner,sunxi-power-domain-test";

reg = <0x0 0x0 0x0 0x0>;

power-domains = <&pd1 A523_PCK_PCIE>;

status = "okay";

};

pd_dsp_test: pd-dsp-test@0 {

compatible = "allwinner,sunxi-power-domain-test";

reg = <0x0 0x0 0x0 0x0>;

power-domains = <&pd A523_PD_DSP>;

status = "okay";

};

pd_npu_test: pd-npu-test@0 {

compatible = "allwinner,sunxi-power-domain-test";

reg = <0x0 0x0 0x0 0x0>;

power-domains = <&pd A523_PD_NPU>;

status = "okay";

};

pd_sram_test: pd-sram-test@0 {

compatible = "allwinner,sunxi-power-domain-test";

reg = <0x0 0x0 0x0 0x0>;

power-domains = <&pd A523_PD_SRAM>;

status = "okay";

};

pd_riscv_test: pd-riscv-test@0 {

compatible = "allwinner,sunxi-power-domain-test";

reg = <0x0 0x0 0x0 0x0>;

power-domains = <&pd A523_PD_RISCV>;

status = "okay";

};

test_ccu: test_ccu@3000090 {

compatible = "allwinner,sun55iw3-test-ccu";

device_type = "ccu-test";

resets = <&ccu RST_BUS_UART7>, <&ccu RST_BUS_UART6>;

reset-names = "rst-uart7", "rst-uart6";

reg = <0x0 0x3000090 0x0 0x8>;

#clock-cells = <1>;

};

rtc_ccu: rtc_ccu@7090000 {

compatible = "allwinner,sun55iw3-rtc-ccu";

reg = <0x0 0x07090000 0x0 0x400>;

#clock-cells = <1>;

#reset-cells = <1>;

};

cpupll_ccu: clock@8817000 {

compatible = "allwinner,sun55iw3-cpupll";

reg = <0x0 0x08817000 0x0 0x4000>;

#clock-cells = <1>;

#reset-cells = <1>;

pll_step = <0x9>;

/* pll_ssc will divid pll_ssc_scale in code

* keep value 0 < pll_ssc < 10

*/

pll_ssc_scale = <0xa>;

pll_ssc = <0x1>;

};

ccu: ccu@2001000 {

compatible = "allwinner,sun55iw3-ccu";

reg = <0x0 0x02001000 0x0 0x1000>;

clocks = <&dcxo24M>, <&rtc_ccu CLK_OSC32K>, <&rc_16m>;

clock-names = "hosc", "losc", "iosc";

#clock-cells = <1>;

#reset-cells = <1>;

/*

* sdm info:

* for example:

* pll_npux4 {

* sdm-enable = <1>; // required

* sdm-factor = <4>; // required

* freq-mod = <TR_N>; // optional: default TR_N

* sdm-freq = <FREQ_32>; // optional: default FREQ_31_5

* };

*/

};

r_ccu: r_ccu@7010000 {

compatible = "allwinner,sun55iw3-r-ccu";

reg = <0x0 0x07010000 0x0 0x230>;

#clock-cells = <1>;

#reset-cells = <1>;

};

mcu_ccu: mcu_ccu@7102000 {

compatible = "allwinner,sun55iw3-mcu-ccu";

reg = <0x0 0x07102000 0x0 0x165>;

#clock-cells = <1>;

#reset-cells = <1>;

};

disp: disp@5000000 {

compatible = "allwinner,sunxi-disp";

reg = <0x0 0x05000000 0x0 0x400000>, /*de*/

<0x0 0x05500000 0x0 0x1000>, /* display_if_top */

<0x0 0x05501000 0x0 0x1000>, /* tcon0 - tcon_lcd0 */

<0x0 0x05502000 0x0 0x1000>, /* tcon1 - tcon_lcd1 */

<0x0 0x05503000 0x0 0x1000>, /* tcon2 - tcon_tv0 */

<0x0 0x05504000 0x0 0x1000>, /* tcon3 - tcon_tv1 */

<0x0 0x05731000 0x0 0x1000>, /* tcon4 - tcon_lcd2 */

<0x0 0x05506000 0x0 0x1fff>, /* dsi0 */

<0x0 0x05508000 0x0 0x1fff>; /* dsi1 */

interrupts = <GIC_SPI 87 IRQ_TYPE_LEVEL_HIGH>, /* DE */

<GIC_SPI 90 IRQ_TYPE_LEVEL_HIGH>, /* tcon_lcd0 */

<GIC_SPI 92 IRQ_TYPE_LEVEL_HIGH>, /* tcon_lcd1 */

<GIC_SPI 91 IRQ_TYPE_LEVEL_HIGH>, /* tcon_tv0 */

<GIC_SPI 96 IRQ_TYPE_LEVEL_HIGH>, /* tcon_tv1 */

<GIC_SPI 97 IRQ_TYPE_LEVEL_HIGH>, /* tcon_lcd2 */

<GIC_SPI 94 IRQ_TYPE_LEVEL_HIGH>, /* dsi0 */

<GIC_SPI 95 IRQ_TYPE_LEVEL_HIGH>; /* dsi1 */

clocks = <&ccu CLK_DE>,

<&ccu CLK_DE>,

<&ccu CLK_DE0>,

<&ccu CLK_DE0>,

<&ccu CLK_VO0_TCONLCD0>,

<&ccu CLK_VO0_TCONLCD1>,

<&ccu CLK_TCONTV>,

<&ccu CLK_TCONTV1>,

<&ccu CLK_VO1_TCONLCD0>,

<&ccu CLK_BUS_VO0_TCONLCD0>,

<&ccu CLK_BUS_VO0_TCONLCD1>,

<&ccu CLK_BUS_TCONTV>,

<&ccu CLK_BUS_TCONTV1>,

<&ccu CLK_BUS_VO1_TCONLCD0>,

<&ccu CLK_DPSS_TOP0>,

<&ccu CLK_DPSS_TOP0>,

<&ccu CLK_DPSS_TOP0>,

<&ccu CLK_DPSS_TOP0>,

<&ccu CLK_DPSS_TOP1>,

<&ccu CLK_DSI0>,

<&ccu CLK_DSI1>,

<&ccu CLK_BUS_DSI0>,

<&ccu CLK_BUS_DSI1>,

<&ccu CLK_COMBPHY0>,

<&ccu CLK_COMBPHY1>;

clock-names = "clk_de0",

"clk_de1",

"clk_bus_de0",

"clk_bus_de1",

"clk_tcon0",

"clk_tcon1",

"clk_tcon2",

"clk_tcon3",

"clk_tcon4",

"clk_bus_tcon0",

"clk_bus_tcon1",

"clk_bus_tcon2",

"clk_bus_tcon3",

"clk_bus_tcon4",

"clk_bus_dpss_top0",

"clk_bus_dpss_top1",

"clk_bus_dpss_top2",

"clk_bus_dpss_top3",

"clk_bus_dpss_top4",

"clk_mipi_dsi0",

"clk_mipi_dsi1",

"clk_bus_mipi_dsi0",

"clk_bus_mipi_dsi1",

"clk_mipi_dsi_combphy0",

"clk_mipi_dsi_combphy1";

resets = <&ccu RST_BUS_DE0>,

<&ccu RST_BUS_DE0>,

<&ccu RST_BUS_VO0_TCONLCD0>,

<&ccu RST_BUS_VO0_TCONLCD1>,

<&ccu RST_BUS_TCONTV>,

<&ccu RST_BUS_TCONTV1>,

<&ccu RST_BUS_VO1_TCONLCD0>,

<&ccu RST_BUS_LVDS0>,

<&ccu RST_BUS_LVDS1>,

<&ccu RST_BUS_DPSS_TOP0>,

<&ccu RST_BUS_DPSS_TOP0>,

<&ccu RST_BUS_DPSS_TOP0>,

<&ccu RST_BUS_DPSS_TOP0>,

<&ccu RST_BUS_DPSS_TOP1>,

<&ccu RST_BUS_DSI0>,

<&ccu RST_BUS_DSI1>;

reset-names = "rst_bus_de0",

"rst_bus_de1",

"rst_bus_tcon0",

"rst_bus_tcon1",

"rst_bus_tcon2",

"rst_bus_tcon3",

"rst_bus_tcon4",

"rst_bus_lvds0",

"rst_bus_lvds1",

"rst_bus_dpss_top0",

"rst_bus_dpss_top1",

"rst_bus_dpss_top2",

"rst_bus_dpss_top3",

"rst_bus_dpss_top4",

"rst_bus_mipi_dsi0",

"rst_bus_mipi_dsi1";

assigned-clocks = <&ccu CLK_DE>,

<&ccu CLK_VO0_TCONLCD0>,

<&ccu CLK_VO0_TCONLCD1>,

<&ccu CLK_VO1_TCONLCD0>,

<&ccu CLK_BUS_TCONTV>,

<&ccu CLK_TCONTV>,

<&ccu CLK_TCONTV1>,

<&ccu CLK_DSI0>,

<&ccu CLK_DSI1>,

<&ccu CLK_COMBPHY0>,

<&ccu CLK_COMBPHY1>;

assigned-clock-parents = <&ccu CLK_PLL_VIDEO3_4X>,

<&ccu CLK_PLL_VIDEO0_4X>,

<&ccu CLK_PLL_VIDEO0_4X>,

<&ccu CLK_PLL_VIDEO0_4X>,

<&ccu CLK_PLL_VIDEO0_4X>,

<&ccu CLK_PLL_VIDEO1_4X>,

<&ccu CLK_PLL_VIDEO1_4X>,

<&ccu CLK_PLL_PERI0_150M>,

<&ccu CLK_PLL_PERI0_150M>,

<&ccu CLK_PLL_VIDEO0_4X>,

<&ccu CLK_PLL_VIDEO0_4X>;

assigned-clock-rates = <600000000>;

iommus = <&mmu_aw 5 0>;

/*power-domains = <&pd1 A523_PCK_DE>, <&pd1 A523_PCK_VO0>, <&pd1 A523_PCK_VO1>;

power-domain-names = "pd_de", "pd_vo0", "pd_vo1";*/

power-domains = <&pd1 A523_PCK_DE>, <&pd1 A523_PCK_VO0>;

power-domain-names = "pd_de", "pd_vo0";

status = "okay";

boot_disp = <0>;

fb_base = <0>;

};

hdmi: hdmi@5520000 {

compatible = "allwinner,sunxi-hdmi";

reg = <0x0 0x05520000 0x0 0x100000>;

interrupts = <GIC_SPI 93 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_HDMI>,

<&ccu CLK_HDMI_24M>,

<&ccu CLK_HDMI_CEC>,

<&ccu CLK_TCONTV>;

clock-names = "clk_hdmi",

"clk_hdmi_24M",

"clk_cec",

"clk_tcon_tv";

resets = <&ccu RST_BUS_HDMI_SUB>,

<&ccu RST_BUS_HDMI_MAIN>;

reset-names = "rst_bus_sub",

"rst_bus_main";

assigned-clocks = <&ccu CLK_HDMI>;

assigned-clock-rates = <0>, <0>;

status = "okay";

};

edp0: edp0@5720000 {

compatible = "allwinner,sunxi-edp0";

reg = <0x0 0x05720000 0x0 0x4000>;

interrupts = <GIC_SPI 144 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_BUS_EDP>,

<&ccu CLK_EDP>,

<&ccu CLK_HDMI_24M>;

clock-names = "clk_bus_edp", "clk_edp", "edp_clk_24m";

resets = <&ccu RST_BUS_EDP>;

reset-names = "rst_bus_edp";

assigned-clocks = <&ccu CLK_EDP>;

assigned-clock-parents = <&ccu CLK_PLL_VIDEO1_4X>;

status = "disabled";

};

lcd0: lcd0@1c0c000 {

compatible = "allwinner,sunxi-lcd0";

/* Fake registers to avoid dtc compiling warnings */

reg = <0x0 0x1c0c000 0x0 0x0>;

pinctrl-names = "active","sleep";

};

lcd1: lcd1@1c0c000 {

compatible = "allwinner,sunxi-lcd1";

/* Fake registers to avoid dtc compiling warnings */

reg = <0x0 0x1c0c000 0x0 0x0>;

pinctrl-names = "active","sleep";

};

lcd2: lcd2@1c0c000 {

compatible = "allwinner,sunxi-lcd2";

/* Fake registers to avoid dtc compiling warnings */

reg = <0x0 0x1c0c000 0x0 0x0>;

pinctrl-names = "active","sleep";

};

r_pio: pinctrl@7022000 {

#address-cells = <1>;

compatible = "allwinner,sun55iw3-r-pinctrl";

reg = <0x0 0x07022000 0x0 0x800>,

<0x0 0x07010374 0x0 0x4>,

<0x0 0x07010378 0x0 0x4>;

/*

* The reg control i2s0/dmic routes to cpus-pad or sys-pad

* 0: use cpus pad, 1: use sys pad

*/

reg-names = "r-pio", "i2s0", "dmic";

interrupts = <GIC_SPI 159 IRQ_TYPE_LEVEL_HIGH>, /* GPIOL */

<GIC_SPI 161 IRQ_TYPE_LEVEL_HIGH>; /* GPIOM */

clocks = <&ccu CLK_R_APBS1>, <&dcxo24M>, <&rtc_ccu CLK_OSC32K>;

clock-names = "apb", "hosc", "losc";

gpio-controller;

#gpio-cells = <3>;

interrupt-controller;

#interrupt-cells = <3>;

};

g2d: g2d@5440000 {

compatible = "allwinner,sunxi-g2d";

reg = <0x0 0x05440000 0x0 0x30000>;

interrupts = <GIC_SPI 143 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_BUS_G2D>, <&ccu CLK_G2D>;

clock-names = "bus", "g2d";

resets = <&ccu RST_BUS_G2D>;

iommus = <&mmu_aw 4 1>;

power-domains = <&pd1 A523_PCK_VO0>;

power-domain-names = "pd1_vo0";

assigned-clocks = <&ccu CLK_G2D>;

assigned-clock-rates = <300000000>;

};

pio: pinctrl@2000000 {

#address-cells = <1>;

compatible = "allwinner,sun55iw3-pinctrl";

/*

* The reg control i2s0/dmic routes to cpus-pad or sys-pad

* 0: use cpus pad, 1: use sys pad

*/

reg = <0x0 0x02000000 0x0 0x800>,

<0x0 0x07010374 0x0 0x4>,

<0x0 0x07010378 0x0 0x4>;

reg-names = "pio", "i2s0", "dmic";

interrupts = <GIC_SPI 69 IRQ_TYPE_LEVEL_HIGH>, /* GPIOB */

<GIC_SPI 71 IRQ_TYPE_LEVEL_HIGH>, /* GPIOC */

<GIC_SPI 73 IRQ_TYPE_LEVEL_HIGH>, /* GPIOD */

<GIC_SPI 75 IRQ_TYPE_LEVEL_HIGH>, /* GPIOE */

<GIC_SPI 77 IRQ_TYPE_LEVEL_HIGH>, /* GPIOF */

<GIC_SPI 79 IRQ_TYPE_LEVEL_HIGH>, /* GPIOG */

<GIC_SPI 81 IRQ_TYPE_LEVEL_HIGH>, /* GPIOH */

<GIC_SPI 83 IRQ_TYPE_LEVEL_HIGH>, /* GPIOI */

<GIC_SPI 85 IRQ_TYPE_LEVEL_HIGH>, /* GPIOJ */

<GIC_SPI 140 IRQ_TYPE_LEVEL_HIGH>; /* GPIOK */

clocks = <&ccu CLK_APB1>, <&dcxo24M>, <&rtc_ccu CLK_OSC32K>;

clock-names = "apb", "hosc", "losc";

gpio-controller;

#gpio-cells = <3>;

interrupt-controller;

#interrupt-cells = <3>;

sdc0_pins_a: sdc0@0 {

pins = "PF0", "PF1", "PF2",

"PF3", "PF4", "PF5";

function = "sdc0";

drive-strength = <40>;

bias-pull-up;

power-source = <3300>;

};

sdc0_pins_b: sdc0@1 {

pins = "PF0", "PF1", "PF2",

"PF3", "PF4", "PF5";

function = "sdc0";

drive-strength = <40>;

bias-pull-up;

power-source = <1800>;

};

sdc0_pins_c: sdc0@2 {

pins = "PF0", "PF1", "PF2",

"PF3", "PF4", "PF5";

function = "gpio_in";

power-source = <3300>;

};

/* TODO: add jtag pin */

sdc0_pins_d: sdc0@3 {

pins = "PF2", "PF4";

function = "uart0";

drive-strength = <10>;

bias-pull-up;

power-source = <3300>;

};

sdc0_pins_e: sdc0@4 {

pins = "PF0", "PF1", "PF3",

"PF5";

function = "jtag";

drive-strength = <10>;

bias-pull-up;

power-source = <3300>;

};

sdc1_pins_a: sdc1@0 {

pins = "PG0", "PG1", "PG2",

"PG3", "PG4", "PG5";

function = "sdc1";

drive-strength = <40>;

bias-pull-up;

};

sdc1_pins_b: sdc1@1 {

pins = "PG0", "PG1", "PG2",

"PG3", "PG4", "PG5";

function = "gpio_in";

};

sdc2_pins_a: sdc2@0 {

pins = "PC1", "PC5", "PC6",

"PC8", "PC9", "PC10", "PC11",

"PC13", "PC14", "PC15", "PC16";

function = "sdc2";

drive-strength = <40>;

bias-pull-up;

};

sdc2_pins_b: sdc2@1 {

pins = "PC0", "PC1", "PC5", "PC6",

"PC8", "PC9", "PC10", "PC11",

"PC13", "PC14", "PC15", "PC16";

function = "gpio_in";

};

sdc2_pins_c: sdc2@2 {

pins = "PC0";

function = "sdc2";

drive-strength = <40>;

bias-pull-down;

};

uart1_pins_a: uart1@0 {

pins = "PG6", "PG7", "PG8", "PG9";

function = "uart1";

drive-strength = <10>;

bias-pull-up;

};

uart1_pins_b: uart1@1 {

pins = "PG6", "PG7", "PG8", "PG9";

function = "gpio_in";

};

dsi0_4lane_pins_a: dsi0_4lane@0 {

pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD8", "PD9";

function = "dsi0";

drive-strength = <30>;

bias-disable;

};

dsi0_4lane_pins_b: dsi0_4lane@1 {

pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD8", "PD9";

function = "io_disabled";

bias-disable;

};

dsi1_4lane_pins_a: dsi1_4lane@0 {

pins = "PD10", "PD11", "PD12", "PD13", "PD14", "PD15", "PD16", "PD17", "PD18", "PD19";

function = "dsi1";

drive-strength = <30>;

bias-disable;

};

dsi1_4lane_pins_b: dsi1_4lane@1 {

pins = "PD10", "PD11", "PD12", "PD13", "PD14", "PD15", "PD16", "PD17", "PD18", "PD19";

function = "io_disabled";

bias-disable;

};

rgb18_pins_a: rgb18@0 {

pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD8", "PD9", \

"PD10", "PD11", "PD12", "PD13", "PD14", "PD15", "PD16", "PD17", "PD18", "PD19", \

"PD20", "PD21";

function = "lcd0";

drive-strength = <30>;

};

rgb18_pins_b: rgb18@1 {

pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD8", "PD9", \

"PD10", "PD11", "PD12", "PD13", "PD14", "PD15", "PD16", "PD17", "PD18", "PD19", \

"PD20", "PD21";

function = "gpio_in";

};

lvds1_pins_a: lvds1@0 {

pins = "PD10", "PD11", "PD12", "PD13", "PD14", "PD15", "PD16", "PD17", "PD18", "PD19";

function = "lvds1";

drive-strength = <30>;

};

lvds1_pins_b: lvds1@1 {

pins = "PD10", "PD11", "PD12", "PD13", "PD14", "PD15", "PD16", "PD17", "PD18", "PD19";

function = "gpio_in";

};

lvds2_pins_a: lvds2@0 {

pins = "PJ0", "PJ1", "PJ2", "PJ3", "PJ4", "PJ5", "PJ6", "PJ7", "PJ8", "PJ9";

function = "lvds2";

drive-strength = <30>;

};

lvds2_pins_b: lvds2@1 {

pins = "PJ0", "PJ1", "PJ2", "PJ3", "PJ4", "PJ5", "PJ6", "PJ7", "PJ8", "PJ9";

function = "gpio_in";

};

lvds3_pins_a: lvds3@0 {

pins = "PJ10", "PJ11", "PJ12", "PJ13", "PJ14", "PJ15", "PJ16", "PJ17", "PJ18", "PJ19";

function = "lvds3";

drive-strength = <30>;

};

lvds3_pins_b: lvds3@1 {

pins = "PJ10", "PJ11", "PJ12", "PJ13", "PJ14", "PJ15", "PJ16", "PJ17", "PJ18", "PJ19";

function = "gpio_in";

};

/*

csi_mclk0_pins_a: csi_mclk0@0 {

pins = "PE0";

function = "mipi0";

drive-strength = <20>;

};

csi_mclk0_pins_b: csi_mclk0@1 {

pins = "PE0";

function = "gpio_in";

};

*/

csi_mclk1_pins_a: csi_mclk1@0 {

pins = "PE5";

function = "mipi1";

drive-strength = <20>;

};

csi_mclk1_pins_b: csi_mclk1@1 {

pins = "PE5";

function = "gpio_in";

};

csi_mclk2_pins_a: csi_mclk2@0 {

pins = "PE15";

function = "mipi2";

drive-strength = <20>;

};

csi_mclk2_pins_b: csi_mclk2@1 {

pins = "PE15";

function = "gpio_in";

};

csi_mclk3_pins_a: csi_mclk3@0 {

pins = "PE10";

function = "mipi3";

drive-strength = <20>;

};

csi_mclk3_pins_b: csi_mclk3@1 {

pins = "PE10";

function = "gpio_in";

};

ncsi_bt656_pins_a: ncsi_BT656@0 {

pins = "PK12", "PK14", "PK15",

"PK16", "PK17", "PK18", "PK19",

"PK20", "PK21", "PK22", "PK23";

function = "ncsi";

drive-strength = <20>;

};

ncsi_bt656_pins_b: ncsi_BT656@1 {

pins = "PK12", "PK14", "PK15",

"PK16", "PK17", "PK18", "PK19",

"PK20", "PK21", "PK22", "PK23";

function = "gpio_in";

};

ncsi_bt1120_pins_a: ncsi_BT1120@0 {

pins = "PK12", "PK14", "PK15",

"PK16", "PK17", "PK18", "PK19",

"PK20", "PK21", "PK22", "PK23",

"PE6", "PE7", "PE8", "PE9",

"PE10", "PE11", "PE12", "PE15";

function = "ncsi";

drive-strength = <20>;

};

ncsi_bt1120_pins_b: ncsi_BT1120@1 {

pins = "PK12", "PK14", "PK15",

"PK16", "PK17", "PK18", "PK19",

"PK20", "PK21", "PK22", "PK23",

"PE6", "PE7", "PE8", "PE9",

"PE10", "PE11", "PE12", "PE15";

function = "gpio_in";

};

mipia_pins_a: mipia@0 {

pins = "PK0", "PK1", "PK2",

"PK3", "PK4", "PK5";

function = "mcsia";

drive-strength = <10>;

};

mipia_pins_b: mipia@1 {

pins = "PK0", "PK1", "PK2",

"PK3", "PK4", "PK5";

function = "gpio_in";

};

mipib_pins_a: mipib@0 {

pins = "PK6", "PK7", "PK8",

"PK9", "PK10", "PK11";

function = "mcsib";

drive-strength = <10>;

};

mipib_pins_b: mipib@1 {

pins = "PK6", "PK7", "PK8",

"PK9", "PK10", "PK11";

function = "gpio_in";

};

mipib_4lane_pins_a: mipib_4lane@0 {

pins = "PK6", "PK7", "PK8",

"PK9", "PK10", "PK11";

function = "mcsib";

drive-strength = <10>;

};

mipib_4lane_pins_b: mipib_4lane@1 {

pins = "PK6", "PK7", "PK8",

"PK9", "PK10", "PK11";

function = "gpio_in";

};

mipic_pins_a: mipic@0 {

pins = "PK12", "PK13", "PK14",

"PK15", "PK16", "PK17";

function = "mcsic";

drive-strength = <10>;

};

mipic_pins_b: mipic@1 {

pins = "PK12", "PK13", "PK14",

"PK15", "PK16", "PK17";

function = "gpio_in";

};

mipid_pins_a: mipid@0 {

pins = "PK18", "PK19", "PK20",

"PK21", "PK22", "PK23";

function = "mcsid";

drive-strength = <10>;

};

mipid_pins_b: mipid@1 {

pins = "PK18", "PK19", "PK20",

"PK21", "PK22", "PK23";

function = "gpio_in";

};

mipid_4lane_pins_a: mipid_4lane@0 {

pins = "PK18", "PK19", "PK20",

"PK21", "PK22", "PK23";

function = "mcsid";

drive-strength = <10>;

};

mipid_4lane_pins_b: mipid_4lane@1 {

pins = "PK18", "PK19", "PK20",

"PK21", "PK22", "PK23";

function = "gpio_in";

};

test_pins_a: test_pins@0 {

pins = "PB2", "PB5";

function = "test";

drive-strength = <10>;

bias-pull-up;

};

test_pins_b: test_pins@1 {

pins = "PB2", "PB5";

function = "gpio_in";

};

};

pinctrl_test: pinctrl_test@2000000 {

reg = <0x0 0x0 0x0 0x0>;

compatible = "allwinner,sunxi-pinctrl-test";

device_type = "pinctrl-test";

pinctrl-0 = <&test_pins_a>;

pinctrl-1 = <&test_pins_b>;

pinctrl-names = "default", "sleep";

test-gpios = <&pio PB 4 GPIO_ACTIVE_LOW>;

suspend-gpios = <&r_pio PL 4 GPIO_ACTIVE_LOW>;

wakeup-source;

interrupt-parent = <&pio>;

interrupts = <PB 6 IRQ_TYPE_LEVEL_HIGH>;

};

ths0: ths0@200a000 {

compatible = "allwinner,sun55iw3p1-ths0";

reg = <0x0 0x0200a000 0x0 0x400>;

clocks = <&ccu CLK_THS>, <&ccu CLK_GPADC0_24M>;

clock-names = "bus", "sclk";

resets = <&ccu RST_BUS_TH>;

#thermal-sensor-cells = <1>;

};

ths1: ths0@2009400 {

compatible = "allwinner,sun55iw3p1-ths1";

reg = <0x0 0x02009400 0x0 0x400>;

clocks = <&ccu CLK_THS>, <&ccu CLK_GPADC1_24M>;

clock-names = "bus", "sclk";

resets = <&ccu RST_BUS_TH>;

#thermal-sensor-cells = <1>;

};

soc_timer0: timer@3008000 {

compatible = "allwinner,sun50i-timer";

device_type = "soc_timer";

reg = <0x0 0x03008000 0x0 0x400>;

interrupt-parent = <&gic>;

interrupts = <GIC_SPI 55 IRQ_TYPE_LEVEL_HIGH>;

clock-names = "parent", "bus", "timer0-mod", "timer1-mod";

clocks = <&dcxo24M>, <&ccu CLK_TIMER>, <&ccu CLK_TIMER0>, <&ccu CLK_TIMER1>;

resets = <&ccu RST_BUS_TIME>;

};

arm_pmu {

compatible = "arm,armv8-pmuv3";

interrupt-parent = <&gic>;

interrupts = <GIC_PPI 7 IRQ_TYPE_LEVEL_HIGH>;

};

dump_reg:dump_reg@40000 {

compatible = "allwinner,sunxi-dump-reg";

reg = <0x0 0x00040000 0x0 0x0004>;

};

soft_jtag_master:soft_jtag_master@0 {

compatible = "allwinner,soft-jtag-master";

tdi-gpios = <&r_pio PL 2 GPIO_ACTIVE_HIGH>;

tdo-gpios = <&r_pio PL 3 GPIO_ACTIVE_HIGH>;

tck-gpios = <&pio PB 11 GPIO_ACTIVE_HIGH>;

tms-gpios = <&pio PB 12 GPIO_ACTIVE_HIGH>;

status = "disabled";

};

reg_pio1_8: pio-18 {

compatible = "regulator-fixed";

regulator-name = "pio-18";

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <1800000>;

};

reg_pio2_8: pio-28 {

compatible = "regulator-fixed";

regulator-name = "pio-28";

regulator-min-microvolt = <2800000>;

regulator-max-microvolt = <2800000>;

};

reg_pio3_3: pio-33 {

compatible = "regulator-fixed";

regulator-name = "pio-33";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

};

uart0: uart@2500000 {

compatible = "allwinner,sun55i-uart";

reg = <0x0 0x02500000 0x0 0x400>;

interrupts = <GIC_SPI 2 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_BUS_UART0>;

resets = <&ccu RST_BUS_UART0>;

uart0_port = <0>;

uart0_type = <2>;

status = "disabled";

};

uart1: uart@2500400 {

compatible = "allwinner,sun55i-uart";

device_type = "uart1";

reg = <0x0 0x02500400 0x0 0x400>;

interrupts = <GIC_SPI 3 IRQ_TYPE_LEVEL_HIGH>;

sunxi,uart-fifosize = <64>;

clocks = <&ccu CLK_BUS_UART1>;

clock-names = "uart1";

resets = <&ccu RST_BUS_UART1>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <&uart1_pins_a>;

pinctrl-1 = <&uart1_pins_b>;

uart1_port = <1>;

uart1_type = <4>;

status = "disabled";

};

uart2: uart@2500800 {

compatible = "allwinner,sun55i-uart";

reg = <0x0 0x2500800 0x0 0x400>;

interrupts = <GIC_SPI 4 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_UART2>;

resets = <&ccu RST_BUS_UART2>;

uart2_port = <2>;

uart2_type = <4>;

sunxi,uart-fifosize = <128>;

status = "disabled";

};

uart3: uart@2500c00 {

compatible = "allwinner,sun55i-uart";

reg = <0x0 0x2500c00 0x0 0x400>;

interrupts = <GIC_SPI 5 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_UART3>;

resets = <&ccu RST_BUS_UART3>;

uart3_port = <3>;

uart3_type = <4>;

sunxi,uart-fifosize = <128>;

status = "disabled";

};

uart4: uart@2501000 {

compatible = "allwinner,sun55i-uart";

reg = <0x0 0x2501000 0x0 0x400>;

interrupts = <GIC_SPI 6 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_UART4>;

resets = <&ccu RST_BUS_UART4>;

uart4_port = <4>;

uart4_type = <4>;

sunxi,uart-fifosize = <128>;

status = "disabled";

};

uart5: uart@2501400 {

compatible = "allwinner,sun55i-uart";

reg = <0x0 0x2501400 0x0 0x400>;

interrupts = <GIC_SPI 7 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_UART5>;

resets = <&ccu RST_BUS_UART5>;

uart5_port = <5>;

uart5_type = <4>;

sunxi,uart-fifosize = <128>;

status = "disabled";

};

uart6: uart@2501800 {

compatible = "allwinner,sun55i-uart";

reg = <0x0 0x2501800 0x0 0x400>;

interrupts = <GIC_SPI 8 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_UART6>;

resets = <&ccu RST_BUS_UART6>;

uart6_port = <6>;

uart6_type = <4>;

sunxi,uart-fifosize = <128>;

status = "disabled";

};

uart7: uart@2501c00 {

compatible = "allwinner,sun55i-uart";

reg = <0x0 0x2501c00 0x0 0x400>;

interrupts = <GIC_SPI 9 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_UART7>;

resets = <&ccu RST_BUS_UART7>;

uart7_port = <7>;

uart7_type = <4>;

sunxi,uart-fifosize = <128>;

status = "disabled";

};

uart8: uart@7080000 {

compatible = "allwinner,sun55i-uart";

reg = <0x0 0x7080000 0x0 0x400>;

interrupts = <GIC_SPI 162 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&r_ccu CLK_BUS_R_UART0>;

resets = <&r_ccu RST_R_UART0>;

uart8_port = <8>;

uart8_type = <2>;

sunxi,uart-fifosize = <64>;

status = "disabled";

};

uart9: uart@7080400 {

compatible = "allwinner,sun55i-uart";

reg = <0x0 0x7080400 0x0 0x400>;

interrupts = <GIC_SPI 163 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&r_ccu CLK_BUS_R_UART1>;

resets = <&r_ccu RST_R_UART1>;

uart9_port = <9>;

uart9_type = <2>;

sunxi,uart-fifosize = <64>;

status = "disabled";

};

dma:dma-controller@3002000 {

compatible = "allwinner,dma-v105";

reg = <0x0 0x03002000 0x0 0x1000>;

interrupts = <GIC_SPI 50 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_DMA>, <&ccu CLK_DMA_MBUS_GATE>;

clock-names = "bus", "mbus";

dma-channels = <8>;

dma-requests = <54>;

resets = <&ccu RST_BUS_DMA>;

#dma-cells = <1>;

status = "okay";

};

dma1:dma1-controller@7121000 {

compatible = "allwinner,dma-v104";

reg = <0x0 0x7121000 0x0 0x1000>;

interrupts = <GIC_SPI 197 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&mcu_ccu CLK_BUS_MCU_DMA>, <&mcu_ccu CLK_BUS_MCU_DMA_MBUS>, <&mcu_ccu CLK_BUS_MCU_MBUS>;

clock-names = "bus", "mbus", "mcu-mbus";

dma-channels = <8>;

dma-requests = <15>;

resets = <&mcu_ccu RST_BUS_MCU_DMA>;

#dma-cells = <1>;

status = "okay";

};

npu: npu@7122000 {

compatible = "allwinner,npu";

reg = <0x0 0x07122000 0x0 0x1000>;

device_type = "npu";

dev_name = "npu";

interrupts = <GIC_SPI 199 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_NPU>, <&ccu CLK_PLL_NPU_2X>, <&mcu_ccu CLK_BUS_MCU_NPU_ACLK>, <&mcu_ccu CLK_BUS_MCU_NPU_HCLK>;

clock-names = "clk_npu", "clk_parent", "npu-aclk", "npu-hclk";

operating-points-v2 = <&npu_opp_table>;

resets = <&mcu_ccu RST_BUS_MCU_NPU>;

interrupt-names = "npu";

npu-vf = <1>;

power-domains = <&pd A523_PD_NPU>;

status = "okay";

};

npu_opp_table: npu-opp-table {

compatible = "allwinner,sun55i-operating-points";

opp-shared;

npu_opp_table_546: opp-546 {

opp-hz = <546000000>;

opp-microvolt-vf1 = <920000>;

opp-microvolt-vf2 = <920000>;

opp-microvolt-vf21 = <920000>;

opp-microvolt-vf3 = <920000>;

opp-microvolt-vf31 = <920000>;

opp-microvolt-vf4 = <920000>;

opp-microvolt-vf5 = <920000>;

};

npu_opp_table_696: opp-696 {

opp-hz = <696000000>;

opp-microvolt-vf1 = <1050000>;

opp-microvolt-vf2 = <1050000>;

opp-microvolt-vf21 = <1050000>;

opp-microvolt-vf3 = <1000000>;

opp-microvolt-vf31 = <1000000>;

opp-microvolt-vf4 = <1000000>;

opp-microvolt-vf5 = <960000>;

};

};

wdt: watchdog@2050000 {

compatible = "allwinner,wdt-v103";

reg = <0x0 0x02050000 0x0 0x20>; /* In Timers Spec */

interrupts = <GIC_SPI 63 IRQ_TYPE_LEVEL_HIGH>; /* In GIC Spec */

};

gpadc0: gpadc0@2009000 {

compatible = "allwinner,sunxi-gpadc";

reg = <0x0 0x02009000 0x0 0x400>;

interrupts = <GIC_SPI 61 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_BUS_GPADC0>;

clock-names = "bus";

resets = <&ccu RST_BUS_GPADC0>;

status = "disabled";

};

gpadc1: gpadc1@2009c00 {

compatible = "allwinner,sunxi-gpadc";

reg = <0x0 0x02009c00 0x0 0x400>;

interrupts = <GIC_SPI 64 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_BUS_GPADC1>;

clock-names = "bus";

resets = <&ccu RST_BUS_GPADC1>;

status = "disabled";

};

dsp0_rproc: dsp0_rproc@0 {

compatible = "allwinner,hifi4-rproc";

clock-frequency = <600000000>;

clocks = <&ccu CLK_PLL_PERI0_2X>, <&mcu_ccu CLK_DSP_DSP>, <&ccu CLK_DSP>, <&mcu_ccu CLK_BUS_DSP_CFG>, <&r_ccu CLK_R_AHB>;

clock-names = "pll", "mcu-mod", "mod", "cfg", "ahbs";

resets = <&mcu_ccu RST_BUS_DSP>, <&mcu_ccu RST_BUS_DSP_CFG>, <&mcu_ccu RST_BUS_DSP_DBG>;

reset-names = "mod-rst", "cfg-rst", "dbg-rst";

reg = <0x0 0x07010364 0x0 0x04>,

<0x0 0x07100000 0x0 0x40>;

reg-names = "sram-for-cpux", "hifi4-cfg";

firmware-name = "amp_dsp0.bin";

power-domains = <&pd A523_PD_DSP>, <&pd A523_PD_SRAM>;

power-domain-names = "pd_dsp", "pd_sram";

status = "disabled";

};

e906_rproc: e906_rproc@7130000 {

compatible = "allwinner,e906-rproc";

clocks = <&mcu_ccu CLK_BUS_PUBSRAM>, <&mcu_ccu CLK_BUS_RV>, <&mcu_ccu CLK_BUS_RV_CFG>;

clock-names = "pubsram", "mod", "cfg";

resets = <&mcu_ccu RST_BUS_PUBSRAM>, <&mcu_ccu RST_BUS_RV>, <&mcu_ccu RST_BUS_RV_CFG>, <&mcu_ccu RST_BUS_RV_DBG>;

reset-names = "pubsram-rst", "mod-rst", "cfg-rst", "dbg-rst";

firmware-name = "amp_rv0.bin";

reg = <0x0 0x07130000 0x0 0x1000>;

reg-names = "e906-cfg";

power-domains = <&pd A523_PD_RISCV>, <&pd A523_PD_SRAM>;

power-domain-names = "pd_riscv", "pd_sram";

status = "disabled";

};

msgbox: msgbox@3003000 {

compatible = "allwinner,sun55iw3-msgbox";

#mbox-cells = <1>;

reg = <0x0 0x03003000 0x0 0x1000>,

<0x0 0x07120000 0x0 0x1000>,

<0x0 0x07094000 0x0 0x1000>,

<0x0 0x07136000 0x0 0x1000>;

interrupts = <GIC_SPI 0 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 1 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 181 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 174 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_MSGBOX0>;

clock-names = "msgbox";

resets = <&ccu RST_BUS_MSGBOX0>;

reset-names = "rst";

local_id = <0>;

};

hwspinlock: hwspinlock@3005000 {

compatible = "allwinner,sunxi-hwspinlock";

reg = <0x0 0x3005000 0x0 0x1000>;

#hwlock-cells = <1>;

clocks = <&ccu CLK_SPINLOCK>;

clock-names = "clk_hwspinlock_bus";

resets = <&ccu RST_BUS_SPINLOCK>;

reset-names = "rst";

num-locks = <32>;

status = "okay";

};

pwm0: pwm0@2000c00 {

#pwm-cells = <0x3>;

compatible = "allwinner,sunxi-pwm-v201";

reg = <0x0 0x02000c00 0x0 0x400>;

clocks = <&ccu CLK_PWM>;

interrupts = <GIC_SPI 19 IRQ_TYPE_LEVEL_HIGH>;

resets = <&ccu RST_BUS_PWM>;

pwm-number = <16>;

pwm-base = <0x0>;

sunxi-pwms = <&pwm0_0>, <&pwm0_1>, <&pwm0_2>, <&pwm0_3>, <&pwm0_4>,

<&pwm0_5>, <&pwm0_6>, <&pwm0_7>, <&pwm0_8>, <&pwm0_9>,

<&pwm0_10>, <&pwm0_11>, <&pwm0_12>, <&pwm0_13>,

<&pwm0_14>, <&pwm0_15>;

status = "okay";

};

pwm0_0: pwm0_0@2000c10 {

compatible = "allwinner,sunxi-pwm0";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02000c10 0x0 0x4>;

reg_base = <0x02000c00>;

status = "disabled";

};

pwm0_1: pwm0_1@2000c11 {

compatible = "allwinner,sunxi-pwm1";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02000c11 0x0 0x4>;

reg_base = <0x02000c00>;

status = "disabled";

};

pwm0_2: pwm0_2@2000c12 {

compatible = "allwinner,sunxi-pwm2";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02000c12 0x0 0x4>;

reg_base = <0x02000c00>;

status = "disabled";

};

pwm0_3: pwm0_3@2000c13 {

compatible = "allwinner,sunxi-pwm3";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02000c13 0x0 0x4>;

reg_base = <0x02000c00>;

status = "disabled";

};

pwm0_4: pwm0_4@2000c14 {

compatible = "allwinner,sunxi-pwm4";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02000c14 0x0 0x4>;

reg_base = <0x02000c00>;

status = "disabled";

};

pwm0_5: pwm0_5@2000c15 {

compatible = "allwinner,sunxi-pwm5";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02000c15 0x0 0x4>;

reg_base = <0x02000c00>;

status = "disabled";

};

pwm0_6: pwm0_6@2000c16 {

compatible = "allwinner,sunxi-pwm6";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02000c16 0x0 0x4>;

reg_base = <0x02000c00>;

status = "disabled";

};

pwm0_7: pwm0_7@2000c17 {

compatible = "allwinner,sunxi-pwm7";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02000c17 0x0 0x4>;

reg_base = <0x02000c00>;

status = "disabled";

};

pwm0_8: pwm0_8@2000c18 {

compatible = "allwinner,sunxi-pwm8";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02000c18 0x0 0x4>;

reg_base = <0x02000c00>;

status = "disabled";

};

pwm0_9: pwm0_9@2000c19 {

compatible = "allwinner,sunxi-pwm9";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02000c19 0x0 0x4>;

reg_base = <0x02000c00>;

status = "disabled";

};

pwm0_10: pwm0_10@2000c1a {

compatible = "allwinner,sunxi-pwm10";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02000c1a 0x0 0x4>;

reg_base = <0x02000c00>;

status = "disabled";

};

pwm0_11: pwm0_11@2000c1b {

compatible = "allwinner,sunxi-pwm11";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02000c1b 0x0 0x4>;

reg_base = <0x02000c00>;

status = "disabled";

};

pwm0_12: pwm0_12@2000c1c {

compatible = "allwinner,sunxi-pwm12";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02000c1c 0x0 0x4>;

reg_base = <0x02000c00>;

status = "disabled";

};

pwm0_13: pwm0_13@2000c1d {

compatible = "allwinner,sunxi-pwm13";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02000c1d 0x0 0x4>;

reg_base = <0x02000c00>;

status = "disabled";

};

pwm0_14: pwm0_14@2000c1e {

compatible = "allwinner,sunxi-pwm14";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02000c1e 0x0 0x4>;

reg_base = <0x02000c00>;

status = "disabled";

};

pwm0_15: pwm0_15@2000c1f {

compatible = "allwinner,sunxi-pwm15";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02000c1f 0x0 0x4>;

reg_base = <0x02000c00>;

status = "disabled";

};

pwm1: pwm1@2051000 {

#pwm-cells = <0x3>;

compatible = "allwinner,sunxi-pwm-v201";

reg = <0x0 0x02051000 0x0 0x400>;

clocks = <&ccu CLK_PWM1>;

interrupts = <GIC_SPI 142 IRQ_TYPE_LEVEL_HIGH>;

resets = <&ccu RST_BUS_PWM1>;

pwm-number = <4>;

pwm-base = <0x10>;

sunxi-pwms = <&pwm1_0>, <&pwm1_1>, <&pwm1_2>, <&pwm1_3>;

status = "disabled";

};

pwm1_0: pwm1_0@2051010 {

compatible = "allwinner,sunxi-pwm16";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02051010 0x0 0x4>;

reg_base = <0x02051000>;

status = "disabled";

};

pwm1_1: pwm1_1@2051011 {

compatible = "allwinner,sunxi-pwm17";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02051011 0x0 0x4>;

reg_base = <0x02051000>;

status = "disabled";

};

pwm1_2: pwm1_2@2051012 {

compatible = "allwinner,sunxi-pwm18";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02051012 0x0 0x4>;

reg_base = <0x02051000>;

status = "disabled";

};

pwm1_3: pwm1_3@2051013 {

compatible = "allwinner,sunxi-pwm19";

pinctrl-names = "active", "sleep";

reg = <0x0 0x02051013 0x0 0x4>;

reg_base = <0x02051000>;

status = "disabled";

};

s_pwm0: s_pwm0@7020c00 {

#pwm-cells = <0x3>;

compatible = "allwinner,sunxi-pwm-v202";

reg = <0x0 0x07020c00 0x0 0x400>;

clocks = <&r_ccu CLK_R_PWM>,<&r_ccu CLK_BUS_R_PWM>;

interrupts = <GIC_SPI 168 IRQ_TYPE_LEVEL_HIGH>;

clock-names = "clk_pwm","clk_bus_pwm";

resets = <&r_ccu RST_R_PWM>;

pwm-number = <2>;

pwm-base = <0x14>;

sunxi-pwms = <&s_pwm0_0>, <&s_pwm0_1>;

status = "disabled";

};

s_pwm0_0: s_pwm0_0@7020c10 {

compatible = "allwinner,sunxi-pwm20";

pinctrl-names = "active", "sleep";

reg = <0x0 0x07020c10 0x0 0x4>;

reg_base = <0x07020c00>;

status = "disabled";

};

s_pwm0_1: s_pwm0_1@7020c11 {

compatible = "allwinner,sunxi-pwm21";

pinctrl-names = "active", "sleep";

reg = <0x0 0x07020c11 0x0 0x4>;

reg_base = <0x07020c00>;

status = "disabled";

};

mcu_pwm0: mcu_pwm0@7103000 {

#pwm-cells = <0x3>;

compatible = "allwinner,sunxi-pwm-v202";

reg = <0x0 0x07103000 0x0 0x400>;

clocks = <&mcu_ccu CLK_MCU_PWM>,<&mcu_ccu CLK_BUS_MCU_PWM>;

interrupts = <GIC_SPI 207 IRQ_TYPE_LEVEL_HIGH>;

clock-names = "clk_pwm","clk_bus_pwm";

resets = <&mcu_ccu RST_BUS_MCU_PWM>;

pwm-number = <8>;

pwm-base = <0x16>;

sunxi-pwms = <&mcu_pwm0_0>, <&mcu_pwm0_1>, <&mcu_pwm0_2>, <&mcu_pwm0_3>,

<&mcu_pwm0_4>,<&mcu_pwm0_5>, <&mcu_pwm0_6>, <&mcu_pwm0_7>;

status = "disabled";

};

mcu_pwm0_0: mcu_pwm0_0@7103010 {

compatible = "allwinner,sunxi-pwm22";

pinctrl-names = "active", "sleep";

reg = <0x0 0x07103010 0x0 0x4>;

reg_base = <0x07103000>;

status = "disabled";

};

mcu_pwm0_1: mcu_pwm0_1@7103020 {

compatible = "allwinner,sunxi-pwm23";

pinctrl-names = "active", "sleep";

reg = <0x0 0x07103020 0x0 0x4>;

reg_base = <0x07103000>;

status = "disabled";

};

mcu_pwm0_2: mcu_pwm0_2@7103030 {

compatible = "allwinner,sunxi-pwm24";

pinctrl-names = "active", "sleep";

reg = <0x0 0x07103030 0x0 0x4>;

reg_base = <0x07103000>;

status = "disabled";

};

mcu_pwm0_3: mcu_pwm0_3@7103040 {

compatible = "allwinner,sunxi-pwm25";

pinctrl-names = "active", "sleep";

reg = <0x0 0x07103040 0x0 0x4>;

reg_base = <0x07103000>;

status = "disabled";

};

mcu_pwm0_4: mcu_pwm0_4@7103050 {

compatible = "allwinner,sunxi-pwm26";

pinctrl-names = "active", "sleep";

reg = <0x0 0x07103050 0x0 0x4>;

reg_base = <0x07103000>;

status = "disabled";

};

mcu_pwm0_5: mcu_pwm0_5@7103060 {

compatible = "allwinner,sunxi-pwm27";

pinctrl-names = "active", "sleep";

reg = <0x0 0x07103060 0x0 0x4>;

reg_base = <0x07103000>;

status = "disabled";

};

mcu_pwm0_6: mcu_pwm0_6@7103070 {

compatible = "allwinner,sunxi-pwm28";

pinctrl-names = "active", "sleep";

reg = <0x0 0x07103070 0x0 0x4>;

reg_base = <0x07103000>;

status = "disabled";

};

mcu_pwm0_7: mcu_pwm0_7@7103080 {

compatible = "allwinner,sunxi-pwm29";

pinctrl-names = "active", "sleep";

reg = <0x0 0x07103080 0x0 0x4>;

reg_base = <0x07103000>;

status = "disabled";

};

ledc: ledc@2008000 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "allwinner,sunxi-leds";

reg = <0x0 0x02008000 0x0 0x400>;

interrupts = <GIC_SPI 28 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_LEDC>, <&ccu CLK_BUS_LEDC>;

clock-names = "clk_ledc", "clk_cpuapb";

resets = <&ccu RST_BUS_LEDC>;

reset-names = "ledc_reset";

dmas = <&dma 42>, <&dma 42>;

dma-names = "rx", "tx";

status = "disabled";

};

irrx: irrx@2005000 {

compatible = "allwinner,irrx";

reg = <0x0 0x02005000 0x0 0x400>;

interrupts = <GIC_SPI 27 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_BUS_IRRX>, <&dcxo24M>, <&ccu CLK_IRRX>;

clock-names = "bus", "pclk", "mclk";

resets = <&ccu RST_BUS_IRRX>;

status = "disabled";

};

s_irrx: s_irrx@7040000 {

compatible = "allwinner,irrx";

reg = <0x0 0x07040000 0x0 0x400>;

interrupts = <GIC_SPI 167 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&r_ccu CLK_BUS_R_IRRX>, <&dcxo24M>, <&r_ccu CLK_R_IRRX>;

clock-names = "bus", "pclk", "mclk";

resets = <&r_ccu RST_R_IRRX>;

status = "disabled";

};

irtx: irtx@2003000 {

compatible = "allwinner,irtx";

reg = <0x0 0x02003000 0x0 0x400>;

interrupts = <GIC_SPI 26 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_BUS_IRTX>, <&dcxo24M>, <&ccu CLK_IRTX>;

clock-names = "bus", "pclk", "mclk";

resets = <&ccu RST_BUS_IRTX>;

status = "disabled";

};

twi0: twi0@2502000 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "allwinner,sunxi-twi-v101";

device_type = "twi0";

reg = <0x0 0x02502000 0x0 0x400>;

interrupts = <GIC_SPI 10 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_TWI0>;

clock-names = "bus";

resets = <&ccu RST_BUS_TWI0>;

dmas = <&dma 43>, <&dma 43>;

dma-names = "tx", "rx";

status = "okay";

};

twi1: twi1@2502400 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "allwinner,sunxi-twi-v101";

device_type = "twi1";

reg = <0x0 0x02502400 0x0 0x400>;

interrupts = <GIC_SPI 11 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_TWI1>;

clock-names = "bus";

resets = <&ccu RST_BUS_TWI1>;

dmas = <&dma 44>, <&dma 44>;

dma-names = "tx", "rx";

status = "disabled";

};

twi2: twi2@2502800 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "allwinner,sunxi-twi-v101";

device_type = "twi2";

reg = <0x0 0x02502800 0x0 0x400>;

interrupts = <GIC_SPI 12 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_TWI2>;

clock-names = "bus";

resets = <&ccu RST_BUS_TWI2>;

dmas = <&dma 45>, <&dma 45>;

dma-names = "tx", "rx";

status = "disabled";

};

twi3: twi3@2502c00 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "allwinner,sunxi-twi-v101";

device_type = "twi3";

reg = <0x0 0x02502c00 0x0 0x400>;

interrupts = <GIC_SPI 13 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_TWI3>;

clock-names = "bus";

resets = <&ccu RST_BUS_TWI3>;

dmas = <&dma 46>, <&dma 46>;

dma-names = "tx", "rx";

status = "disabled";

};

twi4: twi4@2503000 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "allwinner,sunxi-twi-v101";

device_type = "twi4";

reg = <0x0 0x02503000 0x0 0x400>;

interrupts = <GIC_SPI 14 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_TWI4>;

clock-names = "bus";

resets = <&ccu RST_BUS_TWI4>;

dmas = <&dma 47>, <&dma 47>;

dma-names = "tx", "rx";

status = "disabled";

};

twi5: twi5@2503400{

#address-cells = <1>;

#size-cells = <0>;

compatible = "allwinner,sunxi-twi-v101";

device_type = "twi5";

reg = <0x0 0x02503400 0x0 0x400>;

interrupts = <GIC_SPI 15 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_TWI5>;

clock-names = "bus";

resets = <&ccu RST_BUS_TWI5>;

dmas = <&dma 48>, <&dma 48>;

dma-names = "tx", "rx";

status = "disabled";

};

twi6: s_twi0@7081400 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "allwinner,sunxi-twi-v101";

device_type = "twi6";

reg = <0x0 0x07081400 0x0 0x400>;

interrupts = <GIC_SPI 164 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&r_ccu CLK_BUS_R_TWI0>;

clock-names = "bus";

resets = <&r_ccu RST_R_TWI0>;

dmas = <&dma1 9>, <&dma1 9>;

dma-names = "tx", "rx";

status = "disabled";

};

twi7: s_twi1@7081800 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "allwinner,sunxi-twi-v101";

device_type = "twi7";

reg = <0x0 0x07081800 0x0 0x400>;