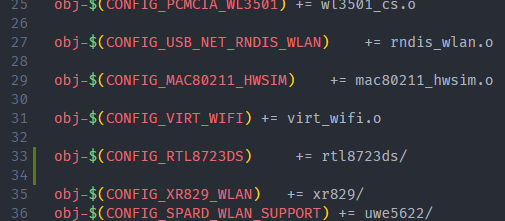

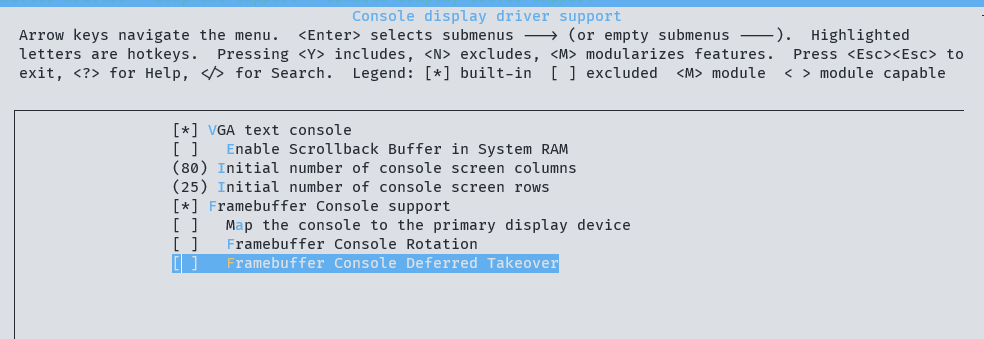

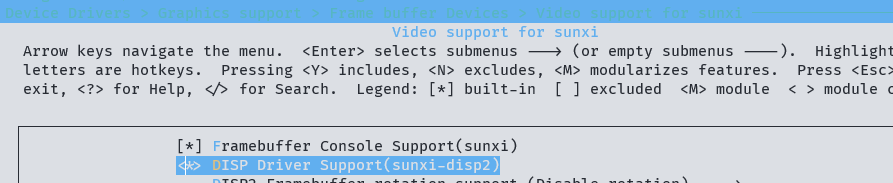

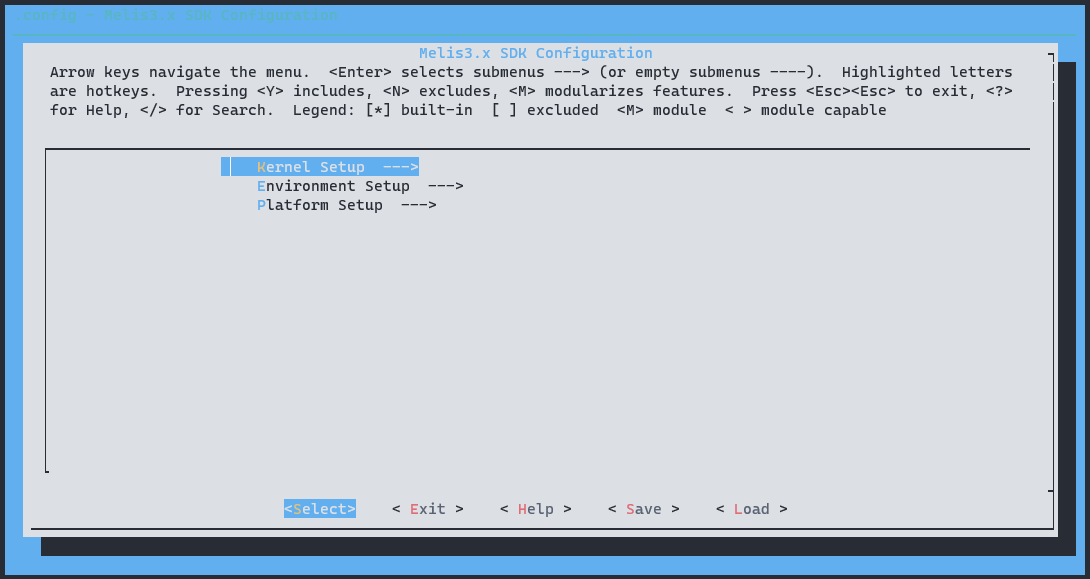

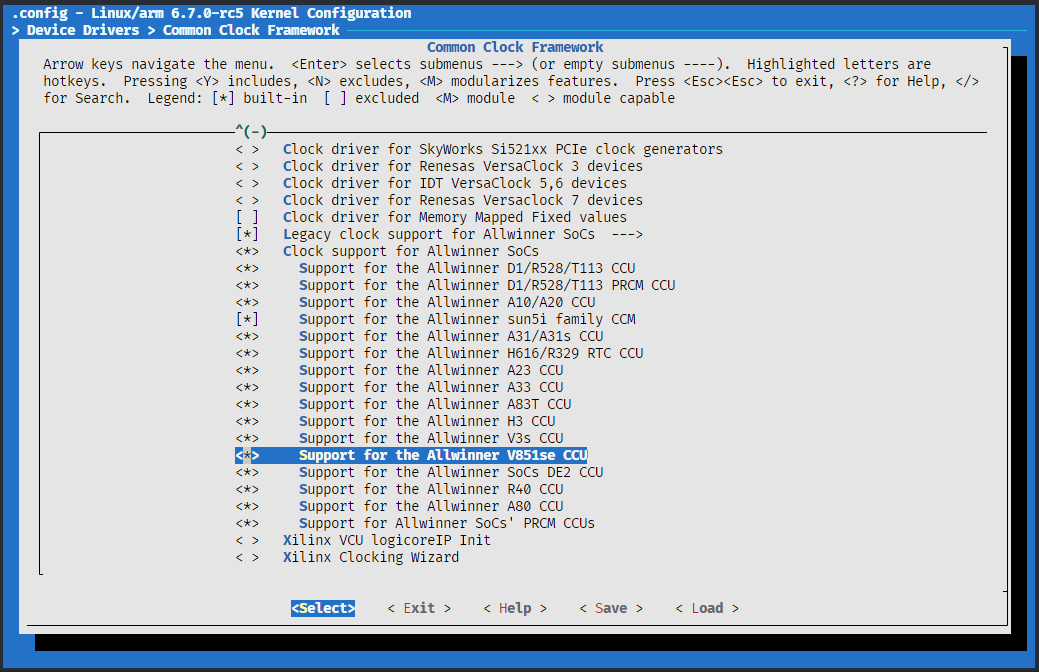

内核配置

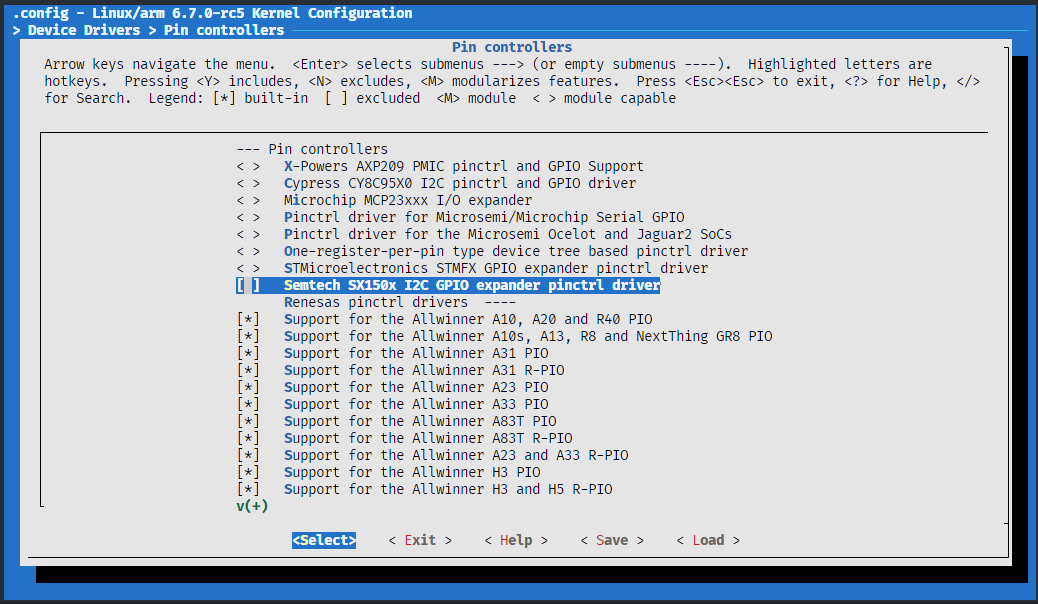

运行 m kernel_menuconfig 勾选下列驱动

Device Drivers --->

<*> Multimedia support --->

[*] V4L platform devices --->

<*> Video Multiplexer

[*] SUNXI platform devices --->

<*> sunxi video input (camera csi/mipi isp vipp)driver

<M> v4l2 new driver for SUNXI

<*> use cci function

select cci or cci to twi (chenge cci to twi) --->

[*] use IOMMU for memery alloc

[*] ISP WDR module

[*] sensor same i2c addr

sensor driver select --->

<M> use ov5640 driver

[*] Memory-to-memory multimedia devices --->

<*> Deinterlace support

<*> SuperH VEU mem2mem video processing driver

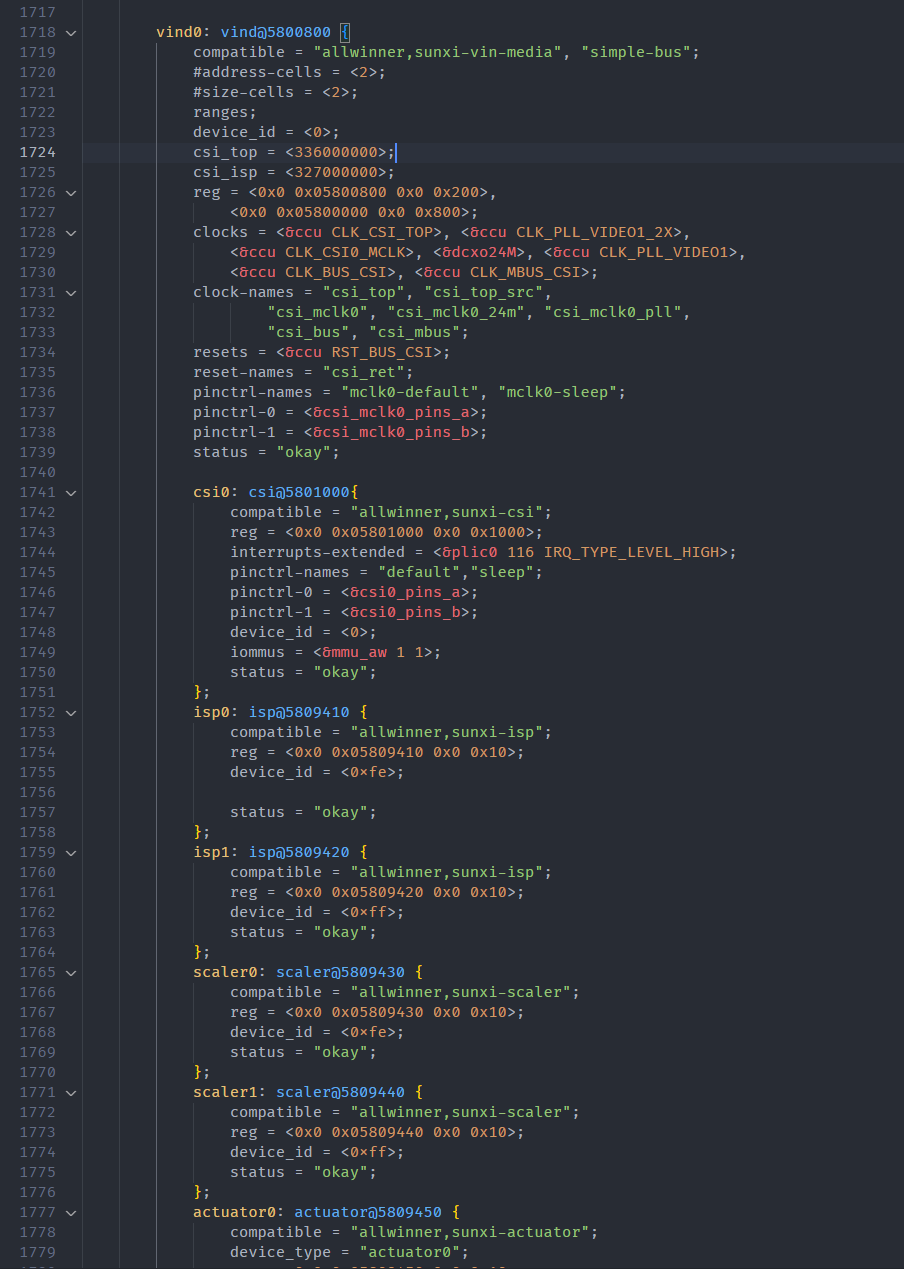

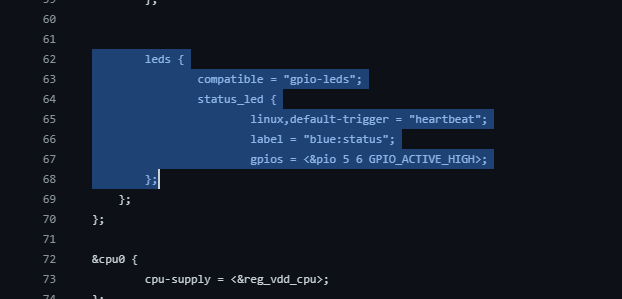

设备树配置

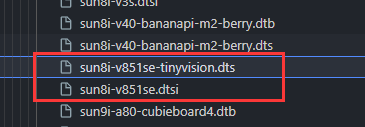

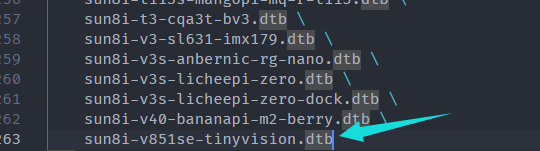

路径:lichee/linux-5.4/arch/riscv/boot/dts/sunxi/sun20iw1p1.dtsi

vind0: vind@5800800 {

compatible = "allwinner,sunxi-vin-media", "simple-bus";

#address-cells = <2>;

#size-cells = <2>;

ranges;

device_id = <0>;

csi_top = <336000000>;

csi_isp = <327000000>;

reg = <0x0 0x05800800 0x0 0x200>,

<0x0 0x05800000 0x0 0x800>;

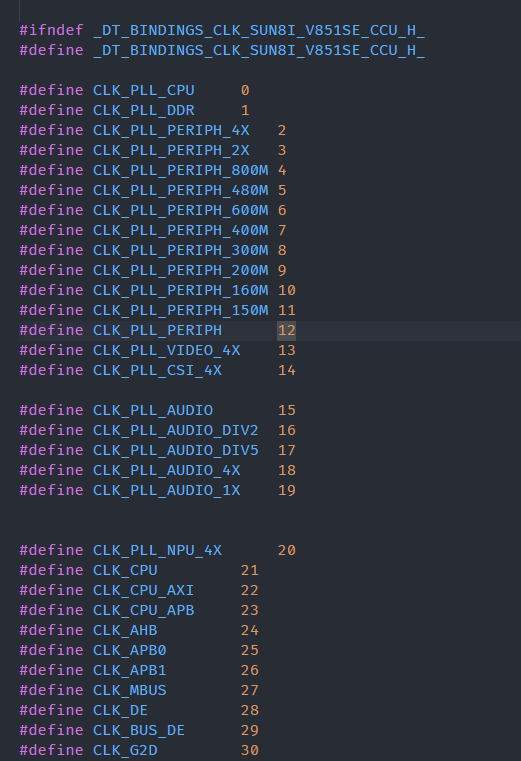

clocks = <&ccu CLK_CSI_TOP>, <&ccu CLK_PLL_VIDEO1_2X>,

<&ccu CLK_CSI0_MCLK>, <&dcxo24M>, <&ccu CLK_PLL_VIDEO1>,

<&ccu CLK_BUS_CSI>, <&ccu CLK_MBUS_CSI>;

clock-names = "csi_top", "csi_top_src",

"csi_mclk0", "csi_mclk0_24m", "csi_mclk0_pll",

"csi_bus", "csi_mbus";

resets = <&ccu RST_BUS_CSI>;

reset-names = "csi_ret";

pinctrl-names = "mclk0-default", "mclk0-sleep";

pinctrl-0 = <&csi_mclk0_pins_a>;

pinctrl-1 = <&csi_mclk0_pins_b>;

status = "okay";

csi0: csi@5801000{

compatible = "allwinner,sunxi-csi";

reg = <0x0 0x05801000 0x0 0x1000>;

interrupts-extended = <&plic0 116 IRQ_TYPE_LEVEL_HIGH>;

pinctrl-names = "default","sleep";

pinctrl-0 = <&csi0_pins_a>;

pinctrl-1 = <&csi0_pins_b>;

device_id = <0>;

iommus = <&mmu_aw 1 1>;

status = "okay";

};

isp0: isp@5809410 {

compatible = "allwinner,sunxi-isp";

reg = <0x0 0x05809410 0x0 0x10>;

device_id = <0xfe>;

status = "okay";

};

isp1: isp@5809420 {

compatible = "allwinner,sunxi-isp";

reg = <0x0 0x05809420 0x0 0x10>;

device_id = <0xff>;

status = "okay";

};

scaler0: scaler@5809430 {

compatible = "allwinner,sunxi-scaler";

reg = <0x0 0x05809430 0x0 0x10>;

device_id = <0xfe>;

status = "okay";

};

scaler1: scaler@5809440 {

compatible = "allwinner,sunxi-scaler";

reg = <0x0 0x05809440 0x0 0x10>;

device_id = <0xff>;

status = "okay";

};

actuator0: actuator@5809450 {

compatible = "allwinner,sunxi-actuator";

device_type = "actuator0";

reg = <0x0 0x05809450 0x0 0x10>;

actuator0_name = "ad5820_act";

actuator0_slave = <0x18>;

actuator0_af_pwdn = <>;

actuator0_afvdd = "afvcc-csi";

actuator0_afvdd_vol = <2800000>;

status = "okay";

};

flash0: flash@5809460 {

device_type = "flash0";

compatible = "allwinner,sunxi-flash";

reg = <0x0 0x05809460 0x0 0x10>;

flash0_type = <2>;

flash0_en = <>;

flash0_mode = <>;

flash0_flvdd = "";

flash0_flvdd_vol = <>;

device_id = <0>;

status = "okay";

};

sensor0: sensor@5809470 {

reg = <0x0 0x05809470 0x0 0x10>;

device_type = "sensor0";

compatible = "allwinner,sunxi-sensor";

sensor0_mname = "ov5640";

sensor0_twi_cci_id = <2>;

sensor0_twi_addr = <0x78>;

sensor0_mclk_id = <0>;

sensor0_pos = "rear";

sensor0_isp_used = <0>;

sensor0_fmt = <0>;

sensor0_stby_mode = <0>;

sensor0_vflip = <0>;

sensor0_hflip = <0>;

sensor0_iovdd-supply = <>;

sensor0_iovdd_vol = <>;

sensor0_avdd-supply = <>;

sensor0_avdd_vol = <>;

sensor0_dvdd-supply = <>;

sensor0_dvdd_vol = <>;

sensor0_power_en = <>;

sensor0_reset = <&pio PE 14 GPIO_ACTIVE_LOW>;

sensor0_pwdn = <&pio PE 15 GPIO_ACTIVE_LOW>;

sensor0_sm_vs = <>;

flash_handle = <&flash0>;

act_handle = <&actuator0>;

device_id = <0>;

status = "okay";

};

sensor1: sensor@5809480 {

reg = <0x0 0x05809480 0x0 0x10>;

device_type = "sensor1";

compatible = "allwinner,sunxi-sensor";

sensor1_mname = "ov5647";

sensor1_twi_cci_id = <3>;

sensor1_twi_addr = <0x6c>;

sensor1_mclk_id = <1>;

sensor1_pos = "front";

sensor1_isp_used = <0>;

sensor1_fmt = <0>;

sensor1_stby_mode = <0>;

sensor1_vflip = <0>;

sensor1_hflip = <0>;

sensor1_iovdd-supply = <>;

sensor1_iovdd_vol = <>;

sensor1_avdd-supply = <>;

sensor1_avdd_vol = <>;

sensor1_dvdd-supply = <>;

sensor1_dvdd_vol = <>;

sensor1_power_en = <>;

sensor1_reset = <&pio PE 7 GPIO_ACTIVE_LOW>;

sensor1_pwdn = <&pio PE 6 GPIO_ACTIVE_LOW>;

sensor1_sm_vs = <>;

flash_handle = <>;

act_handle = <>;

device_id = <1>;

status = "disabled";

};

vinc0: vinc@5809000 {

compatible = "allwinner,sunxi-vin-core";

device_type = "vinc0";

reg = <0x0 0x05809000 0x0 0x200>;

interrupts-extended = <&plic0 111 IRQ_TYPE_LEVEL_HIGH>;

vinc0_csi_sel = <0>;

vinc0_mipi_sel = <0xff>;

vinc0_isp_sel = <0>;

vinc0_tdm_rx_sel = <0xff>;

vinc0_rear_sensor_sel = <0>;

vinc0_front_sensor_sel = <0>;

vinc0_sensor_list = <0>;

device_id = <0>;

iommus = <&mmu_aw 1 1>;

status = "okay";

};

vinc1: vinc@5809200 {

device_type = "vinc1";

compatible = "allwinner,sunxi-vin-core";

reg = <0x0 0x05809200 0x0 0x200>;

interrupts-extended = <&plic0 112 IRQ_TYPE_LEVEL_HIGH>;

vinc1_csi_sel = <0>;

vinc1_mipi_sel = <0xff>;

vinc1_isp_sel = <1>;

vinc1_tdm_rx_sel = <0xff>;

vinc1_rear_sensor_sel = <0>;

vinc1_front_sensor_sel = <0>;

vinc1_sensor_list = <0>;

device_id = <1>;

iommus = <&mmu_aw 1 1>;

status = "disabled";

};

};

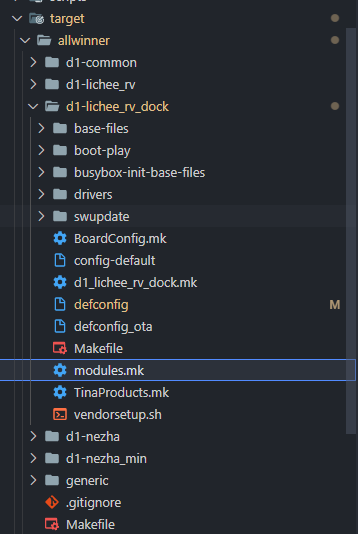

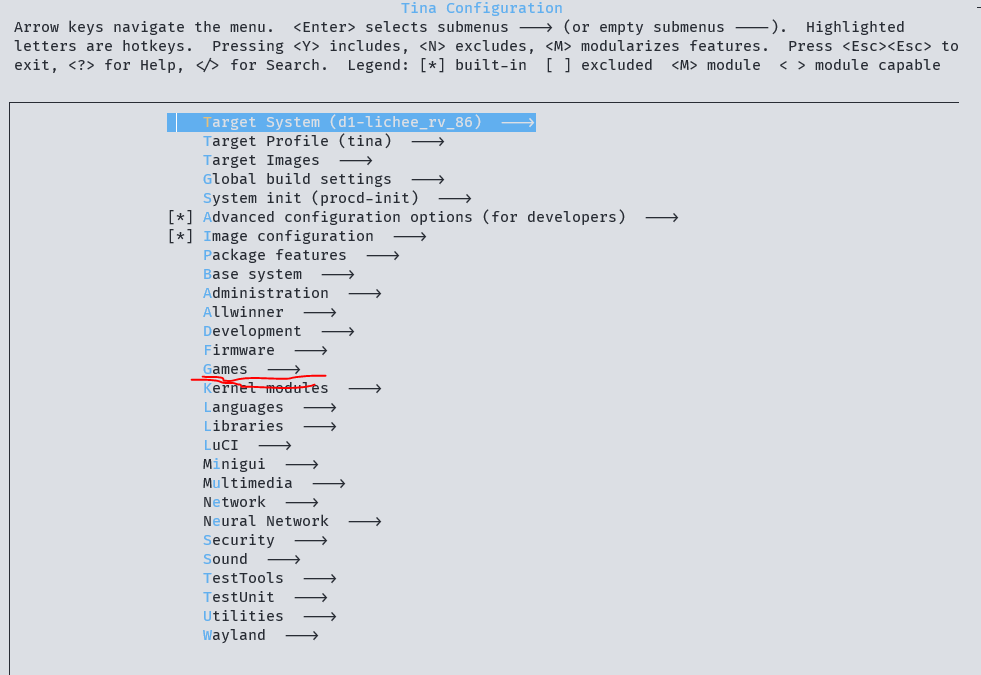

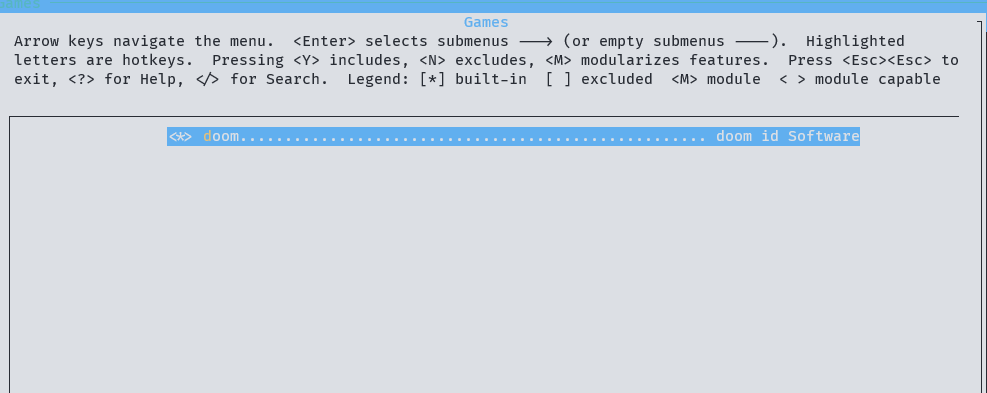

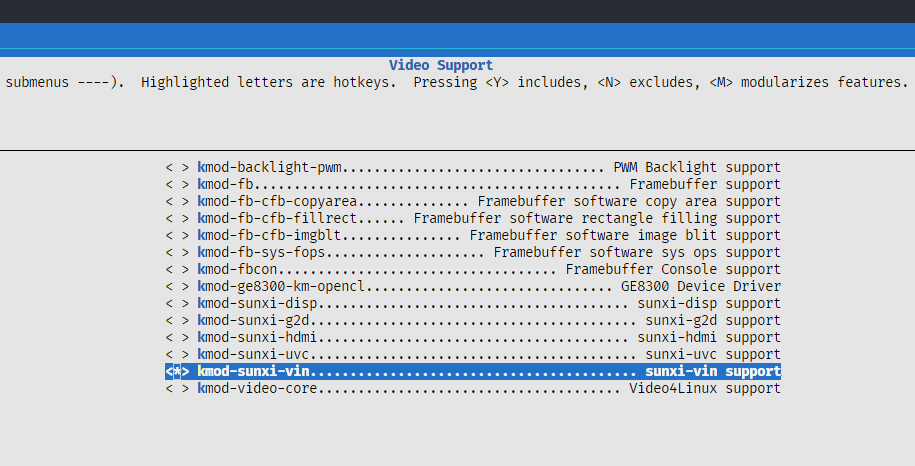

ROOTFS 配置

运行 m menuconfig,勾选 <*> kmod-sunxi-vin......................................... sunxi-vin support

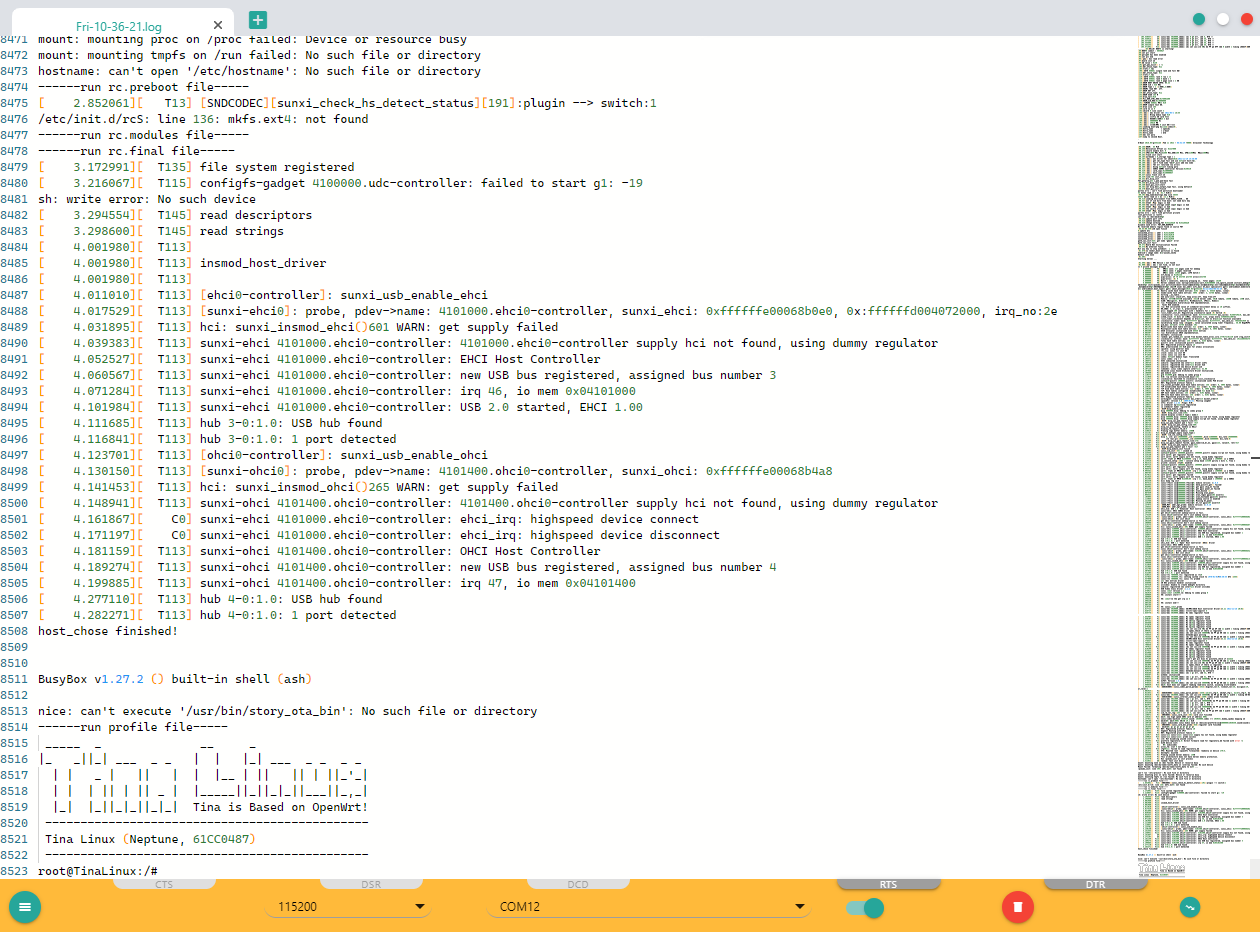

常见错误

[VIN_ERR]media_entity_find_link null

驱动版本不匹配所致,目前SDK分支过多驱动版本过多,用下列驱动替换即可:

sunxi-vin.tar.gz

解压,覆盖到 tina-d1-h/lichee/linux-5.4/drivers/media/platform/sunxi-vin 文件夹

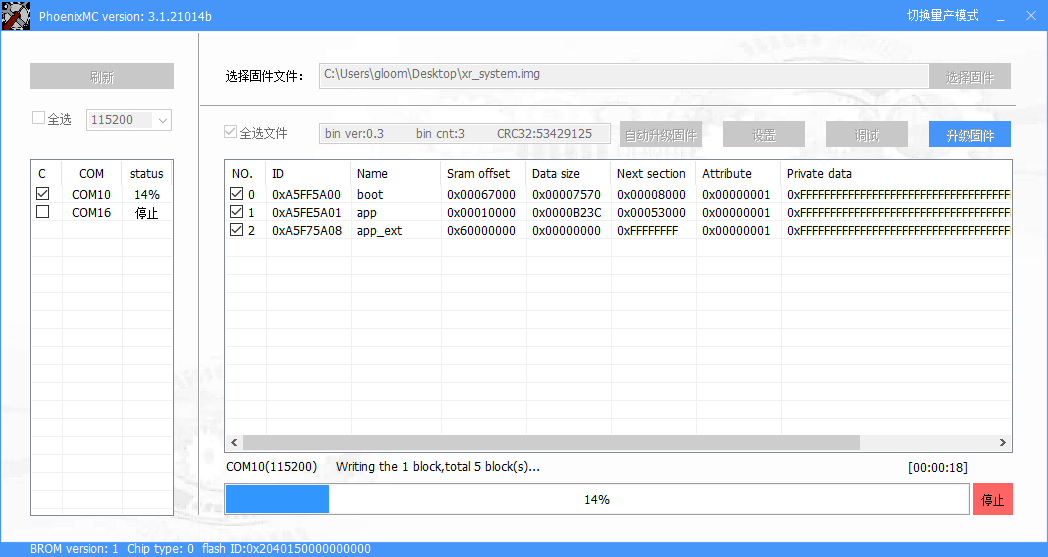

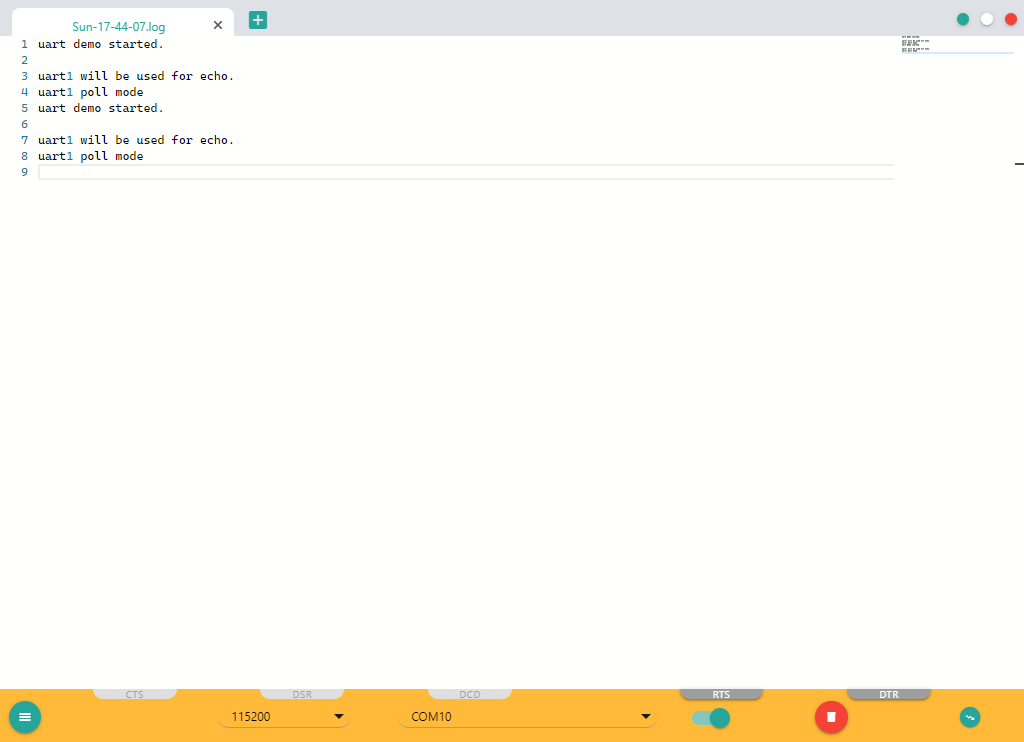

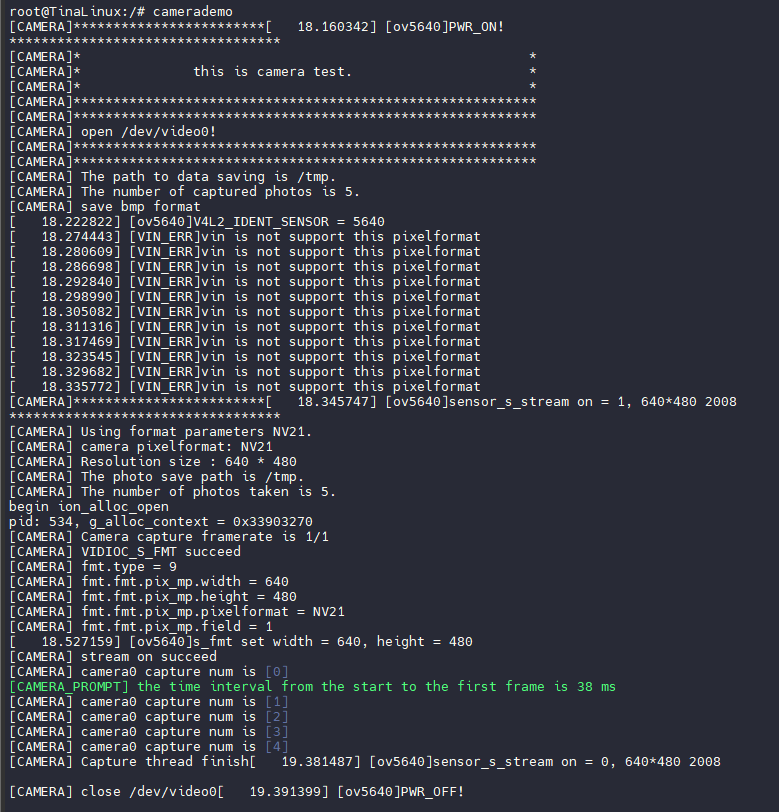

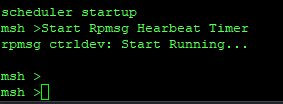

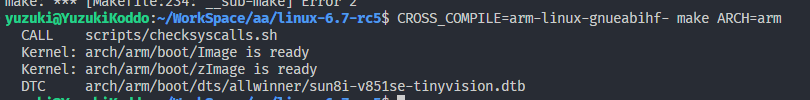

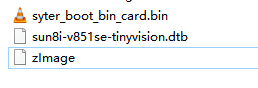

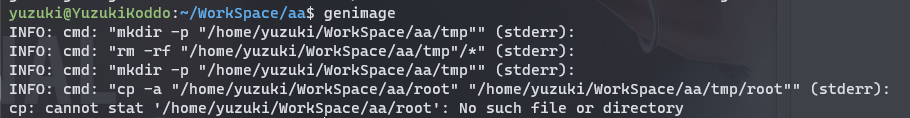

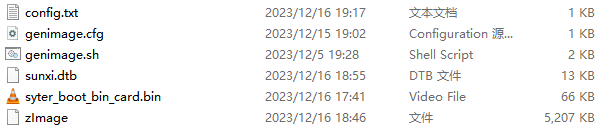

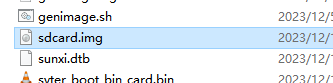

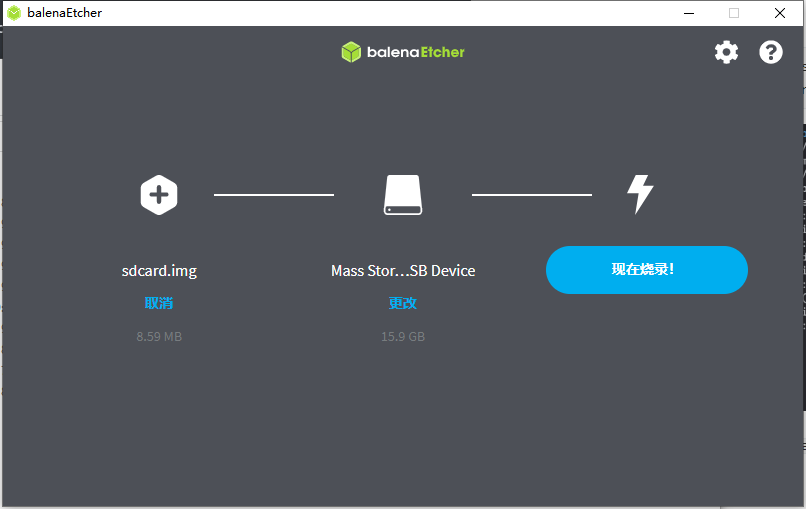

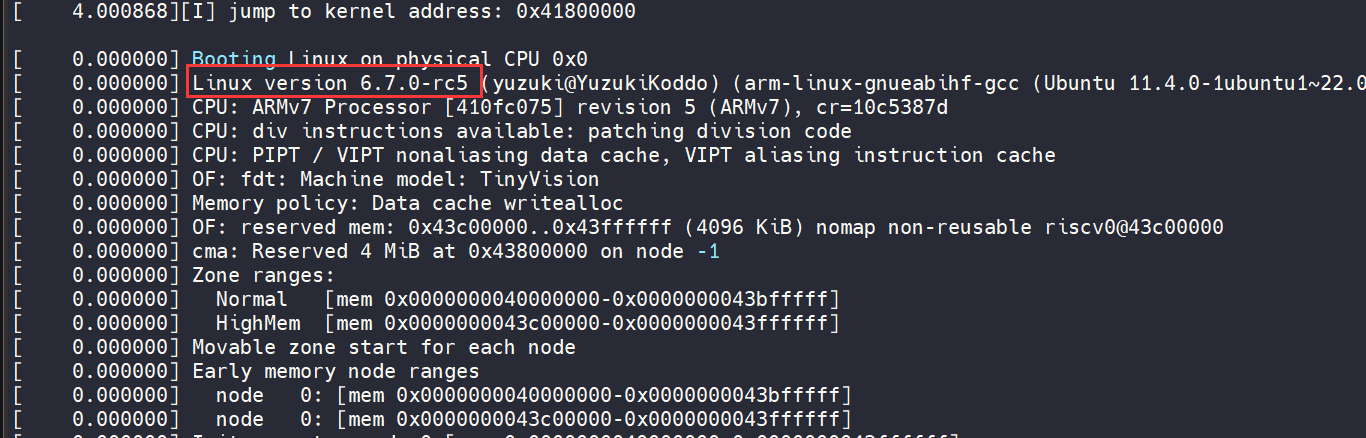

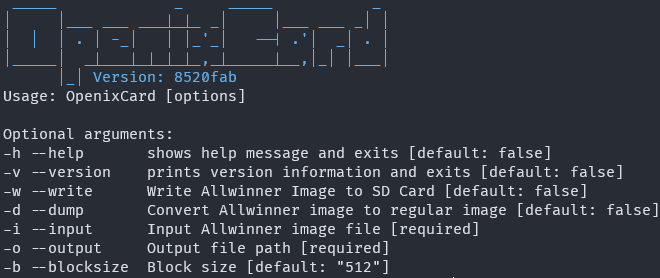

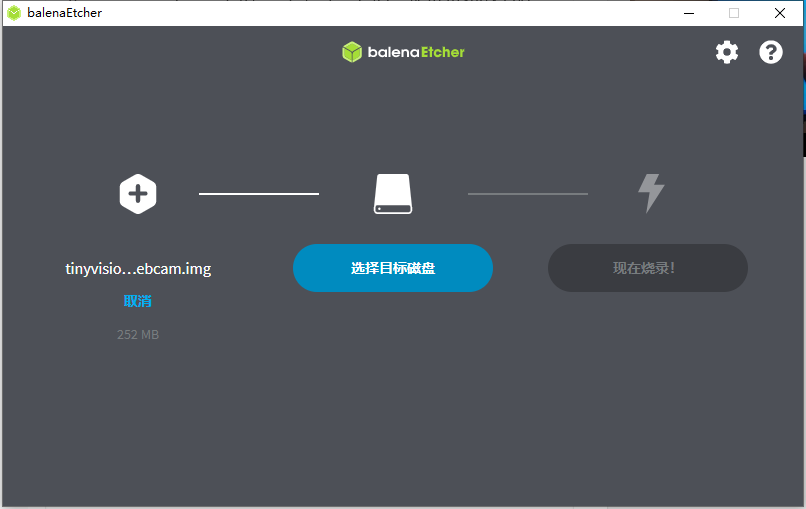

测试固件

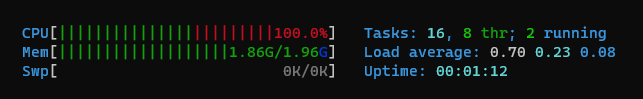

eim

eim