【T113-I】 请问该产品支持spi传输32bit数据吗

-

您好,尊敬的大佬们,由于我选用的spi外设是32bit传输的,所以应外设的需求,我根据T113的数据手册去设置BATC寄存器,还有更改了spi-sunxi.c中的 master->bits_per_word_mask = SPI_BPW_MASK(8) | SPI_BPW_MASK(32);

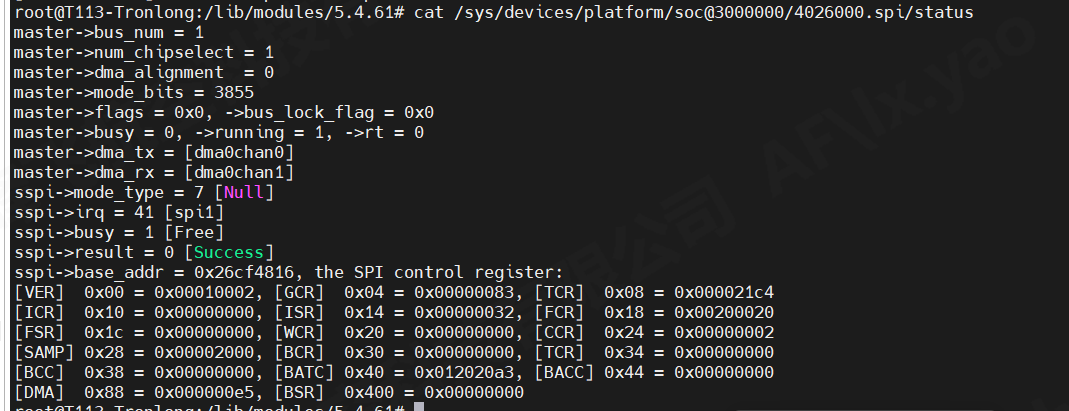

但是通过逻辑分析仪,甚至无法出现数据。以下是我通过截取spi寄存器的数值图:

所以我有以下三个疑问:

1:T113-i这款芯片 硬件上支持spi传输32bit吗?

2:若支持,请问我这样配置是否有误?

3:若不支持,请问我是否能够通过spi-gpio模拟出读写32bit的spi

非常希望得到大佬们的点拨

-

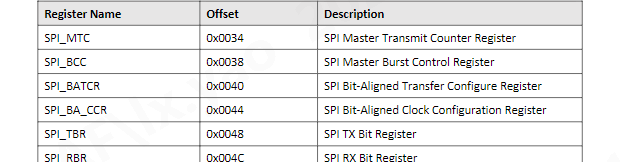

其次我看数据手册和spi-sunxi.h中 寄存器的地址定义不同,此外数据手册是否缺少了0x3c的寄存器定义

-

@wayneyao IP版本不同,驱动有修改,以手册为准,控制器支持32bit,请提供设备树和驱动修改

-

@awwwwa

以下是我的设备树修改:&spi1 { clock-frequency = <50000000>; // pinctrl-0 = <&spi1_pins_a &spi1_pins_b>; pinctrl-0 = <&spi1_pins_a>; pinctrl-1 = <&spi1_pins_c>; pinctrl-names = "default", "sleep"; spi_slave_mode = <0>; spi1_cs_number = <1>; spi1_cs_bitmap = <1>; status = "okay"; cs-gpios =<&pio PB 8 (GPIO_ACTIVE_LOW | GPIO_PULL_UP)>; ,<&pio PB 12 (GPIO_ACTIVE_LOW | GPIO_PULL_UP)>; /*nWKRQ RST nINT SCLK SDI SDO NCS PD4 PD5 PD6 PB11 PB10 PB9 PD10 PD7 PD8 PD9 PB11 PB10 PB9 PD11 */ tcan4551_0:tcan4551@0{ #address-cells=<1>; #size-cells=<1>; compatible = "ti,tcan4x5x"; reg = <0>; spi-max-frequency =<10000000>; bosch,mram-cfg = <0x0 0 0 32 0 0 1 1>; interrupt-parent = <&pio>; interrupts = <DP 6 IRQ_TYPE_LEVEL_HIGH>; device-wake-gpios = <&pio PD 4 GPIO_ACTIVE_HIGH>; reset-gpios = <&pio PD 5 GPIO_ACTIVE_LOW>; }; tcan4551_2:tcan4552@0{ #address-cells=<1>; #size-cells=<1>; compatible = "ti,tcan4x5x"; reg = <0>; spi-max-frequency =<10000000>; bosch,mram-cfg = <0x0 0 0 32 0 0 1 1>; interrupt-parent = <&pio>; interrupts = <PD 9 IRQ_TYPE_LEVEL_HIGH>; device-wake-gpios = <&pio PD 7 GPIO_ACTIVE_HIGH>; reset-gpios = <&pio PD 8 GPIO_ACTIVE_LOW>; }; }; spi1_pins_a: spi1@0 { pins = "PB11", "PB10", "PB9"; /*clk mosi miso hold wp*/ function = "spi1"; drive-strength = <10>; }; -

@awwwwa

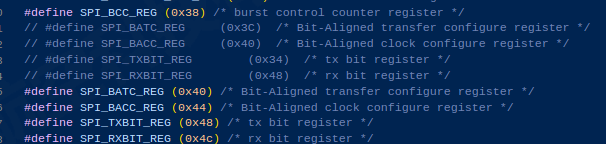

spi-sunxi.h spi-sunxi.c

以上是我稍作修改的spi-sunxi文件,

主要是做了以下三个地方的修改:

1:在.h文件当中将寄存器地址与t113的数据手册对齐:// #define SPI_BATC_REG (0x3C) /* Bit-Aligned transfer configure register */ // #define SPI_BACC_REG (0x40) /* Bit-Aligned clock configure register */ // #define SPI_TXBIT_REG (0x34) /* tx bit register */ // #define SPI_RXBIT_REG (0x48) /* rx bit register */ #define SPI_BATC_REG (0x40) /* Bit-Aligned transfer configure register */ #define SPI_BACC_REG (0x44) /* Bit-Aligned clock configure register */ #define SPI_TXBIT_REG (0x48) /* tx bit register */ #define SPI_RXBIT_REG (0x4c) /* rx bit register */ 2:在spi初始化阶段执行spi_config_batc(): static void spi_config_batc(u32 config, void __iomem *base_addr) { u32 reg_val = readl(base_addr + SPI_BATC_REG); // config &= ~SPI_BPW_MASK(8); // if (config) { reg_val |= 0x03; // reg_val |=(0x1 << 0); // reg_val |=(0x1 << 1); //设置成32位一帧 reg_val |= (32 << 8); reg_val |= (32 << 16); reg_val |= (0x1 << 24); // } writel(reg_val, base_addr + SPI_BATC_REG); }3:在3033行对bits_per_word_mask 增加32bit的位掩码

master->bits_per_word_mask = SPI_BPW_MASK(8) | SPI_BPW_MASK(32);

非常感谢您的回复,以上便是我的全部修改,请问还有什么需要我去调整的地方吗 -

@wayneyao 使用bit-aligin模式可以支持1~32bpw,但旧驱动没有完善这部分功能,需要对照手册自行添加下

-

@jingyan :

您好 ,我已按照数据手册修改了bit-aligned相关部分寄存器BATC的值 0x40=0x012020a3,但仍未生效32bit传输,不知是否还需要配置其他寄存器,修改的部分在上面已上传。

您好 ,我已按照数据手册修改了bit-aligned相关部分寄存器BATC的值 0x40=0x012020a3,但仍未生效32bit传输,不知是否还需要配置其他寄存器,修改的部分在上面已上传。 -

@wayneyao 还需要给0x40[bit31]置1发起传输,然后向0x48写入32bit数据,等待0x40[bit25]置1完成传输后,从0x4C读出32bit数据。

另外bit模式不支持全双工,若tx/rx同时配置,会先发再收 -

@jingyan

难度炸裂

难度炸裂 -

@jingyan 您好请问 不支持全双工,是指只能用3线制才能实现bit-aligin传输吗 还是说四线制spi也支持bit-aligin传输 只是无法同时读写

-

@wayneyao 是的,无法同时读写。bit模式支持3线或标准4线,具体见0x40[1:0]配置

-

@jingyan 好的 感谢您的回复

-

SPI 可以通过组包的方式 发送4次8bit 组成一次32bit

//线传输地址,再传输要传送的值 线传输低位,再传输高位addr = TCAN4X5X_WRITE_CMD | (*((u16 *)reg) << 8) | val_len >> 2; txaddr[0] = (addr >> 24) & 0xff; txaddr[1] = (addr >> 16) & 0xff; txaddr[2] = (addr >> 8) & 0xff; txaddr[3] = (addr >> 0) & 0xff; txval[0] = (*(u32 *)val >> 24) & 0xff; txval[1] = (*(u32 *)val >> 16) & 0xff; txval[2] = (*(u32 *)val >> 8) & 0xff; txval[3] = (*(u32 *)val >> 0) & 0xff; struct spi_transfer t[8] = { { .tx_buf = &txaddr[0], .len = 1, .cs_change = 0, }, { .tx_buf = &txaddr[1], .len = 1, .cs_change = 0, }, { .tx_buf = &txaddr[2], .len = 1, .cs_change = 0, }, { .tx_buf = &txaddr[3], .len = 1, .cs_change = 0, }, { .tx_buf = &txval[0], .len = 1, .cs_change = 0, }, { .tx_buf = &txval[1], .len = 1, .cs_change = 0, }, { .tx_buf = &txval[2], .len = 1, .cs_change = 0, }, { .tx_buf = &txval[3], .len = val_len, }, }; // printk("txbuf:%x %x %x %x %x\n", txaddr, txaddr[0], txaddr[1], // txaddr[2], txaddr[3]); // printk("txval:%x %x %x %x %x\n", *(u32 *)val, txval[0], txval[1], // txval[2], txval[3]); spi_message_init(&m); spi_message_add_tail(&t[0], &m); spi_message_add_tail(&t[1], &m); spi_message_add_tail(&t[2], &m); spi_message_add_tail(&t[3], &m); spi_message_add_tail(&t[4], &m); spi_message_add_tail(&t[5], &m); spi_message_add_tail(&t[6], &m); spi_message_add_tail(&t[7], &m); -

@wayneyao 也是一种方法,但限制是bit要8的倍数才行

-

Moved from 其它全志芯片讨论区 by

xiaowenge

xiaowenge

Copyright © 2024 深圳全志在线有限公司 粤ICP备2021084185号 粤公网安备44030502007680号