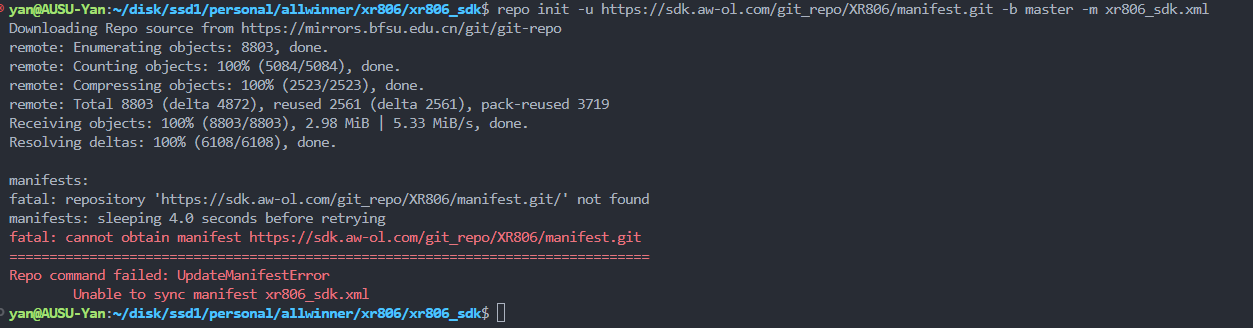

@q1215200171 XR806 SDK下载失败

J

Jingyan 发布的最佳帖子

-

回复: V851S I2C/TWI 损坏(xfer 错误)发布在 V Series

@kanken6174 不建议修改引脚驱动能力,因为i2c协议要求总线为弱上拉,提高IO驱动能力会使之变成强上拉

当VCC为1.8V时,上拉电阻应选用2K

当VCC为3.3V时,上拉电阻应选用4.7K若无法正常使用,应排查走线质量与信号干扰。

-

回复: Tina系统没有/etc/config/network文件发布在 其它全志芯片讨论区

@a06041114 这是rootfs的功能,跟menuconfig无关,如果缺少的话可以自己添加下,具体可以网上查查,很多资料

-

回复: V853的SPI能否实现从机模式下的DMA循环内存接收?发布在 V Series

@sssanton 可以,串链/单链是DMA的功能,与外设支持与否无关。但SPI驱动默认用的是单链这个模式,需要自行开发

Jingyan 发布的最新帖子

-

回复: V853的SPI能否实现从机模式下的DMA循环内存接收?发布在 V Series

@sssanton 可以,串链/单链是DMA的功能,与外设支持与否无关。但SPI驱动默认用的是单链这个模式,需要自行开发

-

回复: V853的SPI能否实现从机模式下的DMA循环内存接收?发布在 V Series

@sssanton 可以,使用环形缓冲区+dma cycle mode,注意dma需要配置成width=1,burst=1

目前该用例还没有开放,需要自行实现或在全志平台提单

-

回复: Tina Linux pack失败问题发布在 T Series

@huangliqun 参考下 pack 时 ERROR: unable to open file boot-resource.fex

sudo apt-get install lib32z1 lib32z1-dev