@wnlyd

单次解决可以用 ifconfig 命令修改MAC地址

永久修改需要看下IC是否有烧MAC码

Jingyan 发布的帖子

-

回复: V853的SPI能否实现从机模式下的DMA循环内存接收?发布在 V Series

@sssanton 可以,串链/单链是DMA的功能,与外设支持与否无关。但SPI驱动默认用的是单链这个模式,需要自行开发

-

回复: V853的SPI能否实现从机模式下的DMA循环内存接收?发布在 V Series

@sssanton 可以,使用环形缓冲区+dma cycle mode,注意dma需要配置成width=1,burst=1

目前该用例还没有开放,需要自行实现或在全志平台提单

-

回复: Tina Linux pack失败问题发布在 T Series

@huangliqun 参考下 pack 时 ERROR: unable to open file boot-resource.fex

sudo apt-get install lib32z1 lib32z1-dev -

回复: Tina系统没有/etc/config/network文件发布在 其它全志芯片讨论区

@a06041114 这是rootfs的功能,跟menuconfig无关,如果缺少的话可以自己添加下,具体可以网上查查,很多资料

-

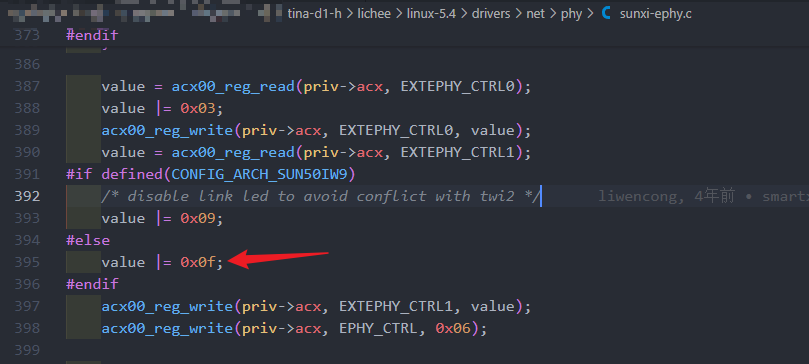

回复: T113-S3 eth0可以识别到但是无法PING通发布在 T Series

@miaoxiaoxiao 先确认下PHY是否有正常linkup

驱动排查手段,参考:https://open.allwinnertech.com/#/faq/0/show?menuID=17&faqId=55 -

回复: 怎么解决A133编译报错发布在 编译和烧写问题专区

@qw348313 在device/softwinner下搜下有没有sys_partition.fex文件。感觉是SDK包不完整,问代理商再拿一份吧

-

回复: 飞凌T113-i核心板+自制底板 mcp2515驱动失败发布在 飞凌嵌入式专区

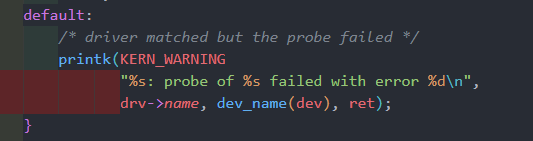

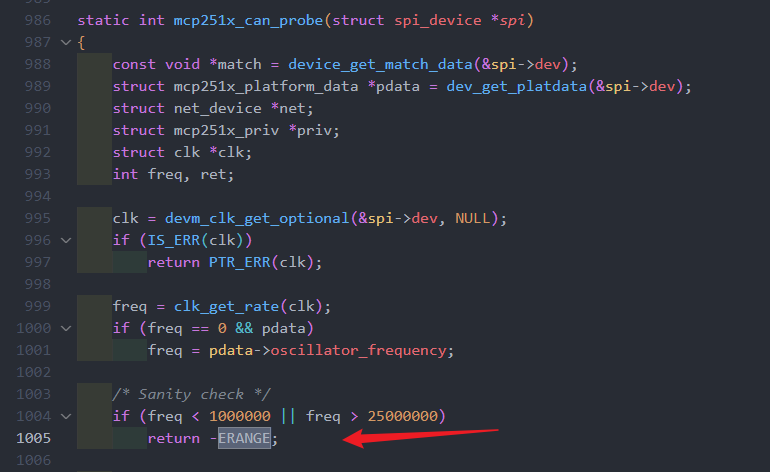

@ts_123456789 在 飞凌T113-i核心板+自制底板 mcp2515驱动失败 中说:

这个报错是mcp驱动返回的错误码,请检查时钟。要求范围在1M~25M之间 -

回复: 【T113-I】 请问该产品支持spi传输32bit数据吗发布在 T Series

@wayneyao 还需要给0x40[bit31]置1发起传输,然后向0x48写入32bit数据,等待0x40[bit25]置1完成传输后,从0x4C读出32bit数据。

另外bit模式不支持全双工,若tx/rx同时配置,会先发再收 -

回复: 【T113-I】 请问该产品支持spi传输32bit数据吗发布在 T Series

@wayneyao 使用bit-aligin模式可以支持1~32bpw,但旧驱动没有完善这部分功能,需要对照手册自行添加下

-

回复: T113s spi0 cs0 的疑难问题发布在 T Series

@ou13556101201 不是很清楚你想要达到怎样的效果。

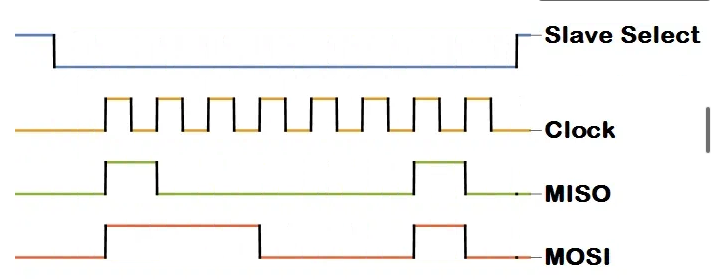

SPI协议规定一次传输中,CS是持续有效(你所说的拉低)。如果一次传输是4字节,那么就是CS包住连续的32个CLK;如果一次传输是1字节,那么就是CS包住8个CLK。

-

回复: T113-S3 UART4/5 发送异常发布在 其它全志芯片讨论区

@edward-x 在uboot阶段看看这几个脚的波形是怎么样的。另外观察下整个上电启动过程,叠加的正弦波是在什么时候出现的?是上电的一瞬间,还是运行到某个阶段开始才有?

-

回复: 100s tina 3.5.1 跑fbtft spi接口屏,LVGL 做长跑测试出现报错发布在 Linux

@wyljkl 看上去是驱动有问题导致锁有竞争,可以把相应得debug打开看下有没有有效信息

-

回复: 新 SDK 平台下载 D1-H/D1s SDK发布在 MR Series

@gharibi Woohoo, Congratulations, welcome join aw development.

-

回复: YT8531发布在 T Series

@shuaige MAC到PHY看起来是正常的,千兆这个速率大概率是PHY-PHY之间的问题。

可以换个网线,或者用通用PHY驱动试试。对端也是T527吗?

-

回复: 新 SDK 平台下载 D1-H/D1s SDK发布在 MR Series

@gharibi Yes baidu cloud can also download SDK, the only difference with git is cannot pull the newest code and git commit log

-

回复: 新 SDK 平台下载 D1-H/D1s SDK发布在 MR Series

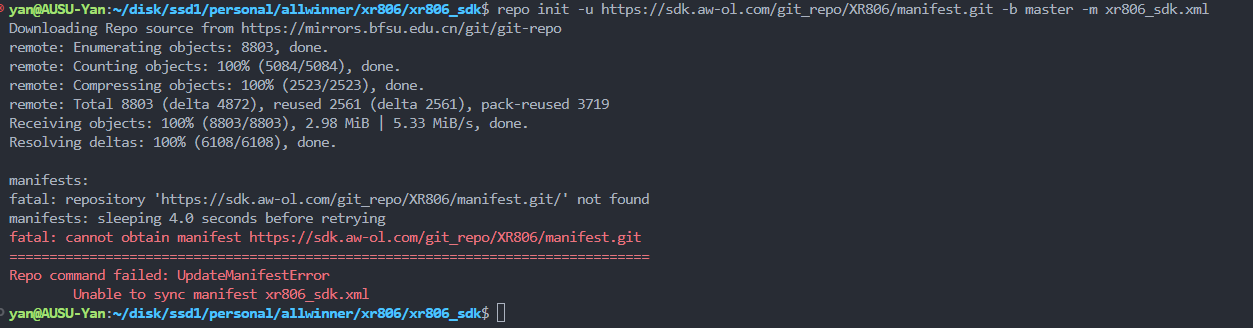

@gharibi Yes it's git configure issue, you can reference to https://www.cnblogs.com/jsdy/p/12191828.html

-

回复: 全志v85x spi通信速率稍微高点,spi clk就没输出,硬件BUG?用imx6ul就没有这种问题发布在 V Series

@sofia 没太明白,为什么软件32K频率读,控制器会是33M频率输出?你可以试下spidev_test测试是否正常

-

回复: 新 SDK 平台下载 D1-H/D1s SDK发布在 MR Series

@gharibi From the log i see the dl folder cannot download, cloud you please try clone it alone such as

git clone https://sdk.aw-ol.com/git_repo/D1_Tina_Open/tina-d1-h/product/tina/dl

to see what happend.

Again, I think is still network or your git configuretion issue.

Try the search early EOF or TLS packet keywords on google -

回复: t113主频问题发布在 MR Series

@wyljkl dts里面有频点表吗?试试

# 查看当前各个核频率 more /sys/devices/system/cpu/cpu*/cpufreq/cpuinfo_cur_freq | cat # 查看当前设置频点 cat /sys/devices/system/cpu/cpufreq/policy0/scaling_cur_freq # 查看系统当前可用频点 cat /sys/devices/system/cpu/cpufreq/policy0/scaling_available_frequencies # 查看当前调度策略 cat /sys/devices/system/cpu/cpufreq/policy0/scaling_governor echo performance > /sys/devices/system/cpu/cpufreq/policy0/scaling_governor -

回复: 新 SDK 平台下载 D1-H/D1s SDK发布在 MR Series

@gharibi Hi, where is your location? we didn't try it out of china

Maybe you need VPN...

Maybe you need VPN... -

回复: 全志v85x spi通信速率稍微高点,spi clk就没输出,硬件BUG?用imx6ul就没有这种问题发布在 V Series

- dmesg|grep spi看下spi的打印信息

- cat /sys/kernel/debug/clk/clk_summary 看下时钟树是怎么分配的

- dump ccu中对应spi的寄存器,看下实际的分频系数是多少

-

回复: T507 twi 加密芯片atsha204发布在 Linux

@z15242116489 dts节点要放对应的i2c下面,你放dtsi是没法识别到设备的。

最新社区内核代码github有

https://github.com/torvalds/linux -

回复: T507 twi 加密芯片atsha204发布在 Linux

@z15242116489 看上去不是这么简单使用的,需要先写配置命令,在进行响应操作。

可以参考下

https://blog.csdn.net/weixin_41263510/article/details/105263052

https://github.com/Tvirus/atsha204a_driver -

回复: MQ 卡在VCC_Pc not found这里发布在 编译和烧写问题专区

@wd15365693548 不用,在uboot命令行改启动参数就可以

setenv initcall_debug 1 boot -

回复: R128 SPI 问题 : 高于20MHZ CS控制出现异常, 导致无法传输数据, 且某些频率无法正常使用发布在 MR Series

- CS翻转问题请检查下逻辑分析仪的触发电平是否设置的太低?

- CLK不匹配问题,请看下CCU中SPI相关的寄存器与软件设置的值是否有差异?或者用hal_ccmu打印当前时钟源信息看看SPI是哪个时钟源,频率是多少?

-

回复: V851S I2C/TWI 损坏(xfer 错误)发布在 V Series

@kanken6174 不建议修改引脚驱动能力,因为i2c协议要求总线为弱上拉,提高IO驱动能力会使之变成强上拉

当VCC为1.8V时,上拉电阻应选用2K

当VCC为3.3V时,上拉电阻应选用4.7K若无法正常使用,应排查走线质量与信号干扰。

-

回复: 请问D1怎么才能通过命令行动态给SPI调速?发布在 MR Series

使用spidev-test测试命令的-s参数可以调整spi速率

Usage: ./spidev_test [-DsbdlHOLC3vpNR24SI] -D --device device to use (default /dev/spidev1.1) -s --speed max speed (Hz) -d --delay delay (usec) -b --bpw bits per word -i --input input data from a file (e.g. "test.bin") -o --output output data to a file (e.g. "results.bin") -l --loop loopback -H --cpha clock phase -O --cpol clock polarity -L --lsb least significant bit first -C --cs-high chip select active high -3 --3wire SI/SO signals shared -v --verbose Verbose (show tx buffer) -p Send data (e.g. "1234\xde\xad") -N --no-cs no chip select -R --ready slave pulls low to pause -2 --dual dual transfer -4 --quad quad transfer -8 --octal octal transfer -S --size transfer size -I --iter iterations -

回复: T507 twi 加密芯片atsha204发布在 Linux

@z15242116489 这种特殊芯片可能需要特定的时序访问才能读到正确数据,请贴上datasheet或者read/write相关时序图

-

回复: R528的uart1如何开启R485自动流控发布在 Linux

@liuqiang UART转RS485 IC的流控通过IO脚进行方向控制,控制器本身并没有这种功能,需要在代码里添加相关GPIO操作