T113-s3 CAN linux 下已调通

-

看到有朋友裸板调通T113-s3的CAN, 我以调通linux 下的CAN驱动,与君共享

dtsi 中加入

can0: can@02504000 { compatible = "allwinner,sunxi-t113-can"; reg = <0x0 0x02504000 0x0 0x400>; interrupts = <GIC_SPI 21 IRQ_TYPE_LEVEL_HIGH>;// 21+32 =53 clocks = <&ccu CLK_BUS_CAN0>; clock-names = "can0"; resets = <&ccu RST_BUS_CAN0>; status = "disabled"; }; can1: can@02504400 { compatible = "allwinner,sunxi-t113-can"; reg = <0x0 0x02504400 0x0 0x400>; interrupts = <GIC_SPI 22 IRQ_TYPE_LEVEL_HIGH>;// 22+32 =54 clocks = <&ccu CLK_BUS_CAN1>; clock-names = "can1"; resets = <&ccu RST_BUS_CAN1>; status = "disabled"; };dts 中 加入

can0_pins_a: can0_pins@0 { pins = "PB2", "PB3"; function = "can0"; drive-strength = <10>; bias-pull-up; }; can0_pins_b: can0_pins@1 { pins = "PB2", "PB3"; function = "gpio_in"; }; can1_pins_a: can1_pins@0 { pins = "PB4", "PB5"; function = "can1"; drive-strength = <10>; bias-pull-up; }; can1_pins_b: can1_pins@1 { pins = "PB4", "PB5"; function = "gpio_in"; };。。

&can0 { pinctrl-names = "default"; pinctrl-0 = <&can0_pins_a>; pinctrl-1 = <&can0_pins_b>; status = "okay"; }; &can1 { pinctrl-names = "default"; pinctrl-0 = <&can1_pins_a>; pinctrl-1 = <&can1_pins_b>; status = "okay"; };驱动文件 放入 drivers/net/can/sun4i_can.c 这个文件是我改的

/* * sun4i_can.c - CAN bus controller driver for Allwinner SUN4I&SUN7I based SoCs * * Copyright (C) 2013 Peter Chen * Copyright (C) 2015 Gerhard Bertelsmann * All rights reserved. * * Parts of this software are based on (derived from) the SJA1000 code by: * Copyright (C) 2014 Oliver Hartkopp <oliver.hartkopp@volkswagen.de> * Copyright (C) 2007 Wolfgang Grandegger <wg@grandegger.com> * Copyright (C) 2002-2007 Volkswagen Group Electronic Research * Copyright (C) 2003 Matthias Brukner, Trajet Gmbh, Rebenring 33, * 38106 Braunschweig, GERMANY * * Redistribution and use in source and binary forms, with or without * modification, are permitted provided that the following conditions * are met: * 1. Redistributions of source code must retain the above copyright * notice, this list of conditions and the following disclaimer. * 2. Redistributions in binary form must reproduce the above copyright * notice, this list of conditions and the following disclaimer in the * documentation and/or other materials provided with the distribution. * 3. Neither the name of Volkswagen nor the names of its contributors * may be used to endorse or promote products derived from this software * without specific prior written permission. * * Alternatively, provided that this notice is retained in full, this * software may be distributed under the terms of the GNU General * Public License ("GPL") version 2, in which case the provisions of the * GPL apply INSTEAD OF those given above. * * The provided data structures and external interfaces from this code * are not restricted to be used by modules with a GPL compatible license. * * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS * "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT * LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR * A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT * OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, * SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT * LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, * DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY * THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT * (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE * OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH * DAMAGE. * */ #include <linux/netdevice.h> #include <linux/can.h> #include <linux/can/dev.h> #include <linux/can/error.h> #include <linux/can/led.h> #include <linux/clk.h> #include <linux/reset.h> #include <linux/delay.h> #include <linux/interrupt.h> #include <linux/init.h> #include <linux/io.h> #include <linux/module.h> #include <linux/of.h> #include <linux/of_device.h> #include <linux/platform_device.h> #define DRV_NAME "sunxi_can" /* Registers address (physical base address 0x01C2BC00) */ #define SUN4I_REG_MSEL_ADDR 0x0000 /* CAN Mode Select */ #define SUN4I_REG_CMD_ADDR 0x0004 /* CAN Command */ #define SUN4I_REG_STA_ADDR 0x0008 /* CAN Status */ #define SUN4I_REG_INT_ADDR 0x000c /* CAN Interrupt Flag */ #define SUN4I_REG_INTEN_ADDR 0x0010 /* CAN Interrupt Enable */ #define SUN4I_REG_BTIME_ADDR 0x0014 /* CAN Bus Timing 0 */ #define SUN4I_REG_TEWL_ADDR 0x0018 /* CAN Tx Error Warning Limit */ #define SUN4I_REG_ERRC_ADDR 0x001c /* CAN Error Counter */ #define SUN4I_REG_RMCNT_ADDR 0x0020 /* CAN Receive Message Counter */ #define SUN4I_REG_RBUFSA_ADDR 0x0024 /* CAN Receive Buffer Start Address */ #define SUN4I_REG_BUF0_ADDR 0x0040 /* CAN Tx/Rx Buffer 0 */ #define SUN4I_REG_BUF1_ADDR 0x0044 /* CAN Tx/Rx Buffer 1 */ #define SUN4I_REG_BUF2_ADDR 0x0048 /* CAN Tx/Rx Buffer 2 */ #define SUN4I_REG_BUF3_ADDR 0x004c /* CAN Tx/Rx Buffer 3 */ #define SUN4I_REG_BUF4_ADDR 0x0050 /* CAN Tx/Rx Buffer 4 */ #define SUN4I_REG_BUF5_ADDR 0x0054 /* CAN Tx/Rx Buffer 5 */ #define SUN4I_REG_BUF6_ADDR 0x0058 /* CAN Tx/Rx Buffer 6 */ #define SUN4I_REG_BUF7_ADDR 0x005c /* CAN Tx/Rx Buffer 7 */ #define SUN4I_REG_BUF8_ADDR 0x0060 /* CAN Tx/Rx Buffer 8 */ #define SUN4I_REG_BUF9_ADDR 0x0064 /* CAN Tx/Rx Buffer 9 */ #define SUN4I_REG_BUF10_ADDR 0x0068 /* CAN Tx/Rx Buffer 10 */ #define SUN4I_REG_BUF11_ADDR 0x006c /* CAN Tx/Rx Buffer 11 */ #define SUN4I_REG_BUF12_ADDR 0x0070 /* CAN Tx/Rx Buffer 12 */ #define SUN4I_REG_ACPC_ADDR 0x0028 /* CAN Acceptance Code 0 */ #define SUN4I_REG_ACPM_ADDR 0x002c /* CAN Acceptance Mask 0 */ #define SUN4I_REG_RBUF_RBACK_START_ADDR 0x0180 /* CAN transmit buffer start */ #define SUN4I_REG_RBUF_RBACK_END_ADDR 0x01b0 /* CAN transmit buffer end */ /* Controller Register Description */ /* mode select register (r/w) * offset:0x0000 default:0x0000_0001 */ #define SUN4I_MSEL_SLEEP_MODE (0x01 << 4) /* write in reset mode */ #define SUN4I_MSEL_WAKE_UP (0x00 << 4) #define SUN4I_MSEL_SINGLE_FILTER (0x01 << 3) /* write in reset mode */ #define SUN4I_MSEL_DUAL_FILTERS (0x00 << 3) #define SUN4I_MSEL_LOOPBACK_MODE BIT(2) #define SUN4I_MSEL_LISTEN_ONLY_MODE BIT(1) #define SUN4I_MSEL_RESET_MODE BIT(0) /* command register (w) * offset:0x0004 default:0x0000_0000 */ #define SUN4I_CMD_BUS_OFF_REQ BIT(5) #define SUN4I_CMD_SELF_RCV_REQ BIT(4) #define SUN4I_CMD_CLEAR_OR_FLAG BIT(3) #define SUN4I_CMD_RELEASE_RBUF BIT(2) #define SUN4I_CMD_ABORT_REQ BIT(1) #define SUN4I_CMD_TRANS_REQ BIT(0) /* status register (r) * offset:0x0008 default:0x0000_003c */ #define SUN4I_STA_BIT_ERR (0x00 << 22) #define SUN4I_STA_FORM_ERR (0x01 << 22) #define SUN4I_STA_STUFF_ERR (0x02 << 22) #define SUN4I_STA_OTHER_ERR (0x03 << 22) #define SUN4I_STA_MASK_ERR (0x03 << 22) #define SUN4I_STA_ERR_DIR BIT(21) #define SUN4I_STA_ERR_SEG_CODE (0x1f << 16) #define SUN4I_STA_START (0x03 << 16) #define SUN4I_STA_ID28_21 (0x02 << 16) #define SUN4I_STA_ID20_18 (0x06 << 16) #define SUN4I_STA_SRTR (0x04 << 16) #define SUN4I_STA_IDE (0x05 << 16) #define SUN4I_STA_ID17_13 (0x07 << 16) #define SUN4I_STA_ID12_5 (0x0f << 16) #define SUN4I_STA_ID4_0 (0x0e << 16) #define SUN4I_STA_RTR (0x0c << 16) #define SUN4I_STA_RB1 (0x0d << 16) #define SUN4I_STA_RB0 (0x09 << 16) #define SUN4I_STA_DLEN (0x0b << 16) #define SUN4I_STA_DATA_FIELD (0x0a << 16) #define SUN4I_STA_CRC_SEQUENCE (0x08 << 16) #define SUN4I_STA_CRC_DELIMITER (0x18 << 16) #define SUN4I_STA_ACK (0x19 << 16) #define SUN4I_STA_ACK_DELIMITER (0x1b << 16) #define SUN4I_STA_END (0x1a << 16) #define SUN4I_STA_INTERMISSION (0x12 << 16) #define SUN4I_STA_ACTIVE_ERROR (0x11 << 16) #define SUN4I_STA_PASSIVE_ERROR (0x16 << 16) #define SUN4I_STA_TOLERATE_DOMINANT_BITS (0x13 << 16) #define SUN4I_STA_ERROR_DELIMITER (0x17 << 16) #define SUN4I_STA_OVERLOAD (0x1c << 16) #define SUN4I_STA_BUS_OFF BIT(7) #define SUN4I_STA_ERR_STA BIT(6) #define SUN4I_STA_TRANS_BUSY BIT(5) #define SUN4I_STA_RCV_BUSY BIT(4) #define SUN4I_STA_TRANS_OVER BIT(3) #define SUN4I_STA_TBUF_RDY BIT(2) #define SUN4I_STA_DATA_ORUN BIT(1) #define SUN4I_STA_RBUF_RDY BIT(0) /* interrupt register (r) * offset:0x000c default:0x0000_0000 */ #define SUN4I_INT_BUS_ERR BIT(7) #define SUN4I_INT_ARB_LOST BIT(6) #define SUN4I_INT_ERR_PASSIVE BIT(5) #define SUN4I_INT_WAKEUP BIT(4) #define SUN4I_INT_DATA_OR BIT(3) #define SUN4I_INT_ERR_WRN BIT(2) #define SUN4I_INT_TBUF_VLD BIT(1) #define SUN4I_INT_RBUF_VLD BIT(0) /* interrupt enable register (r/w) * offset:0x0010 default:0x0000_0000 */ #define SUN4I_INTEN_BERR BIT(7) #define SUN4I_INTEN_ARB_LOST BIT(6) #define SUN4I_INTEN_ERR_PASSIVE BIT(5) #define SUN4I_INTEN_WAKEUP BIT(4) #define SUN4I_INTEN_OR BIT(3) #define SUN4I_INTEN_ERR_WRN BIT(2) #define SUN4I_INTEN_TX BIT(1) #define SUN4I_INTEN_RX BIT(0) /* error code */ #define SUN4I_ERR_INRCV (0x1 << 5) #define SUN4I_ERR_INTRANS (0x0 << 5) /* filter mode */ #define SUN4I_FILTER_CLOSE 0 #define SUN4I_SINGLE_FLTER_MODE 1 #define SUN4I_DUAL_FILTER_MODE 2 /* message buffer flags */ #define SUN4I_MSG_EFF_FLAG BIT(7) #define SUN4I_MSG_RTR_FLAG BIT(6) /* max. number of interrupts handled in ISR */ #define SUN4I_CAN_MAX_IRQ 20 #define SUN4I_MODE_MAX_RETRIES 200 struct sun4ican_priv { struct can_priv can; void __iomem *base; struct clk *clk; struct reset_control *reset; spinlock_t cmdreg_lock; /* lock for concurrent cmd register writes */ }; static const struct can_bittiming_const sun4ican_bittiming_const = { .name = DRV_NAME, .tseg1_min = 1, .tseg1_max = 16, .tseg2_min = 1, .tseg2_max = 8, .sjw_max = 4, .brp_min = 1, .brp_max = 64, .brp_inc = 1, }; static void sun4i_can_write_cmdreg(struct sun4ican_priv *priv, u8 val) { unsigned long flags; spin_lock_irqsave(&priv->cmdreg_lock, flags); writel(val, priv->base + SUN4I_REG_CMD_ADDR); spin_unlock_irqrestore(&priv->cmdreg_lock, flags); } static int set_normal_mode(struct net_device *dev) { struct sun4ican_priv *priv = netdev_priv(dev); int retry = SUN4I_MODE_MAX_RETRIES; u32 mod_reg_val = 0; do { mod_reg_val = readl(priv->base + SUN4I_REG_MSEL_ADDR); mod_reg_val &= ~SUN4I_MSEL_RESET_MODE; writel(mod_reg_val, priv->base + SUN4I_REG_MSEL_ADDR); } while (retry-- && (mod_reg_val & SUN4I_MSEL_RESET_MODE)); if (readl(priv->base + SUN4I_REG_MSEL_ADDR) & SUN4I_MSEL_RESET_MODE) { netdev_err(dev, "setting controller into normal mode failed!\n"); return -ETIMEDOUT; } return 0; } static int set_reset_mode(struct net_device *dev) { struct sun4ican_priv *priv = netdev_priv(dev); int retry = SUN4I_MODE_MAX_RETRIES; u32 mod_reg_val = 0; do { mod_reg_val = readl(priv->base + SUN4I_REG_MSEL_ADDR); mod_reg_val |= SUN4I_MSEL_RESET_MODE; writel(mod_reg_val, priv->base + SUN4I_REG_MSEL_ADDR); } while (retry-- && !(mod_reg_val & SUN4I_MSEL_RESET_MODE)); if (!(readl(priv->base + SUN4I_REG_MSEL_ADDR) & SUN4I_MSEL_RESET_MODE)) { netdev_err(dev, "setting controller into reset mode failed!\n"); return -ETIMEDOUT; } return 0; } /* bittiming is called in reset_mode only */ static int sun4ican_set_bittiming(struct net_device *dev) { struct sun4ican_priv *priv = netdev_priv(dev); struct can_bittiming *bt = &priv->can.bittiming; u32 cfg; cfg = ((bt->brp - 1) & 0x3FF) | (((bt->sjw - 1) & 0x3) << 14) | (((bt->prop_seg + bt->phase_seg1 - 1) & 0xf) << 16) | (((bt->phase_seg2 - 1) & 0x7) << 20); if (priv->can.ctrlmode & CAN_CTRLMODE_3_SAMPLES) cfg |= 0x800000; netdev_dbg(dev, "setting BITTIMING=0x%08x\n", cfg); writel(cfg, priv->base + SUN4I_REG_BTIME_ADDR); return 0; } static int sun4ican_get_berr_counter(const struct net_device *dev, struct can_berr_counter *bec) { struct sun4ican_priv *priv = netdev_priv(dev); u32 errors; int err; err = clk_prepare_enable(priv->clk); if (err) { netdev_err(dev, "could not enable clock\n"); return err; } errors = readl(priv->base + SUN4I_REG_ERRC_ADDR); bec->txerr = errors & 0xFF; bec->rxerr = (errors >> 16) & 0xFF; clk_disable_unprepare(priv->clk); return 0; } static int sun4i_can_start(struct net_device *dev) { struct sun4ican_priv *priv = netdev_priv(dev); int err; u32 mod_reg_val; /* we need to enter the reset mode */ err = set_reset_mode(dev); if (err) { netdev_err(dev, "could not enter reset mode\n"); return err; } /* set filters - we accept all */ writel(0x00000000, priv->base + SUN4I_REG_ACPC_ADDR); writel(0xFFFFFFFF, priv->base + SUN4I_REG_ACPM_ADDR); /* clear error counters and error code capture */ writel(0, priv->base + SUN4I_REG_ERRC_ADDR); /* enable interrupts */ if (priv->can.ctrlmode & CAN_CTRLMODE_BERR_REPORTING) writel(0xFF, priv->base + SUN4I_REG_INTEN_ADDR); else writel(0xFF & ~SUN4I_INTEN_BERR, priv->base + SUN4I_REG_INTEN_ADDR); /* enter the selected mode */ mod_reg_val = readl(priv->base + SUN4I_REG_MSEL_ADDR); if (priv->can.ctrlmode & CAN_CTRLMODE_LOOPBACK) mod_reg_val |= SUN4I_MSEL_LOOPBACK_MODE; else if (priv->can.ctrlmode & CAN_CTRLMODE_LISTENONLY) mod_reg_val |= SUN4I_MSEL_LISTEN_ONLY_MODE; writel(mod_reg_val, priv->base + SUN4I_REG_MSEL_ADDR); err = sun4ican_set_bittiming(dev); if (err) return err; /* we are ready to enter the normal mode */ err = set_normal_mode(dev); if (err) { netdev_err(dev, "could not enter normal mode\n"); return err; } priv->can.state = CAN_STATE_ERROR_ACTIVE; return 0; } static int sun4i_can_stop(struct net_device *dev) { struct sun4ican_priv *priv = netdev_priv(dev); int err; priv->can.state = CAN_STATE_STOPPED; /* we need to enter reset mode */ err = set_reset_mode(dev); if (err) { netdev_err(dev, "could not enter reset mode\n"); return err; } /* disable all interrupts */ writel(0, priv->base + SUN4I_REG_INTEN_ADDR); return 0; } static int sun4ican_set_mode(struct net_device *dev, enum can_mode mode) { int err; switch (mode) { case CAN_MODE_START: err = sun4i_can_start(dev); if (err) { netdev_err(dev, "starting CAN controller failed!\n"); return err; } if (netif_queue_stopped(dev)) netif_wake_queue(dev); break; default: return -EOPNOTSUPP; } return 0; } /* transmit a CAN message * message layout in the sk_buff should be like this: * xx xx xx xx ff ll 00 11 22 33 44 55 66 77 * [ can_id ] [flags] [len] [can data (up to 8 bytes] */ static netdev_tx_t sun4ican_start_xmit(struct sk_buff *skb, struct net_device *dev) { struct sun4ican_priv *priv = netdev_priv(dev); struct can_frame *cf = (struct can_frame *)skb->data; u8 dlc; u32 dreg, msg_flag_n; canid_t id; int i; if (can_dropped_invalid_skb(dev, skb)) return NETDEV_TX_OK; netif_stop_queue(dev); id = cf->can_id; dlc = cf->can_dlc; msg_flag_n = dlc; if (id & CAN_RTR_FLAG) msg_flag_n |= SUN4I_MSG_RTR_FLAG; if (id & CAN_EFF_FLAG) { msg_flag_n |= SUN4I_MSG_EFF_FLAG; dreg = SUN4I_REG_BUF5_ADDR; writel((id >> 21) & 0xFF, priv->base + SUN4I_REG_BUF1_ADDR); writel((id >> 13) & 0xFF, priv->base + SUN4I_REG_BUF2_ADDR); writel((id >> 5) & 0xFF, priv->base + SUN4I_REG_BUF3_ADDR); writel((id << 3) & 0xF8, priv->base + SUN4I_REG_BUF4_ADDR); } else { dreg = SUN4I_REG_BUF3_ADDR; writel((id >> 3) & 0xFF, priv->base + SUN4I_REG_BUF1_ADDR); writel((id << 5) & 0xE0, priv->base + SUN4I_REG_BUF2_ADDR); } for (i = 0; i < dlc; i++) writel(cf->data[i], priv->base + (dreg + i * 4)); writel(msg_flag_n, priv->base + SUN4I_REG_BUF0_ADDR); can_put_echo_skb(skb, dev, 0); if (priv->can.ctrlmode & CAN_CTRLMODE_LOOPBACK) sun4i_can_write_cmdreg(priv, SUN4I_CMD_SELF_RCV_REQ); else sun4i_can_write_cmdreg(priv, SUN4I_CMD_TRANS_REQ); return NETDEV_TX_OK; } static void sun4i_can_rx(struct net_device *dev) { struct sun4ican_priv *priv = netdev_priv(dev); struct net_device_stats *stats = &dev->stats; struct can_frame *cf; struct sk_buff *skb; u8 fi; u32 dreg; canid_t id; int i; /* create zero'ed CAN frame buffer */ skb = alloc_can_skb(dev, &cf); if (!skb) return; fi = readl(priv->base + SUN4I_REG_BUF0_ADDR); cf->can_dlc = get_can_dlc(fi & 0x0F); if (fi & SUN4I_MSG_EFF_FLAG) { dreg = SUN4I_REG_BUF5_ADDR; id = (readl(priv->base + SUN4I_REG_BUF1_ADDR) << 21) | (readl(priv->base + SUN4I_REG_BUF2_ADDR) << 13) | (readl(priv->base + SUN4I_REG_BUF3_ADDR) << 5) | ((readl(priv->base + SUN4I_REG_BUF4_ADDR) >> 3) & 0x1f); id |= CAN_EFF_FLAG; } else { dreg = SUN4I_REG_BUF3_ADDR; id = (readl(priv->base + SUN4I_REG_BUF1_ADDR) << 3) | ((readl(priv->base + SUN4I_REG_BUF2_ADDR) >> 5) & 0x7); } /* remote frame ? */ if (fi & SUN4I_MSG_RTR_FLAG) id |= CAN_RTR_FLAG; else for (i = 0; i < cf->can_dlc; i++) cf->data[i] = readl(priv->base + dreg + i * 4); cf->can_id = id; sun4i_can_write_cmdreg(priv, SUN4I_CMD_RELEASE_RBUF); stats->rx_packets++; stats->rx_bytes += cf->can_dlc; netif_rx(skb); can_led_event(dev, CAN_LED_EVENT_RX); } static int sun4i_can_err(struct net_device *dev, u8 isrc, u8 status) { struct sun4ican_priv *priv = netdev_priv(dev); struct net_device_stats *stats = &dev->stats; struct can_frame *cf; struct sk_buff *skb; enum can_state state = priv->can.state; enum can_state rx_state, tx_state; unsigned int rxerr, txerr, errc; u32 ecc, alc; /* we don't skip if alloc fails because we want the stats anyhow */ skb = alloc_can_err_skb(dev, &cf); errc = readl(priv->base + SUN4I_REG_ERRC_ADDR); rxerr = (errc >> 16) & 0xFF; txerr = errc & 0xFF; if (skb) { cf->data[6] = txerr; cf->data[7] = rxerr; } if (isrc & SUN4I_INT_DATA_OR) { /* data overrun interrupt */ netdev_dbg(dev, "data overrun interrupt\n"); if (likely(skb)) { cf->can_id |= CAN_ERR_CRTL; cf->data[1] = CAN_ERR_CRTL_RX_OVERFLOW; } stats->rx_over_errors++; stats->rx_errors++; /* reset the CAN IP by entering reset mode * ignoring timeout error */ set_reset_mode(dev); set_normal_mode(dev); /* clear bit */ sun4i_can_write_cmdreg(priv, SUN4I_CMD_CLEAR_OR_FLAG); } if (isrc & SUN4I_INT_ERR_WRN) { /* error warning interrupt */ netdev_dbg(dev, "error warning interrupt\n"); if (status & SUN4I_STA_BUS_OFF) state = CAN_STATE_BUS_OFF; else if (status & SUN4I_STA_ERR_STA) state = CAN_STATE_ERROR_WARNING; else state = CAN_STATE_ERROR_ACTIVE; } if (isrc & SUN4I_INT_BUS_ERR) { /* bus error interrupt */ netdev_dbg(dev, "bus error interrupt\n"); priv->can.can_stats.bus_error++; stats->rx_errors++; if (likely(skb)) { ecc = readl(priv->base + SUN4I_REG_STA_ADDR); cf->can_id |= CAN_ERR_PROT | CAN_ERR_BUSERROR; switch (ecc & SUN4I_STA_MASK_ERR) { case SUN4I_STA_BIT_ERR: cf->data[2] |= CAN_ERR_PROT_BIT; break; case SUN4I_STA_FORM_ERR: cf->data[2] |= CAN_ERR_PROT_FORM; break; case SUN4I_STA_STUFF_ERR: cf->data[2] |= CAN_ERR_PROT_STUFF; break; default: cf->data[3] = (ecc & SUN4I_STA_ERR_SEG_CODE) >> 16; break; } /* error occurred during transmission? */ if ((ecc & SUN4I_STA_ERR_DIR) == 0) cf->data[2] |= CAN_ERR_PROT_TX; } } if (isrc & SUN4I_INT_ERR_PASSIVE) { /* error passive interrupt */ netdev_dbg(dev, "error passive interrupt\n"); if (state == CAN_STATE_ERROR_PASSIVE) state = CAN_STATE_ERROR_WARNING; else state = CAN_STATE_ERROR_PASSIVE; } if (isrc & SUN4I_INT_ARB_LOST) { /* arbitration lost interrupt */ netdev_dbg(dev, "arbitration lost interrupt\n"); alc = readl(priv->base + SUN4I_REG_STA_ADDR); priv->can.can_stats.arbitration_lost++; stats->tx_errors++; if (likely(skb)) { cf->can_id |= CAN_ERR_LOSTARB; cf->data[0] = (alc >> 8) & 0x1f; } } if (state != priv->can.state) { tx_state = txerr >= rxerr ? state : 0; rx_state = txerr <= rxerr ? state : 0; if (likely(skb)) can_change_state(dev, cf, tx_state, rx_state); else priv->can.state = state; if (state == CAN_STATE_BUS_OFF) can_bus_off(dev); } if (likely(skb)) { stats->rx_packets++; stats->rx_bytes += cf->can_dlc; netif_rx(skb); } else { return -ENOMEM; } return 0; } static irqreturn_t sun4i_can_interrupt(int irq, void *dev_id) { struct net_device *dev = (struct net_device *)dev_id; struct sun4ican_priv *priv = netdev_priv(dev); struct net_device_stats *stats = &dev->stats; u8 isrc, status; int n = 0; while ((isrc = readl(priv->base + SUN4I_REG_INT_ADDR)) && (n < SUN4I_CAN_MAX_IRQ)) { n++; status = readl(priv->base + SUN4I_REG_STA_ADDR); if (isrc & SUN4I_INT_WAKEUP) netdev_warn(dev, "wakeup interrupt\n"); if (isrc & SUN4I_INT_TBUF_VLD) { /* transmission complete interrupt */ stats->tx_bytes += readl(priv->base + SUN4I_REG_RBUF_RBACK_START_ADDR) & 0xf; stats->tx_packets++; can_get_echo_skb(dev, 0); netif_wake_queue(dev); can_led_event(dev, CAN_LED_EVENT_TX); } if ((isrc & SUN4I_INT_RBUF_VLD) && !(isrc & SUN4I_INT_DATA_OR)) { /* receive interrupt - don't read if overrun occurred */ while (status & SUN4I_STA_RBUF_RDY) { /* RX buffer is not empty */ sun4i_can_rx(dev); status = readl(priv->base + SUN4I_REG_STA_ADDR); } } if (isrc & (SUN4I_INT_DATA_OR | SUN4I_INT_ERR_WRN | SUN4I_INT_BUS_ERR | SUN4I_INT_ERR_PASSIVE | SUN4I_INT_ARB_LOST)) { /* error interrupt */ if (sun4i_can_err(dev, isrc, status)) netdev_err(dev, "can't allocate buffer - clearing pending interrupts\n"); } /* clear interrupts */ writel(isrc, priv->base + SUN4I_REG_INT_ADDR); readl(priv->base + SUN4I_REG_INT_ADDR); } if (n >= SUN4I_CAN_MAX_IRQ) netdev_dbg(dev, "%d messages handled in ISR", n); return (n) ? IRQ_HANDLED : IRQ_NONE; } static int sun4ican_open(struct net_device *dev) { struct sun4ican_priv *priv = netdev_priv(dev); int err; /* common open */ err = open_candev(dev); if (err) return err; /* register interrupt handler */ err = request_irq(dev->irq, sun4i_can_interrupt, 0, dev->name, dev); if (err) { netdev_err(dev, "request_irq err: %d\n", err); goto exit_irq; } err = reset_control_assert(priv->reset); if (err) { netdev_err(dev, "[CAN] Unable to assert reset clock return %x\n", PTR_RET(priv->clk)); goto exit_clock; } err =reset_control_deassert(priv->reset) ; if (err) { netdev_err(dev,"[CAN] Unable to deassert reset clock return %x\n", PTR_RET(priv->clk)); goto exit_clock; } /* turn on clocking for CAN peripheral block */ err = clk_prepare_enable(priv->clk); if (err) { netdev_err(dev, "could not enable CAN peripheral clock\n"); goto exit_clock; } err = sun4i_can_start(dev); if (err) { netdev_err(dev, "could not start CAN peripheral\n"); goto exit_can_start; } can_led_event(dev, CAN_LED_EVENT_OPEN); netif_start_queue(dev); return 0; exit_can_start: clk_disable_unprepare(priv->clk); exit_clock: free_irq(dev->irq, dev); exit_irq: close_candev(dev); return err; } static int sun4ican_close(struct net_device *dev) { struct sun4ican_priv *priv = netdev_priv(dev); netif_stop_queue(dev); sun4i_can_stop(dev); clk_disable_unprepare(priv->clk); free_irq(dev->irq, dev); close_candev(dev); can_led_event(dev, CAN_LED_EVENT_STOP); return 0; } static const struct net_device_ops sun4ican_netdev_ops = { .ndo_open = sun4ican_open, .ndo_stop = sun4ican_close, .ndo_start_xmit = sun4ican_start_xmit, }; static const struct of_device_id sun4ican_of_match[] = { {.compatible = "allwinner,sunxi-t113-can"}, {}, }; MODULE_DEVICE_TABLE(of, sun4ican_of_match); static int sun4ican_remove(struct platform_device *pdev) { struct net_device *dev = platform_get_drvdata(pdev); unregister_netdev(dev); free_candev(dev); return 0; } static int sun4ican_probe(struct platform_device *pdev) { struct device_node *np = pdev->dev.of_node; struct resource *mem_res; struct clk *clk; void __iomem *addr; int err, irq; struct net_device *dev; struct sun4ican_priv *priv; struct reset_control *reset; clk = of_clk_get(np, 0); if (IS_ERR(clk)) { dev_err(&pdev->dev, "unable to request clock\n"); err = -ENODEV; goto exit; } irq = platform_get_irq(pdev, 0); if (irq < 0) { dev_err(&pdev->dev, "could not get a valid irq\n"); err = -ENODEV; goto exit; } mem_res = platform_get_resource(pdev, IORESOURCE_MEM, 0); //dev_info(&pdev->dev, "CAN device phy_addr 0x%x)\n",(u32)mem_res->start); addr = devm_ioremap_resource(&pdev->dev, mem_res); if (IS_ERR(addr)) { err = -EBUSY; goto exit; } reset=devm_reset_control_get(&pdev->dev, NULL); if (IS_ERR_OR_NULL(reset)) { dev_err(&pdev->dev,"[can] Unable to acquire reset clock , return %x\n",PTR_RET(reset)); err = -ENXIO; goto exit; } dev = alloc_candev(sizeof(struct sun4ican_priv), 1); if (!dev) { dev_err(&pdev->dev,"could not allocate memory for CAN device\n"); err = -ENOMEM; goto exit; } dev->netdev_ops = &sun4ican_netdev_ops; dev->irq = irq; dev->flags |= IFF_ECHO; priv = netdev_priv(dev); priv->can.clock.freq = clk_get_rate(clk); priv->can.bittiming_const = &sun4ican_bittiming_const; priv->can.do_set_mode = sun4ican_set_mode; priv->can.do_get_berr_counter = sun4ican_get_berr_counter; priv->can.ctrlmode_supported = CAN_CTRLMODE_BERR_REPORTING | CAN_CTRLMODE_LISTENONLY | CAN_CTRLMODE_LOOPBACK | CAN_CTRLMODE_3_SAMPLES; priv->base = addr; priv->clk = clk; priv->reset= reset; spin_lock_init(&priv->cmdreg_lock); platform_set_drvdata(pdev, dev); SET_NETDEV_DEV(dev, &pdev->dev); err = register_candev(dev); if (err) { dev_err(&pdev->dev, "registering %s failed (err=%d)\n", DRV_NAME, err); goto exit_free; } devm_can_led_init(dev); dev_info(&pdev->dev, "device registered ( base=%p, irq=%d )\n", priv->base, dev->irq); return 0; exit_free: free_candev(dev); exit: return err; } static struct platform_driver sun4i_can_driver = { .driver = { .name = DRV_NAME, .of_match_table = sun4ican_of_match, }, .probe = sun4ican_probe, .remove = sun4ican_remove, }; module_platform_driver(sun4i_can_driver); MODULE_AUTHOR("Peter Chen <xingkongcp@gmail.com>"); MODULE_AUTHOR("Gerhard Bertelsmann <info@gerhard-bertelsmann.de>"); MODULE_LICENSE("Dual BSD/GPL"); MODULE_DESCRIPTION("CAN driver for Allwinner SoCs (T113-s3)");drivers/net/can/Kconfig 加入

粗体字config CAN_SUN8I tristate "Sun8i CAN bus controller" default n help This is the Sun8i CAN BUS driver for android system by peter chen.drivers/net/can/Makefile 加入

obj-$(CONFIG_CAN_SUN8I) += sun4i_can.o -

Moved from 公告 by

q1215200171

q1215200171

-

@liukia 大侠 有应用的测试程序吗 贴上来看看吧 想知道怎么初始化 发送 接收 数据

-

-

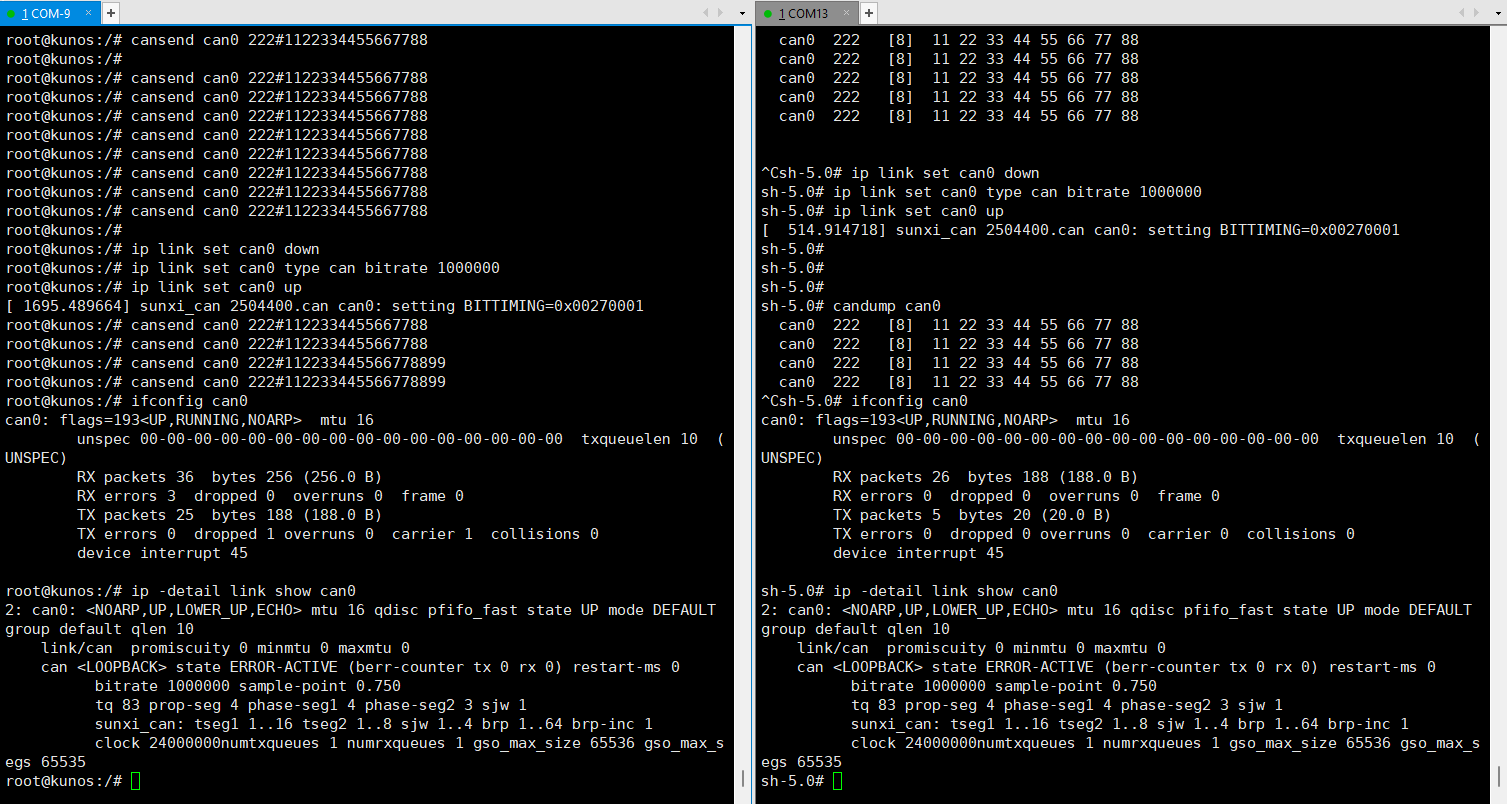

@lansecd 读取压力测试怎么样 我这边1M速度 8000多帧会出现丢帧 2500帧才稳定

-

@a892755772 压力测试没啥问题,老哥USB1用了没,配置CAN工作后,USB1做HOST没反应了,有遇到不

-

Referenced by L liukia

-

@lansecd USB1 没有用啊

-

@a892755772 有解决吗,我也遇到类似的问题

-

@lizh023 还没有找到问题,CAN0会影响USB1,CAN1没事

-

This post is deleted! -

@lansecd @a892755772 刚刚没有描述清楚我的问题,我也遇到压力测试会丢帧的问题,这边1M速度 75%总线负载下测试!有时候也会出现CAN掉线异常状态。你们有思路可以分享一下吗

-

@lizh023 我发现禁用网络就没有问题 就是不连接WiFi 把掉网线。猜测是CAN在Linux这边认为是网络设备 其他网络设备通讯导致丢帧

-

@lansecd

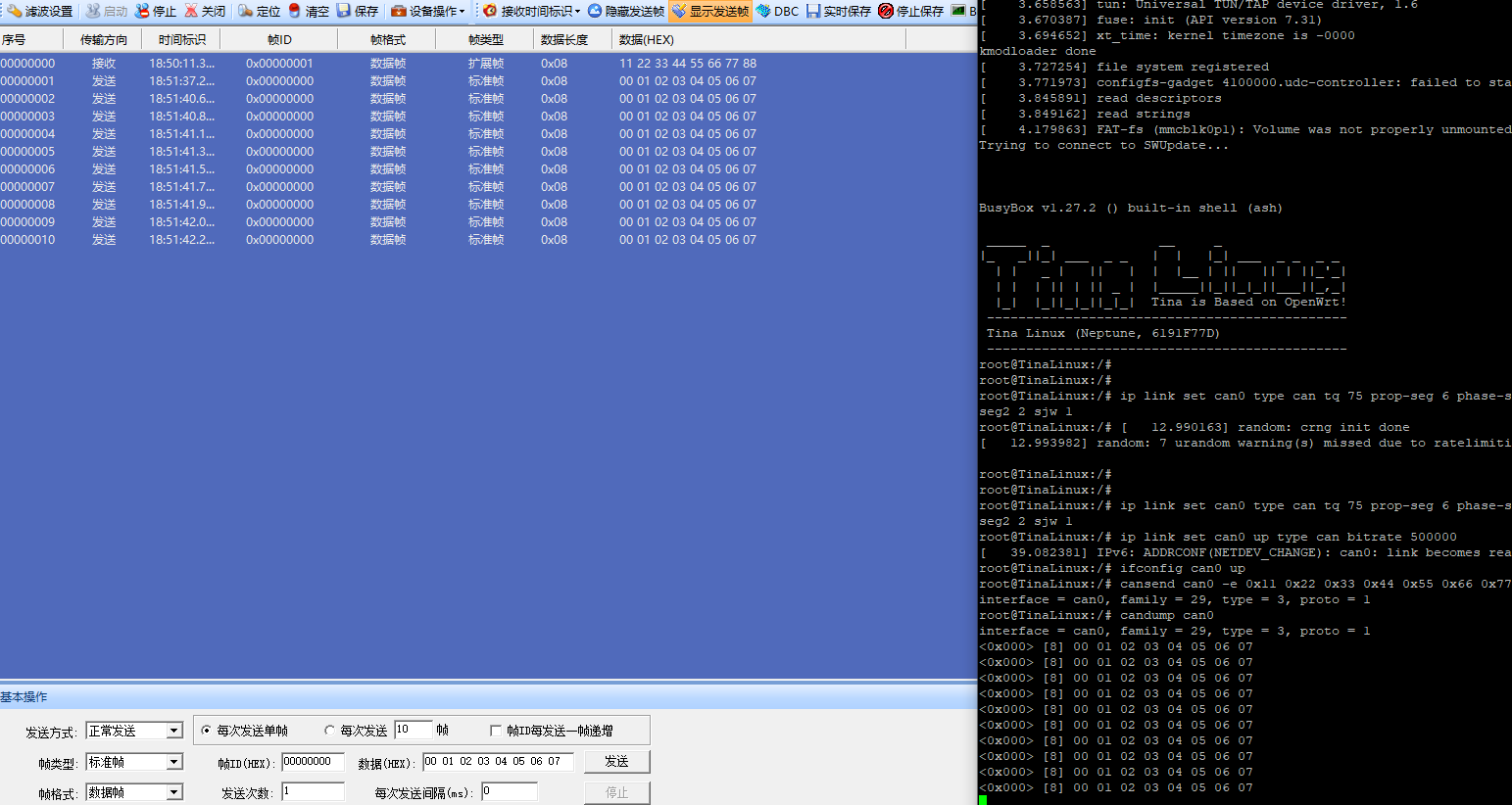

你好,我按照上面修改,执行cansend can0 123#1122334455667788会报错,跪求大佬给看看吧!root@TinaLinux:/# cansend can0 123#1122334455667788 interface = can0, family = 29, type = 3, proto = 1[ 55.350220] sunxi_can 2504000.can can0: error warning interrupt [ 55.360888] sunxi_can 2504000.can can0: bus error interrupt [ 55.367103] sunxi_can 2504000.can can0: New error state: 1 root@TinaLinux:/# ifconfig can0 can0 Link encap:UNSPEC HWaddr 00-00-00-00-00-00-00-00-00-00-00-00-00-00-00-00 UP RUNNING NOARP MTU:16 Metric:1 RX packets:1 errors:1 dropped:0 overruns:0 frame:0 TX packets:0 errors:0 dropped:0 overruns:0 carrier:0 collisions:0 txqueuelen:10 RX bytes:8 (8.0 B) TX bytes:0 (0.0 B) Interrupt:45 root@TinaLinux:/# ip -detail link show can0 2: can0: <NOARP,UP,LOWER_UP,ECHO> mtu 16 qdisc pfifo_fast state UP mode DEFAULT group default qlen 10 link/can promiscuity 0 minmtu 0 maxmtu 0 can state ERROR-WARNING (berr-counter tx 183 rx 0) restart-ms 0 bitrate 125000 sample-point 0.875 tq 500 prop-seg 6 phase-seg1 7 phase-seg2 2 sjw 1 brp 12 sunxi_can: tseg1 1..16 tseg2 1..8 sjw 1..4 brp 1..64 brp_inc 1 clock 24000000 numtxqueues 1 numrxqueues 1 gso_max_size 65536 gso_max_segs 65535下面是启动信息

[ 0.000000] Booting Linux on physical CPU 0x0 [ 0.000000] Linux version 5.4.61 (t113@t113) (arm-openwrt-linux-muslgnueabi-gcc.bin (OpenWrt/CodeSourcery GCC 8.3.0 2021.08) 8.3.0, GNU ld (GNU Binutils) 2.28) #269 SMP PREEMPT Mon Oct 17 08:37:45 UTC 2022 [ 0.000000] CPU: ARMv7 Processor [410fc075] revision 5 (ARMv7), cr=10c5387d [ 0.000000] CPU: div instructions available: patching division code [ 0.000000] CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache [ 0.000000] OF: fdt: Machine model: sun8iw20 [ 0.000000] printk: bootconsole [earlycon0] enabled [ 0.000000] Memory policy: Data cache writealloc [ 0.000000] cma: Reserved 4 MiB at 0x47c00000 [ 0.000000] On node 0 totalpages: 32768 [ 0.000000] Normal zone: 256 pages used for memmap [ 0.000000] Normal zone: 0 pages reserved [ 0.000000] Normal zone: 32768 pages, LIFO batch:7 [ 0.000000] psci: probing for conduit method from DT. [ 0.000000] psci: PSCIv1.0 detected in firmware. [ 0.000000] psci: Using standard PSCI v0.2 function IDs [ 0.000000] psci: MIGRATE_INFO_TYPE not supported. [ 0.000000] psci: SMC Calling Convention v1.0 [ 0.000000] percpu: Embedded 15 pages/cpu s30412 r8192 d22836 u61440 [ 0.000000] pcpu-alloc: s30412 r8192 d22836 u61440 alloc=15*4096 [ 0.000000] pcpu-alloc: [0] 0 [0] 1 [ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 32512 [ 0.000000] Kernel command line: earlyprintk=sunxi-uart,0x02500C00 clk_ignore_unused initcall_debug=0 console=ttyS3,115200 rootdelay=2 loglevel=8 root=/dev/mmcblk0p5 init=/pseudo_init partitions=boot-resource@mmcblk0p1:env@mmcblk0p2:env-redund@mmcblk0p3:boot@mmcblk0p4:rootfs@mmcblk0p5:private@mmcblk0p6:rootfs_data@mmcblk0p7:UDISK@mmcblk0p8 cma=4M snum= mac_addr= wifi_mac= bt_mac= specialstr= gpt=1 androidboot.mode=normal androidboot.hardware=sun8iw20p1 boot_type=2 androidboot.boot_type=2 gpt=1 uboot_message=2018.05-g2a1965a-dirty(07/10/2022-02:50:57) mbr_offset=1032192 disp_reserve=2457600,0x43f06000 androidboot.dramsize=128 [ 0.000000] Dentry cache hash table entries: 16384 (order: 4, 65536 bytes, linear) [ 0.000000] Inode-cache hash table entries: 8192 (order: 3, 32768 bytes, linear) [ 0.000000] mem auto-init: stack:off, heap alloc:off, heap free:off [ 0.000000] Memory: 104088K/131072K available (6144K kernel code, 281K rwdata, 1624K rodata, 1024K init, 1168K bss, 22888K reserved, 4096K cma-reserved) [ 0.000000] SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=2, Nodes=1 [ 0.000000] rcu: Preemptible hierarchical RCU implementation. [ 0.000000] Tasks RCU enabled. [ 0.000000] rcu: RCU calculated value of scheduler-enlistment delay is 10 jiffies. [ 0.000000] NR_IRQS: 16, nr_irqs: 16, preallocated irqs: 16 [ 0.000000] random: get_random_bytes called from start_kernel+0x258/0x3dc with crng_init=0 [ 0.000000] arch_timer: cp15 timer(s) running at 24.00MHz (phys). [ 0.000000] clocksource: arch_sys_counter: mask: 0xffffffffffffff max_cycles: 0x588fe9dc0, max_idle_ns: 440795202592 ns [ 0.000005] sched_clock: 56 bits at 24MHz, resolution 41ns, wraps every 4398046511097ns [ 0.008007] Switching to timer-based delay loop, resolution 41ns [ 0.014187] clocksource: timer: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 79635851949 ns [ 0.023900] Calibrating delay loop (skipped), value calculated using timer frequency.. 48.00 BogoMIPS (lpj=240000) [ 0.034266] pid_max: default: 32768 minimum: 301 [ 0.039007] Mount-cache hash table entries: 1024 (order: 0, 4096 bytes, linear) [ 0.046346] Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes, linear) [ 0.054661] CPU: Testing write buffer coherency: ok [ 0.059860] /cpus/cpu@0 missing clock-frequency property [ 0.065202] /cpus/cpu@1 missing clock-frequency property [ 0.070539] CPU0: thread -1, cpu 0, socket 0, mpidr 80000000 [ 0.076701] Setting up static identity map for 0x40100000 - 0x40100060 [ 0.083355] rcu: Hierarchical SRCU implementation. [ 0.088557] smp: Bringing up secondary CPUs ... [ 0.094199] CPU1: thread -1, cpu 1, socket 0, mpidr 80000001 [ 0.094322] smp: Brought up 1 node, 2 CPUs [ 0.104142] SMP: Total of 2 processors activated (96.00 BogoMIPS). [ 0.110337] CPU: All CPU(s) started in SVC mode. [ 0.115403] devtmpfs: initialized [ 0.130531] VFP support v0.3: implementor 41 architecture 2 part 30 variant 7 rev 5 [ 0.138635] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604462750000 ns [ 0.148749] pinctrl core: initialized pinctrl subsystem [ 0.154915] NET: Registered protocol family 16 [ 0.160898] DMA: preallocated 256 KiB pool for atomic coherent allocations [ 0.195317] rtc_ccu: sunxi ccu init OK [ 0.201339] ccu: sunxi ccu init OK [ 0.205167] r_ccu: sunxi ccu init OK [ 0.228353] iommu: Default domain type: Translated [ 0.233437] sunxi iommu: irq = 24 [ 0.237604] SCSI subsystem initialized [ 0.241619] usbcore: registered new interface driver usbfs [ 0.247147] usbcore: registered new interface driver hub [ 0.252569] usbcore: registered new device driver usb [ 0.258353] Advanced Linux Sound Architecture Driver Initialized. [ 0.265176] Bluetooth: Core ver 2.22 [ 0.268801] NET: Registered protocol family 31 [ 0.273237] Bluetooth: HCI device and connection manager initialized [ 0.279633] Bluetooth: HCI socket layer initialized [ 0.284524] Bluetooth: L2CAP socket layer initialized [ 0.289593] Bluetooth: SCO socket layer initialized [ 0.294730] pwm module init! [ 0.298757] g2d 5410000.g2d: Adding to iommu group 0 [ 0.304012] G2D: rcq version initialized.major:251 [ 0.309628] clocksource: Switched to clocksource arch_sys_counter [ 0.324253] sun8iw20-pinctrl 2000000.pinctrl: initialized sunXi PIO driver [ 0.332880] sunxi udc is no enable [ 0.336514] NET: Registered protocol family 2 [ 0.341638] tcp_listen_portaddr_hash hash table entries: 512 (order: 0, 6144 bytes, linear) [ 0.350072] TCP established hash table entries: 1024 (order: 0, 4096 bytes, linear) [ 0.357739] TCP bind hash table entries: 1024 (order: 1, 8192 bytes, linear) [ 0.364819] TCP: Hash tables configured (established 1024 bind 1024) [ 0.371276] UDP hash table entries: 256 (order: 1, 8192 bytes, linear) [ 0.377835] UDP-Lite hash table entries: 256 (order: 1, 8192 bytes, linear) [ 0.385028] NET: Registered protocol family 1 [ 0.391574] workingset: timestamp_bits=30 max_order=15 bucket_order=0 [ 0.403041] squashfs: version 4.0 (2009/01/31) Phillip Lougher [ 0.409014] ntfs: driver 2.1.32 [Flags: R/W]. [ 0.448760] io scheduler mq-deadline registered [ 0.453322] io scheduler kyber registered [ 0.458352] [DISP]disp_module_init [ 0.462326] disp 5000000.disp: Adding to iommu group 0 [ 0.467981] [DISP] disp_init,line:2386: [ 0.467986] smooth display screen:0 type:1 mode:4 [ 0.493181] display_fb_request,fb_id:0 [ 0.502267] Freeing logo buffer memory: 2400K [ 0.507097] disp_al_manager_apply ouput_type:1 [ 0.509886] [DISP]disp_module_init finish [ 0.511722] [DISP] lcd_clk_config,line:744: [ 0.511733] disp 0, clk: pll(364000000),clk(364000000),dclk(52000000) dsi_rate(364000000) [ 0.511733] clk real:pll(360000000),clk(360000000),dclk(51428571) dsi_rate(0) [ 0.516494] sunxi_sid_init()551 - insmod ok [ 0.520032] sun8iw20-pinctrl 2000000.pinctrl: 2000000.pinctrl supply vcc-pd not found, using dummy regulator [ 0.536495] sun8iw20-pinctrl 2000000.pinctrl: 2000000.pinctrl supply vcc-pe not found, using dummy regulator [ 0.559881] uart uart0: uart0 supply uart not found, using dummy regulator [ 0.567000] uart0: ttyS0 at MMIO 0x2500000 (irq = 34, base_baud = 1500000) is a SUNXI [ 0.575522] uart uart3: uart3 supply uart not found, using dummy regulator [ 0.582711] uart3: ttyS3 at MMIO 0x2500c00 (irq = 35, base_baud = 1500000) is a SUNXI [ 0.590609] sw_console_setup()1808 - console setup baud 115200 parity n bits 8, flow n ÿ[ 0.598592] printk: console [ttyS3] enabled [ 0.598592] printk: console [ttyS3] enabled [ 0.607514] printk: bootconsole [earlycon0] disabled [ 0.607514] printk: bootconsole [earlycon0] disabled [ 0.618662] uart uart4: uart4 supply uart not found, using dummy regulator [ 0.626640] uart4: ttyS4 at MMIO 0x2501000 (irq = 36, base_baud = 1500000) is a SUNXI [ 0.635984] uart uart5: uart5 supply uart not found, using dummy regulator [ 0.643957] uart5: ttyS5 at MMIO 0x2501400 (irq = 37, base_baud = 1500000) is a SUNXI [ 0.653437] misc dump reg init [ 0.658160] dma-buf: Running sanitycheck [ 0.662578] dma-buf: Running dma_fence [ 0.666755] sizeof(dma_fence)=48 [ 0.670458] dma-buf: Running dma_fence/sanitycheck [ 0.675832] dma-buf: Running dma_fence/test_signaling [ 0.681480] dma-buf: Running dma_fence/test_add_callback [ 0.687402] dma-buf: Running dma_fence/test_late_add_callback [ 0.693829] dma-buf: Running dma_fence/test_rm_callback [ 0.699668] dma-buf: Running dma_fence/test_late_rm_callback [ 0.705984] dma-buf: Running dma_fence/test_status [ 0.711336] dma-buf: Running dma_fence/test_error [ 0.716579] dma-buf: Running dma_fence/test_wait [ 0.721738] dma-buf: Running dma_fence/test_wait_timeout [ 0.759643] dma-buf: Running dma_fence/test_stub [ 0.764809] dma-buf: Running dma_fence/race_signal_callback [ 0.839640] thread_signal_callback[0] completed 36602 passes, 50 misses [ 0.847046] thread_signal_callback[1] completed 36579 passes, 27 misses [ 0.919646] thread_signal_callback[0] completed 40641 passes, 40638 misses [ 0.927340] thread_signal_callback[1] completed 40629 passes, 40628 misses [ 0.935570] libphy: Fixed MDIO Bus: probed [ 0.940183] CAN device driver interface [ 0.944573] usbcore: registered new interface driver usb_8dev [ 0.951066] usbcore: registered new interface driver ems_usb [ 0.957409] usbcore: registered new interface driver esd_usb2 [ 0.963883] usbcore: registered new interface driver gs_usb [ 0.970206] usbcore: registered new interface driver kvaser_usb [ 0.976838] usbcore: registered new interface driver mcba_usb [ 0.983303] usbcore: registered new interface driver peak_usb [ 0.989756] usbcore: registered new interface driver ucan [ 0.996084] sun8iw20-pinctrl 2000000.pinctrl: 2000000.pinctrl supply vcc-pb not found, using dummy regulator [ 1.007874] sunxi_can 2504000.can: device registered ( base=(ptrval), irq=45 ) [ 1.016713] sunxi_can 2504400.can: device registered ( base=(ptrval), irq=46 ) [ 1.025225] usbcore: registered new interface driver cdc_ether [ 1.031806] usbcore: registered new interface driver rndis_host [ 1.038444] usbcore: registered new interface driver qmi_wwan [ 1.044864] ehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver [ 1.052153] sunxi-ehci: EHCI SUNXI driver [ 1.057031] get ehci0-controller wakeup-source is fail. [ 1.062881] sunxi ehci0-controller is no enable [ 1.067934] sunxi-ehci 4101000.ehci0-controller: init_sunxi_hci is fail [ 1.075342] sunxi-ehci: probe of 4101000.ehci0-controller failed with error -1 [ 1.083470] ohci_hcd: USB 1.1 'Open' Host Controller (OHCI) Driver [ 1.090403] sunxi-ohci: OHCI SUNXI driver [ 1.095277] get ohci0-controller wakeup-source is fail. [ 1.101126] sunxi ohci0-controller is no enable [ 1.106178] sunxi-ohci 4101400.ohci0-controller: init_sunxi_hci is fail [ 1.113586] sunxi-ohci: probe of 4101400.ohci0-controller failed with error -1 [ 1.121771] usbcore: registered new interface driver cdc_wdm [ 1.128143] usbcore: registered new interface driver usb-storage [ 1.134970] usbcore: registered new interface driver usbserial_generic [ 1.142291] usbserial: USB Serial support registered for generic [ 1.149016] usbcore: registered new interface driver option [ 1.155266] usbserial: USB Serial support registered for GSM modem (1-port) [ 1.163182] i2c /dev entries driver [ 1.167142] sunxi cedar version 1.1 [ 1.171223] sunxi-cedar 1c0e000.ve: Adding to iommu group 0 [ 1.177457] VE: failed to get alias ve id [ 1.177457] [ 1.183585] VE: sunxi_cedar_probe power-domain init!!! [ 1.189316] VE: install start!!! [ 1.189316] [ 1.194830] VE: cedar-ve the get irq is 43 [ 1.194830] [ 1.201248] VE: ve_debug_proc_info:(ptrval), data:(ptrval), lock:(ptrval) [ 1.201248] [ 1.210485] VE: install end!!! [ 1.210485] [ 1.215531] VE: sunxi_cedar_probe [ 1.219411] Bluetooth: HCI UART driver ver 2.3 [ 1.224381] Bluetooth: HCI UART protocol H4 registered [ 1.230132] Bluetooth: HCI UART protocol BCSP registered [ 1.236052] Bluetooth: HCI UART protocol (null) registered [ 1.242176] Bluetooth: HCI Realtek H5 protocol initialized [ 1.249722] sun8iw20-pinctrl 2000000.pinctrl: 2000000.pinctrl supply vcc-pc not found, using dummy regulator [ 1.260910] sunxi-mmc 4022000.sdmmc: SD/MMC/SDIO Host Controller Driver(v4.22 2021-12-20 15:40) [ 1.270826] sunxi-mmc 4022000.sdmmc: ***ctl-spec-caps*** 308 [ 1.277195] sunxi-mmc 4022000.sdmmc: No vmmc regulator found [ 1.283527] sunxi-mmc 4022000.sdmmc: No vqmmc regulator found [ 1.289954] sunxi-mmc 4022000.sdmmc: No vdmmc regulator found [ 1.296359] sunxi-mmc 4022000.sdmmc: No vd33sw regulator found [ 1.302873] sunxi-mmc 4022000.sdmmc: No vd18sw regulator found [ 1.309381] sunxi-mmc 4022000.sdmmc: No vq33sw regulator found [ 1.315895] sunxi-mmc 4022000.sdmmc: No vq18sw regulator found [ 1.322450] sunxi-mmc 4022000.sdmmc: Cann't get pin bias hs pinstate,check if needed [ 1.331891] sunxi-mmc 4022000.sdmmc: sdc set ios:clk 0Hz bm PP pm UP vdd 21 width 1 timing LEGACY(SDR12) dt B [ 1.355582] sunxi-mmc 4022000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B [ 1.379760] sunxi-mmc 4022000.sdmmc: detmode:alway in(non removable) [ 1.386864] sunxi-mmc 4022000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B [ 1.399545] sunxi-mmc 4020000.sdmmc: SD/MMC/SDIO Host Controller Driver(v4.22 2021-12-20 15:40) [ 1.401471] sunxi-mmc 4022000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B [ 1.409459] sunxi-mmc 4020000.sdmmc: ***ctl-spec-caps*** 8 [ 1.422177] sunxi-mmc 4022000.sdmmc: sdc set ios:clk 400000Hz bm OD pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B [ 1.426970] sunxi-mmc 4020000.sdmmc: No vmmc regulator found [ 1.444805] sunxi-mmc 4020000.sdmmc: No vqmmc regulator found [ 1.451222] sunxi-mmc 4020000.sdmmc: No vdmmc regulator found [ 1.457627] sunxi-mmc 4020000.sdmmc: No vd33sw regulator found [ 1.464152] sunxi-mmc 4020000.sdmmc: No vd18sw regulator found [ 1.464594] sunxi-mmc 4022000.sdmmc: sdc set ios:clk 400000Hz bm OD pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B [ 1.470666] sunxi-mmc 4020000.sdmmc: No vq33sw regulator found [ 1.470672] sunxi-mmc 4020000.sdmmc: No vq18sw regulator found [ 1.482289] sunxi-mmc 4022000.sdmmc: sdc set ios:clk 400000Hz bm OD pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B [ 1.489147] sunxi-mmc 4020000.sdmmc: Got CD GPIO [ 1.498271] sunxi-mmc 4022000.sdmmc: sdc set ios:clk 400000Hz bm OD pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B [ 1.523957] sunxi-mmc 4020000.sdmmc: sdc set ios:clk 0Hz bm PP pm UP vdd 21 width 1 timing LEGACY(SDR12) dt B [ 1.535074] sunxi-mmc 4020000.sdmmc: no vqmmc,Check if there is regulator [ 1.538929] sunxi-mmc 4022000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B [ 1.555182] sunxi-mmc 4020000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B [ 1.566564] sunxi-mmc 4022000.sdmmc: avoid to switch power_off_notification to POWERED_ON(0x01) [ 1.576457] sunxi-mmc 4022000.sdmmc: avoid to switch power_off_notification to POWERED_ON(0x01) [ 1.579543] sunxi-mmc 4020000.sdmmc: detmode:gpio irq [ 1.586190] sunxi-mmc 4022000.sdmmc: avoid to switch power_off_notification to POWERED_ON(0x01) [ 1.591848] sunxi-mmc 4020000.sdmmc: sdc set ios:clk 0Hz bm PP pm OFF vdd 0 width 1 timing LEGACY(SDR12) dt B [ 1.601536] sunxi-mmc 4022000.sdmmc: avoid to switch power_off_notification to POWERED_ON(0x01) [ 1.613112] sun8iw20-pinctrl 2000000.pinctrl: 2000000.pinctrl supply vcc-pg not found, using dummy regulator [ 1.622681] sunxi-mmc 4022000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing MMC-HS(SDR20) dt B [ 1.633572] sunxi-mmc 4021000.sdmmc: SD/MMC/SDIO Host Controller Driver(v4.22 2021-12-20 15:40) [ 1.645285] sunxi-mmc 4022000.sdmmc: sdc set ios:clk 50000000Hz bm PP pm ON vdd 21 width 1 timing MMC-HS(SDR20) dt B [ 1.654762] sunxi-mmc 4021000.sdmmc: ***ctl-spec-caps*** 8 [ 1.666549] sunxi-mmc 4022000.sdmmc: sdc set ios:clk 50000000Hz bm PP pm ON vdd 21 width 4 timing MMC-HS(SDR20) dt B [ 1.672482] sunxi-mmc 4021000.sdmmc: No vmmc regulator found [ 1.684415] sunxi-mmc 4022000.sdmmc: sdc set ios:clk 50000000Hz bm PP pm ON vdd 21 width 4 timing MMC-DDR52 dt B [ 1.690522] sunxi-mmc 4021000.sdmmc: No vqmmc regulator found [ 1.690527] sunxi-mmc 4021000.sdmmc: No vdmmc regulator found [ 1.690534] sunxi-mmc 4021000.sdmmc: No vd33sw regulator found [ 1.702072] mmc0: new DDR MMC card at address 0001 [ 1.708284] sunxi-mmc 4021000.sdmmc: No vd18sw regulator found [ 1.708292] sunxi-mmc 4021000.sdmmc: No vq33sw regulator found [ 1.715679] mmcblk0: mmc0:0001 4FTE4R 3.64 GiB [ 1.721249] sunxi-mmc 4021000.sdmmc: No vq18sw regulator found [ 1.726849] mmcblk0rpmb: mmc0:0001 4FTE4R partition 3 512 KiB, chardev (247:0) [ 1.733136] sunxi-mmc 4021000.sdmmc: Cann't get pin bias hs pinstate,check if needed [ 1.746127] mmcblk0: p1 p2 p3 p4 p5 p6 p7 p8 [ 1.773500] sunxi-mmc 4021000.sdmmc: sdc set ios:clk 0Hz bm PP pm UP vdd 21 width 1 timing LEGACY(SDR12) dt B [ 1.784638] sunxi-mmc 4021000.sdmmc: no vqmmc,Check if there is regulator [ 1.804764] sunxi-mmc 4021000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B [ 1.828936] sunxi-mmc 4021000.sdmmc: detmode:manually by software [ 1.836047] sunxi-mmc 4021000.sdmmc: smc 2 p1 err, cmd 52, RE !! [ 1.836357] exFAT: Version 1.3.0 [ 1.846646] sunxi-mmc 4021000.sdmmc: smc 2 p1 err, cmd 52, RE !! [ 1.853377] sunxi-mmc 4021000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B [ 1.865528] NET: Registered protocol family 10 [ 1.871414] Segment Routing with IPv6 [ 1.875614] NET: Registered protocol family 17 [ 1.880699] NET: Registered protocol family 15 [ 1.885759] can: controller area network core (rev 20170425 abi 9) [ 1.892756] NET: Registered protocol family 29 [ 1.897740] sunxi-mmc 4021000.sdmmc: sdc set ios:clk 400000Hz bm PP pm ON vdd 21 width 1 timing LEGACY(SDR12) dt B [ 1.899658] can: raw protocol (rev 20170425) [ 1.914065] sunxi-mmc 4021000.sdmmc: smc 2 p1 err, cmd 5, RE !! [ 1.920694] sunxi-mmc 4021000.sdmmc: smc 2 p1 err, cmd 5, RE !! [ 1.927307] sunxi-mmc 4021000.sdmmc: smc 2 p1 err, cmd 5, RE !! [ 1.933936] sunxi-mmc 4021000.sdmmc: smc 2 p1 err, cmd 5, RE !! [ 1.933963] sunxi-mmc 4021000.sdmmc: sdc set ios:clk 0Hz bm PP pm OFF vdd 0 width 1 timing LEGACY(SDR12) dt B [ 1.940698] Bluetooth: RFCOMM TTY layer initialized [ 1.957102] Bluetooth: RFCOMM socket layer initialized [ 1.962874] Bluetooth: RFCOMM ver 1.11 [ 1.967671] Registering SWP/SWPB emulation handler [ 1.987180] sunxi-i2c sunxi-i2c2: sunxi-i2c2 supply twi not found, using dummy regulator [ 1.997141] sunxi-i2c sunxi-i2c2: probe success [ 2.003092] sunxi udc is no enable [ 2.007224] get ehci0-controller wakeup-source is fail. [ 2.013104] sunxi ehci0-controller is no enable [ 2.018157] sunxi-ehci 4101000.ehci0-controller: init_sunxi_hci is fail [ 2.025575] sunxi-ehci: probe of 4101000.ehci0-controller failed with error -1 [ 2.033909] get ohci0-controller wakeup-source is fail. [ 2.039786] sunxi ohci0-controller is no enable [ 2.044840] sunxi-ohci 4101400.ohci0-controller: init_sunxi_hci is fail [ 2.052248] sunxi-ohci: probe of 4101400.ohci0-controller failed with error -1 [ 2.063396] clk: Not disabling unused clocks [ 2.068167] ALSA device list: [ 2.071684] platform regulatory.0: Direct firmware load for regulatory.db failed with error -2 [ 2.081332] No soundcards found. [ 2.081359] alloc_fd: slot 0 not NULL! [ 2.085154] cfg80211: failed to load regulatory.db [ 2.094907] Waiting 2 sec before mounting root device... [ 4.121191] random: fast init done [ 4.126824] VFS: Mounted root (squashfs filesystem) readonly on device 179:5. [ 4.136498] devtmpfs: mounted [ 4.140960] Freeing unused kernel memory: 1024K [ 4.159792] Run /pseudo_init as init process mount: mounting none on /dev failed: Resource busy [ 4.418421] EXT4-fs: Warning: mounting with data=journal disables delayed allocation and O_DIRECT support! [ 4.431816] EXT4-fs (mmcblk0p7): mounted filesystem with journalled data mode. Opts: data=journal can't run '/etc/preinit': No such file or directory mount: mounting proc on /proc failed: Resource busy mount: mounting tmpfs on /run failed: No such file or directory hostname: can't open '/etc/hostname': No such file or directory ------run rc.preboot file----- [ 4.586990] EXT4-fs (mmcblk0p8): mounted filesystem with ordered data mode. Opts: (null) ------run rc.modules file----- insmod: can't insert '/lib/modules/5.4.61/usb-storage.ko': No such file or directory [ 4.611946] sunxi_gpadc_init,2151, success [ 4.616831] sunxi_gpadc_setup: get channel scan data failed [ 4.623430] input: sunxi-gpadc0 as /devices/virtual/input/input0 insmod: can't insert '/lib/modules/5.4.61/8723ds.ko': Operation not permitted [ 9.173522] random: wpa_supplicant: uninitialized urandom read (3 bytes read) [ 9.181533] random: wpa_supplicant: uninitialized urandom read (1024 bytes read) Successfully initialized wpa_supplicant Could not read interface wlan0 flags: No such device nl80211: Driver does not support authentication/association or connect commands nl80211: deinit ifname=wlan0 disabled_11b_rates=0 Could not read interface wlan0 flags: No such device wlan0: Failed to initialize driver interface ------run rc.final file----- Trying to connect to SWUpdate... mount: mounting /dev/mmcblk0p1 on /mnt/extsd failed: No such file or directory BusyBox v1.27.2 () built-in shell (ash) ------run profile file----- _____ _ __ _ |_ _||_| ___ _ _ | | |_| ___ _ _ _ _ | | _ | || | | |__ | || || | ||_'_| | | | || | || _ | |_____||_||_|_||___||_,_| |_| |_||_|_||_|_| Tina is Based on OpenWrt! ---------------------------------------------- Tina Linux (Neptune, 5C1C9C53) ---------------------------------------------- nodev debugfs [ 9.347500] get ctp_name is fail, -22 [ 9.351865] get ctp_power is fail, -22 [ 9.356191] get ctp_power_ldo_vol is fail, -22 [ 9.361883] sunxi_ctp_startup: ctp_power_io is invalid. [ 9.367829] get ctp_gesture_wakeup fail, no gesture wakeup [ 9.374269] gt9xxnew_ts 2-005d: 2-005d supply ctp not found, using dummy regulator [ 9.379695] file system registered swu_param: #### swu_software: #### swu_mode: #### no swupdate_cmd to run, wait for next swupdate sh: write error: No such device [ 9.420072] read descriptors [ 9.423300] read strings [ 9.545816] sunxi-i2c sunxi-i2c2: drv-mode: dma read data end [ 9.579879] input: gt9xxnew_ts as /devices/virtual/input/input1 [ 9.639084] sunxi_can 2504000.can can0: setting BITTIMING=0x001c000b [ 9.646388] IPv6: ADDRCONF(NETDEV_CHANGE): can0: link becomes ready root@TinaLinux:/# [ 16.193296] random: crng init done root@TinaLinux:/# root@TinaLinux:/# root@TinaLinux:/# cansend can0 123#1122334455667788 interface = can0, family = 29, type = 3, proto = 1[ 30.130429] sunxi_can 2504000.can can0: error warning interrupt [ 30.141054] sunxi_can 2504000.can can0: bus error interrupt [ 30.147269] sunxi_can 2504000.can can0: New error state: 1 -

@msh410278586 已经调通了,can芯片的电压不正常,正常后就没问题了。

-

@liukia 你好,我是按照你方法配置can的,ifconfig里面有can0和can1,但是使用ifconfig can0 up就会报错,似乎跟波特率相关,难道我还有其他的配置要做吗

-

你好!200K的波特率有没有测试过?我现在用创龙的开发板测试,200K的收发都不正常,发送会提示BUS-OFF。100K,500K则工作正常。

-

@liukia 你好 我在《T113-S3_Datasheet_V1.5.pdf》与 《T113-S3_User_Manual_V1.2.pdf》找不到相关的CAN 寄存器说明,请问你是哪里查到的啊?

-

Moved from MR Series by

xiaowenge

xiaowenge -

Referenced by W wjp2547532

-

大佬,想问一下,你有测试过80k以下波特率的吗?我试了一下,会报这个错误。

ip link set can0 type can bitrate 50000

sunxi_can 2504000.can can0: bitrate error 8589934.5% too high。你有遇到过吗? -

@msh410278586 内核需要进行什么设置吗?用的是不是百闻网提供的tina?

-

你好,我的不晓得为啥ifconfig -a 都没有can显示出来,用的TINA配置的

-

@qinlinbin 在 T113-s3 CAN linux 下已调通 中说:

大佬,想问一下,你有测试过80k以下波特率的吗?我试了一下,会报这个错误。

ip link set can0 type can bitrate 50000

sunxi_can 2504000.can can0: bitrate error 8589934.5% too high。你有遇到过吗?看起来是驱动不支持这么低波特率?

-

感谢博主的分享,已在T113下把CAN调通,谢谢

-

我来补一下,不让更多人浪费时间;

在 sun8iw20-ccu.h 添加

#define CLK_BUS_CAN0 73

#define CLK_BUS_CAN1 74#define RST_BUS_CAN0 28

#define RST_BUS_CAN1 29 -

This post is deleted! -

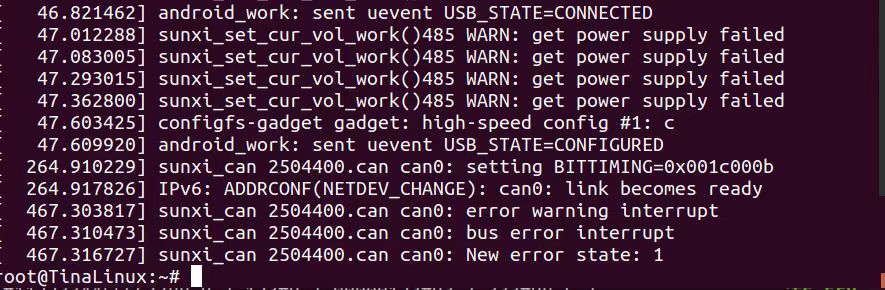

今天也要调这个CANBUS,按照步骤写好后,ip link set can0 up,可以看到 can0 ready。

但是,一调用cansend can0 123#11223344556677,就不行,跳了一个中断错误。

大佬给看看,什么情况?!

-

@allbluecom 我遇到了同样的错误,请问解决了吗?

-

@allbluecom 我遇到了同样的错误,请问解决了吗?是怎么解决的呀

-

@msh410278586n您好,can的问题您解决了吗

Copyright © 2024 深圳全志在线有限公司 粤ICP备2021084185号 粤公网安备44030502007680号