@willok 发表一个回复就是LV2了

awwwwa 发布的最佳帖子

-

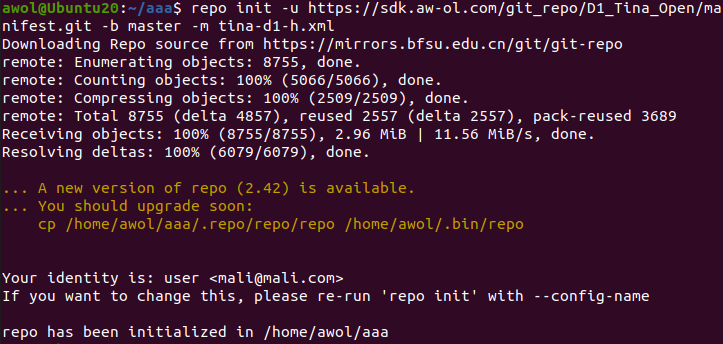

回复: 搭建开发环境,出现问了了,总是报fatal: cannot obtain manifest https://sdk.aw-ol.com/git_repo/V853Tina_Open/manifest.git发布在 V Series

- 执行命令设置全局保存密码

git config --global credential.helper store- 执行命令输入密码

git clone https://sdk.aw-ol.com/git_repo/V853Tina_Open/manifest.git- 使用repo拉取sdk

repo init -u https://sdk.aw-ol.com/git_repo/V853Tina_Open/manifest.git -b master -m tina-v853-open.xml由于repo更新,目前不支持通过repo输入密码,请先使用git命令输入保存密码

-

R128-S2 驱动 1024x600 RGB 显示屏 并运行 LVGL发布在 A Series

由于屏幕较大首先精简系统内存,关闭DSP核心,并将 RV 核心移到 HSPSRAM 上提高带宽。配置 LV_COLOR_DEPTH 16 提高帧率降低内存占用

patch 如下,增加了新方案r128-devkit-rgb:161ca91b-f759-4108-8bfc-85114394da0c-r128-devkit-rgb.tar.gz

编译打包即可

700ms启动 LVGL:

-

回复: V853 的 CPU1(E907)启动流程发布在 RTOS

参考Linux端代码即可,本质上为:

- 加载固件

- 调用 firmware 接口获取文件系统中的固件

- 解析固件的 resource_table 段,该段有如下内容

- 声明需要的内存(Linux 为其分配)

- 声明使用的 vdev(固定为一个)

- 声明使用的 vring(固定为两个)

- 将固件加载到指定地址

- 注册 rpmsg virtio 设备

- 提供 vdev->ops(基于 virtio 接口实现的)

- 与 rpmsg_bus 驱动匹配,完成 rpmsg 初始化

- 启动小核

- 调用 rproc->ops->start

- 加载固件

-

回复: 寻求tina的display 官方文档说明,感谢发布在 V Series

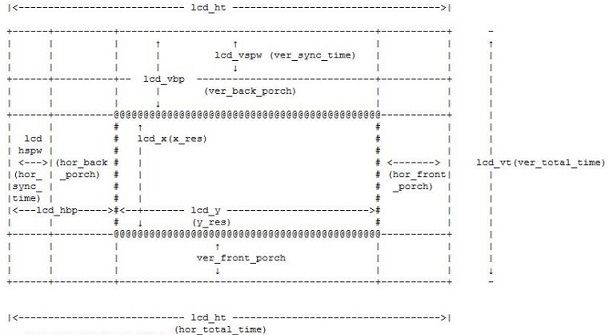

disp init configuration disp_mode (0:screen0<screen0,fb0>) screenx_output_type (0:none; 1:lcd; 2:tv; 3:hdmi;5:vdpo) screenx_output_mode (used for hdmi output, 0:480i 1:576i 2:480p 3:576p 4:720p50) (5:720p60 6:1080i50 7:1080i60 8:1080p24 9:1080p50 10:1080p60) screenx_output_format (for hdmi, 0:RGB 1:yuv444 2:yuv422 3:yuv420) screenx_output_bits (for hdmi, 0:8bit 1:10bit 2:12bit 2:16bit) screenx_output_eotf (for hdmi, 0:reserve 4:SDR 16:HDR10 18:HLG) screenx_output_cs (for hdmi, 0:undefined 257:BT709 260:BT601 263:BT2020) screenx_output_dvi_hdmi (for hdmi, 0:undefined 1:dvi mode 2:hdmi mode) screen0_output_range (for hdmi, 0:default 1:full 2:limited) screen0_output_scan (for hdmi, 0:no data 1:overscan 2:underscan) screen0_output_aspect_ratio (for hdmi, 8-same as original picture 9-4:3 10-16:9 11-14:9) fbx format (4:RGB655 5:RGB565 6:RGB556 7:ARGB1555 8:RGBA5551 9:RGB888 10:ARGB8888 12:ARGB4444) fbx pixel sequence (0:ARGB 1:BGRA 2:ABGR 3:RGBA) fb0_scaler_mode_enable(scaler mode enable, used FE) fbx_width,fbx_height (framebuffer horizontal/vertical pixels, fix to output resolution while equal 0) lcdx_backlight (lcd init backlight,the range:[0,256],default:197 lcdx_yy (lcd init screen bright/contrast/saturation/hue, value:0~100, default:50/50/57/50) lcd0_contrast (LCD contrast, 0~100) lcd0_saturation (LCD saturation, 0~100) lcd0_hue (LCD hue, 0~100) framebuffer software rotation setting: disp_rotation_used: (0:disable; 1:enable,you must set fbX_width to lcd_y, set fbX_height to lcd_x) degreeX: (X:screen index; 0:0 degree; 1:90 degree; 3:270 degree) degreeX_Y: (X:screen index; Y:layer index 0~15; 0:0 degree; 1:90 degree; 3:270 degree) devX_output_type : config output type in bootGUI framework in UBOOT-2018. (0:none; 1:lcd; 2:tv; 4:hdmi;) devX_output_mode : config output resolution(see include/video/sunxi_display2.h) of bootGUI framework in UBOOT-2018 devX_screen_id : config display index of bootGUI framework in UBOOT-2018 devX_do_hpd : whether do hpd detectation or not in UBOOT-2018 chn_cfg_mode : Hardware DE channel allocation config. 0:single display with 6 channel, 1:dual display with 4 channel in main display and 2 channel in second display, 2:dual display with 3 channel in main display and 3 channel in second in display. -

回复: 有R128点亮百问网7寸RGB屏的DEMO吗?发布在 A Series

R128-S2 驱动 1024x600 RGB 显示屏 并运行 LVGL

https://bbs.aw-ol.com/topic/4316/share/1 -

回复: 个人开发者如何获取D1、D1s的 SDK?需要签NDA吗?发布在 代码下载问题专区

@damiaa 现在是新版本平台了,直接拿awol账号下载,免去再注册一个平台的麻烦:https://d1.docs.aw-ol.com/study/study_3getsdktoc/

-

回复: V851S tina linux ov5647 驱动程序没有 dmesg发布在 V Series

ov5647 这个型号的摄像头并没有适配,SDK也没有支持。

请参考V85x的摄像头支持手册选择适配的摄像头。这里推荐已经量产的产品使用的GC2063,GC2083,GC4663这三款摄像头,已经经过严格的测试与调试,可以达到最佳画质和分辨率

-

回复: 关于打印启动日志到/dev/fb0的问题发布在 V Series

找到 env.cfg

#kernel command arguments earlyprintk=sunxi-uart,0x02500000 initcall_debug=0 console=ttyS0,115200 consolefb=tty0 nand_root=ubi0_4 mmc_root=/dev/mmcblk0p4 nor_root=/dev/mtdblock1 init=/init loglevel=8 coherent_pool=16K #reserve_list=30M@64M,78M@128M,200M@512M mac= wifi_mac= bt_mac= specialstr= root_partition=rootfs mtd_name=sys rootfstype=ubifs, rw #set kernel cmdline if boot.img or recovery.img has no cmdline we will use this setargs_nor=setenv bootargs earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} console=${console—fb} loglevel=${loglevel} root=${nor_root} rootwait init=${init} rdinit=${rdinit} partitions=${partitions} cma=${cma} coherent_pool=${coherent_pool} ion_carveout_list=${reserve_list} setargs_nand=setenv bootargs earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} console=${console—fb} loglevel=${loglevel} ubi.mtd=${mtd_name} root=${nand_root} rootfstype=${rootfstype} rootwait init=${init} rdinit=${rdinit} partitions=${partitions} cma=${cma} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} selinux=${selinux} specialstr=${specialstr} coherent_pool=${coherent_pool} ion_carveout_list=${reserve_list} setargs_nand_ubi=setenv bootargs ubi.mtd=${mtd_name} earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} console=${console—fb} loglevel=${loglevel} root=${nand_root} rootfstype=${rootfstype} init=${init} partitions=${partitions} cma=${cma} snum=${snum} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} specialstr=${specialstr} gpt=1 setargs_mmc=setenv bootargs earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} console=${console—fb} loglevel=${loglevel} root=${mmc_root} rootwait init=${init} partitions=${partitions} cma=${cma} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} selinux=${selinux} specialstr=${specialstr} coherent_pool=${coherent_pool} ion_carveout_list=${reserve_list} #nand command syntax: sunxi_flash read address partition_name read_bytes #0x4007f800 = 0x40080000(kernel entry) - 0x800(boot.img header 2k) boot_partition=boot boot_normal=sunxi_flash read 44800000 ${boot_partition};bootm 44800000 boot_recovery=sunxi_flash read 44800000 extend;bootm 44800000 boot_fastboot=fastboot #recovery key recovery_key_value_max=0x13 recovery_key_value_min=0x10 #fastboot key fastboot_key_value_max=0x8 fastboot_key_value_min=0x2 #uboot system env config bootdelay=1 #default bootcmd, will change at runtime according to key press bootcmd=run setargs_nand boot_normal#default nand boot #verify the kernel verify=N -

回复: V853S mipi LCD显示驱动调试,colorbar显示异常发布在 V Series

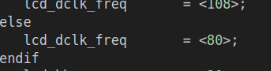

dclk过高,屏幕分屏了?

这里提供一个py脚本计算分频系数,这里对应的是HV屏,DSI也可以参考def find_closest_clock(target_clock, clock_list): clock_list = sorted(clock_list) low, high = 0, len(clock_list) - 1 closest = clock_list[low] while low <= high: mid = (low + high) // 2 if clock_list[mid] < target_clock: low = mid + 1 elif clock_list[mid] > target_clock: high = mid - 1 else: return clock_list[mid] if abs(clock_list[mid] - target_clock) < abs(closest - target_clock): closest = clock_list[mid] return closest def calculate_divisor(clock_need, clock_list, min_divisor=6): is_perfect = True for i in clock_list: for j in range(0, 255): if (clock_need * j) == i: closest_clock = i divisor = j return closest_clock, divisor, is_perfect is_perfect = False closest_clock = find_closest_clock(clock_need, clock_list) if closest_clock == 0: return None, None, None divisor = closest_clock // clock_need if divisor < min_divisor: min_diff = float('inf') best_clock = None for clock in clock_list: if clock >= clock_need * min_divisor: current_divisor = clock // clock_need if current_divisor < min_divisor: continue diff = abs(clock - clock_need * current_divisor) if diff < min_diff: min_diff = diff best_clock = clock if best_clock is not None: return best_clock, best_clock // clock_need, is_perfect return closest_clock, divisor, is_perfect clock_list = [ 408, 420, 432, 444, 456, 468, 480, 492, 504, 516, 528, 540, 552, 564, 576, 588, 600, 612, 624, 636, 648, 660, 672, 684, 696, 708, 720, 732, 744, 756, 768, 780, 792, 804, 816, 828, 840, 852, 864, 876, 888, 900, 912, 924, 936, 948, 960, 972, 984, 996, 1008, 1020, 1032, 1044, 1056, 1068, 1080, 1092, 1104, 1116, 1128, 1140, 1152, 1164, 1176, 1188, 1200, 1212, 1224, 1236, 1248, 1260, 1272, 1284, 1296, 1308, 1320, 1332, 1344, 1356, 1368, 1380, 1392, 1404, 1416, 1428, 1440, 1452, 1464, 1476, 1488, 1500, 1512, 1524, 1536, 1548, 1560, 1572, 1584, 1596, 1608, 1620, 1632, 1644, 1656, 1668, 1680, 1692 ] clock_need = int(input("请输入需要的时钟(MHz): ")) closest_clock, divisor, is_perfect = calculate_divisor(clock_need, clock_list) if is_perfect: print(f"父时钟: {closest_clock}MHz, 分频系数: {divisor}, 分频后的频率: {closest_clock / divisor}MHz") else: print(f"无法找到完美,最近的父时钟: {closest_clock}, 分频系数: {divisor}, 分频后的频率: {closest_clock / divisor}MHz") print("请修改分频系数表 clk_tbl 中 HV 分频系数为: {LCD_IF_HV, " + hex(divisor) + ", 1, 1, 0}") -

回复: V851se的u-boot引导发布在 V Series

会,启动介质优先级描述了每个介质被选择为启动介质的可能性。BROM 首先读取具有最高优先级的介质的 boot0。如果该介质不存在或存在任何问题,BROM 将尝试下一个介质。否则,该介质将被选择为启动介质。

具体可以查看手册GPIO Boot Select表格

-

回复: V851s使用spi nand启动不了 VFS: Cannot open root device "ubi0_4" or unknown-block(0,0): error -2发布在 V Series

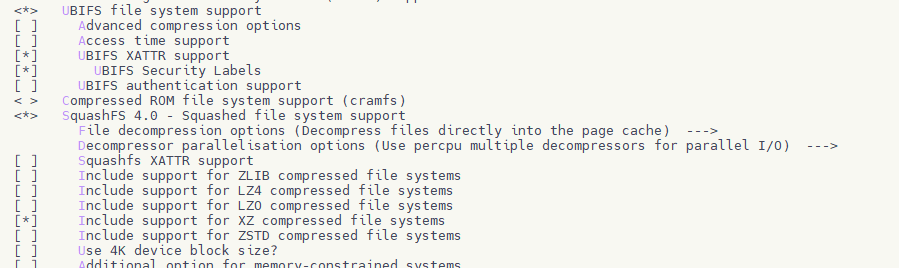

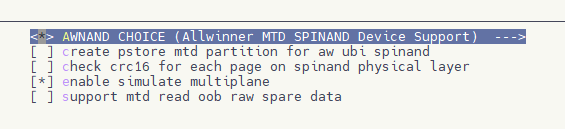

重点:rootfstype=squashfs

v851s/configs/xxx/env.cfg

#kernel command arguments earlyprintk=sunxi-uart,0x02500000 initcall_debug=0 console=ttyS0,115200 nand_root=/dev/ubiblock0_4 mmc_root=/dev/mmcblk0p4 nor_root=/dev/mtdblock3 init=/init rdinit=/rdinit loglevel=8 coherent_pool=32K #reserve_list=30M@64M,78M@128M,200M@512M mac= wifi_mac= bt_mac= specialstr= root_partition=rootfs mtd_name=sys rootfstype=squashfs #set kernel cmdline if boot.img or recovery.img has no cmdline we will use this setargs_nor=setenv bootargs earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${nor_root} rootwait init=${init} rdinit=${rdinit} partitions=${partitions} cma=${cma} coherent_pool=${coherent_pool} ion_carveout_list=${reserve_list} setargs_nand=setenv bootargs earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} ubi.mtd=${mtd_name} root=${nand_root} rootfstype=${rootfstype} rootwait init=${init} rdinit=${rdinit} partitions=${partitions} cma=${cma} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} selinux=${selinux} specialstr=${specialstr} coherent_pool=${coherent_pool} ion_carveout_list=${reserve_list} setargs_nand_ubi=setenv bootargs ubi.mtd=${mtd_name} ubi.block=0,${root_partition} earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${nand_root} rootfstype=${rootfstype} init=${init} partitions=${partitions} cma=${cma} snum=${snum} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} specialstr=${specialstr} gpt=1 setargs_mmc=setenv bootargs earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${mmc_root} rootwait init=${init} partitions=${partitions} cma=${cma} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} selinux=${selinux} specialstr=${specialstr} coherent_pool=${coherent_pool} ion_carveout_list=${reserve_list} #nand command syntax: sunxi_flash read address partition_name read_bytes #0x4007f800 = 0x40080000(kernel entry) - 0x800(boot.img header 2k) boot_partition=boot boot_normal=sunxi_flash read 44800000 ${boot_partition};bootm 44800000 boot_recovery=sunxi_flash read 44800000 extend;bootm 44800000 boot_fastboot=fastboot #recovery key recovery_key_value_max=0x13 recovery_key_value_min=0x10 #fastboot key fastboot_key_value_max=0x8 fastboot_key_value_min=0x2 #uboot system env config bootdelay=1 #default bootcmd, will change at runtime according to key press #default nand boot bootcmd=run setargs_nand boot_normal #verify the kernel verify=N -

回复: 请教关于V821的SPI的问题-设备树发布在 V Series

-

821是 SPIF 控制器连接 NOR Flash,开启SPIF是由uboot动态修改设备树,SPIF是针对NOR,NAND存储器件优化的控制器,读取性能是普通SPI的一倍以上

-

是的

-

-

回复: R128 打包失败 merge_full_rtos_img_failed发布在 MR Series

@cai_yp 分区参数错误,只打包了UDISK分区,但是UDISK是自动生成的分区

32356+0 records in 32356+0 records out 8283136 bytes (8.3 MB) copied, 0.0394041 s, 210 MB/s this is not a partition key update mbr file ok ----------------mbr convert to gpt start--------------------- out: sunxi_gpt_nor.fex source: sunxi_mbr_nor.fex input_logic_offset: 256 input_flash_size: 16M gpt partition entry crc32 = 0x618ebc8 gpt header crc32 = 0x4fdf09e2 GPT----part num 10--- gpt_entry: 128 gpt_header: 92 GPT:env : 120 127 GPT:env-redund : 128 12f GPT:arm-lpsram : 130 a8f GPT:rv-lpsram : a90 1a2f GPT:dsp-hpsram : 1a30 206f GPT:rtos-xip : 2070 33f7 GPT:arm-b : 33f8 3d57 GPT:config : 3d58 3d77 GPT:settings : 3d78 3db7 GPT:UDISK : 3db8 7fff update gpt file ok ----------------mbr convert to gpt end--------------------- boot0: boot0_spinor.fex redund boot0: boot0_spinor.fex mbr: sunxi_gpt_nor.fex partition: sys_partition_nor.bin UDISK_partition_size: 16968 sector outfile: rtos_16Mnor.bin logic_start: 128K total_image_size: 16M load file: boot0_spinor.fex ok load file: sunxi_gpt_nor.fex ok load file: boot0_spinor.fex ok support redund boot0 at 0x10000 load file: sys_partition_nor.bin ok part name=env file name:env.fex part size:8 sector load file: env.fex ok part name=env-redund file name:env.fex part size:8 sector load file: env.fex ok part name=arm-lpsram file name:rtos_arm.fex part size:2400 sector load file: rtos_arm.fex ok part name=rv-lpsram file name:rtos_riscv.fex part size:4000 sector load file: rtos_riscv.fex ok part name=dsp-hpsram file name:rtos_dsp.fex part size:1600 sector load file: rtos_dsp.fex ok part name=rtos-xip file name:rtos_xip_rv.fex part size:5000 sector load file: rtos_xip_rv.fex ok part name=arm-b file name:etf.fex part size:2400 sector load file: etf.fex ok part name=config file name:config.fex part size:32 sector load file: config.fex ok part name=settings part size:64 sector part name=UDISK file name:data_udisk.fex load file: data_udisk.fex ok partname: UDISK this is not a partition key merge_package ok -

回复: MR536 SDK MR536_V1.1直接编译和打包后烧录全志MR536 evk(黄色),报错如下: Unable to handle kernel paging request at virtual address 0000000000040008发布在 MR Series

Unable to handle kernel paging request at virtual address 0000000000040008

看看内核代码rb_next附近,有非法地址访问

-

回复: A133編譯kernel 遇到error trying to exec cc1: execvp : No such file or directory发布在 其它全志芯片讨论区

环境没有安装

Ubuntu 22.04 / 20.04

- 更新软件源,更新系统软件包

sudo apt-get update sudo apt-get upgrade -y- 安装开发依赖

sudo apt-get install build-essential subversion git libncurses5-dev zlib1g-dev gawk flex bison quilt libssl-dev xsltproc libxml-parser-perl mercurial bzr ecj cvs unzip lsof- 安装相关工具

sudo apt-get install kconfig-frontends android-tools-mkbootimg python2 libpython3-dev- 增加架构支持

sudo dpkg --add-architecture i386 sudo apt-get update- 安装支持包

sudo apt install gcc-multilib sudo apt install libc6:i386 libstdc++6:i386 lib32z1Ubuntu 18.04

- 更新软件源,更新系统软件包

sudo apt-get update sudo apt-get upgrade -y- 安装开发依赖

sudo apt-get install build-essential subversion git libncurses5-dev zlib1g-dev gawk flex bison quilt libssl-dev xsltproc libxml-parser-perl mercurial bzr ecj cvs unzip lsof- 安装相关工具

sudo apt-get install android-tools-mkbootimg libpython3-dev- 增加架构支持

sudo dpkg --add-architecture i386 sudo apt-get update- 安装支持包

sudo apt install gcc-multilib sudo apt install libc6:i386 libstdc++6:i386 lib32z1Arch Linux / Manjaro

- 更新软件源,更新系统软件包

pacman -Syyuu- 安装开发依赖

pacman -S --needed base-devel autoconf automake bash binutils bison bzip2 fakeroot file findutils flex gawk gcc gettext git grep groff gzip time unzip util-linux wget which zlib asciidoc help2man intltool perl-extutils-makemaker swig- 安装相关工具

pacman -S --needed libelf libtool libxslt m4 make ncurses openssl patch pkgconf python rsync sed texinfo- 增加架构支持

pacman -S --needed multilib-develCentOS / Fedora / openEuler

sudo dnf --setopt install_weak_deps=False --skip-broken install bash-completion bzip2 gcc gcc-c++ git make ncurses-devel patch rsync tar unzip wget which diffutils python2 python3 perl-base perl-Data-Dumper perl-File-Compare perl-File-Copy perl-FindBin perl-Thread-Queue glibc.i686openSUSE

sudo zypper install --no-recommends asciidoc bash bc binutils bzip2 fastjar flex gawk gcc -

回复: SyterKit 启动 T527 失败发布在 T Series

修改设备树,增加memory和chosen