已刷新文档内容,感谢反馈

awwwwa 发布的帖子

-

回复: v821的udc 出错,dma初始化失败,gadget切换功能有问题发布在 Linux

bsp/drivers/usb/sunxi_usb/udc/sunxi_udc.c

unsigned static int g_dma_enable = 0; -

回复: 编译T113固件的时候总是出现改错误发布在 T Series

@z2500abc 在 编译T113固件的时候总是出现改错误 中说:

eyesee-mpp

eyesee-mpp 错误无视即可,这个软件包不支持T113平台,是其他平台使用的

第二个错误需要提供完整的日志,这一部分不包括真正的错误

-

回复: T507启动卡启动失败,用的是供应商提供的镜像,但是启动显示找不到内核镜像是为什么?发布在 T Series

@xiduanya 这个是依赖SDK支持的,SDK如果不支持生成卡启动分区表则不行

-

回复: T507启动卡启动失败,用的是供应商提供的镜像,但是启动显示找不到内核镜像是为什么?发布在 T Series

GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid GPT *** part_get_info_efi: *** Using Backup GPT *** GUID Partition Table Header signature is wrong: 0x0 != 0x5452415020494645 part_get_info_efi: *** ERROR: Invalid GPT *** part_get_info_efi: *** Using Backup GPT *** Wrong Image Format for bootm command这个镜像应该是不支持启动卡,需要用量产卡生成gpt分区,启动卡这里GPT都是空的

-

回复: MR536 SDK MR536_V1.1直接编译和打包后烧录全志MR536 evk(黄色),报错如下: Unable to handle kernel paging request at virtual address 0000000000040008发布在 MR Series

Unable to handle kernel paging request at virtual address 0000000000040008

看看内核代码rb_next附近,有非法地址访问

-

回复: 为什么tina liunx打包后没有分区表?烧录时报错?不支持的镜像?发布在 Linux

如果想从SD/TF卡启动,记得选择启动卡

想将其转换为标准镜像?用其他软件烧录?

可以参考这里

https://bbs.aw-ol.com/topic/1365/openixcard-在-linux-系统刷写全志镜像到-sd-卡

https://github.com/YuzukiTsuru/OpenixCard -

回复: OpenixCard - 在 Linux 系统刷写全志镜像到 SD 卡发布在 编译和烧写问题专区

@yunyisa 自制的固件无法打包成全志的镜像,只能由SDK生成,全志镜像有专有的封装格式,不仅仅是地址偏移

-

回复: 对R128模块原理图的疑问发布在 A Series

1.AVCC是芯片内部电源供电吗?datasheet上没说。 -- 是芯片内部供电

2.EXT-LDO33不是内部LDO输出么,为什么要外接3V3? -- 外接DCDC降低功耗,减少发热

3.为什么VDD-SYS1与VDD-SYS2、VDD-AON与VDD12-PSM外部要接在一起。 -- R128各模块供电采用内部 PMU

我猜应该有一本完整的硬件设计指南可以解答问题,只是没公开。 -- https://r128.docs.aw-ol.com/hardware/hardware_design/ -

回复: 程序运行之后告诉我有错误发布在 V Series

@aaa0557li V851S 不能刷 V851SE,不能刷V851S3,ic cant match axp, please check... 是检查固件与芯片型号不对应,另外检查编译环境是否有其他变量导致编译出来的固件检查不匹配,如果都没问题建议重装一个干净的SDK不要与其他SDK复用同一个环境

-

回复: ISP_ERR发布在 V Series

@nimadibaj

[ISP_ERR]isp_ctx_save_exit, line: 109,open /mnt/isp0_1920_1088_30_0_ctx_saved.bin failed, err:Read-only file system.

这个是暂存isp参数,由于没有文件所以打开失败。可以无视。真正的问题是Got signal 11, exiting ...,程序出现段错误,请检查指针使用

-

回复: 搭建开发环境,出现问了了,总是报fatal: cannot obtain manifest https://sdk.aw-ol.com/git_repo/V853Tina_Open/manifest.git发布在 V Series

- 执行命令设置全局保存密码

git config --global credential.helper store- 执行命令输入密码

git clone https://sdk.aw-ol.com/git_repo/V853Tina_Open/manifest.git- 使用repo拉取sdk

repo init -u https://sdk.aw-ol.com/git_repo/V853Tina_Open/manifest.git -b master -m tina-v853-open.xml由于repo更新,目前不支持通过repo输入密码,请先使用git命令输入保存密码

-

回复: T113S3双路 dual lvds驱动不起来发布在 T Series

uboot和dtsi里面添加dual link IO的配置

demo: lvds2link_pins_a: lvds2link@0 { allwinner,pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", "PD8", "PD9", "PD6", "PD7", \ "PD10", "PD11", "PD12", "PD13", "PD14", "PD15", "PD18", "PD19", "PD16", "PD17"; allwinner,pname = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", "PD8", "PD9", "PD6", "PD7", \ "PD10", "PD11", "PD12", "PD13", "PD14", "PD15", "PD18", "PD19", "PD16", "PD17"; allwinner,function = "lvds1"; allwinner,muxsel = <3>; allwinner,drive = <3>; allwinner,pull = <0>; }; lvds2link_pins_b: lvds2link@1 { allwinner,pins = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", "PD8", "PD9", "PD6", "PD7", \ "PD10", "PD11", "PD12", "PD13", "PD14", "PD15", "PD18", "PD19", "PD16", "PD17"; allwinner,pname = "PD0", "PD1", "PD2", "PD3", "PD4", "PD5", "PD8", "PD9", "PD6", "PD7", \ "PD10", "PD11", "PD12", "PD13", "PD14", "PD15", "PD18", "PD19", "PD16", "PD17"; allwinner,function = "lvds1_suspend"; allwinner,muxsel = <7>; allwinner,drive = <3>; allwinner,pull = <0>; };dts中 修改为lvds dual link模式,并引用dtsi里配好的dual link IO

&lcd0{ ... lcd_lvds_if = <1>; ... ... pinctrl-0 = <&lvds2link_pins_a>; pinctrl-1 = <&lvds2link_pins_b>; ... }其他和single link的配置方法无异,如果点不亮请检查时序

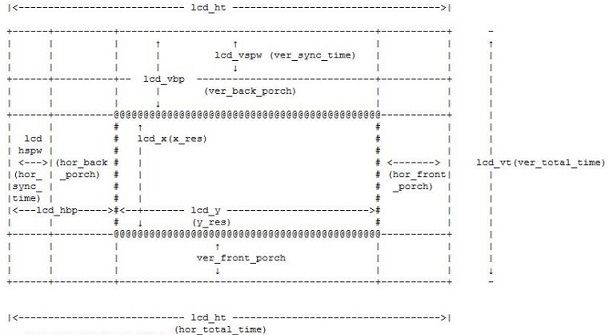

这里看到dclk配置是80

但是手册需求的是54

这里提供一套1920x720的时序作为参考

&lcd0 { lcd_used = <1>; lcd_driver_name = "default_lcd"; lcd_backlight = <50>; lcd_if = <3>; lcd_x = <1920>; lcd_y = <720>; lcd_width = <150>; lcd_height = <94>; lcd_dclk_freq = <94>; lcd_pwm_used = <1>; lcd_pwm_ch = <3>; lcd_pwm_freq = <50000>; lcd_pwm_pol = <1>; lcd_pwm_max_limit = <255>; lcd_hbp = <64>; lcd_ht = <2064>; lcd_hspw = <20>; lcd_vbp = <30>; lcd_vt = <760>; lcd_vspw = <10>; lcd_lvds_if = <1>; lcd_lvds_colordepth = <0>; lcd_lvds_mode = <0>; lcd_frm = <1>; lcd_hv_clk_phase = <0>; lcd_hv_sync_polarity= <0>; lcd_gamma_en = <0>; lcd_bright_curve_en = <0>; lcd_cmap_en = <0>; deu_mode = <0>; lcdgamma4iep = <22>; smart_color = <90>; pinctrl-0 = <&lvds2link_pins_a>; pinctrl-1 = <&lvds2link_pins_b>; }; -

回复: V853 和 V853S NPU算力差了0.2,这个0.2在具体应用上会有明显的性能差距吗?主要用来做目标检测,静态场景。发布在 V Series

根据具体的模型和需求的规格来看,实际感觉差不多

-

回复: V851s使用spi nand启动不了 VFS: Cannot open root device "ubi0_4" or unknown-block(0,0): error -2发布在 V Series

重点:rootfstype=squashfs

v851s/configs/xxx/env.cfg

#kernel command arguments earlyprintk=sunxi-uart,0x02500000 initcall_debug=0 console=ttyS0,115200 nand_root=/dev/ubiblock0_4 mmc_root=/dev/mmcblk0p4 nor_root=/dev/mtdblock3 init=/init rdinit=/rdinit loglevel=8 coherent_pool=32K #reserve_list=30M@64M,78M@128M,200M@512M mac= wifi_mac= bt_mac= specialstr= root_partition=rootfs mtd_name=sys rootfstype=squashfs #set kernel cmdline if boot.img or recovery.img has no cmdline we will use this setargs_nor=setenv bootargs earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${nor_root} rootwait init=${init} rdinit=${rdinit} partitions=${partitions} cma=${cma} coherent_pool=${coherent_pool} ion_carveout_list=${reserve_list} setargs_nand=setenv bootargs earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} ubi.mtd=${mtd_name} root=${nand_root} rootfstype=${rootfstype} rootwait init=${init} rdinit=${rdinit} partitions=${partitions} cma=${cma} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} selinux=${selinux} specialstr=${specialstr} coherent_pool=${coherent_pool} ion_carveout_list=${reserve_list} setargs_nand_ubi=setenv bootargs ubi.mtd=${mtd_name} ubi.block=0,${root_partition} earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${nand_root} rootfstype=${rootfstype} init=${init} partitions=${partitions} cma=${cma} snum=${snum} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} specialstr=${specialstr} gpt=1 setargs_mmc=setenv bootargs earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${mmc_root} rootwait init=${init} partitions=${partitions} cma=${cma} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} selinux=${selinux} specialstr=${specialstr} coherent_pool=${coherent_pool} ion_carveout_list=${reserve_list} #nand command syntax: sunxi_flash read address partition_name read_bytes #0x4007f800 = 0x40080000(kernel entry) - 0x800(boot.img header 2k) boot_partition=boot boot_normal=sunxi_flash read 44800000 ${boot_partition};bootm 44800000 boot_recovery=sunxi_flash read 44800000 extend;bootm 44800000 boot_fastboot=fastboot #recovery key recovery_key_value_max=0x13 recovery_key_value_min=0x10 #fastboot key fastboot_key_value_max=0x8 fastboot_key_value_min=0x2 #uboot system env config bootdelay=1 #default bootcmd, will change at runtime according to key press #default nand boot bootcmd=run setargs_nand boot_normal #verify the kernel verify=N -

回复: V851se的u-boot引导发布在 V Series

会,启动介质优先级描述了每个介质被选择为启动介质的可能性。BROM 首先读取具有最高优先级的介质的 boot0。如果该介质不存在或存在任何问题,BROM 将尝试下一个介质。否则,该介质将被选择为启动介质。

具体可以查看手册GPIO Boot Select表格

-

回复: R128 Vector支持发布在 A Series

@layzerlee 需要修改编译参数加上v扩展支持

CONFIG_TOOLCHAIN_MACH_FLAGS="-mcmodel=medany -mabi=lp64dv -march=rv64gcxvthead" CONFIG_TOOLCHAIN_FPU_ABI="-march=rv64gcxvthead" -

回复: V853S mipi LCD显示驱动调试,colorbar显示异常发布在 V Series

dclk过高,屏幕分屏了?

这里提供一个py脚本计算分频系数,这里对应的是HV屏,DSI也可以参考def find_closest_clock(target_clock, clock_list): clock_list = sorted(clock_list) low, high = 0, len(clock_list) - 1 closest = clock_list[low] while low <= high: mid = (low + high) // 2 if clock_list[mid] < target_clock: low = mid + 1 elif clock_list[mid] > target_clock: high = mid - 1 else: return clock_list[mid] if abs(clock_list[mid] - target_clock) < abs(closest - target_clock): closest = clock_list[mid] return closest def calculate_divisor(clock_need, clock_list, min_divisor=6): is_perfect = True for i in clock_list: for j in range(0, 255): if (clock_need * j) == i: closest_clock = i divisor = j return closest_clock, divisor, is_perfect is_perfect = False closest_clock = find_closest_clock(clock_need, clock_list) if closest_clock == 0: return None, None, None divisor = closest_clock // clock_need if divisor < min_divisor: min_diff = float('inf') best_clock = None for clock in clock_list: if clock >= clock_need * min_divisor: current_divisor = clock // clock_need if current_divisor < min_divisor: continue diff = abs(clock - clock_need * current_divisor) if diff < min_diff: min_diff = diff best_clock = clock if best_clock is not None: return best_clock, best_clock // clock_need, is_perfect return closest_clock, divisor, is_perfect clock_list = [ 408, 420, 432, 444, 456, 468, 480, 492, 504, 516, 528, 540, 552, 564, 576, 588, 600, 612, 624, 636, 648, 660, 672, 684, 696, 708, 720, 732, 744, 756, 768, 780, 792, 804, 816, 828, 840, 852, 864, 876, 888, 900, 912, 924, 936, 948, 960, 972, 984, 996, 1008, 1020, 1032, 1044, 1056, 1068, 1080, 1092, 1104, 1116, 1128, 1140, 1152, 1164, 1176, 1188, 1200, 1212, 1224, 1236, 1248, 1260, 1272, 1284, 1296, 1308, 1320, 1332, 1344, 1356, 1368, 1380, 1392, 1404, 1416, 1428, 1440, 1452, 1464, 1476, 1488, 1500, 1512, 1524, 1536, 1548, 1560, 1572, 1584, 1596, 1608, 1620, 1632, 1644, 1656, 1668, 1680, 1692 ] clock_need = int(input("请输入需要的时钟(MHz): ")) closest_clock, divisor, is_perfect = calculate_divisor(clock_need, clock_list) if is_perfect: print(f"父时钟: {closest_clock}MHz, 分频系数: {divisor}, 分频后的频率: {closest_clock / divisor}MHz") else: print(f"无法找到完美,最近的父时钟: {closest_clock}, 分频系数: {divisor}, 分频后的频率: {closest_clock / divisor}MHz") print("请修改分频系数表 clk_tbl 中 HV 分频系数为: {LCD_IF_HV, " + hex(divisor) + ", 1, 1, 0}") -

回复: 打补丁后,编译失败发布在 V Series

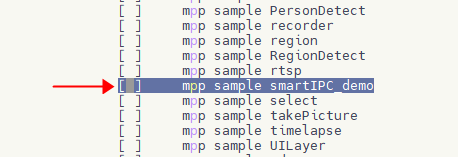

第一次编译时候请取消勾选

mpp sample smartIPC_demo编译完成一次之后使用 cleanmpp && mkmpp 来编译mpp相关demo。

-

回复: R329代码里找不到BOOT0启动打印“HELLO! BOOT0 is starting!”发布在 其它全志芯片讨论区

@yimu163com 在 R329代码里找不到BOOT0启动打印“HELLO! BOOT0 is starting!” 中说:

Binary file ./device/config/chips/r329/bin/boot0_nand_sun50iw11p1.bin matches

Binary file ./device/config/chips/r329/bin/sboot_sun50iw11p1.bin matches

Binary file ./device/config/chips/r329/bin/boot0_spinor_sun50iw11p1.bin matches

Binary file ./device/config/chips/r329/bin/boot0_sdcard_sun50iw11p1.bin matches在这几个bin里,BOOT0不开源

-

回复: T527 使用 DRM 驱动 edp 屏幕发布在 T Series

DSI

dsi1_backlight: backlight0 { compatible = "pwm-backlight"; status = "okay"; brightness-levels = < 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189 190 191 192 193 194 195 196 197 198 199 200 201 202 203 204 205 206 207 208 209 210 211 212 213 214 215 216 217 218 219 220 221 222 223 224 225 226 227 228 229 230 231 232 233 234 235 236 237 238 239 240 241 242 243 244 245 246 247 248 249 250 251 252 253 254 255>; default-brightness-level = <200>; enable-gpios = <&pio PH 18 GPIO_ACTIVE_HIGH>; pwms = <&pwm0 0 50000 0>; }; &de { chn_cfg_mode = <3>; status = "okay"; }; &vo0 { status = "okay"; }; &dlcd1 { status = "okay"; }; &dsi1 { status = "okay"; pinctrl-0 = <&dsi1_4lane_pins_a>; pinctrl-1 = <&dsi1_4lane_pins_b>; pinctrl-names = "active","sleep"; ports { dsi1_out: port@1{ reg = <1>; dsi_out_panel: endpoint { remote-endpoint = <&panel_in>; }; }; }; panel: panel@0 { compatible = "panel-dsi"; status = "okay"; reg = <0>; power0-supply = <®_cldo4>; power1-supply = <®_cldo1>; reset-gpios = <&pio PD 22 GPIO_ACTIVE_HIGH>; //reset backlight = <&dsi1_backlight>; dsi,flags = <MIPI_DSI_MODE_VIDEO>; dsi,lanes = <4>; dsi,format = <0>; panel-init-sequence = [ 15 00 02 E0 00 15 00 02 E1 93 15 00 02 E2 65 15 00 02 E3 F8 15 00 02 80 03 15 00 02 E0 01 15 00 02 00 00 15 00 02 01 25 15 00 02 03 00 15 00 02 04 30 15 00 02 0C 74 15 00 02 17 00 15 00 02 18 C7 15 00 02 19 01 15 00 02 1A 00 15 00 02 1B C7 15 00 02 1C 01 15 00 02 24 FE 15 00 02 37 19 15 00 02 35 28 15 00 02 38 05 15 00 02 39 08 15 00 02 3A 12 15 00 02 3C 7E 15 00 02 3D FF 15 00 02 3E FF 15 00 02 3F 7F 15 00 02 40 06 15 00 02 41 A0 15 00 02 43 1E 15 00 02 44 0B 15 00 02 55 02 15 00 02 57 6A 15 00 02 59 0A 15 00 02 5A 2E 15 00 02 5B 1A 15 00 02 5C 15 15 00 02 5D 7F 15 00 02 5E 61 15 00 02 5F 50 15 00 02 60 43 15 00 02 61 3F 15 00 02 62 32 15 00 02 63 35 15 00 02 64 1F 15 00 02 65 38 15 00 02 66 36 15 00 02 67 36 15 00 02 68 54 15 00 02 69 42 15 00 02 6A 48 15 00 02 6B 39 15 00 02 6C 34 15 00 02 6D 26 15 00 02 6E 14 15 00 02 6F 02 15 00 02 70 7F 15 00 02 71 61 15 00 02 72 50 15 00 02 73 43 15 00 02 74 3F 15 00 02 75 32 15 00 02 76 35 15 00 02 77 1F 15 00 02 78 38 15 00 02 79 36 15 00 02 7A 36 15 00 02 7B 54 15 00 02 7C 42 15 00 02 7D 48 15 00 02 7E 39 15 00 02 7F 34 15 00 02 80 26 15 00 02 81 14 15 00 02 82 02 15 00 02 E0 02 15 00 02 00 52 15 00 02 01 5F 15 00 02 02 5F 15 00 02 03 50 15 00 02 04 77 15 00 02 05 57 15 00 02 06 5F 15 00 02 07 4E 15 00 02 08 4C 15 00 02 09 5F 15 00 02 0A 4A 15 00 02 0B 48 15 00 02 0C 5F 15 00 02 0D 46 15 00 02 0E 44 15 00 02 0F 40 15 00 02 10 5F 15 00 02 11 5F 15 00 02 12 5F 15 00 02 13 5F 15 00 02 14 5F 15 00 02 15 5F 15 00 02 16 53 15 00 02 17 5F 15 00 02 18 5F 15 00 02 19 51 15 00 02 1A 77 15 00 02 1B 57 15 00 02 1C 5F 15 00 02 1D 4F 15 00 02 1E 4D 15 00 02 1F 5F 15 00 02 20 4B 15 00 02 21 49 15 00 02 22 5F 15 00 02 23 47 15 00 02 24 45 15 00 02 25 41 15 00 02 26 5F 15 00 02 27 5F 15 00 02 28 5F 15 00 02 29 5F 15 00 02 2A 5F 15 00 02 2B 5F 15 00 02 2C 13 15 00 02 2D 1F 15 00 02 2E 1F 15 00 02 2F 01 15 00 02 30 17 15 00 02 31 17 15 00 02 32 1F 15 00 02 33 0D 15 00 02 34 0F 15 00 02 35 1F 15 00 02 36 05 15 00 02 37 07 15 00 02 38 1F 15 00 02 39 09 15 00 02 3A 0B 15 00 02 3B 11 15 00 02 3C 1F 15 00 02 3D 1F 15 00 02 3E 1F 15 00 02 3F 1F 15 00 02 40 1F 15 00 02 41 1F 15 00 02 42 12 15 00 02 43 1F 15 00 02 44 1F 15 00 02 45 00 15 00 02 46 17 15 00 02 47 17 15 00 02 48 1F 15 00 02 49 0C 15 00 02 4A 0E 15 00 02 4B 1F 15 00 02 4C 04 15 00 02 4D 06 15 00 02 4E 1F 15 00 02 4F 08 15 00 02 50 0A 15 00 02 51 10 15 00 02 52 1F 15 00 02 53 1F 15 00 02 54 1F 15 00 02 55 1F 15 00 02 56 1F 15 00 02 57 1F 15 00 02 58 40 15 00 02 5B 10 15 00 02 5C 06 15 00 02 5D 40 15 00 02 5E 00 15 00 02 5F 00 15 00 02 60 40 15 00 02 61 03 15 00 02 62 04 15 00 02 63 6C 15 00 02 64 6C 15 00 02 65 75 15 00 02 66 08 15 00 02 67 B4 15 00 02 68 08 15 00 02 69 6C 15 00 02 6A 6C 15 00 02 6B 0C 15 00 02 6D 00 15 00 02 6E 00 15 00 02 6F 88 15 00 02 75 BB 15 00 02 76 00 15 00 02 77 05 15 00 02 78 2A 15 00 02 E0 04 15 00 02 37 58 15 00 02 00 0E 15 00 02 02 B3 15 00 02 09 61 15 00 02 0E 48 15 00 02 E0 00 05 32 01 11 05 05 01 29 15 32 02 35 00 ]; panel-exit-sequence = [ 05 14 01 28 05 50 01 10 ]; display-timings { native-mode = <&dsi1_timing0>; dsi1_timing0: timing0 { clock-frequency = <68215200>; hback-porch = <20>; hactive = <800>; hfront-porch = <20>; hsync-len = <20>; vback-porch = <8>; vactive = <1280>; vfront-porch = <30>; vsync-len = <4>; }; }; port { panel_in: endpoint { remote-endpoint = <&dsi_out_panel>; }; }; }; }; &dsi0combophy { status = "disabled"; }; &dsi1combophy { status = "okay"; }; -

回复: 只用的全志的板子,怎么才能往rootfs中添加文件发布在 Linux

target/allwinner/t113-nezha/base-files

target/allwinner/t113-nezha/busybox-init-base-files根据选择的overlay方式而定

-

回复: TLT113-MiniEVM 启动引导失败:E/TC:0 0 check_hardware_info:90 hardware check error1发布在 创龙科技专区

@scanli 请问设备是否刷写过安全启动?如果没有刷写过但是出现这个情况可以做以下临时修改

在

device/config/chips/t113_i/configs/default/修改boot_package.cfg删除optee.fex行在

lichee/linux-5.4/arch/arm/boot/dts/sun8iw20p1.dtsi中注释psci { compatible = "arm,psci-1.0"; method = "smc"; };前往

lichee/linux-5.4/arch/arm/mach-sunxi/platsmp.c加入static int sun8i_t113_smp_boot_secondary(unsigned int cpu, struct task_struct *idle) { u32 reg; void __iomem *cpucfg_membase = ioremap(0x09010000, 0x10); void __iomem *cpuexec_membase[] = {ioremap(0x070005C4, 0x10),ioremap(0x070005C8, 0x10)}; if (cpu != 1) return 0; spin_lock(&cpu_lock); writel(__pa_symbol(secondary_startup), cpuexec_membase[cpu]); reg = readl(cpucfg_membase); writel(reg | BIT(cpu), cpucfg_membase); spin_unlock(&cpu_lock); return 0; } static const struct smp_operations sun8i_t113_smp_ops __initconst = { .smp_boot_secondary = sun8i_t113_smp_boot_secondary, }; CPU_METHOD_OF_DECLARE(sun8i_t113_smp, "allwinner,sun8iw20p1", &sun8i_t113_smp_ops);注意这只是临时修改跳过检查,之后最好使用创龙提供的虚拟机复现看看会不会也出现这个问题

-

回复: rs485的设备树怎么修改发布在 其它全志芯片讨论区

DE和RO为使能管脚。DE为低电平、RE为低电平时为接收;DE为高电平、RE为高电平时为发送;RO和DI为数据管脚。RO为接收,DI为发送;因此我们经常将DE和RE直接连接,用一个IO口控制。

需要添加以下三个成员:

- sunxi,uart-rs485

- 0:485模式关闭

- 1:485模式使能

- sunxi,uart-485fl

- 0:485 gpio管脚数值为0时表示发送状态

- 1:485 gpio管脚数值为1时表示发送状态

- sunxi,uart-485oe-gpios

- 用于外部转换芯片使能信号的gpio引脚,GPIO_ACTIVE_HIGH含义为默认为高电平

示例:

uart1: uart@2500400 { ... status = "okay"; //添加以下三行 sunxi,uart-rs485 = <1>; sunxi,uart-485fl = <1>; sunxi,uart-485oe-gpios = <&pio PG 8 GPIO_ACTIVE_HIGH>; };A40I 5.10 内核:

uart5_pins_a: uart5_pins@0 { pins = "PH6", "PH7"; function = "uart5"; }; uart5_pins_b: uart5_pins@1 { pins = "PH6", "PH7"; function = "gpio_in"; }; &uart5 { pinctrl-names = "default", "sleep"; pinctrl-0 = <&uart5_pins_a>; pinctrl-1 = <&uart5_pins_b>; rs485-enable = <0>; rs485-mode = <0>; /* defalut 0:rx 1:tx */ rs485-mode-pin = <&pio PH 8 GPIO_ACTIVE_LOW>; status = "disabled"; }; - sunxi,uart-rs485

-

回复: mboot和mkernel可以代替make命令吗发布在 编译和烧写问题专区

mboot,mkernel是编译boot和内核的,并没有编译rootfs,如果已经编译好了rootfs则可以代替,如果没有编译rootfs则需要make来编译rootfs

-

回复: TLT113-MiniEVM 启动引导失败:E/TC:0 0 check_hardware_info:90 hardware check error1发布在 创龙科技专区

make distclean后删除out文件夹重新编译看看

-

回复: R128-S2 使用外部1.2VDC的情况下, 如何关闭 APP_LDO发布在 MR Series

@maplerian 开启外部DCDC, POWERTCTL会自动关闭APP_LDO,这个是一个硬件行为

-

回复: R128-S2 使用外部1.2VDC的情况下, 如何关闭 APP_LDO发布在 MR Series

@maplerian 在深度休眠下,内部APP_LDO由PWRCTRL硬件关闭,且深度休眠下GPIO控制器断电不会启用DCDC,唤醒时由PWRCTRL硬件逻辑开启内部APP_LDO,然后启用GPIO控制器拉高启用外部DCDC,启用后自动切换到外部DCDC供电

-

回复: R128-S2 使用外部1.2VDC的情况下, 如何关闭 APP_LDO发布在 MR Series

APP_LDO的关闭是PWRCTRL的硬件行为,由配置处理器

deep sleep mode后,CPU进入WFI触发PWRCTRL的该行为,无寄存器配置。PWRCTRL仅支持手动关闭DSP。外挂DCDC可以通过读取LDO_EN寄存器查看目前是否开启内部LDO -

回复: XR829在T113-i芯片+原SDK基础上蓝牙有成功过的伙伴吗?发布在 Wireless & Analog Series

@chrisvista 如果配置UART适配8250规范则是AS0,如果是sunxi-uart规范则是S0

-

回复: XR829在T113-i芯片+原SDK基础上蓝牙有成功过的伙伴吗?发布在 Wireless & Analog Series

测试 AWOL 开源的 Tina SDK + T113-S3 板子,

hciattach -n ttyS1 xradio正常 -

回复: T113 ledc 驱动bug 长时间运行以后出错发布在 MR Series

“sunxi_ledc_irq_handler()1313 - wait time is more than 600000 ns,going to reset ledc and drop this operation!”

看代码,此打印的意思是ledc传输数据后超过600ms才进入中断处理,看上去是被别的高优先级中断抢占

-

回复: Tina-T113 openWrt 新增软件包,选中menuconfig后,编译报错,makefile完全就是按照sdk里QT对应的makefile来写的发布在 MR Series

Makefile:68: *** missing separator. Stop.

这个错误通常表示在 Makefile 的第 68 行或附近存在语法错误。Makefile 中使用的规则必须遵循严格的缩进规范,通常是使用 Tab 键进行缩进,而不是空格。

请检查 Makefile 第 68 行附近的代码,确保每个规则的命令部分都以 Tab 键开头,并且规则名称和命令之间使用冒号(:)分隔。此外,还需要确认 Makefile 的每一行都是使用相同的缩进方式,要么都是 Tab,要么都是空格,不要混用。

-

回复: D1-H哪吒开发板HDMI默认可以使用吗发布在 MR Series

默认HDMI不开,需要命令开启

cd /sys/kernel/debug/dispdbg echo disp0 > name; echo switch1 > command; echo 4 10 0 0 0x4 0x101 0 0 0 8 > param; echo 1 > start;