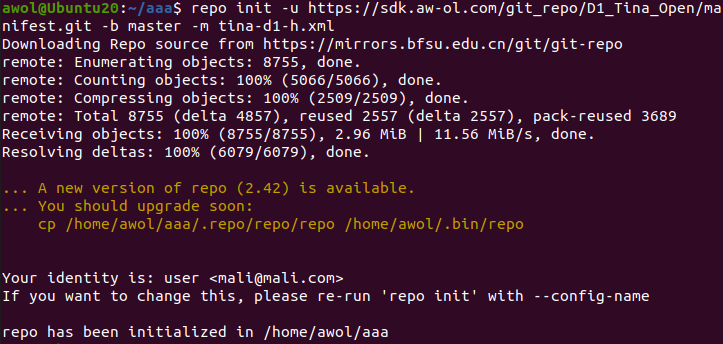

@damiaa 现在是新版本平台了,直接拿awol账号下载,免去再注册一个平台的麻烦:https://d1.docs.aw-ol.com/study/study_3getsdktoc/

awwwwa 发布的帖子

-

回复: 个人开发者如何获取D1、D1s的 SDK?需要签NDA吗?发布在 代码下载问题专区

-

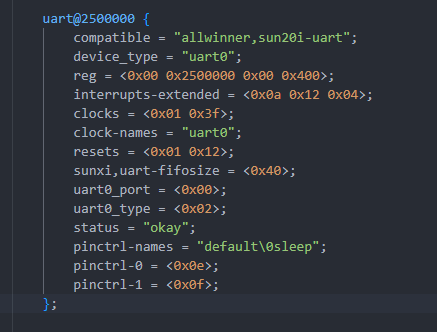

回复: 修改了linux-5.4/board.dts的uart0部分,但是烧写到板子上面没有生效发布在 编译和烧写问题专区

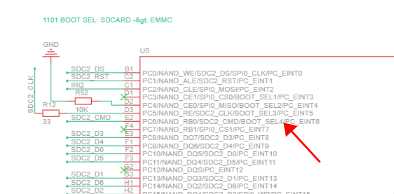

@zifeiyu 那为什么pack打包到固件的有,刷进去就没了,是不是刷写到emmc但是TF卡启动了?

-

回复: 修改了linux-5.4/board.dts的uart0部分,但是烧写到板子上面没有生效发布在 编译和烧写问题专区

@zifeiyu 那你得检查下是不是刷错固件了,或者没有运行pack命令刷的还是老版本

-

回复: 修改了linux-5.4/board.dts的uart0部分,但是烧写到板子上面没有生效发布在 编译和烧写问题专区

@zifeiyu 那看一下合成的dts的uart情况,out/t113-100ask/image/.sunxi.dts

-

回复: 修改了linux-5.4/board.dts的uart0部分,但是烧写到板子上面没有生效发布在 编译和烧写问题专区

也可以看一下

out/t113-100ask/image/.sunxi.dts文件的

-

回复: 修改了linux-5.4/board.dts的uart0部分,但是烧写到板子上面没有生效发布在 编译和烧写问题专区

@zifeiyu uboot阶段fdt print看看有没有okay,另外图没发上来

-

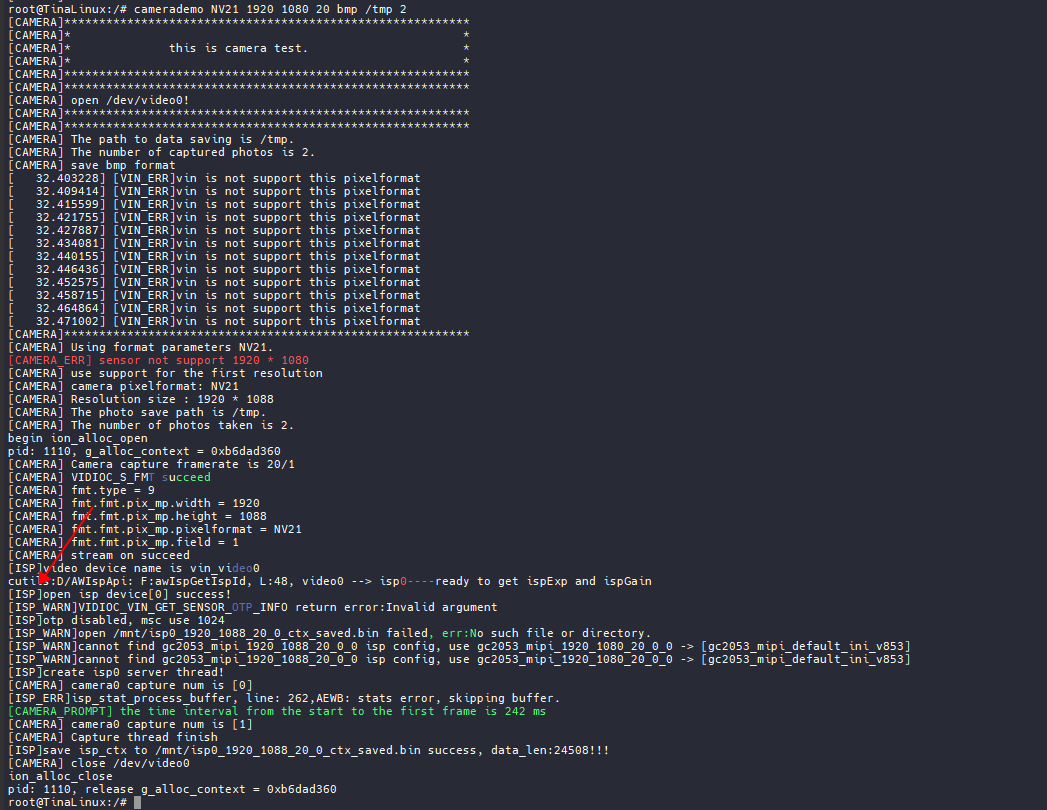

回复: v851 使用sample_rtsp 报ISP_ERR发布在 V Series

检查使用的SDK是哪一个版本,目前awol的Tina 5.0不支持sample_rtsp,这个demo适配的是Tina 4.0,需要向代理获取支持

-

回复: tina linux SDL1.2.15发布在 爱搞机专区

@wj8331585 支持,出现段错误可以编译一个gdb进去看看哪里错了

测试代码:

w = 1920; h = 1080; bpp = 32; SDL_Init( SDL_INIT_EVERYTHING ); SDL_SetVideoMode( w,h, bpp, SDL_HWSURFACE|SDL_DOUBLEBUF ); -

回复: V853SDK:奇怪的帧缓冲区操作发布在 V Series

@alb702 add your layer and cat that file see what layer you configured

-

回复: R128 WIFI AP模式获取连接设备的IP地址的问题发布在 A Series

AP的数据是在 lwip 的 static struct etharp_entry arp_table[ARP_TABLE_SIZE]; 中维护

#if LWIP_XR_IMPL ip4_addr_t* etharp_get_ip_from_mac(struct eth_addr *ethaddr) { int i; ip4_addr_t* ip_ret = NULL; LWIP_ASSERT("ethaddr != NULL", ethaddr != NULL); for (i = 0; i < ARP_TABLE_SIZE; i++) { if (memcmp(ethaddr, &arp_table[i].ethaddr, sizeof(struct eth_addr)) == 0) { ip_ret = &arp_table[i].ipaddr; break; } } return ip_ret; } #endif -

回复: V853SDK:奇怪的帧缓冲区操作发布在 V Series

@alb702 try to

cat /sys/class/disp/disp/attr/sysempty:

root@TinaLinux:/# cat /sys/class/disp/disp/attr/sys screen 0: de_rate 300000000 hz, ref_fps:62 mgr0: 800x1280 fmt[rgb] cs[0x204] range[full] eotf[0x4] bits[8bits] err[0] force_sync[0] unblank direct_show[false] iommu[1] dmabuf: cache[0] cache max[0] umap skip[0] umap skip max[52] lcd output backlight(100) fps:62.1 800x1280 err:0 skip:228 irq:2786 vsync:0 vsync_skip:0 BUF enable ch[1] lyr[0] z[16] prem[N] a[pixel 255] fmt[ 0] fb[ 800,1280; 800,1280; 800,1280] crop[ 0, 0, 800,1280] frame[ 0, 0, 800,1280] addr[ff800000, 0, 0] flags[0x 0] trd[0,0] depth[ 0]add layer

cat /sys/class/disp/disp/attr/sys screen 0: de_rate 300000000 hz, ref_fps:62 mgr0: 800x1280 fmt[rgb] cs[0x204] range[full] eotf[0x4] bits[8bits] err[0] force_sync[0] unblank direct_show[false] iommu[1] dmabuf: cache[0] cache max[0] umap skip[0] umap skip max[52] lcd output backlight(100) fps:62.1 800x1280 err:933 skip:228 irq:6815 vsync:0 vsync_skip:0 COLOR enable ch[0] lyr[0] z[16] prem[N] a[pixel 0] fmt[ 0] fb[ 0, 0; 0, 0; 0, 0] crop[ 0, 0, 200,1280] frame[ 0, 0, 200,1280] addr[ffff0000, 0, 0] flags[0x 0] trd[0,0] depth[ 0] COLOR enable ch[0] lyr[1] z[16] prem[N] a[pixel 0] fmt[ 0] fb[ 0, 0; 0, 0; 0, 0] crop[ 200, 0, 200,1280] frame[ 200, 0, 200,1280] addr[ff00ff00, 0, 0] flags[0x 0] trd[0,0] depth[ 0] COLOR enable ch[0] lyr[2] z[16] prem[N] a[pixel 0] fmt[ 0] fb[ 0, 0; 0, 0; 0, 0] crop[ 400, 0, 200,1280] frame[ 400, 0, 200,1280] addr[ff0000ff, 0, 0] flags[0x 0] trd[0,0] depth[ 0] COLOR enable ch[0] lyr[3] z[16] prem[N] a[pixel 0] fmt[ 0] fb[ 0, 0; 0, 0; 0, 0] crop[ 600, 0, 200,1280] frame[ 600, 0, 200,1280] addr[ffffff00, 0, 0] flags[0x 0] trd[0,0] depth[ 0] BUF enable ch[1] lyr[0] z[16] prem[N] a[pixel 255] fmt[ 0] fb[ 800,1280; 800,1280; 800,1280] crop[ 0, 0, 800,1280] frame[ 0, 0, 800,1280] addr[ff800000, 0, 0] flags[0x 0] trd[0,0] depth[ 0] -

回复: 全H616启动,GPIO和eFuse启动选择,是在哪里设置的发布在 H/F/TV Series

@fleieng 如果烧录了eFuse会写eFuse标志位,就是eFuse选择,如果没烧eFuse,则是GPIO选择,芯片出厂默认是GPIO选择

-

回复: V853SDK:奇怪的帧缓冲区操作发布在 V Series

try to use english to describe, the translate I can't understand.

-

回复: T113-S3解码1080P视频花屏,set scaledown视频画面不动发布在 MR Series

package/allwinner/tina_multimedia/tplayer/configs/t113_linux_cedarx.conf

检查是否使用

video lbc mode, is_lossy and rc_en如果配置了设置 0 0 0

########### paramter ############ [paramter] start_play_cache_video_frame_num = 4 start_play_cache_size = 8 # KB cache_buffer_size = 10240 # KB cache_buffer_size_live = 10240 # KB start_play_cache_time = 5 # Second max_start_play_chache_size = 512 # KB max_cache_buffer_size = 10240 # KB max_http_stream_buf_size = 2048 #KB # the number of audio stream cached before decoding. max_audio_stream_frame_num = 128 # see comment in player.cpp av_sync_duration = 0 # millisecond # picture num for modules pic_4list_num = 2 pic_4di_num = 0 pic_4rotate_num = 0 pic_4smooth_num = 2 # picture format: mb32/nv21/nv12/nv # deinterlace format deinterlace_fmt = nv12 # video decoder output picture format vd_output_fmt = nv21 # video lbc mode, is_lossy and rc_en vd_lbc_mode = 2 vd_lbc_is_lossy = 1 vd_lbc_rc_en = 0 # gpu align stride values: 16/32 # mali 400mp2 32bit gpu_align_bitwidth = 32 # if value 1 : send 3-frames black-pic to GPU # SP: switch Program #black_pic_4_SP = 0 # compensate for av vsync compensate_vsync = 4 #use transform module to rotate the video. notice:only r18/r58/r40 support transform module tr_rotate_flag = 0 #1 means rotate,0 means not rotate tr_rotate_degree = 0 #0 means the degree is 0, 90 means the degree is 90,180 means the degree is 180, 270 means the degree is 270 #use g2d module to rotate the video. notice:F133/R528 g2d_rotate_degree = 0 #the max width and height of video in this product,which need align 64 hold_last_picture_with = 1920 hold_last_picture_height = 1088 #The first frame decoded will be used for quick display. show_1th_frame_quick = 1 # log will output if level >= log_level #VERBOSE = 2, #DEBUG = 3, #INFO = 4, #WARNING = 5, #ERROR = 6, log_level = 6 # define platform for ve phy addr offset platform = t113 # scaledown large video(>=1080p) or not,0:means not scaledown,1:means scaledown scaledown_large_video_flag = 0 #use ion buf in streamManager.c , 0:means not use ion buf,1:means use ion buf use_ion_buf_flag = 0 ########### plugin ############## # 1. audio decoder plugin [adecoder-0] comment = aac_adecoder id = adecoder.aac lib = libaw_aacdec.so [adecoder-1] comment = alac_adecoder id = adecoder.alac lib = libaw_alacdec.so [adecoder-2] comment = amr_adecoder id = adecoder.amr lib = libaw_amrdec.so [adecoder-3] comment = ape_adecoder id = adecoder.ape lib = libaw_apedec.so [adecoder-4] comment = flac_adecoder id = adecoder.flac lib = libaw_flacdec.so [adecoder-5] comment = mp3_adecoder id = adecoder.mp3 lib = libaw_mp3dec.so [adecoder-6] comment = ogg_adecoder id = adecoder.ogg lib = libaw_oggdec.so [adecoder-7] comment = wav_adecoder id = adecoder.wav lib = libaw_wavdec.so [adecoder-8] comment = atrc_adecoder id = adecoder.atrc lib = libaw_atrcdec.so [adecoder-9] comment = ra_adecoder id = adecoder.ra lib = libaw_radec.so [adecoder-10] comment = dsd_adecoder id = adecoder.dsd lib = libaw_dsddec.so [adecoder-11] comment = g729_adecoder id = adecoder.g729 lib = libaw_g729dec.so [adecoder-12] comment = opus_adecoder id = adecoder.opus lib = libaw_opusdec.so # 2. video decoder plugin [vdecoder-0] comment = h264_vdecoder id = vdecoder.h264 lib = libawh264.so init = CedarPluginVDInit [vdecoder-1] comment = mjpeg_vdecoder id = vdecoder.mjpeg lib = libawmjpeg.so init = CedarPluginVDInit [vdecoder-2] comment = mpeg2_vdecoder id = vdecoder.mpeg2 lib = libawmpeg2.so init = CedarPluginVDInit [vdecoder-3] comment = mpeg4base_vdecoder id = vdecoder.mpeg4base lib = libawmpeg4base.so init = CedarPluginVDInit [vdecoder-4] comment = mpeg4dx_vdecoder id = vdecoder.mpeg4dx lib = libawmpeg4dx.so init = CedarPluginVDInit reference = vdecoder.mpeg4base [vdecoder-5] comment = mpeg4h263_vdecoder id = vdecoder.mpeg4h263 lib = libawmpeg4h263.so init = CedarPluginVDInit reference = vdecoder.mpeg4base [vdecoder-6] comment = mpeg4normal_vdecoder id = vdecoder.mpeg4normal lib = libawmpeg4normal.so init = CedarPluginVDInit reference = vdecoder.mpeg4base [vdecoder-7] comment = wmv3_vdecoder id = vdecoder.wmv3 lib = libawwmv3.so init = CedarPluginVDInit [vdecoder-8] comment = h265_vdecoder id = vdecoder.h265 lib = libawh265.so init = CedarPluginVDInit # 3. external plugin #[plugin-0] #comment = rtp_plugin #id = rtp #lib = librtp.so -

回复: T113pro使用tina sdk无法将模块自动拷进rootfs发布在 编译和烧写问题专区

检查一下modules的配置

define KernelPackage/net-broadcom SUBMENU:=$(WIRELESS_MENU) DEPENDS:= +ap6256-firmware +@PACKAGE_broadcom-rftest TITLE:=broadcom(ap6256...) support FILES:=$(LINUX_DIR)/drivers/net/wireless/bcmdhd/bcmdhd.ko KCONFIG:=\ CONFIG_BCMDHD=m \ CONFIG_BCMDHD_SDIO=y \ CONFIG_BCMDHD_OOB=y \ CONFIG_BCMDHD_FW_PATH="/etc/firmware/fw_bcmdhd.bin" \ CONFIG_BCMDHD_NVRAM_PATH="/etc/firmware/nvram.txt" \ CONFIG_BCMDHD_SDIO=y \ CONFIG_SUNXI_RFKILL=y \ CONFIG_MMC=y \ CONFIG_PWRSEQ_EMMC=y \ CONFIG_PWRSEQ_SIMPLE=y \ CONFIG_MMC_SUNXI=y \ CONFIG_MMC_SUNXI_V4P1X=y \ CONFIG_MMC_SUNXI_V4P00X=y \ CONFIG_MMC_SUNXI_V4P10X=y \ CONFIG_MMC_SUNXI_V4P5X=y \ CONFIG_MMC_SUNXI_V5P3X=y \ AUTOLOAD:=$(call AutoProbe,bcmdhd,1) endef define KernelPackage/net-broadcom/description Kernel modules for Broadcom AP6256... support endef $(eval $(call KernelPackage,net-broadcom)) -

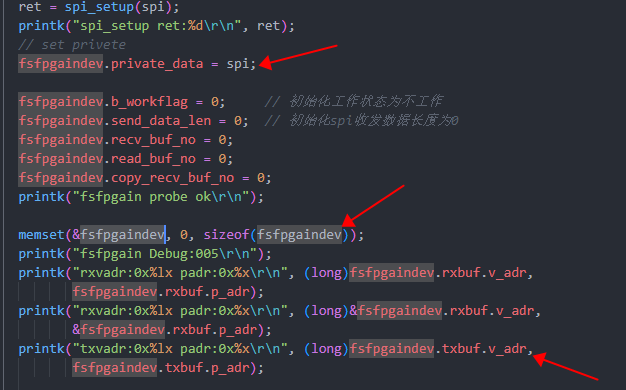

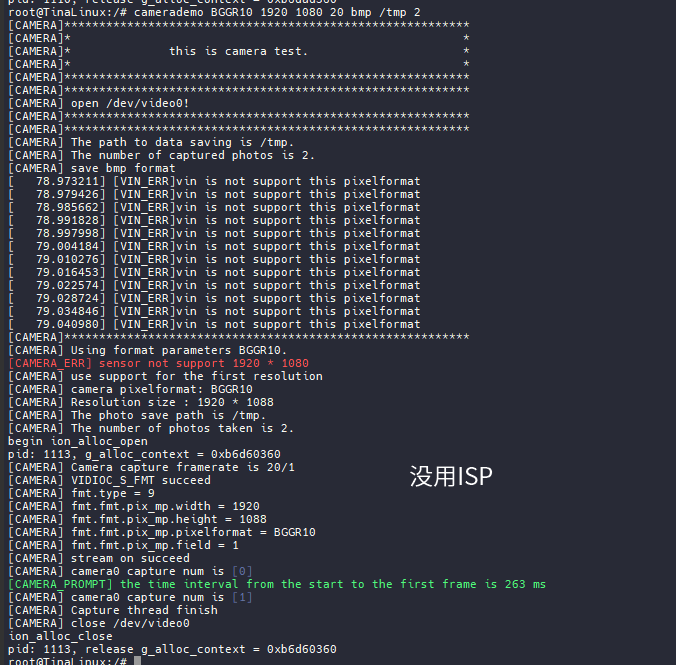

回复: D1s DMA驱动Ledc 问题发布在 MR Series

使用dma模式搬运数据,需要打上如下补丁:

ledc在dma模式的代码存在问题,已修复该问题,ledc的dma通道之前也没有支持,需要添加上

diff --git a/hal/source/dma/platform/dma-sun8iw20.h b/hal/source/dma/platform/dma-sun8iw20.h index 2140014..fc5c72e 100644 --- a/hal/source/dma/platform/dma-sun8iw20.h +++ b/hal/source/dma/platform/dma-sun8iw20.h @@ -136,6 +136,7 @@ #define DRQDST_OTG_EP3 32 #define DRQDST_OTG_EP4 33 #define DRQDST_OTG_EP5 34 +#define DRQDST_LEDC 42 #define DRQDST_TWI0_TX 43 #define DRQDST_TWI1_TX 44 #define DRQDST_TWI2_TX 45 diff --git a/hal/source/ledc/hal_ledc.c b/hal/source/ledc/hal_ledc.c index 5499452..ddf471f 100755 --- a/hal/source/ledc/hal_ledc.c +++ b/hal/source/ledc/hal_ledc.c @@ -20,9 +20,10 @@ #define led_err(fmt, args...) printf("%s()%d - "fmt, __func__, __LINE__, ##args) #define LEDC_PIN_SLEEP 0 +#define LEDC_DMA_BUF_SIZE 4096 struct ledc_config ledc_config = { - .led_count = 3, + .led_count = 1024, .reset_ns = 84, .t1h_ns = 800, .t1l_ns = 450, @@ -37,6 +38,7 @@ static unsigned long base_addr = LEDC_BASE; struct sunxi_dma_chan *dma_chan; struct sunxi_led *led; +static uint8_t already_init; static hal_irqreturn_t sunxi_ledc_irq_handler(void *dummy) { @@ -448,15 +450,16 @@ void hal_ledc_dma_callback(void *para) { - printf("dma callback\n"); + ledc_info("dma transfer end\n"); } -void hal_ledc_trans_data(struct ledc_config *ledc) +int hal_ledc_trans_data(struct ledc_config *ledc) { - int i; + int i, ret; unsigned long int size; unsigned int mask = 0; struct dma_slave_config slave_config; + unsigned int const *buf = ledc->data; mask = LEDC_TRANS_FINISH_INT_EN | LEDC_WAITDATA_TIMEOUT_INT_EN | LEDC_FIFO_OVERFLOW_INT_EN | LEDC_GLOBAL_INT_EN; @@ -480,23 +483,32 @@ ledc_reset_en(); size = ledc->length * 4; + if (size <= LEDC_DMA_BUF_SIZE) { + memcpy(ledc->align_dma_buf, buf, ledc->length); + buf = ledc->align_dma_buf; + } - hal_dcache_clean((unsigned long)ledc->data, sizeof(ledc->data)); + hal_dcache_clean((unsigned long)buf, size); slave_config.direction = DMA_MEM_TO_DEV; - slave_config.src_addr = (unsigned long)(ledc->data); + slave_config.src_addr = (unsigned long)buf; slave_config.dst_addr = (uint32_t)(base_addr + LEDC_DATA_REG); slave_config.src_addr_width = DMA_SLAVE_BUSWIDTH_4_BYTES; slave_config.dst_addr_width = DMA_SLAVE_BUSWIDTH_4_BYTES; - slave_config.src_maxburst = DMA_SLAVE_BURST_16; - slave_config.dst_maxburst = DMA_SLAVE_BURST_16; + slave_config.src_maxburst = DMA_SLAVE_BURST_4; + slave_config.dst_maxburst = DMA_SLAVE_BURST_4; slave_config.slave_id = sunxi_slave_id(DRQDST_LEDC, DRQSRC_SDRAM); - hal_dma_slave_config(dma_chan, &slave_config); + ret = hal_dma_slave_config(dma_chan, &slave_config); + if (ret) { + led_err("dma slave config failed\n"); + return -1; + } - hal_dma_prep_device(dma_chan, slave_config.dst_addr, slave_config.src_addr, size, DMA_MEM_TO_DEV); - - //dma_chan->callback = ledc_dma_callback; - hal_dma_start(dma_chan); + ret = hal_dma_prep_device(dma_chan, slave_config.dst_addr, slave_config.src_addr, size, DMA_MEM_TO_DEV); + if (ret) { + led_err("dma prep device failed\n"); + return -1; + } hal_ledc_set_time(ledc); ledc_set_output_mode(ledc->output_mode); @@ -504,7 +516,15 @@ ledc_set_dma_mode(); ledc_enable_irq(mask); ledc_enable(); + + dma_chan->callback = hal_ledc_dma_callback; + ret = hal_dma_start(dma_chan); + if (ret) { + led_err("dma start trans failed\n"); + return -1; + } } + return 0; } void hal_ledc_clear_all_irq(void) @@ -598,6 +618,14 @@ int hal_ledc_init(void) { + if (already_init) { + already_init++; + ledc_info("ledc has been inited, return ok\n"); + return 0; + } + + int ret, i; + ledc_info("hal_led_init\n"); led = malloc(sizeof(struct sunxi_led)); @@ -611,25 +639,40 @@ led->config.data = malloc(sizeof(unsigned int) * led->config.led_count); if (NULL == led->config.data) { led_err("sunxi led config data malloc err\n"); - goto err1; + goto err0; } + for(i = 0;i < led->config.led_count;i++) + led->config.data[i] = 0; if (ledc_clk_init()) { led_err("ledc clk init failed \n"); + goto err1; } if (ledc_pinctrl_init()) { led_err("ledc pinctrl init failed \n"); + goto err2; } - hal_dma_chan_request(&dma_chan); + ret = hal_dma_chan_request(&dma_chan); + if (ret == HAL_DMA_CHAN_STATUS_BUSY) + { + led_err("request dma_chan failed\n"); + goto err3; + } + led->config.align_dma_buf = dma_alloc_coherent(LEDC_DMA_BUF_SIZE); + if (!led->config.align_dma_buf) + { + led_err("alloc dma memory failed\n"); + goto err4; + } if (hal_request_irq(SUNXI_IRQ_LEDC, sunxi_ledc_irq_handler, "ledc", led) < 0) { led_err("ledc request irq failed \n"); - goto errirq; + goto err5; } hal_enable_irq(SUNXI_IRQ_LEDC); @@ -638,13 +681,22 @@ pm_devops_register(&pm_ledc); #endif + already_init++; ledc_info("hal_led_init success\n"); return 0; -errirq: - free(led->config.data); +err5: + dma_free_coherent(led->config.align_dma_buf); +err4: + hal_dma_chan_free(dma_chan); +err3: + ledc_pinctrl_exit(); +err2: + ledc_clk_exit(); err1: + free(led->config.data); +err0: free(led); return -1; @@ -652,27 +704,35 @@ void hal_ledc_deinit(void) { + if (already_init > 0) { + if (--already_init == 0) { #ifdef CONFIG_COMPONENTS_PM - pm_devops_unregister(&pm_ledc); + pm_devops_unregister(&pm_ledc); #endif - hal_disable_irq(SUNXI_IRQ_LEDC); - hal_free_irq(SUNXI_IRQ_LEDC); - hal_dma_chan_free(dma_chan); - ledc_pinctrl_exit(); - ledc_clk_exit(); - free(led->config.data); - free(led); + hal_disable_irq(SUNXI_IRQ_LEDC); + hal_free_irq(SUNXI_IRQ_LEDC); + dma_free_coherent(led->config.align_dma_buf); + hal_dma_chan_free(dma_chan); + ledc_pinctrl_exit(); + ledc_clk_exit(); + free(led->config.data); + free(led); + } + } } int sunxi_set_all_led(unsigned int brightness) { - int i; + int i, ret; led->config.length = led->config.led_count; for(i = 0;i < led->config.led_count;i++) led->config.data[i] = brightness; - hal_ledc_trans_data(&led->config); + ret = hal_ledc_trans_data(&led->config); + if (ret) { + led_err("ledc trans data error\n"); + } return 0; } @@ -680,6 +740,7 @@ int sunxi_set_led_brightness(int led_num, unsigned int brightness) { u32 reg_val; + int i, ret; if (NULL == led) { led_err("err : ledc is not init\n"); @@ -691,10 +752,16 @@ return -1; } - led->config.length = 1; + led->config.length = led_num; led->config.data[led_num-1] = brightness; - hal_ledc_trans_data(&led->config); + for (i = 0; i < led_num; i++) + ledc_info("the %d led light is %u\n", i + 1, led->config.data[i]); + + ret = hal_ledc_trans_data(&led->config); + if (ret) { + led_err("ledc trans data error\n"); + } reg_val = hal_ledc_get_irq_status(); ledc_info("ledc interrupt status reg is %x", reg_val); diff --git a/hal/source/ledc/platform_ledc.h b/hal/source/ledc/platform_ledc.h index 39f6933..2fa9c38 100644 --- a/hal/source/ledc/platform_ledc.h +++ b/hal/source/ledc/platform_ledc.h @@ -33,8 +33,6 @@ #ifndef __PLATFORM_LEDC_H__ #define __PLATFORM_LEDC_H__ -#define DRQDST_LEDC 43 - #if defined(CONFIG_ARCH_SUN8IW18P1) #include "platform/ledc_sun8iw18.h" #endif diff --git a/hal/test/ledc/test_ledc.c b/hal/test/ledc/test_ledc.c index 1ade796..79694c0 100755 --- a/hal/test/ledc/test_ledc.c +++ b/hal/test/ledc/test_ledc.c @@ -20,6 +20,7 @@ int ledc_test(int argc, char **argv) { int brightness = 0; + int led_num; printf("========LEDC TEST========\n"); @@ -32,9 +33,14 @@ return 0; } - brightness = atoi(argv[2]); + led_num = atoi(argv[1]); + if (led_num < 1 || led_num > 1024) + { + printf("The led_num you entered should be between 1 and 1024\n"); + } + brightness = atoi(argv[3]); - switch(argv[1][0]) + switch(argv[2][0]) { case 'R' : brightness <<= 8; break; case 'G' : brightness <<= 16; break; @@ -43,7 +49,8 @@ return -1; } - sunxi_set_led_brightness(1, brightness); + sunxi_set_led_brightness(led_num, brightness); + printf("led is %d\n", led_num); printf("brightness is %d\n", brightness); return 0; diff --git a/include/hal/sunxi_hal_ledc.h b/include/hal/sunxi_hal_ledc.h index a386338..e5a70d1 100644 --- a/include/hal/sunxi_hal_ledc.h +++ b/include/hal/sunxi_hal_ledc.h @@ -43,6 +43,7 @@ unsigned long long wait_time1_ns; unsigned int wait_data_time_ns; char *output_mode; + unsigned int *align_dma_buf; unsigned int *data; unsigned int length; }; @@ -86,7 +87,7 @@ int hal_ledc_init(void); void hal_ledc_deinit(void); -void hal_ledc_trans_data(struct ledc_config *ledc); +int hal_ledc_trans_data(struct ledc_config *ledc); void hal_ledc_clear_all_irq(void); unsigned int hal_ledc_get_irq_status(void); void hal_ledc_dma_callback(void *para);DMA下 LED 颜色异常

diff --git a/hal/source/ledc/hal_ledc.c b/hal/source/ledc/hal_ledc.c index ddf471f4..8d818662 100755 --- a/hal/source/ledc/hal_ledc.c +++ b/hal/source/ledc/hal_ledc.c @@ -308,11 +308,15 @@ static void ledc_set_wait_data_time_ns(unsigned int wait_data_time_ns) hal_writel(reg_val, base_addr + LEDC_DATA_FINISH_CNT_REG); } +/* + * set the num of leds on the led-strip + * max support up to 1024 leds + */ static void ledc_set_length(unsigned int length) { unsigned int reg_val; - if (length == 0) + if (length == 0 || length > 1024) return; reg_val = hal_readl(base_addr + LEDC_CTRL_REG); @@ -721,12 +725,22 @@ void hal_ledc_deinit(void) } } -int sunxi_set_all_led(unsigned int brightness) +/* + * set the brightness of all the leds in led-strip to a uniform value + * @length: the num of leds on led-strip + * @brightness: the brightness data + */ +int sunxi_set_all_led(unsigned int length, unsigned int brightness) { int i, ret; - led->config.length = led->config.led_count; - for(i = 0;i < led->config.led_count;i++) + if (length > led->config.led_count) { + led_err("%d: max support 1024 leds\n", length); + return -1; + } + + led->config.length = length; + for(i = 0;i < led->length;i++) led->config.data[i] = brightness; ret = hal_ledc_trans_data(&led->config); @@ -737,7 +751,13 @@ int sunxi_set_all_led(unsigned int brightness) return 0; } -int sunxi_set_led_brightness(int led_num, unsigned int brightness) +/* + * set the brightness of each led on the led strip + * @length: all the num of leds on the led strip + * @led_num: the specified led that you want to set + * @brightness: the led brightness data + */ +int sunxi_set_led_brightness(unsigned int length, unsigned int led_num, unsigned int brightness) { u32 reg_val; int i, ret; @@ -747,12 +767,13 @@ int sunxi_set_led_brightness(int led_num, unsigned int brightness) return -1; } - if (led_num > led->config.led_count) { + if (length > led->config.led_count || len_num > length) { led_err("has not the %d led\n", led_num); return -1; } - led->config.length = led_num; + led->config.length = length; + /* set the specified led brightness, others set default brightness: 0x0*/ led->config.data[led_num-1] = brightness; for (i = 0; i < led_num; i++) -

回复: D1s ledc驱动代码bug,DMA模式无法使用发布在 MR Series

@leomini5 我这边没有D1s的板卡,在T113上测试通过,测试1024颗灯,这个可能是RV才有的bug?

-

回复: D1s ledc驱动代码bug,DMA模式无法使用发布在 MR Series

之前在其他帖发过DMA模式的patch,这里同步下

lichee/linux-5.4/drivers/leds/leds-sunxi.c

// SPDX-License-Identifier: GPL-2.0-only /* * drivers/leds/leds-sunxi.c - Allwinner RGB LED Driver * * Copyright (C) 2018 Allwinner Technology Limited. All rights reserved. * http://www.allwinnertech.com * *Author : Albert Yu <yuxyun@allwinnertech.com> * Lewis <liuyu@allwinnertech.com> * This program is free software; you can redistribute it and/or modify * it under the terms of the GNU General Public License version 2 as * published by the Free Software Foundation. * */ #include <linux/module.h> #include <linux/delay.h> #include <linux/leds.h> #include <linux/io.h> #include <linux/of.h> #include <linux/slab.h> #include <linux/clk.h> #include <linux/dmaengine.h> #include <linux/interrupt.h> #include <linux/platform_device.h> #include <linux/pinctrl/consumer.h> #include <linux/dma-mapping.h> #include <linux/debugfs.h> #include <linux/uaccess.h> #include <linux/delay.h> #include <linux/regulator/consumer.h> #include <linux/reset.h> #if IS_ENABLED(CONFIG_PM) #include <linux/pm.h> #endif #include "leds-sunxi.h" /* For debug */ #define LED_ERR(fmt, arg...) pr_err("%s()%d - "fmt, __func__, __LINE__, ##arg) #define dprintk(level_mask, fmt, arg...) \ do { \ if (unlikely(debug_mask & level_mask)) \ pr_warn("%s()%d - "fmt, __func__, __LINE__, ##arg); \ } while (0) static u32 debug_mask = 1; static struct sunxi_led *sunxi_led_global; static struct class *led_class; #define sunxi_slave_id(d, s) (((d)<<16) | (s)) /*For Driver */ static void led_dump_reg(struct sunxi_led *led, u32 offset, u32 len) { u32 i; u8 buf[64], cnt = 0; for (i = 0; i < len; i = i + REG_INTERVAL) { if (i%HEXADECIMAL == 0) cnt += sprintf(buf + cnt, "0x%08x: ", (u32)(led->res->start + offset + i)); cnt += sprintf(buf + cnt, "%08x ", readl(led->iomem_reg_base + offset + i)); if (i%HEXADECIMAL == REG_CL) { pr_warn("%s\n", buf); cnt = 0; } } } static void sunxi_clk_get(struct sunxi_led *led) { struct device *dev = led->dev; struct device_node *np = dev->of_node; led->clk_ledc = of_clk_get(np, 0); if (IS_ERR(led->clk_ledc)) LED_ERR("failed to get clk_ledc!\n"); led->clk_cpuapb = of_clk_get(np, 1); if (IS_ERR(led->clk_cpuapb)) LED_ERR("failed to get clk_cpuapb!\n"); } static void sunxi_clk_put(struct sunxi_led *led) { clk_put(led->clk_ledc); clk_put(led->clk_cpuapb); led->clk_ledc = NULL; led->clk_cpuapb = NULL; } static void sunxi_clk_enable(struct sunxi_led *led) { clk_prepare_enable(led->clk_ledc); clk_prepare_enable(led->clk_cpuapb); } static void sunxi_clk_disable(struct sunxi_led *led) { clk_disable_unprepare(led->clk_ledc); } static void sunxi_clk_init(struct sunxi_led *led) { sunxi_clk_get(led); sunxi_clk_enable(led); } static void sunxi_clk_deinit(struct sunxi_led *led) { sunxi_clk_disable(led); sunxi_clk_put(led); } static u32 sunxi_get_reg(int offset) { struct sunxi_led *led = sunxi_led_global; u32 value = ioread32(((u8 *)led->iomem_reg_base) + offset); return value; } static void sunxi_set_reg(int offset, u32 value) { struct sunxi_led *led = sunxi_led_global; iowrite32(value, ((u8 *)led->iomem_reg_base) + offset); } static inline void sunxi_set_reset_ns(struct sunxi_led *led) { u32 n, reg_val; u32 mask = 0x1FFF; u32 min = SUNXI_RESET_TIME_MIN_NS; u32 max = SUNXI_RESET_TIME_MAX_NS; if (led->reset_ns < min || led->reset_ns > max) { LED_ERR("invalid parameter, reset_ns should be %u-%u!\n", min, max); return; } n = (led->reset_ns - 42) / 42; reg_val = sunxi_get_reg(LED_RESET_TIMING_CTRL_REG_OFFSET); reg_val &= ~(mask << 16); reg_val |= (n << 16); sunxi_set_reg(LED_RESET_TIMING_CTRL_REG_OFFSET, reg_val); } static inline void sunxi_set_t1h_ns(struct sunxi_led *led) { u32 n, reg_val; u32 mask = 0x3F; u32 shift = 21; u32 min = SUNXI_T1H_MIN_NS; u32 max = SUNXI_T1H_MAX_NS; if (led->t1h_ns < min || led->t1h_ns > max) { LED_ERR("invalid parameter, t1h_ns should be %u-%u!\n", min, max); return; } n = (led->t1h_ns - 42) / 42; reg_val = sunxi_get_reg(LED_T01_TIMING_CTRL_REG_OFFSET); reg_val &= ~(mask << shift); reg_val |= n << shift; sunxi_set_reg(LED_T01_TIMING_CTRL_REG_OFFSET, reg_val); } static inline void sunxi_set_t1l_ns(struct sunxi_led *led) { u32 n, reg_val; u32 mask = 0x1F; u32 shift = 16; u32 min = SUNXI_T1L_MIN_NS; u32 max = SUNXI_T1L_MAX_NS; if (led->t1l_ns < min || led->t1l_ns > max) { LED_ERR("invalid parameter, t1l_ns should be %u-%u!\n", min, max); return; } n = (led->t1l_ns - 42) / 42; reg_val = sunxi_get_reg(LED_T01_TIMING_CTRL_REG_OFFSET); reg_val &= ~(mask << shift); reg_val |= n << shift; sunxi_set_reg(LED_T01_TIMING_CTRL_REG_OFFSET, reg_val); } static inline void sunxi_set_t0h_ns(struct sunxi_led *led) { u32 n, reg_val; u32 mask = 0x1F; u32 shift = 6; u32 min = SUNXI_T0H_MIN_NS; u32 max = SUNXI_T0H_MAX_NS; if (led->t0h_ns < min || led->t0h_ns > max) { LED_ERR("invalid parameter, t0h_ns should be %u-%u!\n", min, max); return; } n = (led->t0h_ns - 42) / 42; reg_val = sunxi_get_reg(LED_T01_TIMING_CTRL_REG_OFFSET); reg_val &= ~(mask << shift); reg_val |= n << shift; sunxi_set_reg(LED_T01_TIMING_CTRL_REG_OFFSET, reg_val); } static inline void sunxi_set_t0l_ns(struct sunxi_led *led) { u32 n, reg_val; u32 min = SUNXI_T0L_MIN_NS; u32 max = SUNXI_T0L_MAX_NS; if (led->t0l_ns < min || led->t0l_ns > max) { LED_ERR("invalid parameter, t0l_ns should be %u-%u!\n", min, max); return; } n = (led->t0l_ns - 42) / 42; reg_val = sunxi_get_reg(LED_T01_TIMING_CTRL_REG_OFFSET); reg_val &= ~0x3F; reg_val |= n; sunxi_set_reg(LED_T01_TIMING_CTRL_REG_OFFSET, reg_val); } static inline void sunxi_set_wait_time0_ns(struct sunxi_led *led) { u32 n, reg_val; u32 min = SUNXI_WAIT_TIME0_MIN_NS; u32 max = SUNXI_WAIT_TIME0_MAX_NS; if (led->wait_time0_ns < min || led->wait_time0_ns > max) { LED_ERR("invalid parameter, wait_time0_ns should be %u-%u!\n", min, max); return; } n = (led->wait_time0_ns - 42) / 42; reg_val = (1 << 8) | n; sunxi_set_reg(LEDC_WAIT_TIME0_CTRL_REG, reg_val); } static inline void sunxi_set_wait_time1_ns(struct sunxi_led *led) { unsigned long long tmp, max = SUNXI_WAIT_TIME1_MAX_NS; u32 min = SUNXI_WAIT_TIME1_MIN_NS; u32 n, reg_val; if (led->wait_time1_ns < min || led->wait_time1_ns > max) { LED_ERR("invalid parameter, wait_time1_ns should be %u-%llu!\n", min, max); return; } tmp = led->wait_time1_ns; n = div_u64(tmp, 42); n -= 1; reg_val = (1 << 31) | n; sunxi_set_reg(LEDC_WAIT_TIME1_CTRL_REG, reg_val); } static inline void sunxi_set_wait_data_time_ns(struct sunxi_led *led) { u32 min, max; #ifndef SUNXI_FPGA_LEDC u32 mask = 0x1FFF, shift = 16, reg_val = 0, n; #endif min = SUNXI_WAIT_DATA_TIME_MIN_NS; #ifdef SUNXI_FPGA_LEDC /* * For FPGA platforms, it is easy to meet wait data timeout for * the obvious latency of task which is because of less cpu cores * and lower cpu frequency compared with IC platforms, so here we * permit long enough time latency. */ max = SUNXI_WAIT_DATA_TIME_MAX_NS_FPGA; #else /* SUNXI_FPGA_LEDC */ max = SUNXI_WAIT_DATA_TIME_MAX_NS_IC; #endif /* SUNXI_FPGA_LEDC */ if (led->wait_data_time_ns < min || led->wait_data_time_ns > max) { LED_ERR("invalid parameter, wait_data_time_ns should be %u-%u!\n", min, max); return; } #ifndef SUNXI_FPGA_LEDC n = (led->wait_data_time_ns - 42) / 42; reg_val &= ~(mask << shift); reg_val |= (n << shift); sunxi_set_reg(LEDC_DATA_FINISH_CNT_REG_OFFSET, reg_val); #endif /* SUNXI_FPGA_LEDC */ } static void sunxi_ledc_set_time(struct sunxi_led *led) { sunxi_set_reset_ns(led); sunxi_set_t1h_ns(led); sunxi_set_t1l_ns(led); sunxi_set_t0h_ns(led); sunxi_set_t0l_ns(led); sunxi_set_wait_time0_ns(led); sunxi_set_wait_time1_ns(led); sunxi_set_wait_data_time_ns(led); } static void sunxi_ledc_set_length(struct sunxi_led *led) { u32 reg_val; u32 length = led->length; if (length == 0) return; if (length > led->led_count) return; reg_val = sunxi_get_reg(LEDC_CTRL_REG_OFFSET); reg_val &= ~(0x1FFF << 16); reg_val |= length << 16; sunxi_set_reg(LEDC_CTRL_REG_OFFSET, reg_val); reg_val = sunxi_get_reg(LED_RESET_TIMING_CTRL_REG_OFFSET); reg_val &= ~0x3FF; reg_val |= length - 1; sunxi_set_reg(LED_RESET_TIMING_CTRL_REG_OFFSET, reg_val); } static void sunxi_ledc_set_output_mode(struct sunxi_led *led, const char *str) { u32 val; u32 mask = 0x7; u32 shift = 6; u32 reg_val = sunxi_get_reg(LEDC_CTRL_REG_OFFSET); if (str != NULL) { if (!strncmp(str, "GRB", 3)) val = SUNXI_OUTPUT_GRB; else if (!strncmp(str, "GBR", 3)) val = SUNXI_OUTPUT_GBR; else if (!strncmp(str, "RGB", 3)) val = SUNXI_OUTPUT_RGB; else if (!strncmp(str, "RBG", 3)) val = SUNXI_OUTPUT_RBG; else if (!strncmp(str, "BGR", 3)) val = SUNXI_OUTPUT_BGR; else if (!strncmp(str, "BRG", 3)) val = SUNXI_OUTPUT_BRG; else return; } else { val = led->output_mode.val; } reg_val &= ~(mask << shift); reg_val |= val; sunxi_set_reg(LEDC_CTRL_REG_OFFSET, reg_val); if (str != NULL) { if (strncmp(str, led->output_mode.str, 3)) memcpy(led->output_mode.str, str, 3); } if (val != led->output_mode.val) led->output_mode.val = val; } static void sunxi_ledc_enable_irq(u32 mask) { u32 reg_val = 0; reg_val |= mask; sunxi_set_reg(LEDC_INT_CTRL_REG_OFFSET, reg_val); } static void sunxi_ledc_disable_irq(u32 mask) { u32 reg_val = 0; reg_val = sunxi_get_reg(LEDC_INT_CTRL_REG_OFFSET); reg_val &= ~mask; sunxi_set_reg(LEDC_INT_CTRL_REG_OFFSET, reg_val); } static inline void sunxi_ledc_enable(struct sunxi_led *led) { u32 reg_val; reg_val = sunxi_get_reg(LEDC_CTRL_REG_OFFSET); reg_val |= 1; sunxi_set_reg(LEDC_CTRL_REG_OFFSET, reg_val); } static inline void sunxi_ledc_reset(struct sunxi_led *led) { u32 reg_val = sunxi_get_reg(LEDC_CTRL_REG_OFFSET); sunxi_ledc_disable_irq(LEDC_TRANS_FINISH_INT_EN | LEDC_FIFO_CPUREQ_INT_EN | LEDC_WAITDATA_TIMEOUT_INT_EN | LEDC_FIFO_OVERFLOW_INT_EN | LEDC_GLOBAL_INT_EN); if (debug_mask & DEBUG_INFO2) { dprintk(DEBUG_INFO2, "dump reg:\n"); led_dump_reg(led, 0, 0x30); } reg_val |= 1 << 1; sunxi_set_reg(LEDC_CTRL_REG_OFFSET, reg_val); } #ifdef CONFIG_DEBUG_FS static ssize_t reset_ns_write(struct file *filp, const char __user *buf, size_t count, loff_t *offp) { int err; char buffer[64]; u32 min, max; unsigned long val; struct sunxi_led *led = sunxi_led_global; min = SUNXI_RESET_TIME_MIN_NS; max = SUNXI_RESET_TIME_MAX_NS; if (count >= sizeof(buffer)) goto err_out; if (copy_from_user(buffer, buf, count)) goto err_out; buffer[count] = '\0'; err = kstrtoul(buffer, 10, &val); if (err) goto err_out; if (val < min || val > max) goto err_out; led->reset_ns = val; sunxi_set_reset_ns(led); *offp += count; return count; err_out: LED_ERR("invalid parameter, reset_ns should be %u-%u!\n", min, max); return -EINVAL; } static ssize_t reset_ns_read(struct file *filp, char __user *buf, size_t count, loff_t *offp) { int r; char buffer[64]; struct sunxi_led *led = sunxi_led_global; r = snprintf(buffer, 64, "%u\n", led->reset_ns); return simple_read_from_buffer(buf, count, offp, buffer, r); } static const struct file_operations reset_ns_fops = { .owner = THIS_MODULE, .write = reset_ns_write, .read = reset_ns_read, }; static ssize_t t1h_ns_write(struct file *filp, const char __user *buf, size_t count, loff_t *offp) { int err; char buffer[64]; u32 min, max; unsigned long val; struct sunxi_led *led = sunxi_led_global; min = SUNXI_T1H_MIN_NS; max = SUNXI_T1H_MAX_NS; if (count >= sizeof(buffer)) return -EINVAL; if (copy_from_user(buffer, buf, count)) return -EFAULT; buffer[count] = '\0'; err = kstrtoul(buffer, 10, &val); if (err) return -EINVAL; if (val < min || val > max) goto err_out; led->t1h_ns = val; sunxi_set_t1h_ns(led); *offp += count; return count; err_out: LED_ERR("invalid parameter, t1h_ns should be %u-%u!\n", min, max); return -EINVAL; } static ssize_t t1h_ns_read(struct file *filp, char __user *buf, size_t count, loff_t *offp) { int r; char buffer[64]; struct sunxi_led *led = sunxi_led_global; r = snprintf(buffer, 64, "%u\n", led->t1h_ns); return simple_read_from_buffer(buf, count, offp, buffer, r); } static const struct file_operations t1h_ns_fops = { .owner = THIS_MODULE, .write = t1h_ns_write, .read = t1h_ns_read, }; static ssize_t t1l_ns_write(struct file *filp, const char __user *buf, size_t count, loff_t *offp) { int err; char buffer[64]; u32 min, max; unsigned long val; struct sunxi_led *led = sunxi_led_global; min = SUNXI_T1L_MIN_NS; max = SUNXI_T1L_MAX_NS; if (count >= sizeof(buffer)) goto err_out; if (copy_from_user(buffer, buf, count)) goto err_out; buffer[count] = '\0'; err = kstrtoul(buffer, 10, &val); if (err) goto err_out; if (val < min || val > max) goto err_out; led->t1l_ns = val; sunxi_set_t1l_ns(led); *offp += count; return count; err_out: LED_ERR("invalid parameter, t1l_ns should be %u-%u!\n", min, max); return -EINVAL; } static ssize_t t1l_ns_read(struct file *filp, char __user *buf, size_t count, loff_t *offp) { int r; char buffer[64]; struct sunxi_led *led = sunxi_led_global; r = snprintf(buffer, 64, "%u\n", led->t1l_ns); return simple_read_from_buffer(buf, count, offp, buffer, r); } static const struct file_operations t1l_ns_fops = { .owner = THIS_MODULE, .write = t1l_ns_write, .read = t1l_ns_read, }; static ssize_t t0h_ns_write(struct file *filp, const char __user *buf, size_t count, loff_t *offp) { int err; char buffer[64]; u32 min, max; unsigned long val; struct sunxi_led *led = sunxi_led_global; min = SUNXI_T0H_MIN_NS; max = SUNXI_T0H_MAX_NS; if (count >= sizeof(buffer)) goto err_out; if (copy_from_user(buffer, buf, count)) goto err_out; buffer[count] = '\0'; err = kstrtoul(buffer, 10, &val); if (err) goto err_out; if (val < min || val > max) goto err_out; led->t0h_ns = val; sunxi_set_t0h_ns(led); *offp += count; return count; err_out: LED_ERR("invalid parameter, t0h_ns should be %u-%u!\n", min, max); return -EINVAL; } static ssize_t t0h_ns_read(struct file *filp, char __user *buf, size_t count, loff_t *offp) { int r; char buffer[64]; struct sunxi_led *led = sunxi_led_global; r = snprintf(buffer, 64, "%u\n", led->t0h_ns); return simple_read_from_buffer(buf, count, offp, buffer, r); } static const struct file_operations t0h_ns_fops = { .owner = THIS_MODULE, .write = t0h_ns_write, .read = t0h_ns_read, }; static ssize_t t0l_ns_write(struct file *filp, const char __user *buf, size_t count, loff_t *offp) { int err; char buffer[64]; u32 min, max; unsigned long val; struct sunxi_led *led = sunxi_led_global; min = SUNXI_T0L_MIN_NS; max = SUNXI_T0L_MAX_NS; if (count >= sizeof(buffer)) goto err_out; if (copy_from_user(buffer, buf, count)) goto err_out; buffer[count] = '\0'; err = kstrtoul(buffer, 10, &val); if (err) goto err_out; if (val < min || val > max) goto err_out; led->t0l_ns = val; sunxi_set_t0l_ns(led); *offp += count; return count; err_out: LED_ERR("invalid parameter, t0l_ns should be %u-%u!\n", min, max); return -EINVAL; } static ssize_t t0l_ns_read(struct file *filp, char __user *buf, size_t count, loff_t *offp) { int r; char buffer[64]; struct sunxi_led *led = sunxi_led_global; r = snprintf(buffer, 64, "%u\n", led->t0l_ns); return simple_read_from_buffer(buf, count, offp, buffer, r); } static const struct file_operations t0l_ns_fops = { .owner = THIS_MODULE, .write = t0l_ns_write, .read = t0l_ns_read, }; static ssize_t wait_time0_ns_write(struct file *filp, const char __user *buf, size_t count, loff_t *offp) { int err; char buffer[64]; u32 min, max; unsigned long val; struct sunxi_led *led = sunxi_led_global; min = SUNXI_WAIT_TIME0_MIN_NS; max = SUNXI_WAIT_TIME0_MAX_NS; if (count >= sizeof(buffer)) goto err_out; if (copy_from_user(buffer, buf, count)) goto err_out; buffer[count] = '\0'; err = kstrtoul(buffer, 10, &val); if (err) goto err_out; if (val < min || val > max) goto err_out; led->wait_time0_ns = val; sunxi_set_wait_time0_ns(led); *offp += count; return count; err_out: LED_ERR("invalid parameter, wait_time0_ns should be %u-%u!\n", min, max); return -EINVAL; } static ssize_t wait_time0_ns_read(struct file *filp, char __user *buf, size_t count, loff_t *offp) { int r; char buffer[64]; struct sunxi_led *led = sunxi_led_global; r = snprintf(buffer, 64, "%u\n", led->wait_time0_ns); return simple_read_from_buffer(buf, count, offp, buffer, r); } static const struct file_operations wait_time0_ns_fops = { .owner = THIS_MODULE, .write = wait_time0_ns_write, .read = wait_time0_ns_read, }; static ssize_t wait_time1_ns_write(struct file *filp, const char __user *buf, size_t count, loff_t *offp) { int err; char buffer[64]; u32 min; unsigned long long max; unsigned long long val; struct sunxi_led *led = sunxi_led_global; min = SUNXI_WAIT_TIME1_MIN_NS; max = SUNXI_WAIT_TIME1_MAX_NS; if (count >= sizeof(buffer)) goto err_out; if (copy_from_user(buffer, buf, count)) goto err_out; buffer[count] = '\0'; err = kstrtoull(buffer, 10, &val); if (err) goto err_out; if (val < min || val > max) goto err_out; led->wait_time1_ns = val; sunxi_set_wait_time1_ns(led); *offp += count; return count; err_out: LED_ERR("invalid parameter, wait_time1_ns should be %u-%lld!\n", min, max); return -EINVAL; } static ssize_t wait_time1_ns_read(struct file *filp, char __user *buf, size_t count, loff_t *offp) { int r; char buffer[64]; struct sunxi_led *led = sunxi_led_global; r = snprintf(buffer, 64, "%lld\n", led->wait_time1_ns); return simple_read_from_buffer(buf, count, offp, buffer, r); } static const struct file_operations wait_time1_ns_fops = { .owner = THIS_MODULE, .write = wait_time1_ns_write, .read = wait_time1_ns_read, }; static ssize_t wait_data_time_ns_write(struct file *filp, const char __user *buf, size_t count, loff_t *offp) { int err; char buffer[64]; u32 min, max; unsigned long val; struct sunxi_led *led = sunxi_led_global; min = SUNXI_WAIT_DATA_TIME_MIN_NS; #ifdef SUNXI_FPGA_LEDC max = SUNXI_WAIT_DATA_TIME_MAX_NS_FPGA; #else max = SUNXI_WAIT_DATA_TIME_MAX_NS_IC; #endif if (count >= sizeof(buffer)) goto err_out; if (copy_from_user(buffer, buf, count)) goto err_out; buffer[count] = '\0'; err = kstrtoul(buffer, 10, &val); if (err) goto err_out; if (val < min || val > max) goto err_out; led->wait_data_time_ns = val; sunxi_set_wait_data_time_ns(led); *offp += count; return count; err_out: LED_ERR("invalid parameter, wait_data_time_ns should be %u-%u!\n", min, max); return -EINVAL; } static ssize_t wait_data_time_ns_read(struct file *filp, char __user *buf, size_t count, loff_t *offp) { int r; char buffer[64]; struct sunxi_led *led = sunxi_led_global; r = snprintf(buffer, 64, "%u\n", led->wait_data_time_ns); return simple_read_from_buffer(buf, count, offp, buffer, r); } static const struct file_operations wait_data_time_ns_fops = { .owner = THIS_MODULE, .write = wait_data_time_ns_write, .read = wait_data_time_ns_read, }; static int data_show(struct seq_file *s, void *data) { int i; struct sunxi_led *led = sunxi_led_global; for (i = 0; i < led->led_count; i++) { if (!(i % 4)) { if (i + 4 <= led->led_count) seq_printf(s, "%04d-%04d", i, i + 4); else seq_printf(s, "%04d-%04d", i, led->led_count); } seq_printf(s, " 0x%08x", led->data[i]); if (((i % 4) == 3) || (i == led->led_count - 1)) seq_puts(s, "\n"); } return 0; } static int data_open(struct inode *inode, struct file *file) { return single_open(file, data_show, inode->i_private); } static const struct file_operations data_fops = { .owner = THIS_MODULE, .open = data_open, .read = seq_read, .llseek = seq_lseek, .release = single_release, }; static ssize_t output_mode_write(struct file *filp, const char __user *buf, size_t count, loff_t *offp) { char buffer[64]; struct sunxi_led *led = sunxi_led_global; if (count >= sizeof(buffer)) goto err_out; if (copy_from_user(buffer, buf, count)) goto err_out; buffer[count] = '\0'; sunxi_ledc_set_output_mode(led, buffer); *offp += count; return count; err_out: LED_ERR("invalid parameter!\n"); return -EINVAL; } static ssize_t output_mode_read(struct file *filp, char __user *buf, size_t count, loff_t *offp) { int r; char buffer[64]; struct sunxi_led *led = sunxi_led_global; r = snprintf(buffer, 64, "%s\n", led->output_mode.str); return simple_read_from_buffer(buf, count, offp, buffer, r); } static const struct file_operations output_mode_fops = { .owner = THIS_MODULE, .write = output_mode_write, .read = output_mode_read, }; static ssize_t hwversion_read(struct file *filp, char __user *buf, size_t count, loff_t *offp) { int r; char buffer[64]; u32 reg_val, major_ver, minor_ver; reg_val = sunxi_get_reg(LEDC_VER_NUM_REG); major_ver = reg_val >> 16; minor_ver = reg_val & 0xF; r = snprintf(buffer, 64, "r%up%u\n", major_ver, minor_ver); return simple_read_from_buffer(buf, count, offp, buffer, r); } static const struct file_operations hwversion_fops = { .owner = THIS_MODULE, .read = hwversion_read, }; static void sunxi_led_create_debugfs(struct sunxi_led *led) { struct dentry *debugfs_dir, *debugfs_file; debugfs_dir = debugfs_create_dir("sunxi_leds", NULL); if (IS_ERR_OR_NULL(debugfs_dir)) { LED_ERR("debugfs_create_dir failed!\n"); return; } led->debugfs_dir = debugfs_dir; debugfs_file = debugfs_create_file("reset_ns", 0660, debugfs_dir, NULL, &reset_ns_fops); if (!debugfs_file) LED_ERR("debugfs_create_file for reset_ns failed!\n"); debugfs_file = debugfs_create_file("t1h_ns", 0660, debugfs_dir, NULL, &t1h_ns_fops); if (!debugfs_file) LED_ERR("debugfs_create_file for t1h_ns failed!\n"); debugfs_file = debugfs_create_file("t1l_ns", 0660, debugfs_dir, NULL, &t1l_ns_fops); if (!debugfs_file) LED_ERR("debugfs_create_file for t1l_ns failed!\n"); debugfs_file = debugfs_create_file("t0h_ns", 0660, debugfs_dir, NULL, &t0h_ns_fops); if (!debugfs_file) LED_ERR("debugfs_create_file for t0h_ns failed!\n"); debugfs_file = debugfs_create_file("t0l_ns", 0660, debugfs_dir, NULL, &t0l_ns_fops); if (!debugfs_file) LED_ERR("debugfs_create_file for t0l_ns failed!\n"); debugfs_file = debugfs_create_file("wait_time0_ns", 0660, debugfs_dir, NULL, &wait_time0_ns_fops); if (!debugfs_file) LED_ERR("debugfs_create_file for wait_time0_ns failed!\n"); debugfs_file = debugfs_create_file("wait_time1_ns", 0660, debugfs_dir, NULL, &wait_time1_ns_fops); if (!debugfs_file) LED_ERR("debugfs_create_file for wait_time1_ns failed!\n"); debugfs_file = debugfs_create_file("wait_data_time_ns", 0660, debugfs_dir, NULL, &wait_data_time_ns_fops); if (!debugfs_file) LED_ERR("debugfs_create_file for wait_data_time_ns failed!\n"); debugfs_file = debugfs_create_file("data", 0440, debugfs_dir, NULL, &data_fops); if (!debugfs_file) LED_ERR("debugfs_create_file for data failed!\n"); debugfs_file = debugfs_create_file("output_mode", 0660, debugfs_dir, NULL, &output_mode_fops); if (!debugfs_file) LED_ERR("debugfs_create_file for output_mode failed!\n"); if (!debugfs_file) LED_ERR("debugfs_create_file for trans_mode failed!\n"); debugfs_file = debugfs_create_file("hwversion", 0440, debugfs_dir, NULL, &hwversion_fops); if (!debugfs_file) LED_ERR("debugfs_create_file for hwversion failed!\n"); } static void sunxi_led_remove_debugfs(struct sunxi_led *led) { debugfs_remove_recursive(led->debugfs_dir); } #endif /* CONFIG_DEBUG_FS */ static void sunxi_ledc_set_dma_mode(struct sunxi_led *led) { u32 reg_val = 0; reg_val |= 1 << 5; sunxi_set_reg(LEDC_DMA_CTRL_REG, reg_val); sunxi_ledc_disable_irq(LEDC_FIFO_CPUREQ_INT_EN); } static void sunxi_ledc_set_cpu_mode(struct sunxi_led *led) { u32 reg_val = 0; reg_val &= ~(1 << 5); sunxi_set_reg(LEDC_DMA_CTRL_REG, reg_val); sunxi_ledc_enable_irq(LEDC_FIFO_CPUREQ_INT_EN); } static void sunxi_ledc_dma_callback(void *param) { dprintk(DEBUG_INFO, "finish\n"); } static void sunxi_ledc_trans_data(struct sunxi_led *led) { int i, err; size_t size; unsigned long flags; phys_addr_t dst_addr; struct dma_slave_config slave_config; struct device *dev = led->dev; struct dma_async_tx_descriptor *dma_desc; /* less than 32 lights use cpu transmission. */ /* more than 32 lights use dma transmission. */ if (led->length <= SUNXI_LEDC_FIFO_DEPTH) { dprintk(DEBUG_INFO, "cpu xfer\n"); ktime_get_coarse_real_ts64(&(led->start_time)); sunxi_ledc_set_time(led); sunxi_ledc_set_output_mode(led, led->output_mode.str); sunxi_ledc_set_cpu_mode(led); sunxi_ledc_set_length(led); sunxi_ledc_enable_irq(LEDC_TRANS_FINISH_INT_EN | LEDC_WAITDATA_TIMEOUT_INT_EN | LEDC_FIFO_OVERFLOW_INT_EN | LEDC_GLOBAL_INT_EN); sunxi_ledc_enable(led); for (i = 0; i < led->length; i++) sunxi_set_reg(LEDC_DATA_REG_OFFSET, led->data[i]); } else { dprintk(DEBUG_INFO, "dma xfer\n"); size = led->length * 4; led->src_dma = dma_map_single(dev, led->data, size, DMA_TO_DEVICE); dst_addr = led->res->start + LEDC_DATA_REG_OFFSET; flags = DMA_PREP_INTERRUPT | DMA_CTRL_ACK; slave_config.direction = DMA_MEM_TO_DEV; slave_config.src_addr = led->src_dma; slave_config.dst_addr = dst_addr; slave_config.src_addr_width = DMA_SLAVE_BUSWIDTH_4_BYTES; slave_config.dst_addr_width = DMA_SLAVE_BUSWIDTH_4_BYTES; slave_config.src_maxburst = 4; slave_config.dst_maxburst = 4; err = dmaengine_slave_config(led->dma_chan, &slave_config); if (err < 0) { LED_ERR("dmaengine_slave_config failed!\n"); return; } dma_desc = dmaengine_prep_slave_single(led->dma_chan, led->src_dma, size, DMA_MEM_TO_DEV, flags); if (!dma_desc) { LED_ERR("dmaengine_prep_slave_single failed!\n"); return; } dma_desc->callback = sunxi_ledc_dma_callback; dmaengine_submit(dma_desc); dma_async_issue_pending(led->dma_chan); ktime_get_coarse_real_ts64(&(led->start_time)); sunxi_ledc_set_time(led); sunxi_ledc_set_output_mode(led, led->output_mode.str); sunxi_ledc_set_dma_mode(led); sunxi_ledc_set_length(led); sunxi_ledc_enable_irq(LEDC_TRANS_FINISH_INT_EN | LEDC_WAITDATA_TIMEOUT_INT_EN | LEDC_FIFO_OVERFLOW_INT_EN | LEDC_GLOBAL_INT_EN); sunxi_ledc_enable(led); } } static inline void sunxi_ledc_clear_all_irq(void) { u32 reg_val = sunxi_get_reg(LEDC_INT_STS_REG_OFFSET); reg_val &= ~0x1F; sunxi_set_reg(LEDC_INT_STS_REG_OFFSET, reg_val); } static inline void sunxi_ledc_clear_irq(enum sunxi_ledc_irq_status_reg irq) { u32 reg_val = sunxi_get_reg(LEDC_INT_STS_REG_OFFSET); reg_val &= ~irq; sunxi_set_reg(LEDC_INT_STS_REG_OFFSET, reg_val); } static int sunxi_ledc_complete(struct sunxi_led *led) { unsigned long flags = 0; unsigned long timeout = 0; u32 reg_val; /*wait_event_timeout return 0 : timeout *wait_event_timeout return > 0 : thr left time * */ timeout = wait_event_timeout(led->wait, led->result, 5*HZ); if (timeout == 0) { reg_val = sunxi_get_reg(LEDC_INT_STS_REG_OFFSET); pr_err("LEDC INTERRUPT STATUS REG IS %x", reg_val); LED_ERR("led xfer timeout\n"); reg_val = sunxi_get_reg(LEDC_INT_STS_REG_OFFSET); pr_err("LEDC INTERRUPT STATUS REG IS %x", reg_val); return -ETIME; } else if (led->result == RESULT_ERR) { return -ECOMM; } dprintk(DEBUG_INFO, "xfer complete\n"); spin_lock_irqsave(&led->lock, flags); led->result = 0; spin_unlock_irqrestore(&led->lock, flags); return 0; } static irqreturn_t sunxi_ledc_irq_handler(int irq, void *dev_id) { long delta_time_ns; u32 irq_status, max_ns; struct sunxi_led *led = sunxi_led_global; struct device *dev = led->dev; struct timespec64 current_time; spin_lock(&led->lock); irq_status = sunxi_get_reg(LEDC_INT_STS_REG_OFFSET); sunxi_ledc_clear_all_irq(); if (irq_status & LEDC_TRANS_FINISH_INT) { sunxi_ledc_reset(led); led->result = RESULT_COMPLETE; goto out; } if (irq_status & LEDC_WAITDATA_TIMEOUT_INT) { ktime_get_coarse_real_ts64(¤t_time); delta_time_ns = current_time.tv_sec - led->start_time.tv_sec; delta_time_ns *= 1000 * 1000 * 1000; delta_time_ns += current_time.tv_nsec - led->start_time.tv_nsec; max_ns = led->wait_data_time_ns; if (delta_time_ns <= max_ns) { spin_unlock(&led->lock); return IRQ_HANDLED; } sunxi_ledc_reset(led); if (delta_time_ns <= max_ns * 2) { sunxi_ledc_trans_data(led); } else { LED_ERR("wait time is more than %d ns," "going to reset ledc and drop this operation!\n", max_ns); led->result = RESULT_ERR; } goto out; } if (irq_status & LEDC_FIFO_OVERFLOW_INT) { LED_ERR("there exists fifo overflow issue, irq_status=0x%x!\n", irq_status); sunxi_ledc_reset(led); led->result = RESULT_ERR; goto out; } out: if (led->dma_chan) dma_unmap_single(dev, led->src_dma, led->length * 4, DMA_TO_DEVICE); wake_up(&led->wait); led->length = 0; spin_unlock(&led->lock); return IRQ_HANDLED; } static int sunxi_ledc_irq_init(struct sunxi_led *led) { int err; struct device *dev = led->dev; unsigned long flags = 0; const char *name = "ledcirq"; struct platform_device *pdev; pdev = container_of(dev, struct platform_device, dev); spin_lock_init(&led->lock); led->irqnum = platform_get_irq(pdev, 0); if (led->irqnum < 0) LED_ERR("failed to get ledc irq!\n"); err = request_irq(led->irqnum, sunxi_ledc_irq_handler, flags, name, dev); if (err) { LED_ERR("failed to install IRQ handler for irqnum %d\n", led->irqnum); return -EPERM; } return 0; } static void sunxi_ledc_irq_deinit(struct sunxi_led *led) { free_irq(led->irqnum, led->dev); sunxi_ledc_disable_irq(LEDC_TRANS_FINISH_INT_EN | LEDC_FIFO_CPUREQ_INT_EN | LEDC_WAITDATA_TIMEOUT_INT_EN | LEDC_FIFO_OVERFLOW_INT_EN | LEDC_GLOBAL_INT_EN); } static void sunxi_ledc_pinctrl_init(struct sunxi_led *led) { struct device *dev = led->dev; struct pinctrl *pinctrl = devm_pinctrl_get_select_default(dev); led->pctrl = pinctrl; if (IS_ERR(pinctrl)) LED_ERR("devm_pinctrl_get_select_default failed!\n"); } static int led_regulator_request(struct sunxi_led *led) { struct regulator *regu = NULL; /* Consider "n*" as nocare. Support "none", "nocare", "null", "" etc. */ if ((led->regulator_id[0] == 'n') || (led->regulator_id[0] == 0)) return 0; regu = regulator_get(NULL, led->regulator_id); if (IS_ERR(regu)) { LED_ERR("get regulator %s failed!\n", led->regulator_id); return -1; } led->regulator = regu; return 0; } static int led_regulator_release(struct sunxi_led *led) { if (led->regulator == NULL) return 0; regulator_put(led->regulator); led->regulator = NULL; return 1; } static int sunxi_ledc_dma_get(struct sunxi_led *led) { if (led->dma_chan == NULL) { led->dma_chan = dma_request_chan(led->dev, "tx"); if (IS_ERR(led->dma_chan)) { LED_ERR("failed to get the DMA channel!\n"); return -EFAULT; } } return 0; } static int sunxi_set_led_brightness(struct led_classdev *led_cdev, enum led_brightness value) { unsigned long flags; u32 r, g, b, shift, old_data, new_data, length; struct sunxi_led_info *pinfo; struct sunxi_led_classdev_group *pcdev_group; struct sunxi_led *led = sunxi_led_global; int err; pinfo = container_of(led_cdev, struct sunxi_led_info, cdev); switch (pinfo->type) { case LED_TYPE_G: pcdev_group = container_of(pinfo, struct sunxi_led_classdev_group, g); g = value; shift = 16; break; case LED_TYPE_R: pcdev_group = container_of(pinfo, struct sunxi_led_classdev_group, r); r = value; shift = 8; break; case LED_TYPE_B: pcdev_group = container_of(pinfo, struct sunxi_led_classdev_group, b); b = value; shift = 0; break; } old_data = led->data[pcdev_group->led_num]; if (((old_data >> shift) & 0xFF) == value) return 0; if (pinfo->type != LED_TYPE_R) r = pcdev_group->r.cdev.brightness; if (pinfo->type != LED_TYPE_G) g = pcdev_group->g.cdev.brightness; if (pinfo->type != LED_TYPE_B) b = pcdev_group->b.cdev.brightness; /* LEDC treats input data as GRB by default */ new_data = (g << 16) | (r << 8) | b; length = pcdev_group->led_num + 1; spin_lock_irqsave(&led->lock, flags); led->data[pcdev_group->led_num] = new_data; led->length = length; spin_unlock_irqrestore(&led->lock, flags); /* prepare for dma xfer, dynamic apply dma channel */ if (led->length > SUNXI_LEDC_FIFO_DEPTH) { err = sunxi_ledc_dma_get(led); if (err) return err; } sunxi_ledc_trans_data(led); if (debug_mask & DEBUG_INFO2) { dprintk(DEBUG_INFO2, "dump reg:\n"); led_dump_reg(led, 0, 0x30); } sunxi_ledc_complete(led); if (debug_mask & DEBUG_INFO1) pr_warn("num = %03u\n", length); return 0; } static int sunxi_register_led_classdev(struct sunxi_led *led) { int i, err; size_t size; struct device *dev = led->dev; struct led_classdev *pcdev_RGB; dprintk(DEBUG_INIT, "led_classdev start\n"); if (!led->led_count) led->led_count = SUNXI_DEFAULT_LED_COUNT; size = sizeof(struct sunxi_led_classdev_group) * led->led_count; led->pcdev_group = devm_kzalloc(dev, size, GFP_KERNEL); if (!led->pcdev_group) return -ENOMEM; for (i = 0; i < led->led_count; i++) { led->pcdev_group[i].r.type = LED_TYPE_R; pcdev_RGB = &led->pcdev_group[i].r.cdev; pcdev_RGB->name = devm_kzalloc(dev, 16, GFP_KERNEL); if (!pcdev_RGB->name) return -ENOMEM; sprintf((char *)pcdev_RGB->name, "sunxi_led%dr", i); pcdev_RGB->brightness = LED_OFF; pcdev_RGB->brightness_set_blocking = sunxi_set_led_brightness; pcdev_RGB->dev = dev; err = led_classdev_register(dev, pcdev_RGB); if (err < 0) { LED_ERR("led_classdev_register %s failed!\n", pcdev_RGB->name); return err; } led->pcdev_group[i].g.type = LED_TYPE_G; pcdev_RGB = &led->pcdev_group[i].g.cdev; pcdev_RGB->name = devm_kzalloc(dev, 16, GFP_KERNEL); if (!pcdev_RGB->name) return -ENOMEM; sprintf((char *)pcdev_RGB->name, "sunxi_led%dg", i); pcdev_RGB->brightness = LED_OFF; pcdev_RGB->brightness_set_blocking = sunxi_set_led_brightness; pcdev_RGB->dev = dev; err = led_classdev_register(dev, pcdev_RGB); if (err < 0) { LED_ERR("led_classdev_register %s failed!\n", pcdev_RGB->name); return err; } led->pcdev_group[i].b.type = LED_TYPE_B; pcdev_RGB = &led->pcdev_group[i].b.cdev; pcdev_RGB->name = devm_kzalloc(dev, 16, GFP_KERNEL); if (!pcdev_RGB->name) return -ENOMEM; sprintf((char *)pcdev_RGB->name, "sunxi_led%db", i); pcdev_RGB->brightness = LED_OFF; pcdev_RGB->brightness_set_blocking = sunxi_set_led_brightness; pcdev_RGB->dev = dev; err = led_classdev_register(dev, pcdev_RGB); if (err < 0) { LED_ERR("led_classdev_register %s failed!\n", pcdev_RGB->name); return err; } led->pcdev_group[i].led_num = i; } size = sizeof(u32) * led->led_count; led->data = devm_kzalloc(dev, size, GFP_KERNEL); if (!led->data) return -ENOMEM; return 0; } static void sunxi_unregister_led_classdev(struct sunxi_led *led) { int i; for (i = 0; i < led->led_count; i++) { kfree(led->pcdev_group[i].b.cdev.name); led->pcdev_group[i].b.cdev.name = NULL; kfree(led->pcdev_group[i].g.cdev.name); led->pcdev_group[i].g.cdev.name = NULL; kfree(led->pcdev_group[i].r.cdev.name); led->pcdev_group[i].r.cdev.name = NULL; led_classdev_unregister(&led->pcdev_group[i].b.cdev); led_classdev_unregister(&led->pcdev_group[i].g.cdev); led_classdev_unregister(&led->pcdev_group[i].r.cdev); } kfree(led->data); led->data = NULL; kfree(led->pcdev_group); led->pcdev_group = NULL; } static inline int sunxi_get_u32_of_property(const char *propname, int *val) { int err; struct sunxi_led *led = sunxi_led_global; struct device *dev = led->dev; struct device_node *np = dev->of_node; err = of_property_read_u32(np, propname, val); if (err < 0) LED_ERR("failed to get the value of propname %s!\n", propname); return err; } static inline int sunxi_get_str_of_property(const char *propname, const char **out_string) { int err; struct sunxi_led *led = sunxi_led_global; struct device *dev = led->dev; struct device_node *np = dev->of_node; err = of_property_read_string(np, propname, out_string); if (err < 0) LED_ERR("failed to get the string of propname %s!\n", propname); return err; } static void sunxi_get_para_of_property(struct sunxi_led *led) { int err; u32 val; const char *str; err = sunxi_get_u32_of_property("led_count", &val); if (!err) led->led_count = val; memcpy(led->output_mode.str, "GRB", 3); led->output_mode.val = SUNXI_OUTPUT_GRB; err = sunxi_get_str_of_property("output_mode", &str); if (!err) if (!strncmp(str, "BRG", 3) || !strncmp(str, "GBR", 3) || !strncmp(str, "RGB", 3) || !strncmp(str, "RBG", 3) || !strncmp(str, "BGR", 3)) memcpy(led->output_mode.str, str, 3); err = sunxi_get_str_of_property("led_regulator", &str); if (!err) { if (strlen(str) >= sizeof(led->regulator_id)) LED_ERR("illegal regulator id\n"); else { strcpy(led->regulator_id, str); pr_info("led_regulator: %s\n", led->regulator_id); } } err = sunxi_get_u32_of_property("reset_ns", &val); if (!err) led->reset_ns = val; err = sunxi_get_u32_of_property("t1h_ns", &val); if (!err) led->t1h_ns = val; err = sunxi_get_u32_of_property("t1l_ns", &val); if (!err) led->t1l_ns = val; err = sunxi_get_u32_of_property("t0h_ns", &val); if (!err) led->t0h_ns = val; err = sunxi_get_u32_of_property("t0l_ns", &val); if (!err) led->t0l_ns = val; err = sunxi_get_u32_of_property("wait_time0_ns", &val); if (!err) led->wait_time0_ns = val; err = sunxi_get_u32_of_property("wait_time1_ns", &val); if (!err) led->wait_time1_ns = val; err = sunxi_get_u32_of_property("wait_data_time_ns", &val); if (!err) led->wait_data_time_ns = val; } static void sunxi_led_set_all(struct sunxi_led *led, u8 channel, enum led_brightness value) { u32 i; struct led_classdev *led_cdev; if (channel%3 == 0) { for (i = 0; i < led->led_count; i++) { led_cdev = &led->pcdev_group[i].r.cdev; mutex_lock(&led_cdev->led_access); sunxi_set_led_brightness(led_cdev, value); mutex_unlock(&led_cdev->led_access); } } else if (channel%3 == 1) { for (i = 0; i < led->led_count; i++) { led_cdev = &led->pcdev_group[i].g.cdev; mutex_lock(&led_cdev->led_access); sunxi_set_led_brightness(led_cdev, value); mutex_unlock(&led_cdev->led_access); } } else { for (i = 0; i < led->led_count; i++) { led_cdev = &led->pcdev_group[i].b.cdev; mutex_lock(&led_cdev->led_access); sunxi_set_led_brightness(led_cdev, value); mutex_unlock(&led_cdev->led_access); } } } static ssize_t led_show(struct class *class, struct class_attribute *attr, char *buf) { struct sunxi_led *led = sunxi_led_global; sunxi_led_set_all(led, 0, 0); sunxi_led_set_all(led, 1, 0); sunxi_led_set_all(led, 2, 0); sunxi_led_set_all(led, 0, 20); msleep(500); sunxi_led_set_all(led, 1, 20); msleep(500); sunxi_led_set_all(led, 2, 20); msleep(500); sunxi_led_set_all(led, 0, 0); sunxi_led_set_all(led, 1, 0); sunxi_led_set_all(led, 2, 0); return 0; } static struct class_attribute led_class_attrs[] = { __ATTR(light, 0644, led_show, NULL), //__ATTR_NULL, }; static void led_node_init(void) { int i; int err; /* sys/class/led/xxx */ for (i = 0; i < ARRAY_SIZE(led_class_attrs); i++) { err = class_create_file(led_class, &led_class_attrs[i]); if (err) { LED_ERR("class_create_file() failed!\n"); while (i--) class_remove_file(led_class, &led_class_attrs[i]); class_destroy(led_class); led_class = NULL; } } } static int sunxi_led_probe(struct platform_device *pdev) { int err; struct sunxi_led *led; struct device *dev = &pdev->dev; struct resource *mem_res = NULL; int ret; dprintk(DEBUG_INIT, "start\n"); led = devm_kzalloc(dev, sizeof(struct sunxi_led), GFP_KERNEL); if (!led) return -ENOMEM; sunxi_led_global = led; platform_set_drvdata(pdev, led); led->dev = dev; mem_res = platform_get_resource(pdev, IORESOURCE_MEM, 0); if (mem_res == NULL) { LED_ERR("failed to get MEM res\n"); ret = -ENXIO; goto emem; } if (!request_mem_region(mem_res->start, resource_size(mem_res), mem_res->name)) { LED_ERR("failed to request mem region\n"); ret = -EINVAL; goto emem; } led->iomem_reg_base = ioremap(mem_res->start, resource_size(mem_res)); if (!led->iomem_reg_base) { ret = -EIO; goto eiomap; } led->res = mem_res; led->output_mode.str = devm_kzalloc(dev, 3, GFP_KERNEL); if (!led->output_mode.str) { ret = -ENOMEM; goto ezalloc_str; } sunxi_get_para_of_property(led); err = led_regulator_request(led); if (err < 0) { LED_ERR("request regulator failed!\n"); ret = err; goto eregulator; } err = sunxi_register_led_classdev(led); if (err) { LED_ERR("failed to register led classdev\n"); ret = err; goto eclassdev; } sunxi_ledc_set_time(led); led->reset = devm_reset_control_get(&pdev->dev, NULL); if (IS_ERR(led->reset)) { LED_ERR("get reset clk error\n"); return -EINVAL; } ret = reset_control_deassert(led->reset); if (ret) { LED_ERR("deassert clk error, ret:%d\n", ret); return ret; } sunxi_clk_init(led); init_waitqueue_head(&led->wait); err = sunxi_ledc_irq_init(led); if (err) { LED_ERR("failed to init irq\n"); ret = err; goto eirq; } sunxi_ledc_pinctrl_init(led); #ifdef CONFIG_DEBUG_FS sunxi_led_create_debugfs(led); #endif /* CONFIG_DEBUG_FS */ led_class = class_create(THIS_MODULE, "led"); if (IS_ERR(led_class)) { LED_ERR("class_register err\n"); class_destroy(led_class); ret = -EFAULT; goto eclass; } led_node_init(); dprintk(DEBUG_INIT, "finish\n"); return 0; eclass: #ifdef CONFIG_DEBUG_FS sunxi_led_remove_debugfs(led); #endif /* CONFIG_DEBUG_FS */ sunxi_ledc_irq_deinit(led); eirq: sunxi_unregister_led_classdev(led); sunxi_clk_deinit(led); eclassdev: led_regulator_release(led); eregulator: kfree(led->output_mode.str); ezalloc_str: iounmap(led->iomem_reg_base); led->iomem_reg_base = NULL; eiomap: release_mem_region(mem_res->start, resource_size(mem_res)); emem: kfree(led); return ret; } static int sunxi_led_remove(struct platform_device *pdev) { struct sunxi_led *led = platform_get_drvdata(pdev); class_destroy(led_class); #ifdef CONFIG_DEBUG_FS sunxi_led_remove_debugfs(led); #endif /* CONFIG_DEBUG_FS */ if (led->dma_chan) { dmaengine_terminate_all(led->dma_chan); dma_release_channel(led->dma_chan); led->dma_chan = NULL; } sunxi_ledc_irq_deinit(led); sunxi_unregister_led_classdev(led); sunxi_clk_deinit(led); led_regulator_release(led); kfree(led->output_mode.str); led->output_mode.str = NULL; iounmap(led->iomem_reg_base); led->iomem_reg_base = NULL; release_mem_region(led->res->start, resource_size(led->res)); kfree(led); led = NULL; dprintk(DEBUG_INIT, "finish\n"); return 0; } #if IS_ENABLED(CONFIG_PM) static inline void sunxi_led_save_regs(struct sunxi_led *led) { int i; for (i = 0; i < ARRAY_SIZE(sunxi_led_regs_offset); i++) led->regs_backup[i] = readl(led->iomem_reg_base + sunxi_led_regs_offset[i]); } static inline void sunxi_led_restore_regs(struct sunxi_led *led) { int i; for (i = 0; i < ARRAY_SIZE(sunxi_led_regs_offset); i++) writel(led->regs_backup[i], led->iomem_reg_base + sunxi_led_regs_offset[i]); } static void sunxi_led_enable_irq(struct sunxi_led *led) { enable_irq(led->irqnum); } static void sunxi_led_disable_irq(struct sunxi_led *led) { disable_irq_nosync(led->irqnum); } static int sunxi_led_gpio_state_select(struct sunxi_led *led, char *name) { int err; struct pinctrl_state *pctrl_state; pctrl_state = pinctrl_lookup_state(led->pctrl, name); if (IS_ERR(pctrl_state)) { dev_err(led->dev, "pinctrl_lookup_state(%s) failed! return %p\n", name, pctrl_state); return PTR_ERR(pctrl_state); } err = pinctrl_select_state(led->pctrl, pctrl_state); if (err < 0) { dev_err(led->dev, "pinctrl_select_state(%s) failed! return %d\n", name, err); return err; } return 0; } static void sunxi_led_enable_clk(struct sunxi_led *led) { clk_prepare_enable(led->clk_ledc); clk_prepare_enable(led->clk_cpuapb); } static void sunxi_led_disable_clk(struct sunxi_led *led) { clk_disable_unprepare(led->clk_cpuapb); clk_disable_unprepare(led->clk_ledc); } static int sunxi_led_power_on(struct sunxi_led *led) { int err; if (led->regulator == NULL) return 0; err = regulator_enable(led->regulator); if (err) { dev_err(led->dev, "enable regulator %s failed!\n", led->regulator_id); return err; } return 0; } static int sunxi_led_power_off(struct sunxi_led *led) { int err; if (led->regulator == NULL) return 0; err = regulator_disable(led->regulator); if (err) { dev_err(led->dev, "disable regulator %s failed!\n", led->regulator_id); return err; } return 0; } static int sunxi_led_suspend(struct device *dev) { struct platform_device *pdev = to_platform_device(dev); struct sunxi_led *led = platform_get_drvdata(pdev); dev_dbg(led->dev, "[%s] enter standby\n", __func__); sunxi_led_disable_irq(led); sunxi_led_save_regs(led); sunxi_led_gpio_state_select(led, PINCTRL_STATE_SLEEP); sunxi_led_disable_clk(led); reset_control_assert(led->reset); sunxi_led_power_off(led); return 0; } static int sunxi_led_resume(struct device *dev) { struct platform_device *pdev = to_platform_device(dev); struct sunxi_led *led = platform_get_drvdata(pdev); dev_dbg(led->dev, "[%s] return from standby\n", __func__); sunxi_led_power_on(led); reset_control_deassert(led->reset); sunxi_led_enable_clk(led); sunxi_led_gpio_state_select(led, PINCTRL_STATE_DEFAULT); sunxi_led_restore_regs(led); sunxi_led_enable_irq(led); return 0; } static const struct dev_pm_ops sunxi_led_pm_ops = { .suspend = sunxi_led_suspend, .resume = sunxi_led_resume, }; #define SUNXI_LED_PM_OPS (&sunxi_led_pm_ops) #endif static const struct of_device_id sunxi_led_dt_ids[] = { {.compatible = "allwinner,sunxi-leds"}, {}, }; static struct platform_driver sunxi_led_driver = { .probe = sunxi_led_probe, .remove = sunxi_led_remove, .driver = { .name = "sunxi-leds", .owner = THIS_MODULE, #if IS_ENABLED(CONFIG_PM) .pm = SUNXI_LED_PM_OPS, #endif .of_match_table = sunxi_led_dt_ids, }, }; module_platform_driver(sunxi_led_driver); module_param_named(debug, debug_mask, int, 0664); MODULE_ALIAS("sunxi leds dirver"); MODULE_ALIAS("platform : leds dirver"); MODULE_LICENSE("GPL v2"); MODULE_VERSION("1.2.3"); MODULE_AUTHOR("Albert Yu <yuxyun@allwinnertech.com>"); MODULE_AUTHOR("liuyu <SWCliuyus@allwinnertech.com>"); MODULE_DESCRIPTION("Allwinner ledc-controller driver");lichee/linux-5.4/drivers/leds/leds-sunxi.h

/* * Copyright (C) 2018 Allwinner Technology Limited. All rights reserved. * Albert Yu <yuxyun@allwinnertech.com> * * This program is free software; you can redistribute it and/or modify * it under the terms of the GNU General Public License version 2 as * published by the Free Software Foundation. * */ #ifndef __LINUX_LEDS_SUNXI_H #define __LINUX_LEDS_SUNXI_H #include <linux/device.h> #include <linux/list.h> #include <linux/mutex.h> #include <linux/rwsem.h> #include <linux/spinlock.h> #include <linux/timer.h> #include <linux/workqueue.h> #define HEXADECIMAL (0x10) #define REG_INTERVAL (0x04) #define REG_CL (0x0c) #define RESULT_COMPLETE 1 #define RESULT_ERR 2 #define SUNXI_LEDC_REG_BASE_ADDR 0x06700000 #define SUNXI_MAX_LED_COUNT 1024 #define SUNXI_DEFAULT_LED_COUNT 8 #define SUNXI_RESET_TIME_MIN_NS 84 #define SUNXI_RESET_TIME_MAX_NS 327000 #define SUNXI_T1H_MIN_NS 84 #define SUNXI_T1H_MAX_NS 2560 #define SUNXI_T1L_MIN_NS 84 #define SUNXI_T1L_MAX_NS 1280 #define SUNXI_T0H_MIN_NS 84 #define SUNXI_T0H_MAX_NS 1280 #define SUNXI_T0L_MIN_NS 84 #define SUNXI_T0L_MAX_NS 2560 #define SUNXI_WAIT_TIME0_MIN_NS 84 #define SUNXI_WAIT_TIME0_MAX_NS 10000 #define SUNXI_WAIT_TIME1_MIN_NS 84 #define SUNXI_WAIT_TIME1_MAX_NS 85000000000 #define SUNXI_WAIT_DATA_TIME_MIN_NS 84 #define SUNXI_WAIT_DATA_TIME_MAX_NS_IC 655000 #define SUNXI_WAIT_DATA_TIME_MAX_NS_FPGA 20000000 #define SUNXI_LEDC_FIFO_DEPTH 32 /* 32 * 4 bytes */ #define SUNXI_LEDC_FIFO_TRIG_LEVEL 15 #if defined(CONFIG_FPGA_V4_PLATFORM) || defined(CONFIG_FPGA_V7_PLATFORM) #define SUNXI_FPGA_LEDC #endif enum sunxi_ledc_output_mode_val { SUNXI_OUTPUT_GRB = 0 << 6, SUNXI_OUTPUT_GBR = 1 << 6, SUNXI_OUTPUT_RGB = 2 << 6, SUNXI_OUTPUT_RBG = 3 << 6, SUNXI_OUTPUT_BGR = 4 << 6, SUNXI_OUTPUT_BRG = 5 << 6 }; struct sunxi_ledc_output_mode { char *str; enum sunxi_ledc_output_mode_val val; }; enum sunxi_ledc_trans_mode_val { LEDC_TRANS_CPU_MODE, LEDC_TRANS_DMA_MODE }; enum sunxi_ledc_reg { LEDC_CTRL_REG_OFFSET = 0x00, LED_T01_TIMING_CTRL_REG_OFFSET = 0x04, LEDC_DATA_FINISH_CNT_REG_OFFSET = 0x08, LED_RESET_TIMING_CTRL_REG_OFFSET = 0x0c, LEDC_WAIT_TIME0_CTRL_REG = 0x10, LEDC_DATA_REG_OFFSET = 0x14, LEDC_DMA_CTRL_REG = 0x18, LEDC_INT_CTRL_REG_OFFSET = 0x1c, LEDC_INT_STS_REG_OFFSET = 0x20, LEDC_WAIT_TIME1_CTRL_REG = 0x28, LEDC_VER_NUM_REG = 0x2c, LEDC_FIFO_DATA = 0x30, LEDC_TOTAL_REG_SIZE = LEDC_FIFO_DATA + SUNXI_LEDC_FIFO_DEPTH }; enum sunxi_ledc_irq_ctrl_reg { LEDC_TRANS_FINISH_INT_EN = (1 << 0), LEDC_FIFO_CPUREQ_INT_EN = (1 << 1), LEDC_WAITDATA_TIMEOUT_INT_EN = (1 << 3), LEDC_FIFO_OVERFLOW_INT_EN = (1 << 4), LEDC_GLOBAL_INT_EN = (1 << 5), }; enum sunxi_ledc_irq_status_reg { LEDC_TRANS_FINISH_INT = (1 << 0), LEDC_FIFO_CPUREQ_INT = (1 << 1), LEDC_WAITDATA_TIMEOUT_INT = (1 << 3), LEDC_FIFO_OVERFLOW_INT = (1 << 4), LEDC_FIFO_FULL = (1 << 16), LEDC_FIFO_EMPTY = (1 << 17), }; enum sunxi_led_type { LED_TYPE_R, LED_TYPE_G, LED_TYPE_B }; struct sunxi_led_info { enum sunxi_led_type type; struct led_classdev cdev; }; struct sunxi_led_classdev_group { u32 led_num; struct sunxi_led_info r; struct sunxi_led_info g; struct sunxi_led_info b; }; static u32 sunxi_led_regs_offset[] = { LEDC_CTRL_REG_OFFSET, LED_RESET_TIMING_CTRL_REG_OFFSET, LED_T01_TIMING_CTRL_REG_OFFSET, LEDC_WAIT_TIME0_CTRL_REG, LEDC_WAIT_TIME1_CTRL_REG, LEDC_INT_CTRL_REG_OFFSET, #ifndef SUNXI_FPGA_LEDC LEDC_DATA_FINISH_CNT_REG_OFFSET, #endif }; struct sunxi_led { u32 reset_ns; u32 t1h_ns; u32 t1l_ns; u32 t0h_ns; u32 t0l_ns; u32 wait_time0_ns; unsigned long long wait_time1_ns; u32 wait_data_time_ns; u32 irqnum; u32 led_count; u32 *data; u32 length; u8 result; spinlock_t lock; struct device *dev; dma_addr_t src_dma; struct dma_chan *dma_chan; wait_queue_head_t wait; struct timespec64 start_time; struct clk *clk_ledc; struct clk *clk_cpuapb; struct pinctrl *pctrl; void __iomem *iomem_reg_base; struct resource *res; struct sunxi_ledc_output_mode output_mode; struct sunxi_led_classdev_group *pcdev_group; struct dentry *debugfs_dir; char regulator_id[16]; struct regulator *regulator; struct reset_control *reset; u32 regs_backup[ARRAY_SIZE(sunxi_led_regs_offset)]; }; enum { DEBUG_INIT = 1U << 0, DEBUG_SUSPEND = 1U << 1, DEBUG_INFO = 1U << 2, DEBUG_INFO1 = 1U << 3, DEBUG_INFO2 = 1U << 4, }; #endif /* __LINUX_LEDS_SUNXI_H */kernel/linux-5.4/arch/riscv/boot/dts/sunxi/sun20iw1p1.dtsi

ledc: ledc@2008000 { #address-cells = <1>; #size-cells = <0>; compatible = "allwinner,sunxi-leds"; reg = <0x0 0x02008000 0x0 0x400>; interrupts-extended = <&plic0 36 IRQ_TYPE_LEVEL_HIGH>; interrupt-names = "ledcirq"; clocks = <&ccu CLK_LEDC>, <&ccu CLK_BUS_LEDC>; clock-names = "clk_ledc", "clk_cpuapb"; dmas = <&dma 42>, <&dma 42>; dma-names = "rx", "tx"; resets = <&ccu RST_BUS_LEDC>; reset-names = "ledc_reset"; status = "disable"; }; -

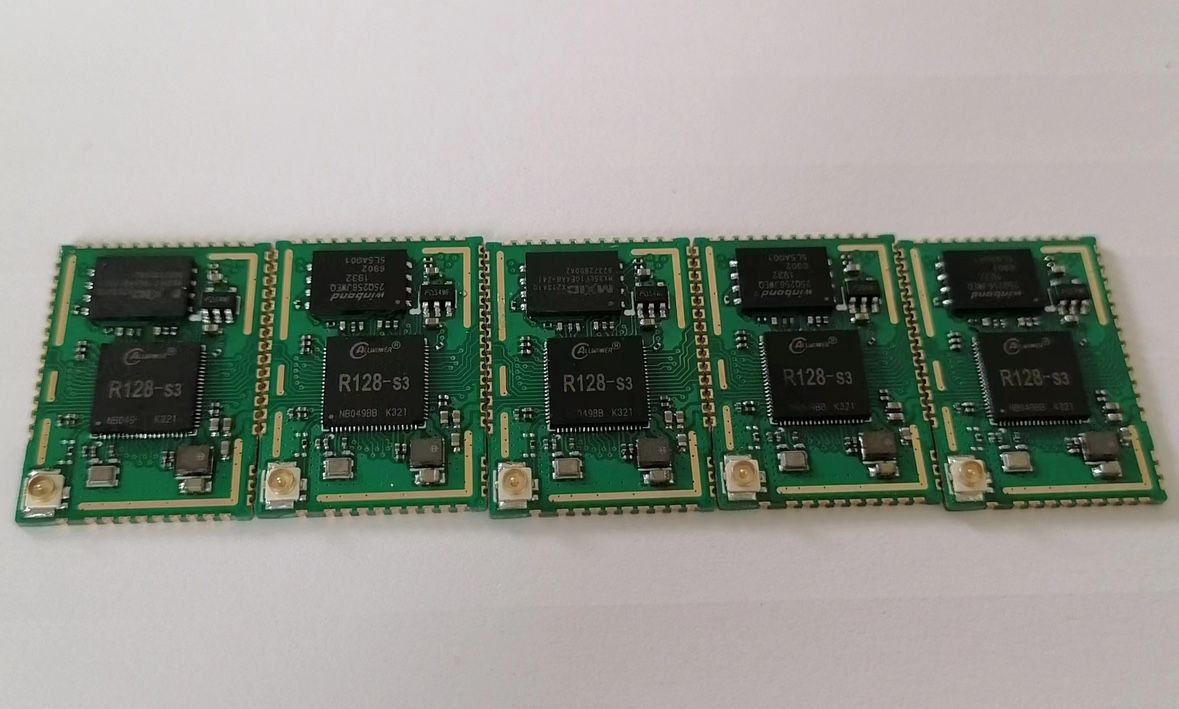

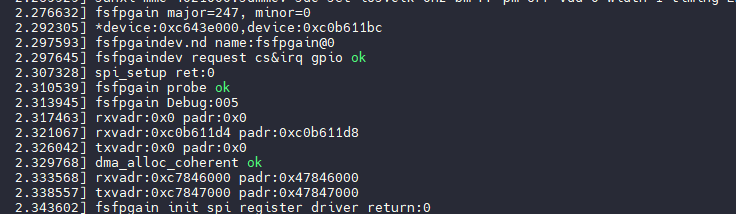

回复: R128-S3不支持NAND FLASH吗?还有SPI0端口不能指定到PA24-P29吗发布在 MR Series

@chen0505 PA引导是BROM不支持,BROM是固化在芯片里的,如果需要修改需要改版芯片

Note Description D/S Datasheet Support but no sample test S/T Support and sample test √ Support and mass produce X Not support (Blank) Can support but not support now Part Number Capacity JEDEC ID PACKAGE R128 Support Status MT29F2G01ABAGDSF-AAT(NW794) 256M 0x2C, 0x24 SOP-16 D/S MT29F1G01ABAFDSF-AAT(NW808) 128M 0x2C, 0x14 SOP-16 D/S MT29F2G01ABAGDWB 256M 0x2C,0x24 SOP-16 D/S W25N01GVZEIG 128M 0xEF 0xAA 0x21 D/S W25N02KVZEIR 256M 0xEF 0xAA 0x22 MX35LF2GE4AB 256M 0xC2 0x22 16-SOP MX35LF1GE4AB 128M 0xC2 0x12 8-WSON √ MX35LF2GE4AD 256M 0xC2 0x26 0x03 8-WSON D/S MX35LF1G24AD 128M 0xC2 0x14 MX35LF4GE4AD 512M GD5F1GQ4UBYIGR 128M 0xC8 0xD1 8-pad 8X6 WSON D/S GD5F2GQ4UB9IGR 256M 0xC8 0xD2 8-pad 8X6 WSON D/S GD5F1GQ4UCYIG 128M 0xC8 0xB1 0x48 WSON8(8x6mm) D/S GD5F1GQ5UEYIG 128M 0xC8 0x51 D/S GD5F2GQ5UEYIGR 256M 0xC8 0x52 GD5F4GQ6UEYIG 512M 0xC8 0x55 F50L1G41LB(2M) -> F50L1G41LB-104YG2M F50L1G41LB-104YG2ME 128M 0xC8 0x01 0x7F 0x7F 0x7F 8-WSON D/S F50L2G41XA 256M 0x2C, 0x24 DS35Q1GA-1B 128M 0xE5 0x71 8-WSON D/S DS35Q2GA-IB 256M 0xE5 0x72 DS35Q2GBXXX 256M 0xE5 0xf2 DS35Q4GMXXX 512M 0xE5 0xf4 DS35X1GBXXX 1G 0xE5 0xF1 8-WSON TC58CVG2S0H 512M 0x98 0xCD TC58CVG0S3HRAIG 128M 0x98 0xC2 8-WSON D/S FS35ND01G-S1F1QWFI 128M 0xCD 0xB1 WSON8(8x6mm) D/S FS35ND01G-S1Y2 128M 0xCD 0xEA WSON8 F35SQA001G 128M 0xCD 0x71 WSON8 √ F35SQA002G 256M 0xCD 0x72 EM73C044VCD-H 128M 0xD5 0x1C 8-WSON EM73E044SNA 128M 0xD5 0x03 8-WSON ZD35Q1GA-IBR 128M 0xba 0x71 8-WSON D/S PN26G01AWSIUG 128M 0xa1, 0xe1 WSON8(8x6mm) XT26G01A 128M 0x0b,0xe1 D/S XT26G02A 256M 0x0b,0xe2 XT26G04A 512M 0x0b,0xe3 WSON8(8x6mm) XT26G01CWSIG 128M 0x0b,0x11 D/S XT26G02CWSIG 256M 0x0b,0x12 XT26G04CWSIG 512M 0x0b,0x13 XT26G02ELGIGA 256M 0x2c, 0x24 FM25S01 128M 0xa1,0xa1 WSON8(8x6mm) FM25S01A 128M 0xa1,0xe4 FM25S02A 256M 0xa1,0xe5 SCN00SA3W1AI8A 128M 0xC8 0x21 8-WSON S35ML01G3 128M 0x01 0x15 S35ML02G300WH100 256M 0x01 0x25 S35ML04G3 512M 0x01 0x35 HYF1GQ4UDACAE 128M 0xC9 0x21 -

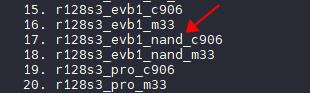

回复: R128-S3不支持NAND FLASH吗?还有SPI0端口不能指定到PA24-P29吗发布在 MR Series

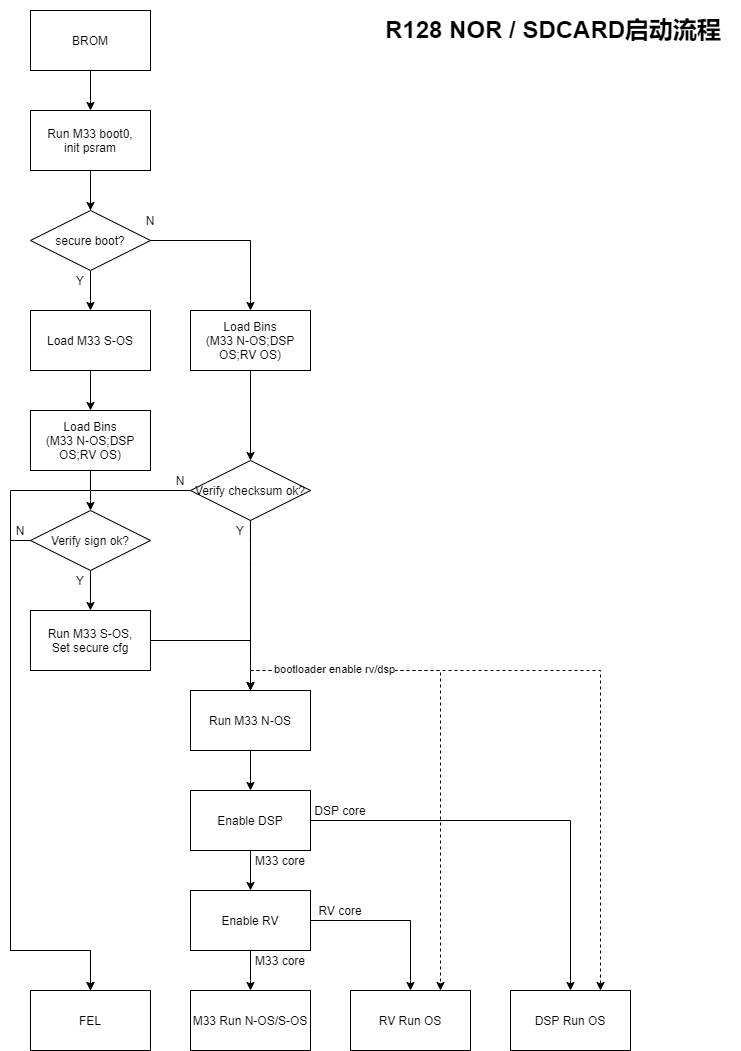

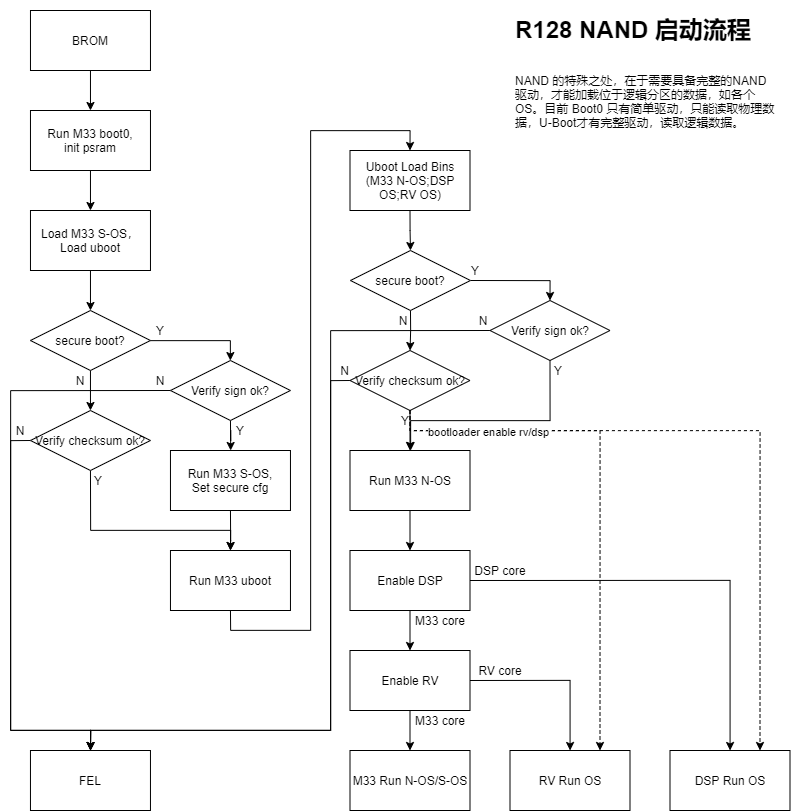

支持NAND的,下图的5个模块分别是NOR和NAND,

启动使用的SPI是在PB组,需要挂在PB上才能启动,并且需要专门配置的SDK,可以在SDK中看到有NAND的选项

附上两种存储介质的启动流程:

NOR:

NAND:

同时也支持 eMMC、SD-NAND启动

-

回复: V853 SDK:Linux内核中的MIPI DSI发布在 V Series

从 log中可以看到,

[ 0.293211] disp 0, clk: pll(426000000),clk(426000000),dclk(71000000) dsi_rate(71000000) [ 0.293211] clk real:pll(420000000),clk(420000000),dclk(105000000) dsi_rate(150000000)内核引脚正确初始化并执行送图,Uboot运行而Kernel不执行函数是因为Kernel驱动当接收到Uboot传入的显示屏信息后不会重新初始化屏幕,这样可以保证整个开机logo显示流畅。

这里log看到的驱动是ICN6202 TO LVDS,这是一颗转换MIPI DSI 转 LVDS的芯片,其MIPI初始化数据与普通 MIPI 屏幕不同,请检查下是否使用了正确的初始化。

MIPI 与 RGB 不同,MIPI需要配置屏幕的参数,需要针对屏幕编写驱动

-

回复: MQ-Quad H616 主线内核编译调试记录(u-boot、kernel、buildroot)发布在 H/F/TV Series

@king-zhao aw859a 的 WIFI 驱动可以在 OrangePi 官方仓库里找到

-

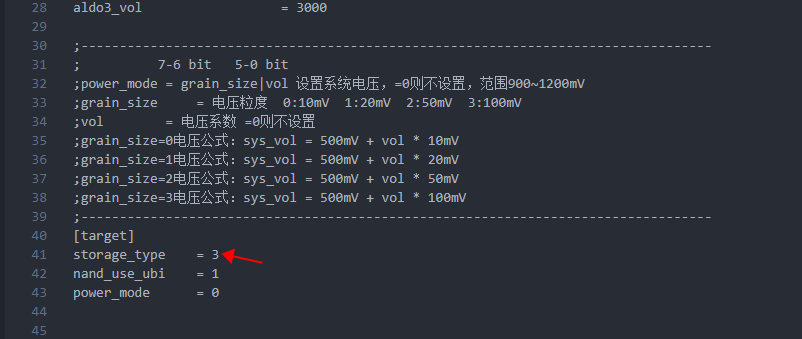

回复: tina SDK ERROR: Dependence broken. Firmware maybe incorrect & cannot booting up...发布在 Linux

@hgs1975 This is not a error, you can normal boot up while showing this error. What's your hardware and how to configure it

-

回复: SyterKit 启动 T527 失败发布在 T Series

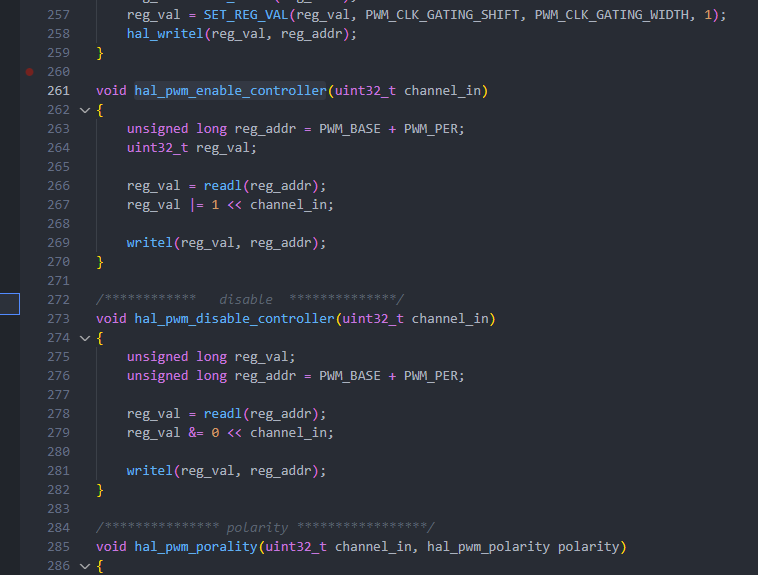

修改设备树,增加memory和chosen