可以自己打个包丢进去

YuzukiTsuru 发布的帖子

-

回复: make sun8iw20p1_nor_defconfig文件里面没有定义CONFIG_CONS_INDEX发布在 其它全志芯片讨论区

@smiletiger 那个是定义在kconfig里的,有一个default默认值,defconfig是精简的,如果与默认值相同那就不会在精简配置中定义

-

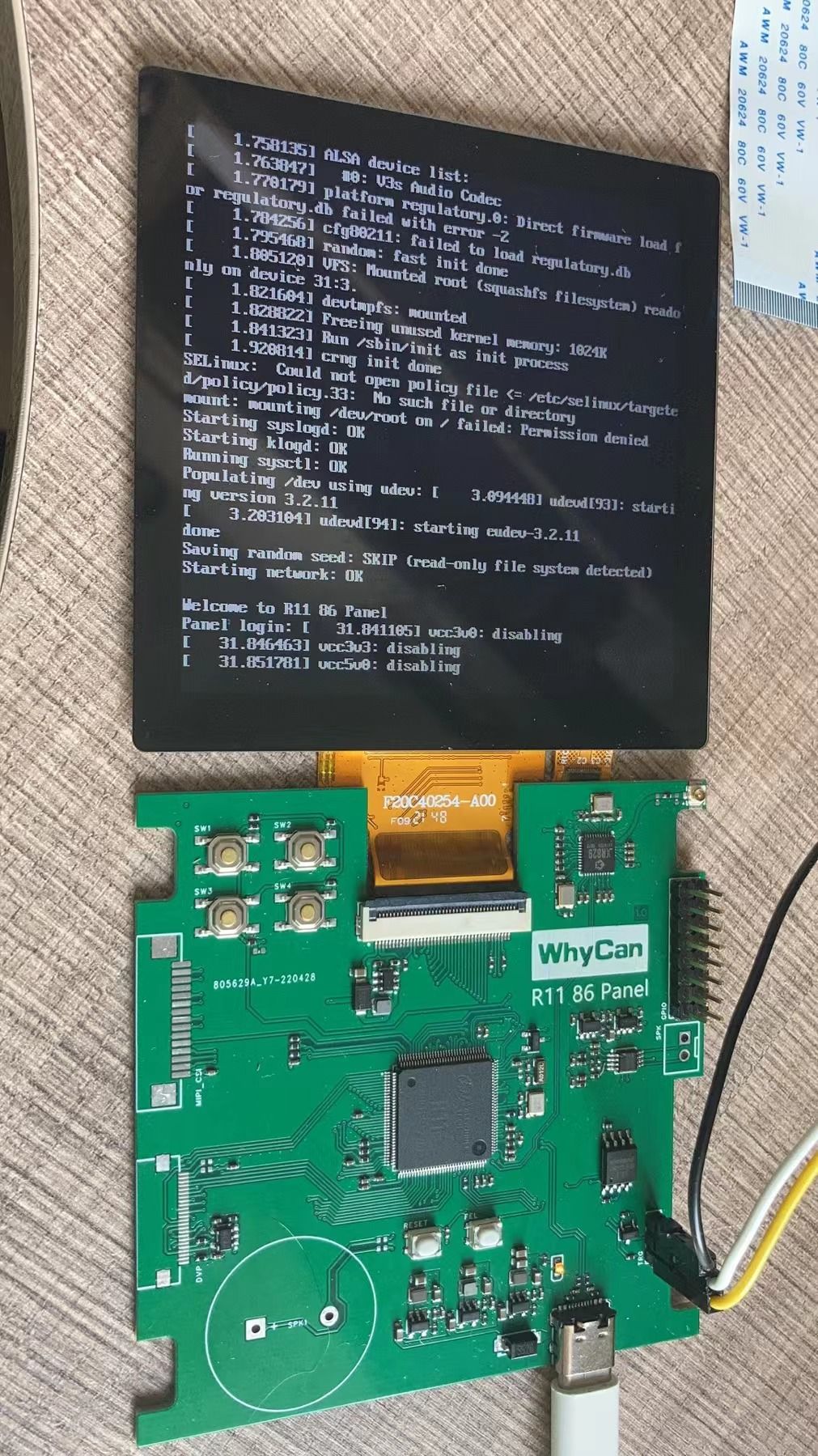

回复: 【WhyCan YuzukiHD联合出品】R11 86 面板发布在 A Series

@gregrgr SPI初始化屏幕,设置屏幕参数模式,然后让屏幕进入RGB模式,使用RGB666刷屏.当然你也可以让屏幕进MIPI模式用MIPI刷。不是SPI刷屏,那不得慢死。测试刷720p的屏幕可以到60fps

-

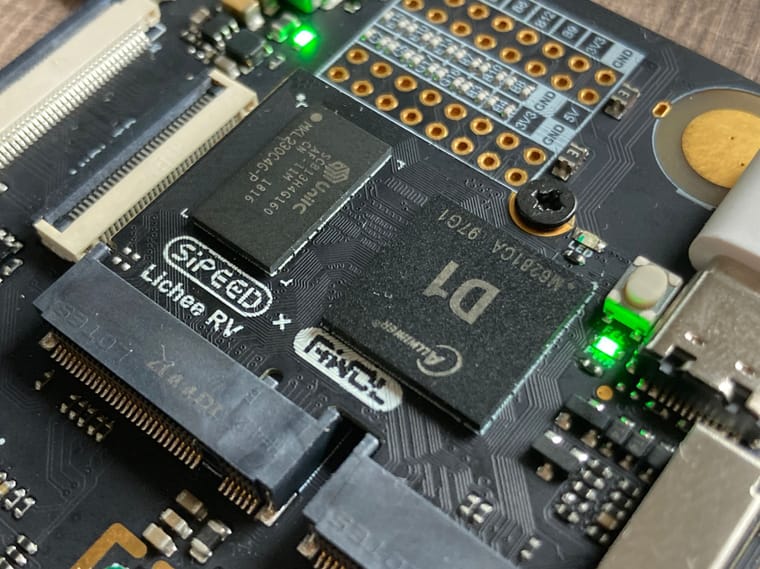

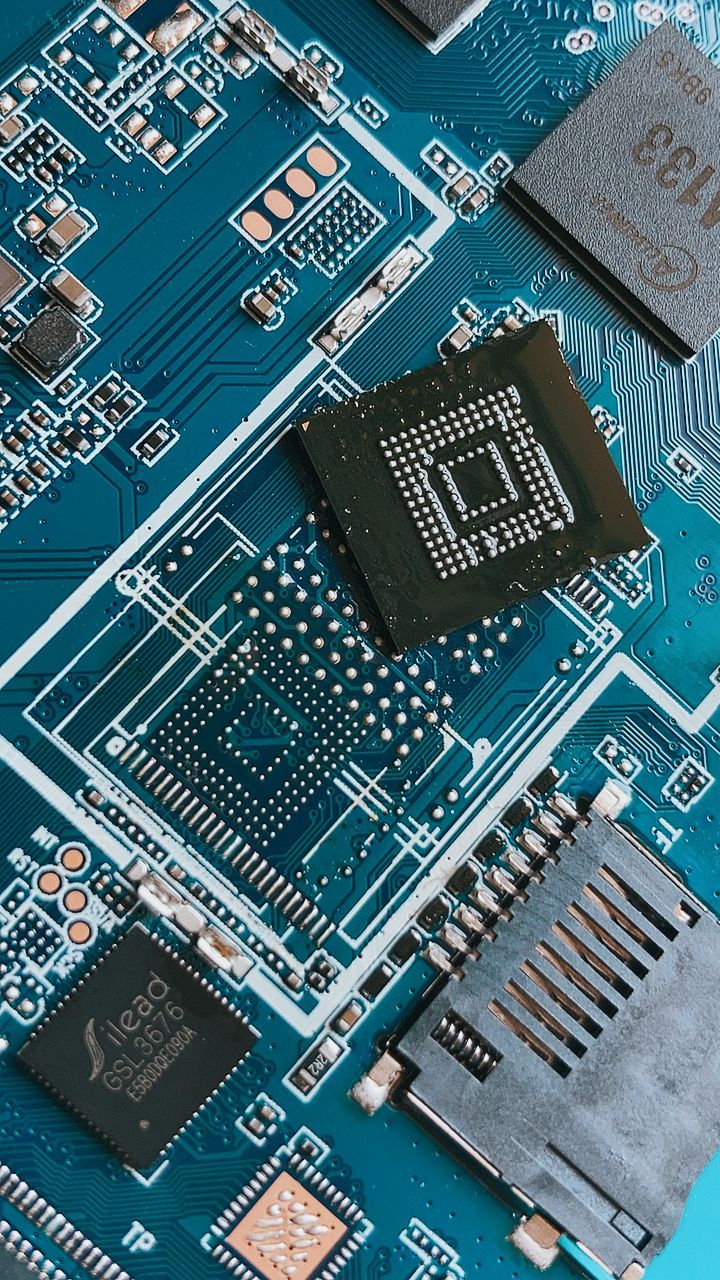

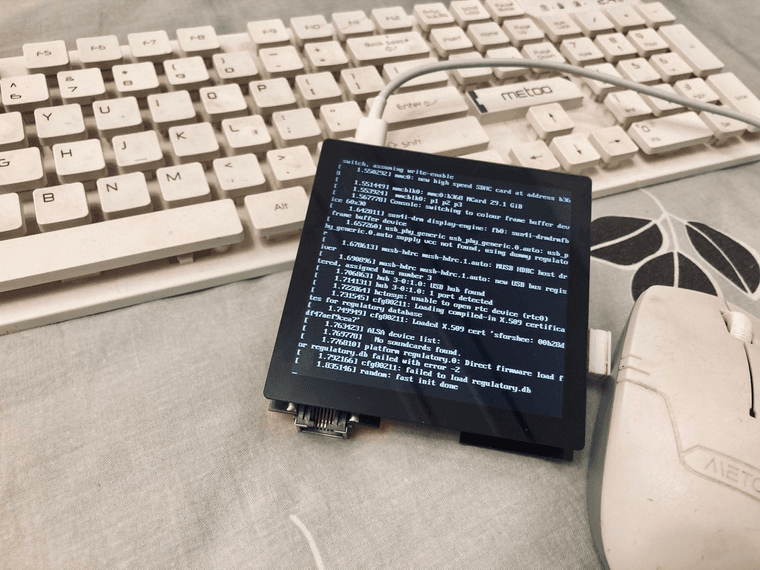

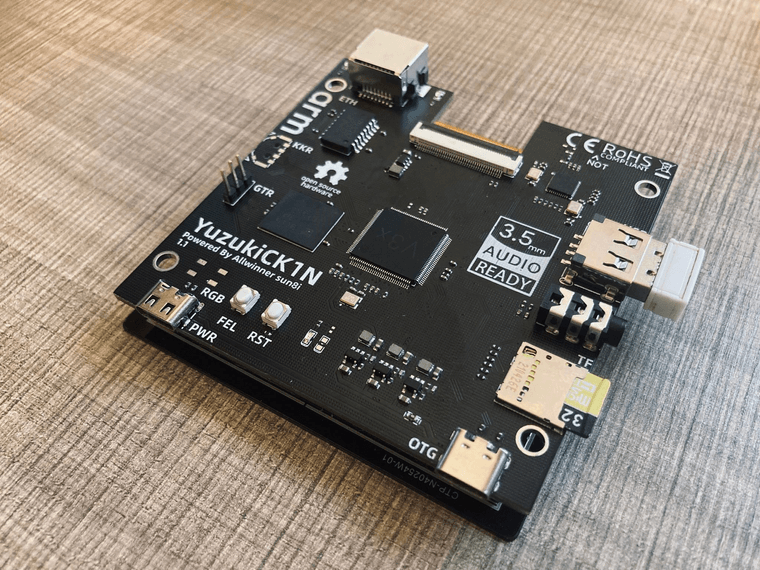

YuzukiCK1N - 基于全志V3x的触屏小电脑【开源硬件】发布在 其它全志芯片讨论区

YuzukiCK1N小电脑

- 支持USB

- 3.5音频输出

- 板载百兆网络

- eMMC储存

- Wi-Fi

- 128M内存,ARM A7

- 4寸方屏,支持480480或720720分辨率

- 电容触摸

软件

软件使用 Linux 5.4.180、U-Boot 2022.01

SDK:https://github.com/YuzukiHD/Buildroot-YuzukiSBC

SDK开发说明:https://yuzukihd.gloomyghost.com/Buildroot-YuzukiSBC/#/

固件下载:https://github.com/YuzukiHD/Buildroot-YuzukiSBC/releases/硬件

-

回复: 【WhyCan YuzukiHD联合出品】R11 86 面板发布在 A Series

屏幕是在UBOOT进行初始化的,初始化代码:

#ifndef _LCD_PANEL_INIT_H_ #define _LCD_PANEL_INIT_H_ #include <asm/gpio.h> #include <asm/arch/gpio.h> #define DELAYBIT 10 #define YS_LOG(fmt, arg...) \ do { \ printf(fmt, ##arg); \ } while (0) #define YS_DBG(fmt, arg...) YS_LOG("[Yuzuki LCD sSPI] " fmt, ##arg) #define st7701s_spi_sdi_0 gpio_direction_output(LCD_MOSI, 0) #define st7701s_spi_sdi_1 gpio_direction_output(LCD_MOSI, 1) #define st7701s_spi_scl_0 gpio_direction_output(LCD_CLK, 0) #define st7701s_spi_scl_1 gpio_direction_output(LCD_CLK, 1) int LCD_RST; // PG10 int LCD_MOSI; // PG11 int LCD_CLK; // PG12 int LCD_BL; // PG12 void lcd_delay_ms(int ms) { unsigned long long delay = ms * 1000 * 20; while (delay--) asm volatile("nop"); } void sunxi_lcd_delay_us(int us) { unsigned long long delay = 100 * us; while (delay--) asm volatile("nop"); } int SPI_Init(void) { int ret; LCD_RST = sunxi_name_to_gpio("PG10"); if (LCD_RST < 0) { YS_DBG("Error invalid LCD RST pin: PG, err %d\n", LCD_RST); return LCD_RST; } ret = gpio_request(LCD_RST, "LCD_RST"); if (ret) { YS_DBG("Error invalid LCD_RST pin: PG, err %d\n", LCD_RST); return ret; } YS_DBG("PG10 --> LCD_RST request OK\n"); LCD_MOSI = sunxi_name_to_gpio("PG11"); if (LCD_MOSI < 0) { YS_DBG("Error invalid LCD_MOSI pin: PG, err %d\n", LCD_MOSI); return LCD_MOSI; } ret = gpio_request(LCD_MOSI, "LCD_MOSI"); if (ret) { YS_DBG("Error invalid LCD_MOSI pin: PG, err %d\n", LCD_MOSI); return ret; } YS_DBG("PG11 --> LCD_MOSI request OK\n"); LCD_CLK = sunxi_name_to_gpio("PG12"); if (LCD_CLK < 0) { YS_DBG("Error invalid LCD_CLK pin: PG, err %d\n", LCD_CLK); return LCD_CLK; } ret = gpio_request(LCD_CLK, "LCD_CLK"); if (ret) { YS_DBG("Error invalid LCD_CLK pin: PG, err %d\n", LCD_CLK); return ret; } YS_DBG("PG12 --> LCD_CLK request OK\n"); LCD_BL = sunxi_name_to_gpio("PB4"); if (LCD_BL < 0) { YS_DBG("Error invalid LCD_CLK pin: PG, err %d\n", LCD_BL); return LCD_BL; } ret = gpio_request(LCD_BL, "LCD_BL"); if (ret) { YS_DBG("Error invalid LCD_BL pin: PG, err %d\n", LCD_BL); return ret; } YS_DBG("PB4 --> LCD_BL request OK\n"); gpio_direction_output(LCD_RST, 1); gpio_direction_output(LCD_MOSI, 1); gpio_direction_output(LCD_CLK, 1); return 0; } void LCD_WRITE_DATA(unsigned int value) { unsigned int i; st7701s_spi_sdi_1; st7701s_spi_scl_0; sunxi_lcd_delay_us(10); st7701s_spi_scl_1; for (i = 0; i < 8; i++) { sunxi_lcd_delay_us(10); if (value & 0x80) st7701s_spi_sdi_1; else st7701s_spi_sdi_0; value <<= 1; sunxi_lcd_delay_us(10); st7701s_spi_scl_0; st7701s_spi_scl_1; } sunxi_lcd_delay_us(10); } void LCD_WRITE_COMMAND(unsigned int value) { unsigned int i; st7701s_spi_sdi_0; st7701s_spi_scl_0; sunxi_lcd_delay_us(10); st7701s_spi_scl_1; for (i = 0; i < 8; i++) { sunxi_lcd_delay_us(10); if (value & 0x80) st7701s_spi_sdi_1; else st7701s_spi_sdi_0; st7701s_spi_scl_0; sunxi_lcd_delay_us(10); st7701s_spi_scl_1; value <<= 1; } sunxi_lcd_delay_us(10); } void LCD_Init(void) { YS_DBG("LCD Panel ST7701s init\n"); SPI_Init(); lcd_delay_ms(1000); gpio_direction_output(LCD_RST, 0); lcd_delay_ms(120); gpio_direction_output(LCD_RST, 1); lcd_delay_ms(120); LCD_WRITE_COMMAND(0xFF); LCD_WRITE_DATA(0x77); LCD_WRITE_DATA(0x01); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x10); LCD_WRITE_COMMAND(0xC0); LCD_WRITE_DATA(0x3B); LCD_WRITE_DATA(0x00); LCD_WRITE_COMMAND(0xC1); LCD_WRITE_DATA(0x0D); LCD_WRITE_DATA(0x02); LCD_WRITE_COMMAND(0xC2); LCD_WRITE_DATA(0x21); LCD_WRITE_DATA(0x08); LCD_WRITE_COMMAND(0xCD); LCD_WRITE_DATA(0x18); //0F 08-OK D0-D18 LCD_WRITE_COMMAND(0xB0); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x11); LCD_WRITE_DATA(0x18); LCD_WRITE_DATA(0x0E); LCD_WRITE_DATA(0x11); LCD_WRITE_DATA(0x06); LCD_WRITE_DATA(0x07); LCD_WRITE_DATA(0x08); LCD_WRITE_DATA(0x07); LCD_WRITE_DATA(0x22); LCD_WRITE_DATA(0x04); LCD_WRITE_DATA(0x12); LCD_WRITE_DATA(0x0F); LCD_WRITE_DATA(0xAA); LCD_WRITE_DATA(0x31); LCD_WRITE_DATA(0x18); LCD_WRITE_COMMAND(0xB1); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x11); LCD_WRITE_DATA(0x19); LCD_WRITE_DATA(0x0E); LCD_WRITE_DATA(0x12); LCD_WRITE_DATA(0x07); LCD_WRITE_DATA(0x08); LCD_WRITE_DATA(0x08); LCD_WRITE_DATA(0x08); LCD_WRITE_DATA(0x22); LCD_WRITE_DATA(0x04); LCD_WRITE_DATA(0x11); LCD_WRITE_DATA(0x11); LCD_WRITE_DATA(0xA9); LCD_WRITE_DATA(0x32); LCD_WRITE_DATA(0x18); LCD_WRITE_COMMAND(0xFF); LCD_WRITE_DATA(0x77); LCD_WRITE_DATA(0x01); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x11); LCD_WRITE_COMMAND(0xB0); LCD_WRITE_DATA(0x60); LCD_WRITE_COMMAND(0xB1); LCD_WRITE_DATA(0x30); LCD_WRITE_COMMAND(0xB2); LCD_WRITE_DATA(0x87); LCD_WRITE_COMMAND(0xB3); LCD_WRITE_DATA(0x80); LCD_WRITE_COMMAND(0xB5); LCD_WRITE_DATA(0x49); LCD_WRITE_COMMAND(0xB7); LCD_WRITE_DATA(0x85); LCD_WRITE_COMMAND(0xB8); LCD_WRITE_DATA(0x21); LCD_WRITE_COMMAND(0xC1); LCD_WRITE_DATA(0x78); LCD_WRITE_COMMAND(0xC2); LCD_WRITE_DATA(0x78); lcd_delay_ms(20); LCD_WRITE_COMMAND(0xE0); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x1B); LCD_WRITE_DATA(0x02); LCD_WRITE_COMMAND(0xE1); LCD_WRITE_DATA(0x08); LCD_WRITE_DATA(0xA0); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x07); LCD_WRITE_DATA(0xA0); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x44); LCD_WRITE_DATA(0x44); LCD_WRITE_COMMAND(0xE2); LCD_WRITE_DATA(0x11); LCD_WRITE_DATA(0x11); LCD_WRITE_DATA(0x44); LCD_WRITE_DATA(0x44); LCD_WRITE_DATA(0xED); LCD_WRITE_DATA(0xA0); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0xEC); LCD_WRITE_DATA(0xA0); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x00); LCD_WRITE_COMMAND(0xE3); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x11); LCD_WRITE_DATA(0x11); LCD_WRITE_COMMAND(0xE4); LCD_WRITE_DATA(0x44); LCD_WRITE_DATA(0x44); LCD_WRITE_COMMAND(0xE5); LCD_WRITE_DATA(0x0A); LCD_WRITE_DATA(0xE9); LCD_WRITE_DATA(0xD8); LCD_WRITE_DATA(0xA0); LCD_WRITE_DATA(0x0C); LCD_WRITE_DATA(0xEB); LCD_WRITE_DATA(0xD8); LCD_WRITE_DATA(0xA0); LCD_WRITE_DATA(0x0E); LCD_WRITE_DATA(0xED); LCD_WRITE_DATA(0xD8); LCD_WRITE_DATA(0xA0); LCD_WRITE_DATA(0x10); LCD_WRITE_DATA(0xEF); LCD_WRITE_DATA(0xD8); LCD_WRITE_DATA(0xA0); LCD_WRITE_COMMAND(0xE6); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x11); LCD_WRITE_DATA(0x11); LCD_WRITE_COMMAND(0xE7); LCD_WRITE_DATA(0x44); LCD_WRITE_DATA(0x44); LCD_WRITE_COMMAND(0xE8); LCD_WRITE_DATA(0x09); LCD_WRITE_DATA(0xE8); LCD_WRITE_DATA(0xD8); LCD_WRITE_DATA(0xA0); LCD_WRITE_DATA(0x0B); LCD_WRITE_DATA(0xEA); LCD_WRITE_DATA(0xD8); LCD_WRITE_DATA(0xA0); LCD_WRITE_DATA(0x0D); LCD_WRITE_DATA(0xEC); LCD_WRITE_DATA(0xD8); LCD_WRITE_DATA(0xA0); LCD_WRITE_DATA(0x0F); LCD_WRITE_DATA(0xEE); LCD_WRITE_DATA(0xD8); LCD_WRITE_DATA(0xA0); LCD_WRITE_COMMAND(0xEB); LCD_WRITE_DATA(0x02); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0xE4); LCD_WRITE_DATA(0xE4); LCD_WRITE_DATA(0x88); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x40); LCD_WRITE_COMMAND(0xEC); LCD_WRITE_DATA(0x3C); LCD_WRITE_DATA(0x00); LCD_WRITE_COMMAND(0xED); LCD_WRITE_DATA(0xAB); LCD_WRITE_DATA(0x89); LCD_WRITE_DATA(0x76); LCD_WRITE_DATA(0x54); LCD_WRITE_DATA(0x02); LCD_WRITE_DATA(0xFF); LCD_WRITE_DATA(0xFF); LCD_WRITE_DATA(0xFF); LCD_WRITE_DATA(0xFF); LCD_WRITE_DATA(0xFF); LCD_WRITE_DATA(0xFF); LCD_WRITE_DATA(0x20); LCD_WRITE_DATA(0x45); LCD_WRITE_DATA(0x67); LCD_WRITE_DATA(0x98); LCD_WRITE_DATA(0xBA); LCD_WRITE_COMMAND(0xFF); LCD_WRITE_DATA(0x77); LCD_WRITE_DATA(0x01); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x00); LCD_WRITE_DATA(0x00); LCD_WRITE_COMMAND(0x3A); LCD_WRITE_DATA(0x66); LCD_WRITE_COMMAND(0x36); LCD_WRITE_DATA(0x00); LCD_WRITE_COMMAND(0x21); LCD_WRITE_COMMAND(0x11); lcd_delay_ms(120); LCD_WRITE_COMMAND(0x29); lcd_delay_ms(120); } #endif // _LCD_PANEL_INIT_H_ -

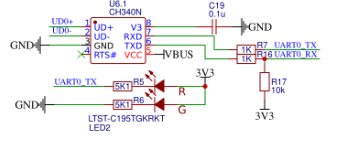

回复: 【WhyCan YuzukiHD联合出品】R11 86 面板发布在 A Series

原理图:SCH_R11_86_Panel_2022-05-10.pdf

Gerber:4509cffe-4971-4f8b-bbf7-65970f8d6d11-Gerber_PCB1_2022-06-18.zip

立创EDA专业版工程文件:cf5cf19a-e977-4e9f-be5b-988c5bbf3709-ProProject_R11+86Panel_2022-06-18.zip适配了 Kernel: 5.4.180 U-Boot 2022.01

SDK: https://github.com/YuzukiHD/Buildroot-YuzukiSBC

SDK开发文档:https://yuzukihd.gloomyghost.com/Buildroot-YuzukiSBC/#/选择

yuzukihd_r11_86panel_defconfig -

回复: 【极简操作】使用builroot 2021一键编译生成D1 nezha 系统镜像!发布在 MR Series

@andy89926 硬件设计是正确的吗,我这里有一个卡槽的CD脚是插入上拉,坑了我一整天

-

回复: 参考设计绘制的PCB,3V3输出电压不对发布在 Wireless & Analog Series

@gregrgr 外围设备呢,可能出现外围灌入IO的情况,因为内部这个电压是内置PMU管理的

-

回复: 研究了好几天还是没搞懂t113的uboot到底要烧录到哪里发布在 MR Series

@smiletiger

可以参考 https://github.com/YuzukiHD/Buildroot-YuzukiSBC 里的 https://github.com/YuzukiHD/Buildroot-YuzukiSBC/tree/master/buildroot/board/mangopi/mq-dual/patch/uboot 部分,可以把uboot转为标准编译模式。这个是打包bootimg的方法 https://github.com/YuzukiHD/Buildroot-YuzukiSBC/blob/master/buildroot/board/allwinner-generic/sun8i-generic/scripts/post-build.sh -

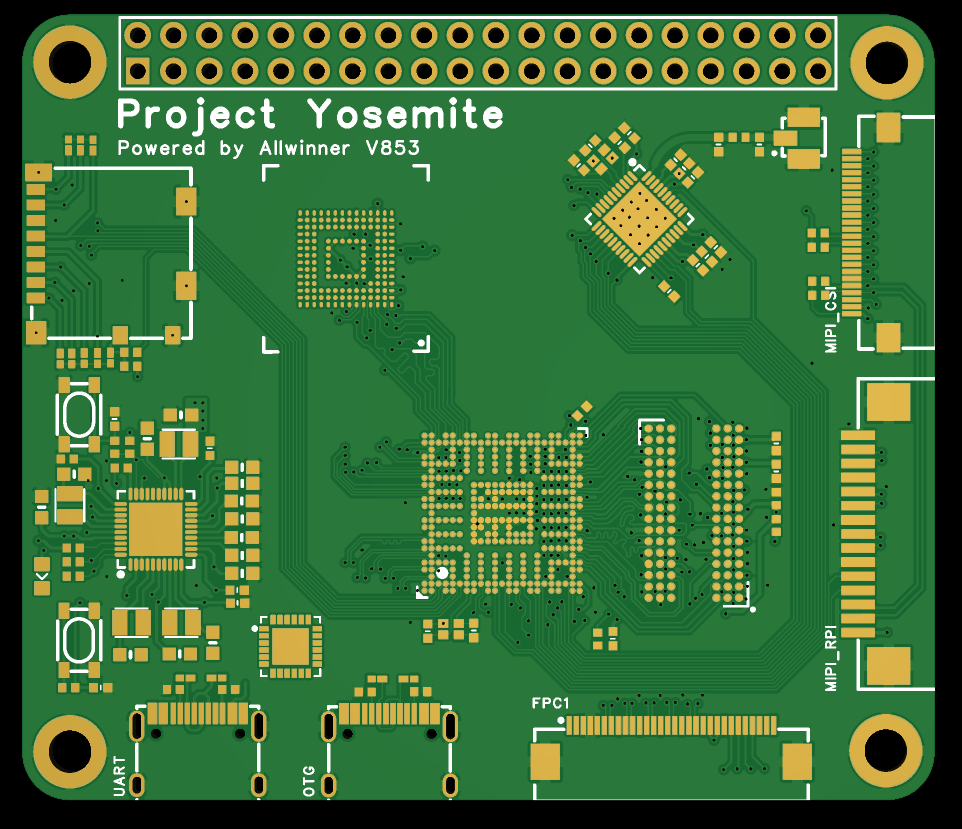

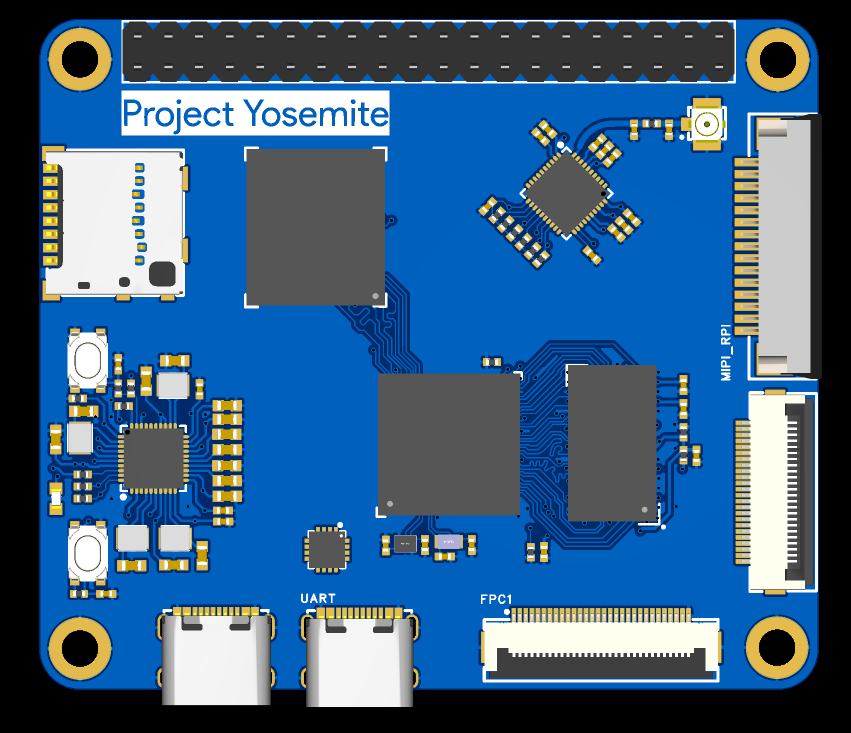

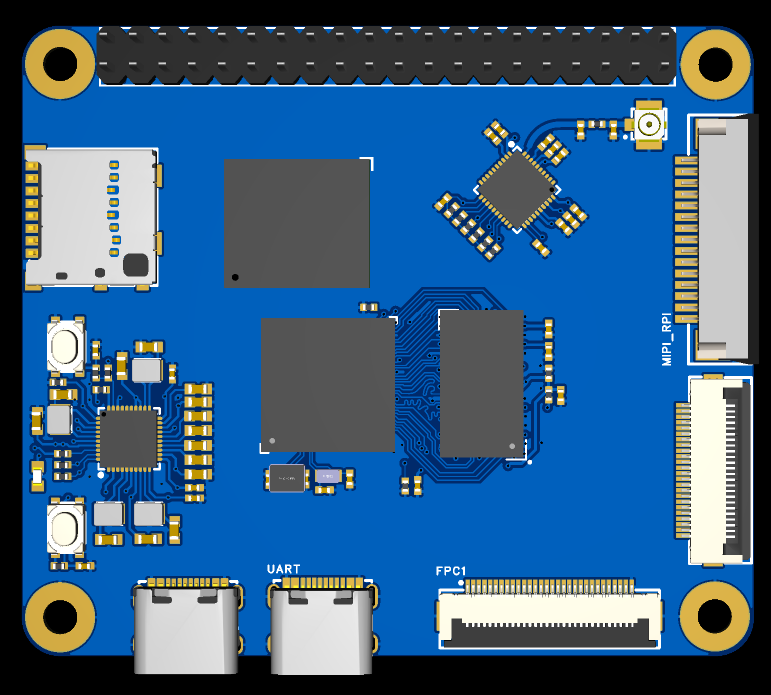

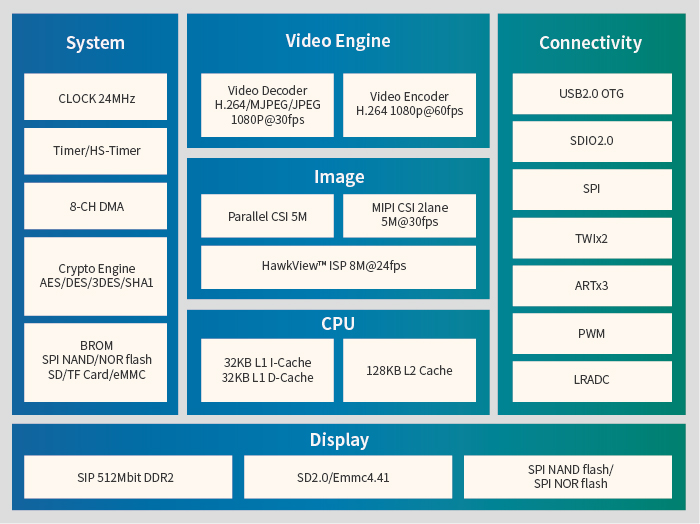

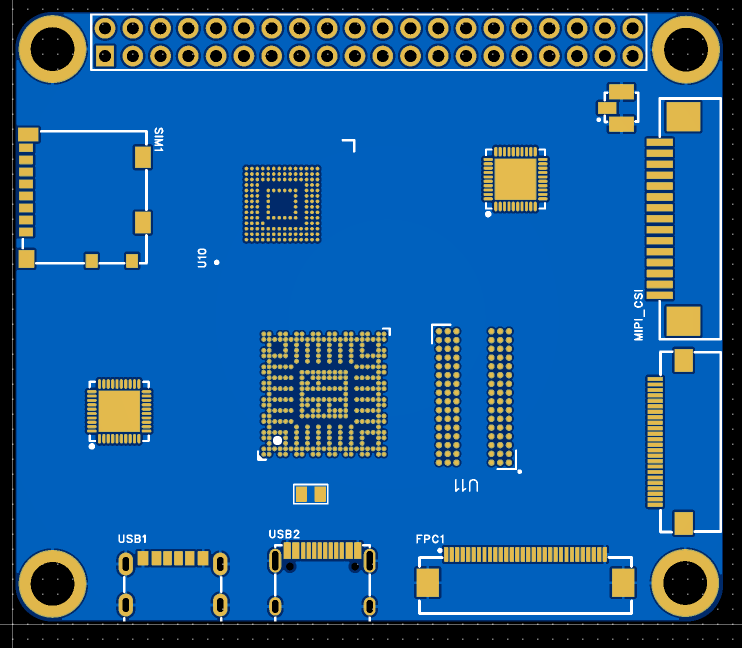

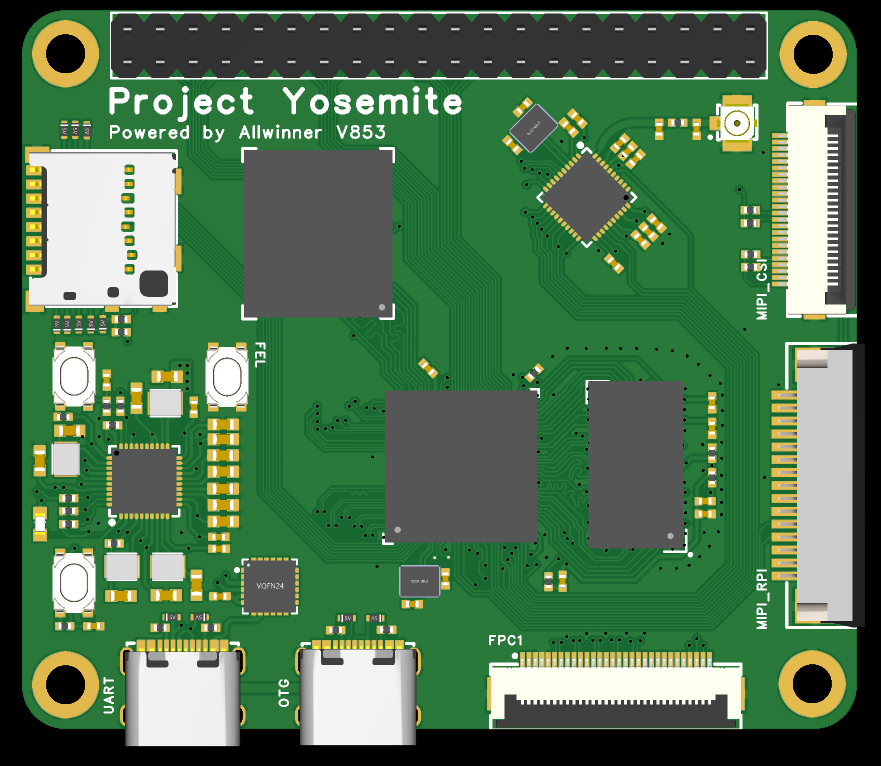

Porject Yosemite - 基于全志V853的开发板发布在 V Series

- V853 ARM A7 + RISC-V E907 + 1T NPU

- UP to 2GiB DDR3 and 128GiB EMMC

- Raspberry Pi Camera Connector

- 2 lane MIPI-CSI

- 4 lane MIPI-DSI up to 1920x1200

- Built-in USB to UART Support RV and ARM

- Built-in XR829 Wi-Fi BT

- Raspberry Pi A Size and Pinout

开源地址:https://oshwhub.com/gloomyghost/porject-yosemite

This is a high-performance heterogeneous edge AI visual processing core development board based on Allwinner V853 - Porject Yosemite. Allwinner V853 supports simultaneous heterogeneous debugging of Arm and RISC-V cores, with 1Tops NPU, and supports TensorFlow, Caffe, Tflite, Python, Onnx NN and other models.

The development board design adopts the Raspberry Pi A version, with a 40Pin IO output and a MIPI DSI screen interface, supporting up to 1920x1200 resolution MIPI screens and capacitive touch.

-

回复: YuzukiXR806 使用 FreeRTOS 开发运行Hello Demo发布在 Wireless & Analog Series

@wlb965 可以,project里按照那个目录结构编写就行了,不需要完全懂

-

回复: 求教D1+Tina能否直接将终端输出到屏幕进行操作呢?发布在 MR Series

可以,详见:D1咋把控制台弄到hdmi上呢?

https://bbs.aw-ol.com/topic/1320/share/4 -

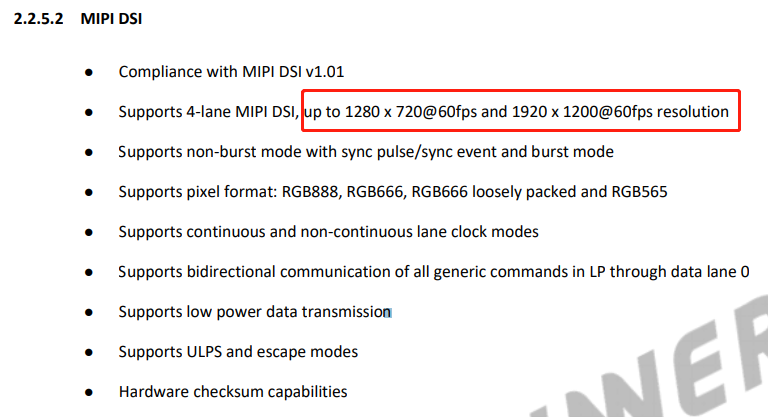

数据手册里的 MIPI DSI 定义了2个分辨率,是什么意思呢发布在 其它全志芯片讨论区

这里写了2个分辨率,一个1280x720,一个1920x1200,到底是按前一个还是后一个?

还是说1280*720以下分辨率可以随意修改,以上只能1920x1200

-

回复: V3s的网络很难连,很挑线是什么问题呢?1米、2米都不行,有一条很长的确可以。发布在 其它全志芯片讨论区

@lonerwolf REXT电阻的2.49k是一个外部参考,就跟ZQ的240欧一样,改了会导致运行不正常,至于多不正常得看芯片的容错能力了(

-

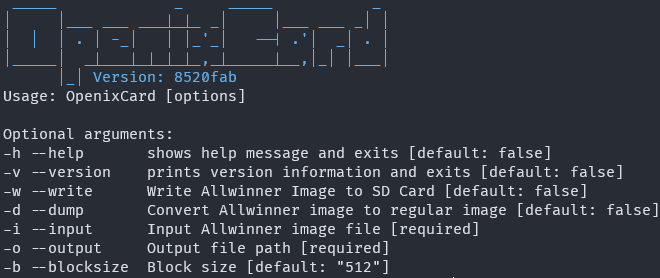

OpenixCard - 在 Linux 系统刷写全志镜像到 SD 卡发布在 编译和烧写问题专区

远古的坑了,最近有时间终于填了下。

线刷在Windows上有PhoenixSuit,在Linux上有LiveSuit,刷写都很方便。但是到了卡刷就寄了,只有一个Windows下的PhoenixCard,在Linux下刷写很头疼。于是写了这个小东西。

功能:

- 在 Linux 解包 Tina 镜像

- 将 Tina 镜像转换为标准的镜像,转换后的镜像可以使用DD、USB Image Tool、Win32diskimager、Etcher刷写。方便分发。

- 更多功能咕咕中....

开源地址

https://github.com/YuzukiTsuru/OpenixCard

视频:转换全志的镜像成为标准镜像并用Etcher刷写。

-

回复: 超级萌新学晕哥也整了一台“台电” P85 TLA016 平板电脑发布在 其它全志芯片讨论区

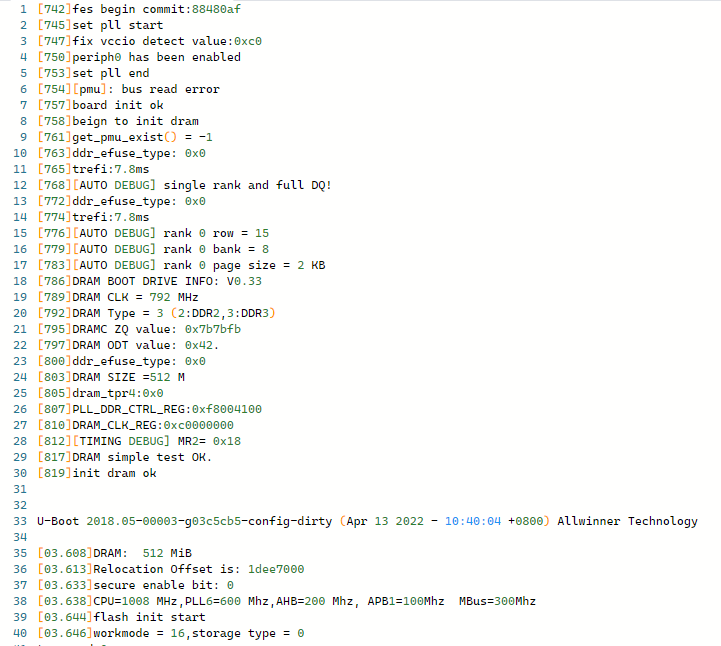

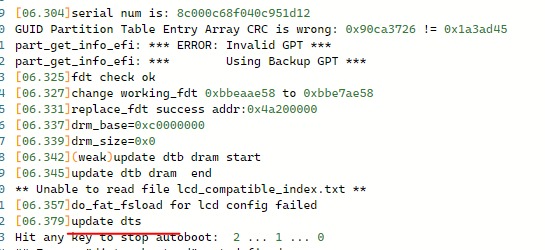

测试下

setenv bootargs earlyprintk=sunxi-uart,0x05000000 console=ttyS0,115200 root=/dev/mmcblk0p4 init=/init sunxi_flash read 45000000 boot;bootm 45000000 -

回复: 超级萌新学晕哥也整了一台“台电” P85 TLA016 平板电脑发布在 其它全志芯片讨论区

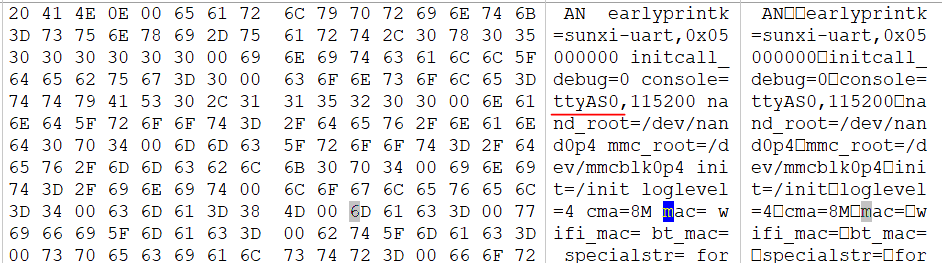

屏幕是K080_IM2AYC805_R_800x1280

Uboot CFG

earlyprintk=sunxi-uart,0x05000000 initcall_debug=0 console=ttyAS0,115200 nand_root=/dev/nand0p4 mmc_root=/dev/mmcblk0p4 init=/init loglevel=4 cma=8M mac= wifi_mac= bt_mac= specialstr= force_normal_boot=1 slot_suffix=_a keybox_list=widevine,ec_key,ec_cert1,ec_cert2,ec_cert3,rsa_key,rsa_cert1,rsa_cert2,rsa_cert3 ab_partition_list=bootloader,env,boot,vendor_boot,dtbo,vbmeta,vbmeta_system,vbmeta_vendor trace_buf_size=64M trace_event=sched_wakeup,sched_switch,sched_blocked_reason,sched_cpu_hotplug,block,ext4 trace_enable=0 setargs_nand=setenv bootargs earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${nand_root} init=${init} cma=${cma} snum=${snum} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} specialstr=${specialstr} gpt=1 androidboot.force_normal_boot=${force_normal_boot} androidboot.slot_suffix=${slot_suffix} setargs_mmc=setenv bootargs earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${mmc_root} init=${init} cma=${cma} snum=${snum} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} specialstr=${specialstr} gpt=1 androidboot.force_normal_boot=${force_normal_boot} androidboot.slot_suffix=${slot_suffix} boot_normal=sunxi_flash read 45000000 boot;bootm 45000000 boot_recovery=sunxi_flash read 45000000 recovery;bootm 45000000 boot_fastboot=fastboot bootdelay=0 bootcmd=run setargs_nand boot_normal -

回复: 超级萌新学晕哥也整了一台“台电” P85 TLA016 平板电脑发布在 其它全志芯片讨论区

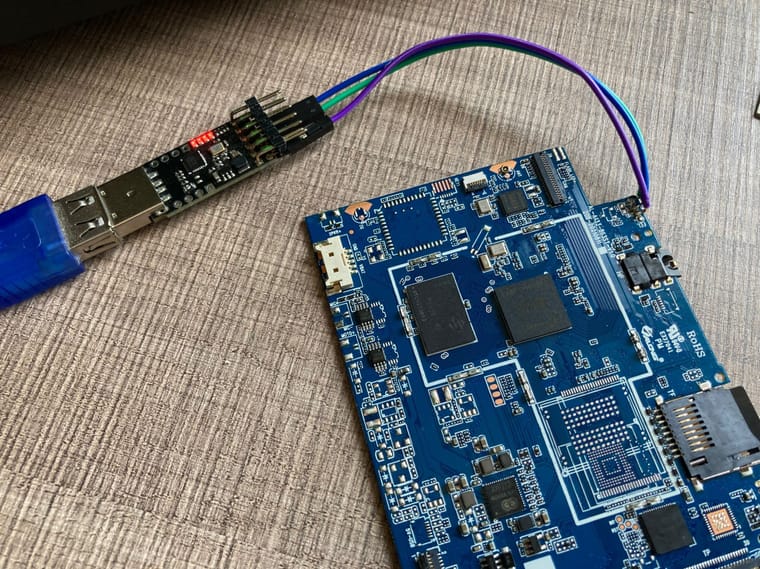

串口可以输入了。抓到完整的设备树